#### **MAX2990**

### 10kHz to 490kHz OFDM-Based Power Line Communication Modem

#### **General Description**

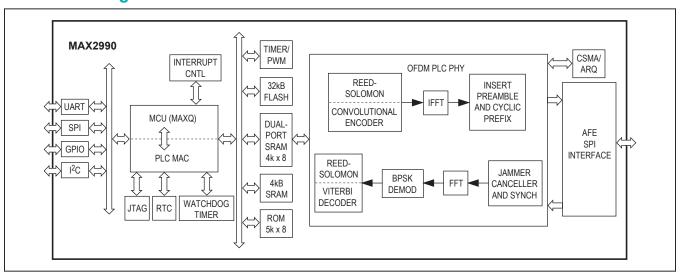

The MAX2990 power line communication (PLC) base-band modem delivers a cost-effective, reliable, halfduplex asynchronous data communication over AC power lines at speeds up to 100kbps. The MAX2990 is a highly integrated system-on-chip (SoC) that combines the physical (PHY) and media access control (MAC) layers using Maxim's 16-bit MAXQ microcontroller core. The MAX2990 utilizes OFDM modulation techniques to enable robust data communication using the same electrical network that supplies power to all other devices on the network.

The MAX2990 includes the MAXQ microcontroller core. The MAXQ is a 16-bit RISC microcontroller with 32kB flash memory, 5.12kB of ROM, and 8kB SRAM, of which 4kB that can be simultaneously accessed by the MCU and the PHY. The MAX2990 is integrated with modules for serial communication (SPI $^{\text{TM}}$ , I<sup>2</sup>C, UART) and a real-time clock (RTC) for time stamping, in addition to standard blocks such as timers, GPIO, and external interrupts.

The MAX2990 transceiver is based on an orthogonal frequency division multiplexing (OFDM) technique that allows robust data transmission over poor channel conditions specifically for environments with impulsive noise. OFDM with binary phase shift key (BPSK) and forward error correcting (FEC) blocks are used because of their inherent adaptability in the presence of frequency selective channels without the use of equalizers, resilience to jammer signals, robust communications in the presence of group delay spread, and robustness to impulsive noise. The MAX2990 features jammer cancellation that removes constant sinusoidal interference signals for FCC and ARIB bands. Privacy is provided by DES encryption.

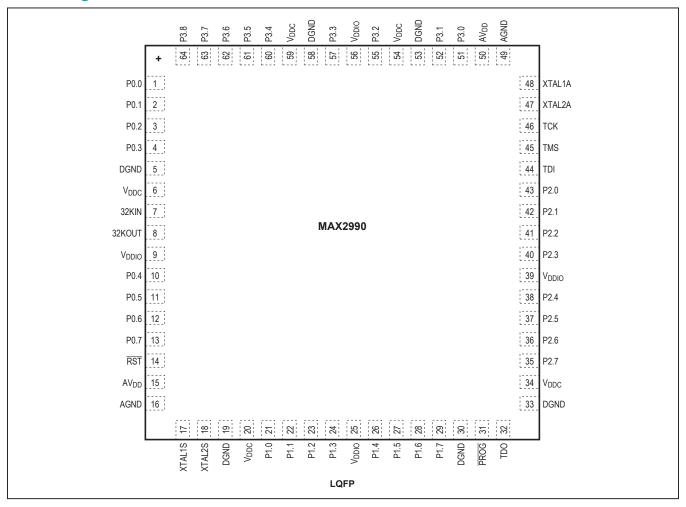

The MAX2990 is available in a 64-pin LQFP package and is specified over the -40°C to +85°C extended temperature range.

#### **Applications**

- Automatic Meter Reading

- Home Automation

- Heating Ventilation and Air Conditioning (HVAC)

- Building Automation

- Industrial Automation

- Lighting Control

- Sensor Control and Data Acquisition

- Remote Monitoring and Control

- Voice-Over-Powerline

- Security Systems/Keyless Entry

#### **Features**

- Combines the Physical Layer (PHY) and Media Access Controller (MAC)

- Integrated Microcontroller with 32kB Password-Protected Flash Memory and 8kB SRAM

- Maximum Effective Data Rate in Normal Mode 32kbps at 10kHz to 95kHz and 100kbps at 10kHz to 490kHz

- · Complies with

CENELEC A (10kHz to 95kHz)

CENELEC B (95kHz to 120kHz)

CENELEC C (120kHz to 140kHz)

FCC (10kHz to 490kHz)

ARIB (10kHz to 450kHz)

- Includes Forward Error Correction (FEC) Mechanism and CRC16

- Includes Fast DES Engine as the Encryption/Decryption Coprocessor and CRC32

- Jammer Cancellation for FCC and ARIB

- User-Configured Start and End Operating Frequency

- Carrier Sense Multiple Access/Collision Avoidance (CSMA/CA) Channel Access Arbitration

- Automatic Repeat Request (ARQ) to Enhance Error Detection and Improve Data Reliability

- Supports SPI, I2C, and UART Interfaces

- Real-Time Clock (RTC)

- PWM Counters

- Built-In Test Mode Engine for Identifying Channel Conditions

### **Ordering Information**

| PART        | TEMP RANGE     | PIN-PACKAGE |  |

|-------------|----------------|-------------|--|

| MAX2990ECB+ | -40°C to +85°C | 64 LQFP     |  |

<sup>+</sup>Denotes a lead-free package.

Pin Configuration appears at end of data sheet.

Typical Application Circuit appears at end of data sheet.

SPI is a trademark of Motorola, Inc.

### **Absolute Maximum Ratings**

| V <sub>DDIO</sub> to DGND                            | 0.5V to +3.6V  | Junction-to-Case Thermal Resistance (θ | <sub>JC</sub> ) (Note 1)    |

|------------------------------------------------------|----------------|----------------------------------------|-----------------------------|

| V <sub>DDC</sub> to DGND                             | 0.5V to +1.98V | 64-Pin LQFP                            | 8°C/W                       |

| AV <sub>DD</sub> to AGND                             | 0.5V to +1.98V | Junction-to-Ambient Thermal Resistance | (θ <sub>JA</sub> ) (Note 1) |

| Port0, Port1, Port2 to GPIO                          | 0.5V to +5.5V  | 64-Pin LQFP                            | 42°C/W                      |

| XTAL1S, XTAL2S, XTAL1A, XTAL2A                       | 0.5V to +1.98V | Operating Temperature Range            | 40°C to +85°C               |

| All Other Pins                                       | 0.5V to +3.6V  | Junction Temperature                   | +150°C                      |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C | (1)            | Storage Temperature Range              | 65°C to +150°C              |

| 64-Pin LQFP (derate 23.8mW/°C above                  | +70°C)1905mW   | Lead Temperature (soldering, 10s)      | +300°C                      |

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to **www.maximintegrated.com/thermal-tutorial**.

CAUTION! ESD SENSITIVE DEVICE

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **DC Electrical Characteristics**

$(V_{DDIO} = +3.0V \text{ to } +3.6V, \ V_{DDC} = AV_{DD} = +1.62V \text{ to } +1.98V, \ T_{A} = -40^{\circ}\text{C to } +85^{\circ}\text{C}, \ \text{unless otherwise noted.}$  Typical values are at  $V_{DDIO} = +3.3V, \ V_{DDC} = AV_{DD} = +1.8V, \ T_{A} = +25^{\circ}\text{C.}) \ (\text{Note 2})$

| PARAMETER                                              | SYMBOL             | CONDITIONS                 | MIN                        | TYP  | MAX                       | UNITS |  |

|--------------------------------------------------------|--------------------|----------------------------|----------------------------|------|---------------------------|-------|--|

| +3.3V I/O Supply Voltage                               | V <sub>DDIO</sub>  |                            | 3.0                        | 3.3  | 3.6                       | V     |  |

| +1.8V Core Supply Voltage                              | V <sub>DDC</sub>   |                            | 1.70                       | 1.80 | 1.98                      | V     |  |

| +1.8V Analog Core Supply                               | AV <sub>DD</sub>   |                            | 1.70                       | 1.80 | 1.98                      | V     |  |

| High-Level Output Voltage                              | V <sub>OH</sub>    | I <sub>HIGH</sub> = -4.0mA | 2.4                        |      |                           | V     |  |

| Low-Level Output Voltage                               | V <sub>OL</sub>    | I <sub>LOW</sub> = 8.0mA   |                            |      | 0.4                       | V     |  |

| High-Level Output Voltage:<br>GPIO Clock Pad           | V <sub>OHG</sub>   | I <sub>HIGH</sub> = -8.0mA | 2.4                        |      |                           | V     |  |

| Output Low Voltage GPIO                                | V <sub>OLG</sub>   | I <sub>LOW</sub> = 8.0mA   |                            |      | 0.4                       | V     |  |

| Input High Voltage<br>(Port0 to Port2)                 | V <sub>IH1</sub>   |                            | 0.7 x<br>V <sub>DDIO</sub> |      | 5.5                       | V     |  |

| Input High Voltage (Port3)                             | V <sub>IH2</sub>   |                            | 0.7 x<br>V <sub>DDIO</sub> |      | $V_{DDIO}$                | V     |  |

| Input High Voltage (XTAL1A, XTAL2A, XTAL1S, XTAL2S)    | V <sub>IHXT</sub>  |                            | 0.7 x<br>V <sub>DDC</sub>  |      | $V_{DDC}$                 | V     |  |

| Input Low Voltage                                      | V <sub>IL</sub>    |                            | V <sub>SS</sub>            |      | 0.3 x<br>V <sub>DDC</sub> | V     |  |

| Input Hysteresis                                       | V <sub>IHYS</sub>  |                            | 0.2                        | 0.5  |                           | V     |  |

| Input Leakage Current                                  | lı                 | Internal pullup disabled   | -100                       |      | +100                      | μA    |  |

| GPIO Pullup Resistance                                 | R <sub>PU</sub>    | Internal pullup enabled    |                            | 80   |                           | kΩ    |  |

| GFIO Fullup Resistance                                 | R <sub>PU3</sub>   |                            |                            | 40   |                           | KZZ   |  |

| V <sub>DDIO</sub> Supply Current                       | I <sub>DDIO</sub>  |                            |                            |      | 35                        | mA    |  |

| V <sub>DDC</sub> Supply Current                        | I <sub>DDC</sub>   |                            |                            |      | 80                        | mA    |  |

| Idle Mode Current                                      | I <sub>IDLE</sub>  | No peripherals running     |                            | 5    |                           | mA    |  |

| Ston Mode Current                                      | I <sub>STOP1</sub> | Power monitor on           |                            | 0.5  |                           | mΛ    |  |

| Stop Mode Current                                      | I <sub>STOP2</sub> | Power monitor off          | 0.25                       |      |                           | - mA  |  |

| V <sub>DDC</sub> /AV <sub>DD</sub> Brownout Trip Point | V <sub>RSTC</sub>  |                            | 1.62                       |      | 1.70                      | V     |  |

### **DC Electrical Characteristics (continued)**

$(V_{DDIO}$  = +3.0V to +3.6V,  $V_{DDC}$  = AV $_{DD}$  = +1.62V to +1.98V,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $V_{DDIO}$  = +3.3V,  $V_{DDC}$  = AV $_{DD}$  = +1.8V,  $T_A$  = +25°C.) (Note 2)

| PARAMETER                                             | SYMBOL             | CONDITIONS | MIN  | TYP               | MAX  | UNITS |

|-------------------------------------------------------|--------------------|------------|------|-------------------|------|-------|

| V <sub>DDIO</sub> Brownout Trip Point                 | V <sub>RSTIO</sub> |            | 2.75 |                   | 3.00 | V     |

| V <sub>DDC</sub> /AV <sub>DD</sub> Power-Fail Warning | VDEMO              |            |      | V <sub>RSTC</sub> |      | V     |

| Level                                                 | VPFWC              |            |      | + 0.04V           |      | V     |

| V <sub>DDIO</sub> Power-Fail Warning Level            | V <sub>PFWIO</sub> |            |      | $V_{RSTIO}$       |      | V     |

| VDDIO I OWEI-I dii Waltiling Level                    | V PFWIO            |            |      | + 0.1V            |      | •     |

#### **AC Electrical Characteristics**

$(V_{DDIO}$  = +3.0V to +3.6V,  $V_{DDC}$  = AV $_{DD}$  = +1.62V to +1.98V,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $V_{DDIO}$  = +3.3V,  $V_{DDC}$  = AV $_{DD}$  = +1.8V,  $T_A$  = +25°C.) (Note 3)

| PARAMETER                                           | SYMBOL                | CONDITIONS | MIN | TYP    | MAX  | UNITS             |

|-----------------------------------------------------|-----------------------|------------|-----|--------|------|-------------------|

| System Clock External Crystal Frequency             | 1/t <sub>CLKS</sub>   |            | 1   |        | 20   | MHz               |

| System Clock External Crystal Frequency—PLL 2x Mode | 1/t <sub>CLKS</sub>   |            | 4.0 |        | 16.5 | MHz               |

| System Clock External Crystal Frequency—PLL 4x Mode | 1/t <sub>CLKS</sub>   |            | 2.0 |        | 8.25 | MHz               |

| System Clock External Clock Frequency               | 1/t <sub>CLKS</sub>   |            | 0   |        | 33   | MHz               |

| System Clock External Clock Frequency—PLL 2x Mode   | 1/t <sub>CLKS</sub>   |            | 4.0 |        | 16.5 | MHz               |

| System Clock External Clock Frequency—PLL 4x Mode   | 1/t <sub>CLKS</sub>   |            | 2.0 |        | 8.25 | MHz               |

| System Clock External Clock Duty Cycle              | 1/t <sub>CLKS</sub> _ |            | 40  |        | 60   | %                 |

| System Clock External Crystal Warmup Delay          | t <sub>ECWS</sub>     |            |     | 65,536 |      | tCLKS             |

| System Clock PLL Warmup Delay                       | t <sub>PLLWS</sub>    |            |     | 65,536 |      | t <sub>CLKS</sub> |

| AFE Clock External Crystal Frequency                | 1/t <sub>CLKA</sub>   |            | 1   |        | 20   | MHz               |

| AFE Clock External Crystal Frequency—PLL 2x Mode    | 1/t <sub>CLKA</sub>   |            | 4   |        | 18   | MHz               |

| AFE Clock External Crystal Frequency—PLL 4x Mode    | 1/t <sub>CLKA</sub>   |            | 2   |        | 9    | MHz               |

| AFE Clock External Clock Frequency                  | 1/t <sub>CLKA</sub>   |            | 0   |        | 36   | MHz               |

| AFE Clock External Clock<br>Frequency—PLL 2x Mode   | 1/t <sub>CLKA</sub>   |            | 4   |        | 18   | MHz               |

| AFE Clock External Clock<br>Frequency—PLL 4x Mode   | 1/t <sub>CLKA</sub>   |            | 2   |        | 9    | MHz               |

### **AC Electrical Characteristics (continued)**

$(V_{DDIO}=+3.0V~to~+3.6V,~V_{DDC}=AV_{DD}=+1.62V~to~+1.98V,~T_{A}=-40^{\circ}C~to~+85^{\circ}C,~unless~otherwise~noted.~Typical~values~are~at~V_{DDIO}=+3.3V,~V_{DDC}=AV_{DD}=+1.8V,~T_{A}=+25^{\circ}C.)~(Note~3)$

| PARAMETER                                       | SYMBOL                              | CONDITIONS                          | MIN                                      | TYP                         | MAX                        | UNITS             |

|-------------------------------------------------|-------------------------------------|-------------------------------------|------------------------------------------|-----------------------------|----------------------------|-------------------|

| AFE Clock External Clock Duty Cycle             | 1/t <sub>CLKA</sub> _<br>DUTY       |                                     | 40                                       |                             | 60                         | %                 |

| AFE Clock External Crystal<br>Warmup Delay      | t <sub>ECWA</sub>                   |                                     |                                          | 65,536                      |                            | t <sub>CLKA</sub> |

| AFE Clock PLL Warmup Delay                      | t <sub>PLLWA</sub>                  |                                     |                                          | 65,536                      |                            | tCLKA             |

| Crystal Tolerance                               |                                     |                                     |                                          | 25                          |                            | ppm               |

| Crystal Input Capacitance                       | C <sub>IN</sub>                     |                                     |                                          | 6                           |                            | pF                |

| Output Fall-Time GPIO I <sup>2</sup> C Pad      | t <sub>OF_I2C</sub>                 |                                     | 20 + 0.1<br>x C <sub>L</sub>             |                             | 250                        | ns                |

| RTC Crystal Frequency                           | 32KIN                               |                                     |                                          | 32.768                      |                            | kHz               |

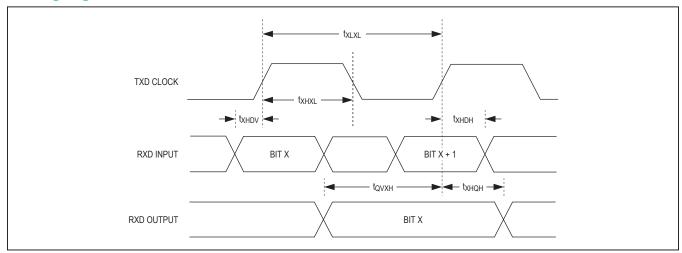

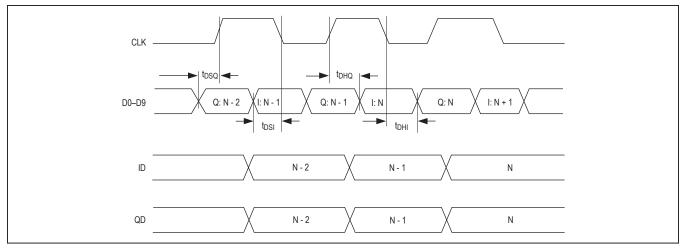

| MCU UART INTERFACE SYNCHI                       | RONOUS MO                           | DE (Note 4) (Figure 1)              |                                          |                             |                            |                   |

| TXD Clock Period                                | t <sub>XLXL</sub>                   | SM2 = 0                             |                                          | 12 x<br>t <sub>CLKS</sub>   |                            | ns                |

| TAD GIOGRA CHOU                                 | 'XLXL                               | SM2 = 1                             |                                          | 4 x<br>t <sub>CLKS</sub>    |                            | 113               |

| TVD Clock High Time                             |                                     | SM2 = 0                             |                                          | 3 x<br>t <sub>CLKS</sub>    |                            |                   |

| TXD Clock High Time                             | txHXL                               | SM2 = 1                             |                                          | 2 x<br>t <sub>CLKS</sub>    |                            | ns                |

| RXD Output Valid to TXD Clock                   | tovou                               | SM2 = 0                             | to                                       | 10 x<br>CLKS - 10           |                            | ns                |

| Rising Edge                                     | <sup>t</sup> QVXH                   | SM2 = 1                             | to                                       | 3 x<br><sub>CLKS</sub> - 10 |                            | 115               |

| RXD Output Data Hold from TXD                   | tymou                               | SM2 = 0                             | to                                       | 2 x<br><sub>CLKS</sub> - 10 |                            | ns                |

| Clock Rising Edge                               | <sup>t</sup> XHQH                   | SM2 = 1                             |                                          | t <sub>CLKS</sub><br>- 10   |                            | 113               |

| RXD Input Data Valid to TXD Clock Rising Edge   | t <sub>XHDV</sub>                   | SM2 = 0, SM2 = 1                    | t <sub>CLKS</sub><br>+ 50                |                             |                            | ns                |

| RXD Input Data Hold After TXD Clock Rising Edge | t <sub>XHDH</sub>                   | SM2 = 0<br>SM2 = 1                  |                                          | 0                           |                            | ns                |

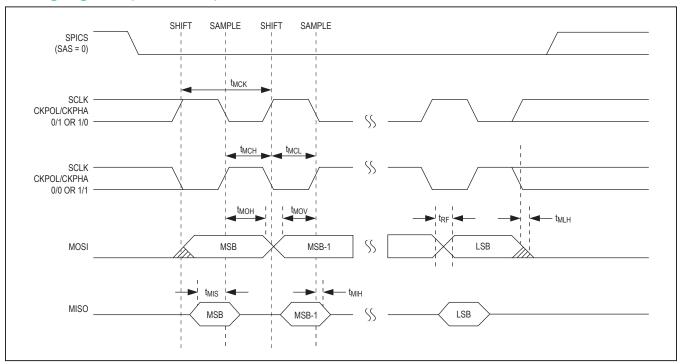

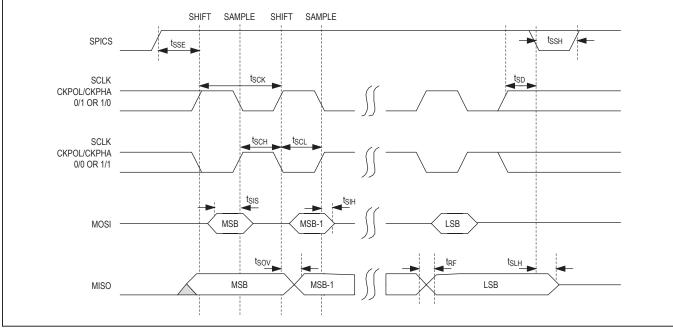

| SPI MASTER (Note 4) (Figure 3)                  |                                     | 1                                   |                                          |                             |                            | <u> </u>          |

| SPI Master Operating Frequency                  | 1/t <sub>MCK</sub>                  |                                     |                                          |                             | 1/2 x<br>t <sub>CLKS</sub> | kHz               |

| I/O Rise/Fall Time                              | t <sub>RF</sub>                     | $C_L = 15pF$ , pullup = $560\Omega$ |                                          |                             | 16                         | ns                |

| SCLK Output Pulse-Width High/<br>Low            | t <sub>MCH</sub> , t <sub>MCL</sub> |                                     | t <sub>MCK</sub> /2<br>- t <sub>RF</sub> |                             |                            | ns                |

### **AC Electrical Characteristics (continued)**

$(V_{DDIO} = +3.0V \ to \ +3.6V, \ V_{DDC} = AV_{DD} = +1.62V \ to \ +1.98V, \ T_A = -40^{\circ}C \ to \ +85^{\circ}C, \ unless otherwise noted. Typical values are at V_{DDIO} = +3.3V, V_{DDC} = AV_{DD} = +1.8V, T_A = +25^{\circ}C.) \ (Note 3)$

| PARAMETER                                                       | SYMBOL                                   | CONDITIONS                          | MIN                                      | TYP | MAX                                           | UNITS |

|-----------------------------------------------------------------|------------------------------------------|-------------------------------------|------------------------------------------|-----|-----------------------------------------------|-------|

| MOSI Output Valid to SCLK Sample Edge (MOSI Setup)              | tмон                                     |                                     | t <sub>MCK</sub> /2<br>- t <sub>RF</sub> |     |                                               | ns    |

| MOSI Output Hold After SCLK<br>Last Sample Edge                 | t <sub>MOV</sub>                         |                                     | t <sub>MCK</sub> /2<br>- t <sub>RF</sub> |     |                                               | ns    |

| SCLK Last Sample Edge to MOSI<br>Output Change (MOSI Last Hold) | t <sub>MLH</sub>                         |                                     | t <sub>MCK</sub> /2<br>- t <sub>RF</sub> |     |                                               | ns    |

| MISO Input Valid to SCLK Sample Edge (MISO Setup)               | t <sub>MIS</sub>                         |                                     | 40                                       |     |                                               | ns    |

| MISO Input Hold After SCLK<br>Sample Edge                       | t <sub>MIH</sub>                         |                                     | 0                                        |     |                                               | ns    |

| SPI SLAVE (Note 4) (Figure 4)                                   |                                          |                                     |                                          |     |                                               |       |

| SPI Slave Operating Frequency                                   | 1/t <sub>SCK</sub>                       |                                     |                                          |     | 1/8t <sub>CLKS</sub>                          | kHz   |

| I/O Rise/Fall Time                                              | t <sub>RF</sub>                          | $C_L = 15pF$ , pullup = $560\Omega$ |                                          |     | 16                                            | ns    |

| SCLK Input Pulse-Width High/Low                                 | tsch, tscl                               |                                     | t <sub>SCK</sub> /2<br>- t <sub>RF</sub> |     |                                               | ns    |

| SPICS Active to First Shift Edge                                | t <sub>SSE</sub>                         |                                     | t <sub>RF</sub>                          |     |                                               | ns    |

| MOSI Input to SCLK Sample<br>Edge Rise/Fall Setup               | t <sub>SIS</sub>                         |                                     | t <sub>RF</sub>                          |     |                                               | ns    |

| MOSI Input from SCLK Sample<br>Edge Transition Hold             | tsiH                                     |                                     | t <sub>RF</sub>                          |     |                                               | ns    |

| MISO Output Valid After SCLK<br>Shift Edge Transition           | t <sub>SOV</sub>                         |                                     |                                          |     | 50                                            | ns    |

| SPICS Inactive to Next SPICS<br>Asserted                        | tssh                                     |                                     | tsck +                                   |     |                                               | ns    |

| SCLK Inactive to SPICS<br>Deasserted                            | t <sub>SD</sub>                          |                                     | t <sub>RF</sub>                          |     |                                               | ns    |

| MISO Output Disabled After SPICS Edge Deasserted                | t <sub>SLH</sub>                         |                                     |                                          |     | 2 x t <sub>SCK</sub><br>+ 2 x t <sub>RF</sub> | ns    |

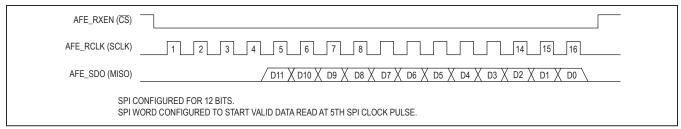

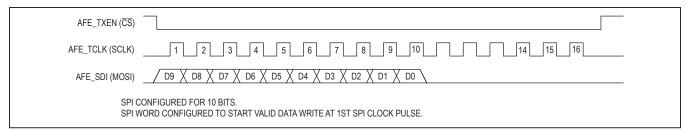

| AFE INTERFACE SERIAL MODE                                       | (Note 5)                                 |                                     |                                          |     |                                               |       |

| AFE Interface Operating Frequency                               | 1/t <sub>TRCK</sub>                      |                                     |                                          |     | t <sub>CLKA</sub>                             | MHz   |

| Clock Rise/Fall Time                                            | t <sub>CRF</sub>                         | C <sub>L</sub> = 20pF               |                                          |     | 6.5                                           | ns    |

| RCLK/TCLK Output Pulse-Width High/Low                           | t <sub>TRCH</sub> ,<br>t <sub>TRCL</sub> |                                     | 0.4 x<br>t <sub>TRCK</sub> /2            |     | 0.6 x<br>t <sub>TRCK</sub> /2                 | ns    |

| SDI Input Setup to RCLK Active Edge                             | t <sub>RIS</sub>                         |                                     | 5                                        |     |                                               | ns    |

| SDI Input Hold After RCLK Active Edge                           | t <sub>RIH</sub>                         |                                     | 0                                        |     |                                               | ns    |

### **AC Electrical Characteristics (continued)**

$(V_{DDIO}=+3.0V~to~+3.6V,~V_{DDC}=AV_{DD}=+1.62V~to~+1.98V,~T_{A}=-40^{\circ}C~to~+85^{\circ}C,~unless~otherwise~noted.~Typical~values~are~at~V_{DDIO}=+3.3V,~V_{DDC}=AV_{DD}=+1.8V,~T_{A}=+25^{\circ}C.)~(Note~3)$

| PARAMETER                                 | SYMBOL                | CONDITIONS                            | MIN                         | TYP                       | MAX                        | UNITS |

|-------------------------------------------|-----------------------|---------------------------------------|-----------------------------|---------------------------|----------------------------|-------|

| RXEN/TXEN Active Level Output Pulse Width | t <sub>TREW</sub>     |                                       | t <sub>TRCK</sub>           |                           |                            | ns    |

| RCLK/TCLK to RXEN/TXEN<br>Active          | t <sub>TRED</sub>     |                                       | 0                           |                           | 10                         | ns    |

| TCLK to SDO Output                        | t <sub>TOD</sub>      |                                       | 0                           |                           | 10                         | ns    |

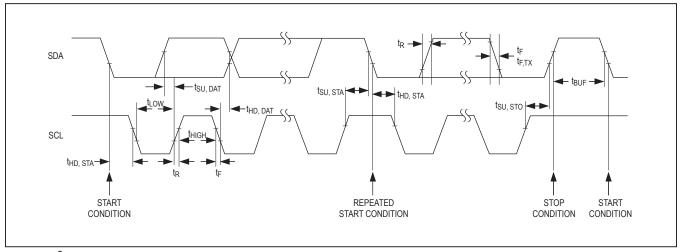

| I <sup>2</sup> C FULL-SPEED TIMING        |                       |                                       |                             |                           |                            |       |

| SCL Clock Frequency                       | f <sub>SCL</sub>      |                                       |                             |                           | 400                        | kHz   |

| Input Low Voltage                         | V <sub>IL_I2C</sub>   |                                       |                             |                           | 0.3 x<br>V <sub>DDIO</sub> | V     |

| Input High Voltage                        | V <sub>IH</sub> _I2C  |                                       | 0.7 x<br>V <sub>DDIO</sub>  |                           |                            | V     |

| Input Hysteresis                          | V <sub>IHYS_I2C</sub> | V <sub>IO</sub> > 2V                  | 0.05 x<br>V <sub>DDIO</sub> |                           |                            | V     |

| SDA Output Logic-Low                      | V <sub>OL_I2C</sub>   | V <sub>L</sub> > 2V, 3mA sink current | 0                           |                           | 0.4                        | V     |

| Input Leakage Current                     | I <sub>IN_I2C</sub>   | 0 < V <sub>IO</sub> < V <sub>L</sub>  | -10                         |                           | +10                        | μΑ    |

| I/O Capacitance                           | C <sub>IO_I2C</sub>   |                                       |                             | 5                         |                            | pF    |

| SDA Output Fall Time                      | t <sub>OF_I2C</sub>   | (Note 6)                              |                             | 20 +<br>0.1C <sub>b</sub> | 250                        | ns    |

| Hold Time After Repeated START            | t <sub>HD,STA</sub>   |                                       | 0.6                         |                           |                            | μs    |

| Clock Low Period                          | t <sub>LOW_I2C</sub>  |                                       | 1.3                         |                           |                            | μs    |

| Clock High Period                         | tHIGH_I2C             |                                       | 0.6                         |                           |                            | μs    |

| Setup Time for Repeated START             | t <sub>SU,STA</sub>   |                                       | 0.6                         |                           |                            | μs    |

| Hold Time for Data                        | t <sub>HD,DAT</sub>   |                                       |                             |                           | 0.9                        | μs    |

| Setup Time for Data                       | t <sub>SU,DAT</sub>   |                                       | 100                         |                           |                            | ns    |

| SDA/SCL Fall Time                         | t <sub>F</sub>        | (Note 6)                              |                             | 20 +<br>0.1C <sub>b</sub> | 300                        | ns    |

| SDA/SCL Rise Time                         | t <sub>R</sub>        | (Note 6)                              |                             | 20 +<br>0.1C <sub>b</sub> | 300                        | ns    |

| Setup Time for STOP                       | tsu,sto               |                                       | 0.6                         |                           |                            | μs    |

| Bus Free Time Between STOP and START      | t <sub>BUF</sub>      |                                       | 1.3                         |                           |                            | μs    |

| Capacitive Load for Each Bus Line         | C <sub>B</sub>        |                                       |                             |                           | 400                        | pF    |

| Pulse Width of Spike Suppressed           | t <sub>SP_I2C</sub>   | (Note 7)                              |                             |                           | 50                         | ns    |

#### **AC Electrical Characteristics (continued)**

$(V_{DDIO}$  = +3.0V to +3.6V,  $V_{DDC}$  = AV $_{DD}$  = +1.62V to +1.98V,  $T_A$  = -40°C to +85°C, unless otherwise noted. Typical values are at  $V_{DDIO}$  = +3.3V,  $V_{DDC}$  = AV $_{DD}$  = +1.8V,  $T_A$  = +25°C.) (Note 3)

| PARAMETER                                                                            | SYMBOL              | CONDITIONS | MIN                        | TYP | MAX | UNITS |

|--------------------------------------------------------------------------------------|---------------------|------------|----------------------------|-----|-----|-------|

| Noise Margin at the Low Level<br>for Each Connected Device<br>(Including Hysteresis) | V <sub>nL_I2C</sub> |            | 0.1 x<br>V <sub>DDIO</sub> |     |     | V     |

| Noise Margin at the High Level for Each Connected Device (Including Hysteresis)      | V <sub>nH_I2C</sub> |            | 0.2 x<br>V <sub>DDIO</sub> |     |     | ٧     |

Note 2: Specifications down to -40°C are guaranteed by design and not production tested.

Note 3: Timing specifications guaranteed by design.

**Note 4:** t<sub>CLKS</sub> refers to the system clock without PLL multiplication.

**Note 5:** t<sub>CLKA</sub> refers to the AFE clock without PLL multiplication.

Note 6:  $I_{SINK} \le 6mA$ ,  $C_B$  = total capacitance of one bus line in pF.  $t_R$  and  $t_F$  are measured between 0.8V and 2.1V.

Note 7: Input filters on the SDA and SCL inputs suppress noise spikes less than 50ns.

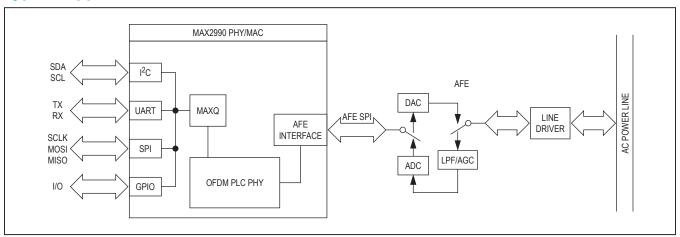

## **Functional Diagram**

## **Pin Description**

| PIN                      | NAME             |                                                | FUNCTION                                                                                                                                                                        |                                                                                                        |                                                                                                                                                                                                                                |  |  |  |  |  |  |

|--------------------------|------------------|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|                          |                  | alternate<br>edge can<br>an output<br>module n | interface<br>be select<br>t, the port<br>nust be co                                                                                                                             | for external interrupts. Eac<br>ed. The default reset cond<br>direction register must be<br>enfigured. | Port0 functions as both an 8-bit I/O port and as an ch interrupt can be individually enabled and the active dition of Port0 is a weak pullup (input). To drive Port0 as programmed to enable outputs or the alternate function |  |  |  |  |  |  |

|                          |                  | Pin                                            | /Port                                                                                                                                                                           | Alternate Function T0A/INT0                                                                            | Alternate Function Description                                                                                                                                                                                                 |  |  |  |  |  |  |

|                          |                  | 2                                              | P0.0<br>P0.1                                                                                                                                                                    | T0A/INT0<br>T0B/INT1                                                                                   | Timer 0 Inout A/External Interrupt 0 Timer 0 Inout B/External Interrupt 1                                                                                                                                                      |  |  |  |  |  |  |

|                          |                  | 3                                              | P0.1                                                                                                                                                                            | T1A/INT2                                                                                               | Timer 1 Inout A/External Interrupt 2                                                                                                                                                                                           |  |  |  |  |  |  |

| 1–4, 10–13               | P0.0-P0.7        | 4                                              | P0.2<br>P0.3                                                                                                                                                                    | T1B/INT3                                                                                               | Timer 1 Inout A/External Interrupt 2 Timer 1 Inout B/External Interrupt 3                                                                                                                                                      |  |  |  |  |  |  |

|                          |                  | 10                                             | P0.3                                                                                                                                                                            | T2A/INT4                                                                                               | Timer 2 Inout A/External Interrupt 4                                                                                                                                                                                           |  |  |  |  |  |  |

|                          |                  | 11                                             | P0.5                                                                                                                                                                            | T2B/AGC0/INT5                                                                                          | Timer 2 Inout A/External Interrupt 4  Timer 2 Inout B/AGC Control Bit 0/ External Interrupt 5                                                                                                                                  |  |  |  |  |  |  |

|                          |                  | 12                                             | P0.6                                                                                                                                                                            | T3A/AGC1/INT6                                                                                          | Timer 3 Inout A/AGC Control Bit 1/<br>External Interrupt 6                                                                                                                                                                     |  |  |  |  |  |  |

|                          |                  | 13                                             | P0.7                                                                                                                                                                            | T3B/AGC2/INT7                                                                                          | Timer 3 Inout B/AGC Freeze or AGC Control Bit 2/External Interrupt 7                                                                                                                                                           |  |  |  |  |  |  |

| 5, 19, 30, 33,<br>53, 58 | DGND             | Digital Gr                                     | ound                                                                                                                                                                            |                                                                                                        |                                                                                                                                                                                                                                |  |  |  |  |  |  |

| 6, 20, 34,<br>54, 59     | V <sub>DDC</sub> | +1.8V Dig                                      |                                                                                                                                                                                 | Supply. Bypass V <sub>DDC</sub> to [                                                                   | DGND with a 0.1µF ceramic capacitor as close as                                                                                                                                                                                |  |  |  |  |  |  |

| 7                        | 32KIN            |                                                | RTC Crystal Oscillator Input. Connect 32KIN to one side of a 32.768kHz crystal and a load capacitor o ground. 32KIN can be configured to be driven by an external clock source. |                                                                                                        |                                                                                                                                                                                                                                |  |  |  |  |  |  |

| 8                        | 32KOUT           |                                                |                                                                                                                                                                                 |                                                                                                        | OUT to the other side of a 32.768kHz crystal and a load ected if 32KIN is driven by an external clock source.                                                                                                                  |  |  |  |  |  |  |

## **Pin Description (continued)**

| PIN              | NAME              |                                          | FUNCTION                                                                                                                                                                                   |                                    |                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|------------------|-------------------|------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 9, 25,<br>39, 56 | V <sub>DDIO</sub> |                                          | out/Output Power Supply. $V_{DDIO}$ is nominally +3.3V and can range from +3.0V to +3.6V. Bypa $_{DDIO}$ to DGND with a 0.1 $\mu$ F ceramic capacitor as close as possible to $V_{DDIO}$ . |                                    |                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 14               | RST               | resistor. R                              | ST also actimer and p                                                                                                                                                                      | ts as an output when the           | ternal active-low input that employs an internal pullup source of the reset is internal to the device, such as a $\overline{8ST}$ is held low while the processor is in a reset state, te.                                                                                                                                                                                        |  |  |  |  |

| 15, 50           | AV <sub>DD</sub>  | +1.8V Ana                                |                                                                                                                                                                                            | Supply. Bypass AV <sub>DD</sub> to | AGND with a 0.1μF ceramic capacitor as close as                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 16, 49           | AGND              | Analog Gr                                | round                                                                                                                                                                                      |                                    |                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 17               | XTAL1S            |                                          |                                                                                                                                                                                            |                                    | AL1S to one side of a parallel resonant crystal and a load ed to be driven by an external clock source.                                                                                                                                                                                                                                                                           |  |  |  |  |

| 18               | XTAL2S            |                                          |                                                                                                                                                                                            |                                    | AL2S to the other side of a parallel resonant crystal and a onnected if XTAL1S is driven by an external clock source.                                                                                                                                                                                                                                                             |  |  |  |  |

| 21–24,<br>26–29  | P1.0–P1.7         | alternate i<br>To drive P<br>alternate f | nterface for                                                                                                                                                                               | r serial protocols. The de         | Port1 functions as both an 8-bit I/O port and as an efault reset condition of Port1 is a weak pullup (input). It register must be programmed to enable outputs or the litto drive the port.  Alternate Function Description  MCU UART Transmit  MCU UART Receive  I <sup>2</sup> C Clock  I <sup>2</sup> C Data  SPI SCLK  SPI Master Out  SPI Master In  SPI Master/Slave Select |  |  |  |  |

| 31               | PROG              | system clo                               | ock cycles of ally sets the                                                                                                                                                                | or until the ready flag is o       | UART bootloader by being held low for at least three detected on TXD. Activating the PROG function egister and initiates an internal reset. Upon code load sternal reset is issued.                                                                                                                                                                                               |  |  |  |  |

| 32               | TDO               | JTAG Dat                                 | a Output                                                                                                                                                                                   |                                    |                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

## **Pin Description (continued)**

| PIN           | NAME        | FUNCTION                        |                                                                                                                                                                                            |                                                                 |                                                                                                                                                                                                                      |  |  |  |

|---------------|-------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|               |             | alternate int                   | terface fo<br>rt2 as an                                                                                                                                                                    | or serial protocols. The                                        | Port2 functions as both an 8-bit I/O port and as an default reset condition of Port2 is a weak pullup (input). On register must be programmed to enable outputs or the ed to drive the port.                         |  |  |  |

|               |             | Pin/P                           | Pin/Port Alternate Function Alternate Function Description                                                                                                                                 |                                                                 |                                                                                                                                                                                                                      |  |  |  |

|               |             | 43                              | P2.0                                                                                                                                                                                       | AFE_GP2/AGC0                                                    | AFE General Purpose 2/AGC Control Bit 0                                                                                                                                                                              |  |  |  |

|               |             | 42                              | P2.1                                                                                                                                                                                       | AFE_GP3/AGC1                                                    | AFE General Purpose 3/AGC Control Bit 1                                                                                                                                                                              |  |  |  |

| i–38,<br>)–43 | P2.7–P2.0   | 41                              | P2.2                                                                                                                                                                                       | AFE_GP4/AGC2                                                    | AFE General Purpose 4/AGC Freeze or AGC Control Bit 2                                                                                                                                                                |  |  |  |

|               |             | 40                              | P2.3                                                                                                                                                                                       | AFE_GP5                                                         | AFE General Purpose 5                                                                                                                                                                                                |  |  |  |

|               |             | 38                              | P2.4                                                                                                                                                                                       | T5A/X1CK                                                        | Timer 5 Inout A/X1 External 3.3V Clock                                                                                                                                                                               |  |  |  |

|               |             | 37                              | P2.5                                                                                                                                                                                       | T5B                                                             | Timer 5 Inout B                                                                                                                                                                                                      |  |  |  |

|               |             | 36                              | P2.6                                                                                                                                                                                       | T4A/T6A/X2CK                                                    | Timer 4 Inout A/Timer 6 Inout A/X2 External 3.3V Clock                                                                                                                                                               |  |  |  |

|               |             | 35                              | P2.7                                                                                                                                                                                       | T4B/T6B                                                         | Timer 4 Inout B/Timer 6 Inout B                                                                                                                                                                                      |  |  |  |

| 44            | TDI         | JTAG Data                       | Input                                                                                                                                                                                      |                                                                 |                                                                                                                                                                                                                      |  |  |  |

| 45            | TMS         | JTAG Mode                       | Select I                                                                                                                                                                                   | nput                                                            |                                                                                                                                                                                                                      |  |  |  |

| 46            | TCK         | JTAG Clock                      | Input                                                                                                                                                                                      |                                                                 |                                                                                                                                                                                                                      |  |  |  |

| 47            | XTAL2A      | ,                               |                                                                                                                                                                                            | •                                                               | 2A to the other side of a parallel resonant crystal and a load cted if XTAL1A is driven by an external clock source.                                                                                                 |  |  |  |

| 48            | XTAL1A      |                                 | AFE Crystal Oscillator Input. Connect XTAL1A to one side of a parallel resonant crystal and a load capacitor to ground. XTAL1A can be configured to be driven by an external clock source. |                                                                 |                                                                                                                                                                                                                      |  |  |  |

|               |             | interface for<br>an output, the | r the AFE<br>he port d<br>st be con                                                                                                                                                        | . The default reset con                                         | Port3 functions as both a 9-bit I/O port and as an alternate dition of Port3 is a weak pullup (input). To drive Port3 as e programmed to enable outputs or the alternate function t.  Alternate Function Description |  |  |  |

|               |             | 51                              | P3.0                                                                                                                                                                                       | AFE_TXEN                                                        | AFE Transmit Enable                                                                                                                                                                                                  |  |  |  |

|               |             | 52                              | P3.1                                                                                                                                                                                       | AFE_SDO                                                         | AFE Serial Data Out                                                                                                                                                                                                  |  |  |  |

| 52, 55,       | P3.0-P3.8   | 55                              | P3.2                                                                                                                                                                                       | AFE_TXCLK                                                       | AFE Transmit Clock                                                                                                                                                                                                   |  |  |  |

| 60–64   「     |             |                                 |                                                                                                                                                                                            | <del></del>                                                     |                                                                                                                                                                                                                      |  |  |  |

|               |             | 60                              | P3.4                                                                                                                                                                                       | _                                                               | AFE Serial Data In                                                                                                                                                                                                   |  |  |  |

|               |             | 61                              | P3.5                                                                                                                                                                                       |                                                                 | AFE Receive Enable                                                                                                                                                                                                   |  |  |  |

|               |             | 62                              | P3.6                                                                                                                                                                                       | AFE_RSTN                                                        | AFE Reset                                                                                                                                                                                                            |  |  |  |

|               |             | 63                              | P3.7                                                                                                                                                                                       | _                                                               | AFE General Purpose 1/RXPIN                                                                                                                                                                                          |  |  |  |

|               |             | 64                              | P3.8                                                                                                                                                                                       | <del></del>                                                     | AFE General Purpose 0/TXPIN                                                                                                                                                                                          |  |  |  |

|               | F 3.0-F 3.0 | 61<br>62<br>63                  | P3.5<br>P3.6<br>P3.7                                                                                                                                                                       | AFE_RXCLK AFE_SDI AFE_RXEN AFE_RSTN AFE_GP1/RXPIN AFE_GP0/TXPIN | AFE Receive Enable AFE Reset AFE General Purpose 1/RXPIN                                                                                                                                                             |  |  |  |

<sup>\*</sup>Note: Type-D ports are capable of interrupts while type-C ports are not.

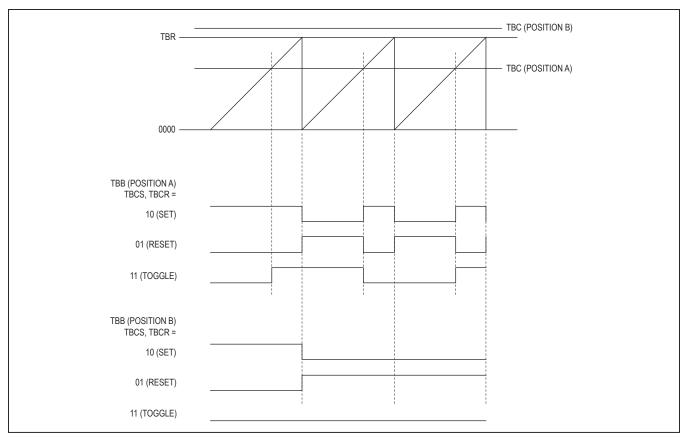

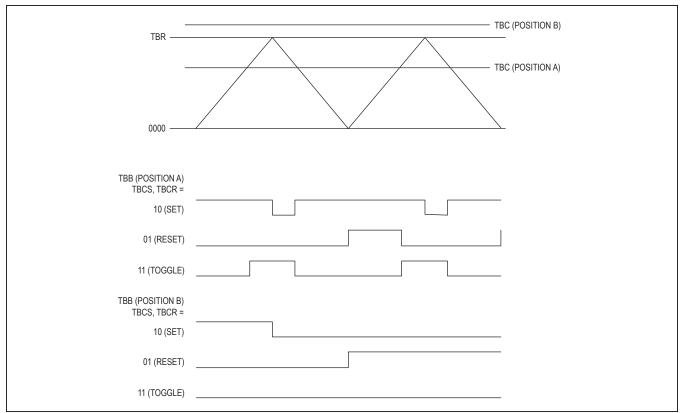

## **Timing Figures**

Figure 1. UART Timing Diagram for Synchronous Mode (Mode 0)

Figure 2. I<sup>2</sup>C Timing Diagram

## **Timing Figures (continued)**

Figure 3. SPI Master Timing Diagram

Figure 4. SPI Slave Timing Diagram

#### **Detailed Description**

The MAX2990 is an integrated SoC power line modem that utilizes advance modulation techniques for PLC. The MAX2990 enables robust data communication using the existing electrical wires, reducing the need for external cables for interconnections between nodes in a network.

The MAX2990 features a modem solution based on OFDM and the high-performance MAXQ microcontroller core. The MAX2990 encodes data at various carrier frequencies from 10kHz to 490kHz and uses advanced OFDM modulation techniques to send multiplexed data over the power line for overall high data throughput of 100kbps. The MAXQ core is a fully static CMOS, 16-bit RISC microcontroller with 32kB flash memory, 5.12kB of ROM, and 8kB of SRAM, of which 4kB can be simultaneously accessed by the internal microprocessor and the PHY. The MAXQ is integrated with modules for serial communication (SPI, I<sup>2</sup>C, and UART) and RTC for time stamping, in addition to standard blocks such as timers for PWM, GPIO, and external interrupts.

The MAX2990 MAC features 48-bit and 16-bit addressing and organizes data into packets before transmission. The MAX2990 uses various registers for precise control over the PHY layer.

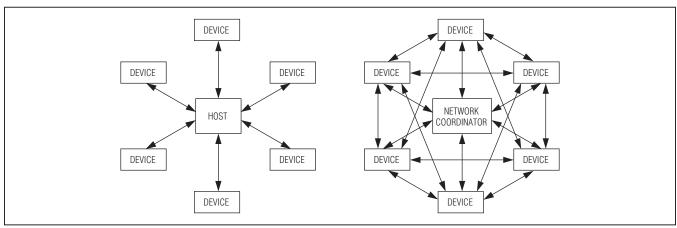

The MAX2990 automatically senses for collisions before it transmits over the power line. If multiple devices are connected in a star topology, collisions are not a problem. However, when multiple devices communicate to each other, collision avoidance becomes a primary issue. In peer-to-peer networks, it is possible for concurrent transmissions by multiple nodes to result in frame collisions. The multiple transmissions interfere with each other; therefore, all data is garbled and receivers are unable to

distinguish the overlapping received signals from each other (Figure 5).

The MAX2990 features a carrier sense multiple access/collision avoidance (CSMA/CA) scheme that prevents collisions. If the channel is not clear, the node waits for a randomly chosen period of time and then checks again to see if the channel is clear. The MAX2990 accepts data from the user at any time, but transmits over the power line in accordance with CSMA/CA. The automatic repeat request (ARQ) feature improves data reliability by requesting packets with errors be retransmitted. The MAX2990 features a programmable ARQ that automatically detects and resends unsuccessful transmission packets without any user interface.

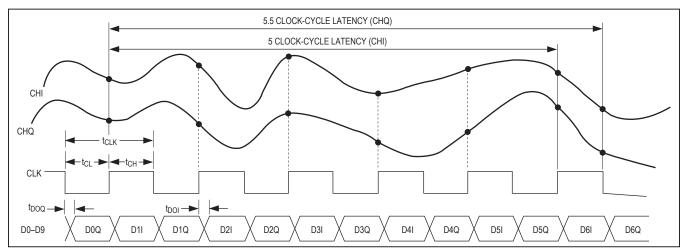

## Orthogonal Frequency-Division Multiplexing (OFDM) Technique

The power line channel is a hostile environment. Channel characteristics and parameters vary with frequency, location, time, and the type of equipment connected. The lower frequency regions from 10kHz to 490kHz are especially susceptible to interference. Furthermore, the power line is a frequency selective channel. Besides background noise, it is subject to impulsive noise often occurring at 50/60Hz, narrowband interference, and group delays up to several hundred microseconds.

OFDM is a modulation technique that can utilize the allowed bandwidth for CENELEC, ARIB, and FCC bands very efficiently, allowing the use of advanced channel coding techniques. This combination enables a very robust power line communication in the presence of narrowband interference, impulsive noise, and frequency selective attenuation.

Figure 5. Carrier Sense Multiple Access/Collision Avoidance

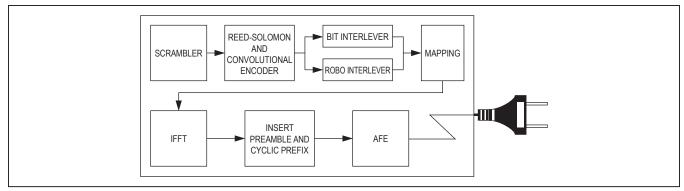

Figure 6. OFDM Transmit Path

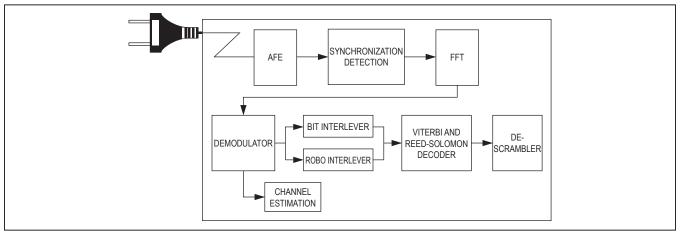

Figure 7. OFDM Receive Path

The approach shown in Figure 6 divides a user-defined bandwidth (such as CENELEC, FCC, or ARIB) into a number of subchannels that can be viewed as many independent BPSK modulated carriers with different non-interfering carrier frequencies.

Convolutional and Reed-Solomon coding provide redundancy bits. This allows the receiver to recover any lost or corrupted bits caused by background and impulsive noise. A time-frequency interleaving scheme is used to decrease the correlation of received noise at the input of the decoder.

Multicarrier signals are generated by performing IFFT on the complex-valued signal points produced by differentially encoded phase/amplitude modulation allocated into the individual subcarrier.

An OFDM symbol is built by appending a cyclic prefix to the beginning of each block generated by IFFT. The length of cyclic prefix, which is programmable from the MAC layer, is chosen so that a channel group delay does not cause successive OFDM-symbols or adjacent subcarriers to

interfere. The start of the data frame carries multiple preamble symbols that contain the synchronization sequence. A synchronizer at the receiving end detects the sequences that indicate the beginning of the data frame (Figure 7).

Blind channel estimator technique is used to monitor the channel variation for each data frame. If a severe change in the power line channel condition occurs, the channel estimator switches the OFDM system into robust mode. In robust mode, data is repeated several times and includes convolutional coding and the Reed-Solomon encoder. In normal mode, the MAX2990 PLC modem can communicate up to 32kbps at 4dB SNR with a bit error rate of approximately 10-9 in the CENELEC A band. In robust mode, the system can provide an additional 5dB improvement.

#### **Modes of Operation**

In autoconfiguration, the MAX2990 operates in both normal and robust modes. In the robust mode, an extra encoder is used after the convolutional coder and repeats the bits several times.

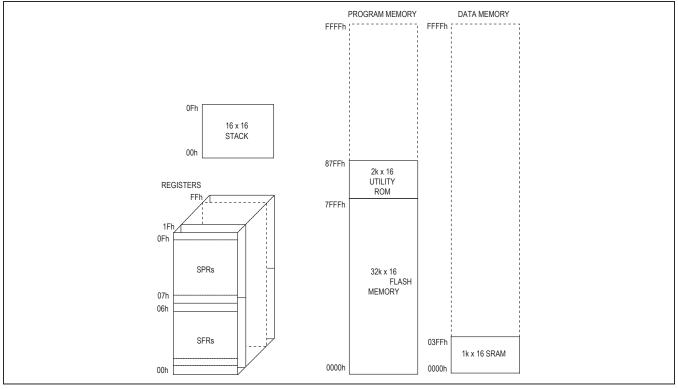

Figure 8. Memory Map

The MAC layer switches the mode of operation based on the channel estimation block output values. The channel estimation block estimates the SNR, input level fluctuations and potential in-band tone reductions. As input signal variation exceeds the predefined thresholds, the MAC layer switches the mode to either normal or robust.

#### **Programmable Bandwidth Selection**

The MAX2990 can operate in CENELEC, FCC, and ARIB bands capable of transmitting data from 10kHz to 490kHz frequency bands; however, in the wideband mode, the start and end frequencies are programmable through the registers. For example, the MAX2990 can be configured to establish data communication in the 95kHz to 190kHz frequency range. For best performance, it is recommended to select the frequency band that covers a minimum of 12 tones.

#### **ACK Signal**

The ACK signal is used when an acknowledgement is required to confirm whether data is correctly received. The transmitting unit waits for an acknowledgement during a predefined time span. The reception of the ACK signal is an indication that the data was delivered with no

errors. If the waiting period exceeds the predefined time span and the ACK signal is not received, it indicates that the data was either lost or corrupted.

#### Programmable-Gain Amplifier (PGA)

The MAX2990 has three external outputs that can be used to control an external analog PGA. The purpose of these outputs is to specify the amount of gain needed from the analog PGA to compensate for fluctuations in the received signal levels. The algorithm used calculates the desired gain and outputs it as a 3-bit binary value. This module works in tandem with a digital AGC module that is implemented inside the PHY. The analog gain resolution can be programmed to 3dB or 6dB, and provides the MAX2990 with an additional dynamic range of 21dB and 42dB, respectively.

#### **Preemphasis**

The MAX2990 features preemphasis that is a linear equalization method where the transmit signal spectrum is shaped to compensate for amplitude distortion. The purpose of preemphasis is to provide frequency shaping to the transmit signal to compensate for attenuation introduced to the signal as it goes through the power line.

#### MAX2990

## 10kHz to 490kHz OFDM-Based Power Line Communication Modem

#### **Jammer Canceller**

A wide range of narrowband interfering signals are present in the AC power line channel. If these in-band signals are stronger than the OFDM signals, they may result in misdetection or data corruption. The jammer canceller detects the presence of in-band jamming signals and removes them from the OFDM signal.

#### **Data Manager**

The data manager handles the interface between the PHY and MAC. The data manager reduces CPU overhead by automating packet transfer to and from the PHY, automating encryption and decryption, CRC32 processing of packet data, and performing packet filtering without MAC code intervention.

#### **Physical Layer (PHY)**

The MAX2990 features a PLC modem-based solution that encodes and decodes data spanned over 10kHz to 490kHz using advanced OFDM techniques. The multiplexed data has a collective throughput of 100kbps, but each carrier individually transmits at a low data rate for high reliability. The MAX2990 communication is halfduplex.

The MAX2990 PLC modem can operate in normal and robust modes that trade off reliability with speed; detect jammer signals; block jammer signals; check the status of ACKs; and offer automatic gain control, signal-to-noise status, and multiple flags and interrupts for status checks.

The MAX2990 PLC modem has register settings for FCC, CENELEC, and ARIB frequency band compliance. The PLC registers can be programmed according to the compliance and coding required.

#### Data Encryption Standard (DES)/ Cyclic Redundancy Check (CRC32)

The MAX2990 ensures privacy through DES encryption and error checking through CRC32. The MAX2990 has registers for control over the DES and CRC32. DES and CRC32 can be enabled independently. The MAX2990 stores its 64-bit key, which can be changed to any key. When CRC32 is enabled, the 32-bit checksum is appended at the end of the packet before encryption.

#### **Memory Organization**

The MAX2990 incorporates several memory areas:

- 512kB utility ROM

- 32kB flash memory for program storage

- · 4kB of SRAM for storage of temporary variables

- 4kB dual-port SRAM for packet buffering

- 16-level memory stack for storage of program return addresses and general-purpose use

The MAX2990 uses Harvard architecture for access of system memory, with separate address spaces for program and data memory. This allows overlapping addresses in program and data memory since they are accessed in different ways. The MAX2990 supports pseudo Von Neumann memory structure, which can merge program and data into a linear memory map. This is accomplished by logically mapping the data memory into the program space or logically mapping program memory segment into the data space.

The incorporation of flash memory as the main program memory allows the MAX2990 to be reprogrammed, eliminating the expense of throwing away one-time programmable devices during development and field upgrades. Flash memory can be password protected with a 32-byte key, denying access to program memory by unauthorized individuals.

#### **Stack Memory**

A 16-bit-wide, 16-word deep internal stack provides storage for program return addresses and general-purpose use. The stack is used automatically by the processor when the CALL, RET, and RETI instructions are executed and interrupts serviced. The stack can also be used explicitly to store and retrieve data by using the PUSH, POP, and POPI instructions.

On reset, the stack pointer (SP) initializes to the top of the stack (0Fh). The CALL, PUSH, and interrupt-vectoring operations increment SP, then store a value at the location pointed to by SP. The RET, RETI, POP, and POPI operations retrieve the value at SP and then decrement SP.

#### **Utility ROM**

The utility ROM supports the following functions:

- Flash ISP loader to load program from JTAG and serial port

- User-callable flash API routines

- · User-callable table lookup routines

- JTAG debugger support

#### **Protected Access**