## Fast Settling, JFET Input Operational Amplifier

## **FEATURES**

| 100% Tested Settling Time             |            | 340ns Typ |

|---------------------------------------|------------|-----------|

| to 1mV at Sum Node, 10V S             | 540ns Max  |           |

| Tested with Fixed Feedback            | Capacitor  |           |

| Slew Rate                             | 60V/µs Min |           |

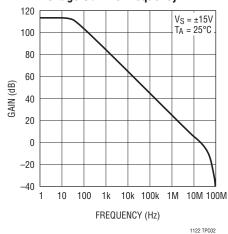

| Gain-Bandwidth Product                |            | 14MHz     |

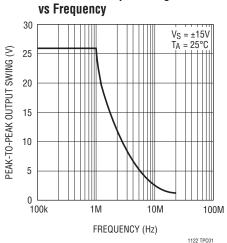

| Power Bandwidth (20V <sub>P-P</sub> ) | 1.2 MHz    |           |

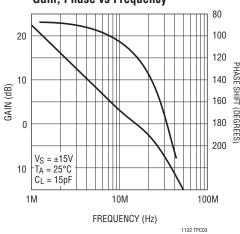

| Unity-Gain Stable; Phase Ma           | 60°        |           |

| Input Offset Voltage                  |            | 600µV Max |

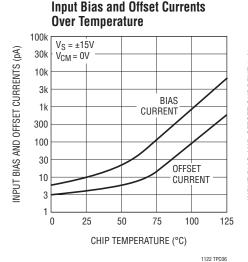

| Input Bias Current                    | 25°C       | 75pA Max  |

|                                       | 70°C       | 600pA Max |

| Input Offset Current                  | 25°C       | 40pA Max  |

|                                       | 70°C       | 150pA Max |

|                                       |            |           |

Low Distortion

## **APPLICATIONS**

- Fast 12-Bit D/A Output Amplifiers

- High Speed Buffers

- Fast Sample-and-Hold Amplifiers

- High Speed Integrators

- Voltage to Frequency Converters

- Active Filters

- Log Amplifiers

- Peak Detectors

## DESCRIPTION

The LT®1122 JFET input operational amplifier combines high speed and precision performance.

A unique poly-gate JFET process minimizes gate series resistance and gate-to-drain capacitance, facilitating wide bandwidth performance, without degrading JFET transistor matching.

It slews at 80V/µs and settles in 340ns. The LT1122 is internally compensated to be unity-gain stable, yet it has a bandwidth of 14MHz at a supply current of only 7mA. Its speed makes the LT1122 an ideal choice for fast settling 12-bit data conversion and acquisition systems.

The LT1122 offset voltage of  $120\mu V$ , and voltage gain of 500,000 also support the 12-bit accurate applications.

The input bias current of 10pA and offset current of 4pA combined with its speed allow the LT1122 to be used in such applications as high speed sample and hold amplifiers, peak detectors, and integrators.

## TYPICAL APPLICATION

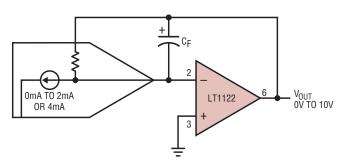

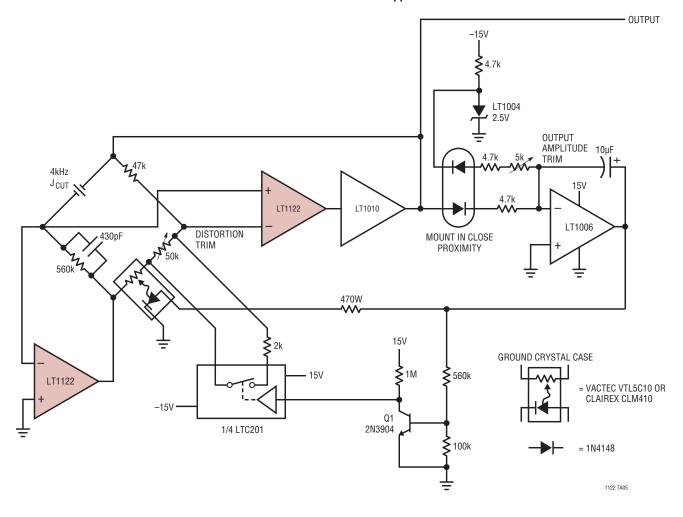

#### 12-Bit Voltage Output D/A Converter

12-BIT CURRENT OUTPUT D/A CONVERTER C<sub>F</sub> = 5pF TO 17pF (DEPENDING ON D/A CONVERTER USED)

LT1122•TA01

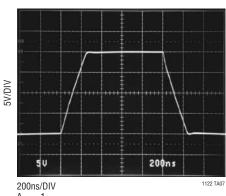

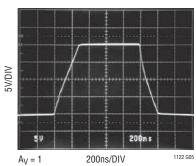

#### Large-Scale Response

<sup>(</sup>LT), LTC, LTM, Linear Technology and the Linear logo are registered trademarks and C-Load is a trademark of Linear Technology Corporation. All other trademarks are the property of their respective owners.

## **ABSOLUTE MAXIMUM RATINGS** (Note 1)

| Supply Voltage                        | ±20V       |

|---------------------------------------|------------|

| Differential Input Voltage            | ±40V       |

| Input Voltage                         | ±20V       |

| Output Short Circuit Duration         | Indefinite |

| Lead Temperature (Soldering, 10 sec.) | 300°C      |

Operating Temperature Range

LT1122AM/BM/CM/DM (OBSOLETE).. -55°C to 125°C

LT1122AC/BC/CC/DC/CS/DS.....-40°C to 85°C

Storage Temperature Range

All Devices......-65°C to 150°C

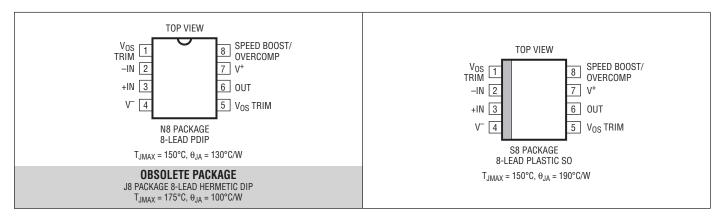

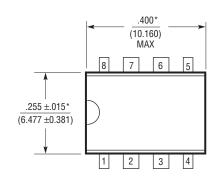

## PIN CONFIGURATION

## ORDER INFORMATION

| LEAD FREE FINISH | TAPE AND REEL    | PART MARKING | PACKAGE DESCRIPTION | TEMPERATURE RANGE |  |  |  |  |

|------------------|------------------|--------------|---------------------|-------------------|--|--|--|--|

| LT1122ACN8#PBF   | LT1122ACN8#TRPBF | LT1122ACN8   | 8-Lead Plastic DIP  | -40°C to 85°C     |  |  |  |  |

| LT1122BCN8#PBF   | LT1122BCN8#TRPBF | LT1122BCN8   | 8-Lead Plastic DIP  | -40°C to 85°C     |  |  |  |  |

| LT1122CCN8#PBF   | LT1122CCN8#TRPBF | LT1122CCN8   | 8-Lead Plastic DIP  | -40°C to 85°C     |  |  |  |  |

| LT1122DCN8#PBF   | LT1122DCN8#TRPBF | LT1122DCN8   | 8-Lead Plastic DIP  | -40°C to 85°C     |  |  |  |  |

| LT1122CS8#PBF    | LT1122CS8#TRPBF  | 1122C        | 8-Lead Plastic SO   | -40°C to 85°C     |  |  |  |  |

| LT1122DS8#PBF    | LT1122DS8#TRPBF  | 1122D        | 8-Lead Plastic SO   | -40°C to 85°C     |  |  |  |  |

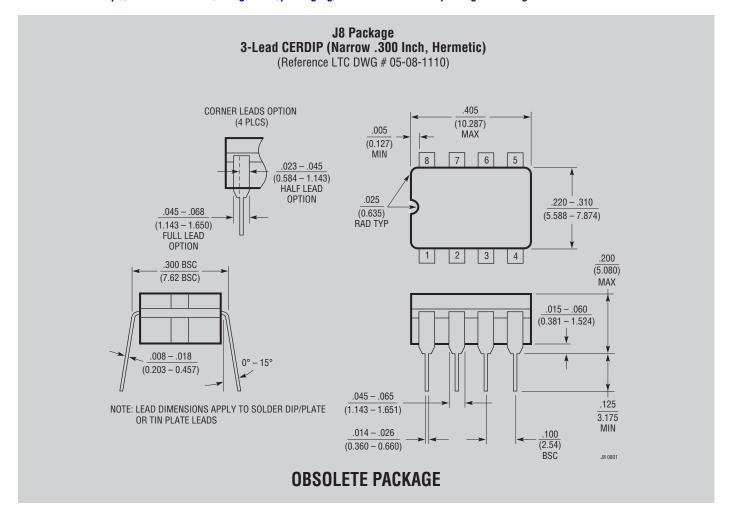

|                  | OBSOLETE PACKAGE |              |                     |                   |  |  |  |  |

| LT1122AMJ8#PBF   | LT1122AMJ8#TRPBF | LT1122AMJ8   | 8-Lead Hermetic DIP | -55°C to 125°C    |  |  |  |  |

| LT1122BMJ8#PBF   | LT1122BMJ8#TRPBF | LT1122BMJ8   | 8-Lead Hermetic DIP | −55°C to 125°C    |  |  |  |  |

| LT1122CMJ8#PBF   | LT1122CMJ8#TRPBF | LT1122CMJ8   | 8-Lead Hermetic DIP | -55°C to 125°C    |  |  |  |  |

| LT1122DMJ8#PBF   | LT1122DMJ8#TRPBF | LT1122DMJ8   | 8-Lead Hermetic DIP | −55°C to 125°C    |  |  |  |  |

| LT1122ACJ8#PBF   | LT1122ACJ8#TRPBF | LT1122ACJ8   | 8-Lead Hermetic DIP | -40°C to 85°C     |  |  |  |  |

| LT1122BCJ8#PBF   | LT1122BCJ8#TRPBF | LT1122BCJ8   | 8-Lead Hermetic DIP | -40°C to 85°C     |  |  |  |  |

| LT1122CCJ8#PBF   | LT1122CCJ8#TRPBF | LT1122CCJ8   | 8-Lead Hermetic DIP | -40°C to 85°C     |  |  |  |  |

| LT1122DCJ8#PBF   | LT1122DCJ8#TRPBF | LT1122DCJ8   | 8-Lead Hermetic DIP | -40°C to 85°C     |  |  |  |  |

Consult LTC Marketing for parts specified with wider operating temperature ranges. Consult LTC Marketing for information on nonstandard lead based finish parts.

For more information on lead free part markings, go to: http://www.linear.com/leadfree/ For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25\,^{\circ}\text{C}$ . $V_S = \pm 15\text{V}$ , $V_{CM} = 0\text{V}$ unless otherwise noted. (Note 2)

| SYMBOL           | PARAMETER                                       | CONDITIONS                                                                                                                                        |              | 122AM,<br>1122AC,<br>TYP                                 |     | LT <sup>-</sup> | 122CM/<br>1122CC/<br>1122CS/<br>TYP                      | /DC | UNITS             |

|------------------|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------------------------------------------------|-----|-----------------|----------------------------------------------------------|-----|-------------------|

| V <sub>OS</sub>  | Input Offset Voltage                            | ONDITIONS                                                                                                                                         |              | 120                                                      | 600 | """             | 130                                                      | 900 | μV                |

| I <sub>0S</sub>  | Input Offset Current                            |                                                                                                                                                   |              | 4                                                        | 40  |                 | 5                                                        | 50  | pA                |

| I <sub>B</sub>   | Input Bias Current                              |                                                                                                                                                   |              | 10                                                       | 75  |                 | 12                                                       | 100 | pA                |

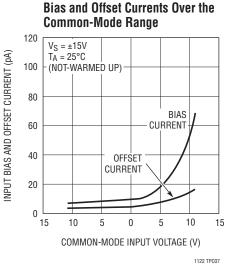

| <u> </u>         | Input Resistance<br>Differential<br>Common Mode | V <sub>CM</sub> = -10V to 8V<br>V <sub>CM</sub> = 8V to 11V                                                                                       |              | 10 <sup>12</sup><br>10 <sup>12</sup><br>10 <sup>11</sup> |     |                 | 10 <sup>12</sup><br>10 <sup>12</sup><br>10 <sup>11</sup> |     | Ω<br>Ω<br>Ω       |

|                  | Input Capacitance                               |                                                                                                                                                   |              | 4                                                        |     |                 | 4                                                        |     | pF                |

| SR               | Slew Rate                                       | $A_V = -1$                                                                                                                                        | 60           | 80                                                       |     | 50              | 75                                                       |     | V/µs              |

|                  | Settling Time (Note 2)                          | 10V to 0V, -10V to 0V<br>100% Tested: A- and C-Grades to 1mV at Sum Node<br>B- and D-Grades to 1mV at Sum Node<br>All Grades to 0.5mV at Sum Node |              | 340<br>350<br>450                                        | 540 |                 | 350<br>360<br>470                                        | 590 | ns<br>ns<br>ns    |

| GBW              | Gain-Bandwidth Product Power Bandwidth          | V <sub>OUT</sub> = 20V <sub>P-P</sub>                                                                                                             |              | 14<br>1.2                                                |     |                 | 13<br>1.1                                                |     | MHz<br>MHz        |

| A <sub>VOL</sub> | Large-Signal Voltage Gain                       | $\begin{aligned} V_{OUT} &= \pm 10 \text{V},  R_L = 2 \text{k} \Omega \\ V_{OUT} &= \pm 10 \text{V},  R_L = 600 \Omega \end{aligned}$             | 180<br>130   | 500<br>250                                               |     | 150<br>110      | 450<br>220                                               |     | V/mV<br>V/mV      |

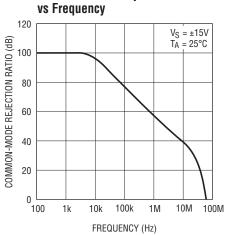

| CMRR             | Common-Mode Rejection Ratio                     | V <sub>CM</sub> = ±10V                                                                                                                            | 83           | 99                                                       |     | 80              | 98                                                       |     | dB                |

|                  | Input Voltage Range                             | (Note 4)                                                                                                                                          | ±10.5        | ±11                                                      |     | ±10.5           | ±11                                                      |     | V                 |

| PSRR             | Power Supply Rejection Ratio                    | $V_S = \pm 10V \text{ to } \pm 18V$                                                                                                               | 86           | 103                                                      |     | 82              | 101                                                      |     | dB                |

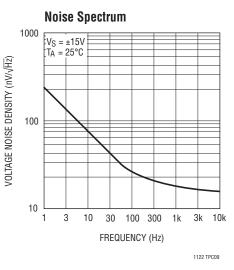

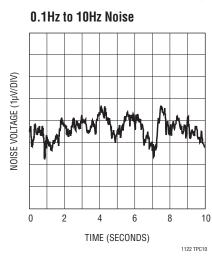

|                  | Input Noise Voltage                             | 0.1Hz to 10Hz                                                                                                                                     |              | 3.0                                                      |     |                 | 3.3                                                      |     | μV <sub>P-P</sub> |

|                  | Input Noise Voltage Density                     | $f_0 = 100$ Hz<br>$f_0 = 10$ kHz                                                                                                                  |              | 25<br>14                                                 |     |                 | 27<br>15                                                 |     | nV/√Hz<br>nV/√Hz  |

|                  | Input Noise Current Density                     | $f_0 = 100$ Hz, $f_0 = 10$ kHz                                                                                                                    |              | 2                                                        |     |                 | 2                                                        |     | fA/√Hz            |

| V <sub>OUT</sub> | Output Voltage Swing                            | $R_L = 2k\Omega$ $R_L = 600\Omega$                                                                                                                | ±12<br>±11.5 | ±12.5<br>±12                                             |     | ±12<br>±11.5    | ±12.5<br>±12                                             |     | V                 |

| Is               | Supply Current                                  |                                                                                                                                                   |              | 7.5                                                      | 10  |                 | 7.8                                                      | 11  | mA                |

|                  | Minimum Supply Voltage                          | (Note 5)                                                                                                                                          | ±5           |                                                          |     | ±5              |                                                          |     | V                 |

|                  | Offset Adjustment Range                         | R <sub>POT</sub> ≥ 10k, Wiper to V <sup>+</sup>                                                                                                   | ±4           | ±10                                                      |     | ±4              | ±10                                                      |     | mV                |

# **ELECTRICAL CHARACTERISTICS** The ullet denotes the specifications which apply over the full operating temperature range, otherwise specifications are at 0°C $\leq$ T<sub>A</sub> $\leq$ 70°C. V<sub>S</sub> = $\pm$ 15V, V<sub>CM</sub> = 0V. (Note 2)

|                  |                                                            |                                       |   | LT    | 1122AC/ | ВС   |       | 1122CC/<br>1122CS/ | -    |       |

|------------------|------------------------------------------------------------|---------------------------------------|---|-------|---------|------|-------|--------------------|------|-------|

| SYMBOL           | PARAMETER                                                  | CONDITIONS                            |   | MIN   | TYP     | MAX  | MIN   | TYP                | MAX  | UNITS |

| $V_{0S}$         | Input Offset Voltage                                       |                                       | • |       | 350     | 1400 |       | 400                | 2000 | μV    |

|                  | Average Temperature Coefficient of<br>Input Offset Voltage |                                       | • |       | 5       | 18   |       | 6                  | 25   | μV/°C |

| I <sub>OS</sub>  | Input Offset Current                                       |                                       | • |       | 12      | 150  |       | 15                 | 200  | pA    |

| IB               | Input Bias Current                                         |                                       | • |       | 80      | 600  |       | 90                 | 800  | pA    |

| A <sub>VOL</sub> | Large-Signal Voltage Gain                                  | $V_{OUT} = \pm 10V, R_L \ge 2k\Omega$ | • | 120   | 380     |      | 100   | 340                |      | V/mV  |

| CMRR             | Common-Mode Rejection Ratio                                | V <sub>CM</sub> = ±10V                | • | 82    | 98      |      | 78    | 96                 |      | dB    |

| PSRR             | Power Supply Rejection Ratio                               | V <sub>S</sub> = ±10V to ±17V         | • | 84    | 101     |      | 80    | 99                 |      | dB    |

|                  | Input Voltage Range                                        |                                       | • | ±10   | ±10.8   |      | ±10   | ±10.8              |      | V     |

| V <sub>OUT</sub> | Output Voltage Swing                                       | $R_L = 2k\Omega$                      | • | ±11.5 | ±12.4   |      | ±11.5 | ±12.4              |      | V     |

| SR               | Slew Rate                                                  | A <sub>V</sub> = -1                   | • | 50    | 70      |      | 40    | 65                 |      | V/µs  |

# The ullet denotes the specifications which apply over the full operating temperature range, otherwise specifications are at -55°C $\leq$ T<sub>A</sub> $\leq$ 125°C. V<sub>S</sub> = ±15V, V<sub>CM</sub> = 0V. (Note 2)

|                  |                                                         |                                       |   | LT*   | 1122AM/ | BM   | LT    | 1122CS/ | DS   |       |

|------------------|---------------------------------------------------------|---------------------------------------|---|-------|---------|------|-------|---------|------|-------|

| SYMBOL           | PARAMETER                                               | CONDITIONS                            |   | MIN   | TYP     | MAX  | MIN   | TYP     | MAX  | UNITS |

| V <sub>OS</sub>  | Input Offset Voltage                                    |                                       | • |       | 650     | 2400 |       | 800     | 3400 | μV    |

|                  | Average Temperature Coefficient of Input Offset Voltage |                                       | • |       | 6       | 18   |       | 7       | 25   | μV/°C |

| I <sub>OS</sub>  | Input Offset Current                                    |                                       | • |       | 0.5     | 6    |       | 0.6     | 9    | nA    |

| I <sub>B</sub>   | Input Bias Current                                      |                                       | • |       | 6       | 25   |       | 7       | 35   | nA    |

| A <sub>VOL</sub> | Large-Signal Voltage Gain                               | $V_{OUT} = \pm 10V, R_L \ge 2k\Omega$ | • | 70    | 230     |      | 60    | 200     |      | V/mV  |

| CMRR             | Common-Mode Rejection Ratio                             | V <sub>CM</sub> = ±10V                | • | 80    | 97      |      | 76    | 94      |      | dB    |

| PSRR             | Power Supply Rejection Ratio                            | $V_S = \pm 10V \text{ to } \pm 17V$   | • | 83    | 100     |      | 78    | 98      |      | dB    |

|                  | Input Voltage Range                                     |                                       | • | ±10   | ±10.5   |      | ±10   | ±10.5   |      | V     |

| V <sub>OUT</sub> | Output Voltage Swing                                    | $R_L = 2k\Omega$                      | • | ±11.3 | ±12.1   |      | ±11.3 | ±12.1   |      | V     |

| SR               | Slew Rate                                               | A <sub>V</sub> = -1                   | • | 45    | 60      |      | 35    | 55      |      | V/µs  |

# The ullet denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $-40^{\circ}C \leq T_A \leq 85^{\circ}C$ . $V_S = \pm 15V$ , $V_{CM} = 0V$ . (Note 6)

|                     |                                                         |                                       |   | LT.   | 1122AM/ | BM   | LT    | 1122CS/ | DS   |       |

|---------------------|---------------------------------------------------------|---------------------------------------|---|-------|---------|------|-------|---------|------|-------|

| SYMBOL              | PARAMETER                                               | CONDITIONS                            |   | MIN   | TYP     | MAX  | MIN   | TYP     | MAX  | UNITS |

| $\overline{V_{OS}}$ | Input Offset Voltage                                    |                                       | • |       | 450     | 1900 |       | 500     | 2700 | μV    |

|                     | Average Temperature Coefficient of Input Offset Voltage |                                       | • |       | 6       | 20   |       | 7       | 28   | μV/°C |

| I <sub>OS</sub>     | Input Offset Current                                    |                                       | • |       | 30      | 600  |       | 40      | 900  | pA    |

| I <sub>B</sub>      | Input Bias Current                                      |                                       | • |       | 230     | 2000 |       | 260     | 2700 | pA    |

| A <sub>VOL</sub>    | Large-Signal Voltage Gain                               | $V_{OUT} = \pm 10V, R_L \ge 2k\Omega$ | • | 95    | 340     |      | 80    | 300     |      | V/mV  |

| CMRR                | Common-Mode Rejection Ratio                             | V <sub>CM</sub> = ±10V                | • | 80    | 98      |      | 76    | 96      |      | dB    |

| PSRR                | Power Supply Rejection Ratio                            | $V_S = \pm 10V \text{ to } \pm 17V$   | • | 83    | 100     |      | 78    | 98      |      | dB    |

|                     | Input Voltage Range                                     |                                       | • | ±10   | ±10.6   |      | ±10   | ±10.6   |      | V     |

| V <sub>OUT</sub>    | Output Voltage Swing                                    | $R_L = 2k\Omega$                      | • | ±11.3 | ±12.2   |      | ±11.3 | ±12.2   |      | V     |

| SR                  | Slew Rate                                               | $A_V = -1$                            | • | 45    | 60      |      | 35    | 60      |      | V/µs  |

## **ELECTRICAL CHARACTERISTICS**

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

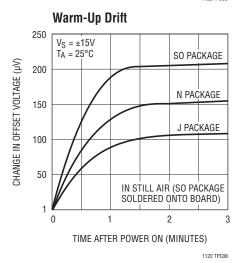

**Note 2:** The LT1122 is measured in an automated tester in less than one second after application of power. Depending on the package used, power dissipation, heat sinking, and air flow conditions, the fully warmed up chip temperature can be 10°C to 50°C higher than the ambient temperature.

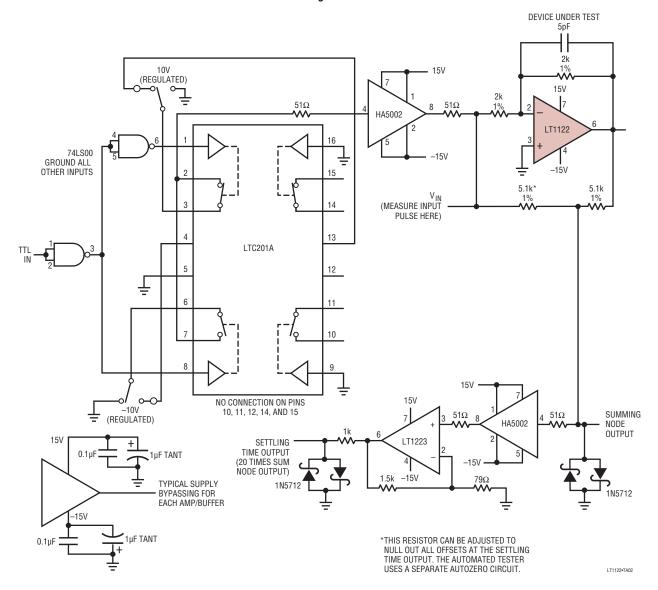

**Note 3:** Settling time is 100% tested for A- and C-grades using the settling time test circuit shown. This test is not included in quality assurance sample testing.

**Note 4:** Input voltage range functionality is assured by testing offset voltage at the input voltage range limits to a maximum of 4mV (A, B grades), to 5.7mV (C, D grades).

**Note 5:** Minimum supply voltage is tested by measuring offset voltage to 7mV maximum at  $\pm 5V$  supplies.

**Note 6:** The LT1122 is not tested and not quality-assurance-sampled at -40°C and at 85°C. These specifications are guaranteed by design, correlation and/or inference from -55°C, 0°C, 25°C, 70°C and/or 125°C tests.

#### **Settling Time Test Fixture**

## TYPICAL PERFORMANCE CHARACTERISTICS

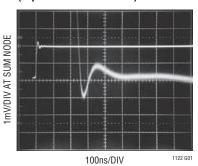

Settling Time (Input from –10V to OV)

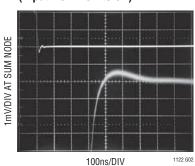

Settling Time (Input from 10V to 0V)

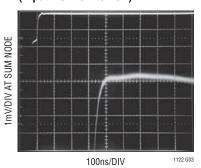

Settling Time (Input from OV to 10V)

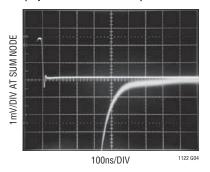

Settling Time (Input from OV to -10V)

Large-Signal Response

Undistorted Output Swing

Voltage Gain vs Frequency

Gain, Phase vs Frequency

Common-Mode Rejection

## TYPICAL PERFORMANCE CHARACTERISTICS

# Voltage 800 3370 UNITS TESTED TA = 25°C (NOT WARMED UP) 400 -900 -500 -100 100 500 900

INPUT OFFSET VOLTAGE (µV)

**Distribution of Input Offset**

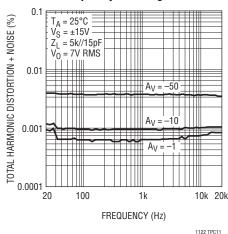

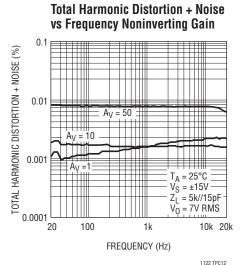

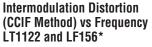

# Total Harmonic Distortion + Noise vs Frequency Inverting Gain

## APPLICATIONS INFORMATION

#### **Settling Time Measurements**

Settling time test circuits shown on some competitive devices' data sheets require:

- 1. A "flat top" pulse generator. Unfortunately, flat top pulse generators are not commercially available.

- 2. A variable feedback capacitor around the device under test. This capacitor varies over a four-to-one range. Presumably, as each op amp is measured for settling time, the capacitor is fine tuned to optimize settling time for that particular device.

- 3. A small inductor load to optimize settling.

The LT1122's settling time is 100% tested in the test circuit shown. No "flat top" pulse generator is required. The test circuit can be readily constructed, using commercially available ICs. Of course, standard high frequency board construction techniques should be followed. All LT1122s are measured with a constant feedback capacitor. No fine tuning is required.

## Speed Boost/Overcompensation Terminal

Pin 8 of the LT1122 can be used to change the input stage operating current of the device. Shorting Pin 8 to the positive supply (Pin 7) increases slew rate and bandwidth by about 25%, but at the expense of a reduction in phase margin by approximately 18 degrees. Unity-gain capacitive load handling decreases from typically 500pF to 100pF.

Conversely, connecting a 15k resistor from Pin 8 to ground pulls 1mA out of Pin 8 (with  $V^+$  = 15V). This reduces slew rate and bandwidth by 25%. Phase margin and capacitive load handling improve; the latter typically increasing to 800pF.

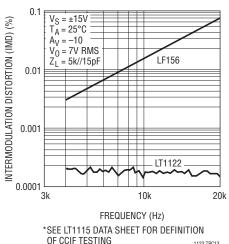

## **High Speed Operation**

As with most high speed amplifiers, care should be taken with supply decoupling, lead dress and component placement.

The power supply connections to the LT1122 must maintain a low impedance to ground over a bandwidth of 20MHz. This is especially important when driving a significant resistive or capacitive load, since all current delivered to the load comes from the power supplies. Multiple high quality bypass capacitors are recommended for each power supply line in any critical application. A  $0.1\mu F$  ceramic and a  $1\mu F$  electrolytic capacitor, as shown, placed as close as possible to the amplifier (with short lead lengths to power supply common) will assure adequate high frequency bypassing, in most applications.

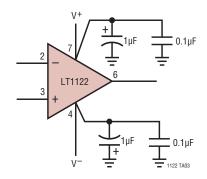

When the feedback around the op amp is resistive ( $R_F$ ), a pole will be created with  $R_F$ , the source resistance and capacitance ( $R_S$ ,  $C_S$ ), and the amplifier input capacitance ( $C_{IN} \approx 4pF$ ). In low closed-loop gain configurations and with  $R_S$  and  $R_F$  in the kilohm range, this pole can create excess phase shift and even oscillation. A small capacitor ( $C_F$ ) in parallel with  $R_F$  eliminates this problem. With  $R_S$  ( $C_S + C_{IN}$ ) =  $R_F C_F$ , the effect of the feedback pole is completely removed.

LINEAR TECHNOLOGY

## TYPICAL APPLICATIONS

## **Quartz Stabilized Oscillator With 9ppm Distortion**

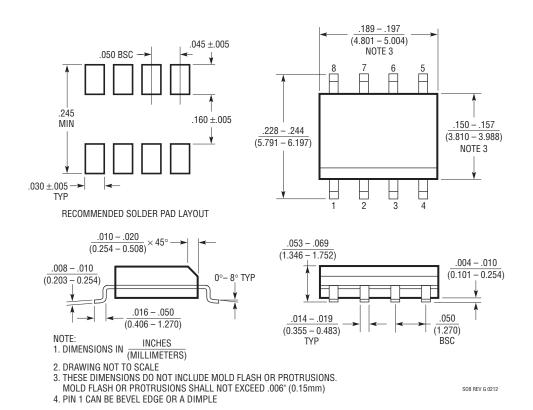

## PACKAGE DESCRIPTION

Please refer to http://www.linear.com/designtools/packaging/ for the most recent package drawings.

#### N Package 8-Lead PDIP (Narrow .300 Inch)

(Reference LTC DWG # 05-08-1510 Rev I)

NOTE:

1. DIMENSIONS ARE INCHES MILLIMETERS

<sup>\*</sup>THESE DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS. MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED .010 INCH (0.254mm)

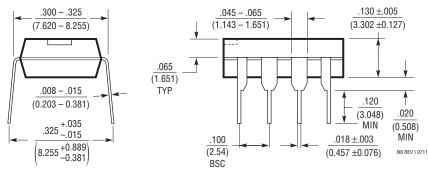

## PACKAGE DESCRIPTION

Please refer to http://www.linear.com/designtools/packaging/ for the most recent package drawings.

## PACKAGE DESCRIPTION

Please refer to http://www.linear.com/designtools/packaging/ for the most recent package drawings.

## \$8 Package 8-Lead Plastic Small Outline (Narrow .150 Inch)

(Reference LTC DWG # 05-08-1610 Rev G)

## **REVISION HISTORY** (Revision history begins at Rev B)

| REV | DATE  | DESCRIPTION                                                                                | PAGE NUMBER |

|-----|-------|--------------------------------------------------------------------------------------------|-------------|

| В   | 02/14 | Updated data sheet to current standards. New Order Information Table, Package Descriptions | 2, 10-12    |

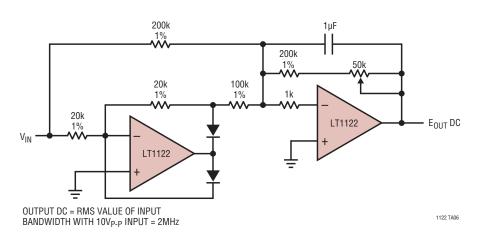

## TYPICAL APPLICATION

## Wide-Band, Filtered, Full Wave Rectifier

## **RELATED PARTS**

| PART NUMBER           | DESCRIPTION                       | COMMENTS                                                                                    |

|-----------------------|-----------------------------------|---------------------------------------------------------------------------------------------|

| LT1022                | High Speed Precision JFET Op Amp  | 23V/μs Min Slew Rate, 250μV V <sub>OS</sub>                                                 |

| LT1055/LT1056         | Precision High Speed JFET Op Amps | 16V/μs Slew Rate, 150μV V <sub>OS</sub>                                                     |

| LT1464                | 1MHz C-Load™ Stable JFET Op Amp   | Capacitive Loads Up to 10nF                                                                 |

| LTC <sup>®</sup> 6244 | 50MHz Low Noise CMOS Op Amp       | 1pA I <sub>B</sub> , 100μV Max V <sub>OS</sub> , 1.5μV <sub>P-P</sub> , 0.1Hz to 10Hz Noise |