DRV8343-Q1

SLVSE12 - MARCH 2018

# DRV8343-Q1 Automotive 5.5 to 60-V Three-Phase Smart Gate Driver With Three Integrated Current Shunt Amplifiers

#### **Features**

- AEC-Q100 Qualified for Automotive Applications

- Temperature Grade 1: –40°C ≤ T<sub>A</sub> ≤ 125°C

- HBM ESD Classification Level 2

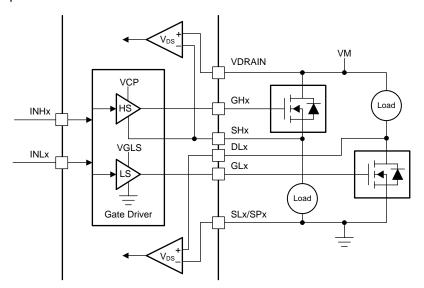

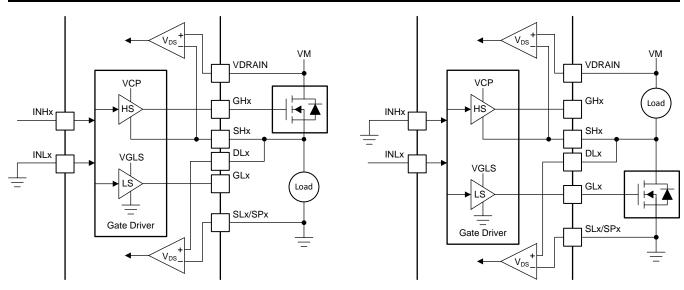

- Triple Half-Bridge Gate Driver

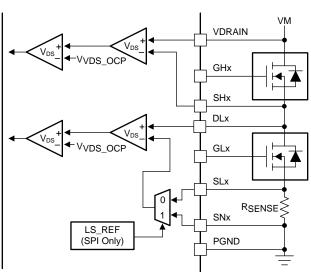

- Dedicated Source (SHx) and Drain (DLx) pins to support independent MOSFET control

- Drives 3 High-Side and 3 Low-Side N-Channel MOSFETs (NMOS)

- Smart Gate Drive Architecture

- Adjustable Slew Rate Control

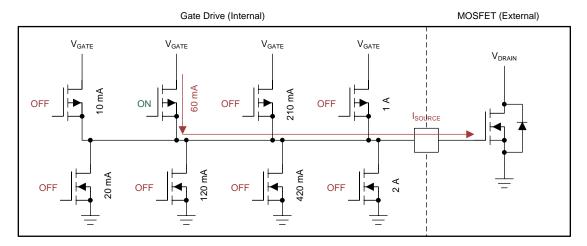

- 1.5-mA to 1-A Peak Source Current

- 3-mA to 2-A Peak Sink Current

- Integrated Gate Driver Power Supplies

- Supports 100% PWM Duty Cycle

- High-Side Charge Pump

- Low-Side Linear Regulator

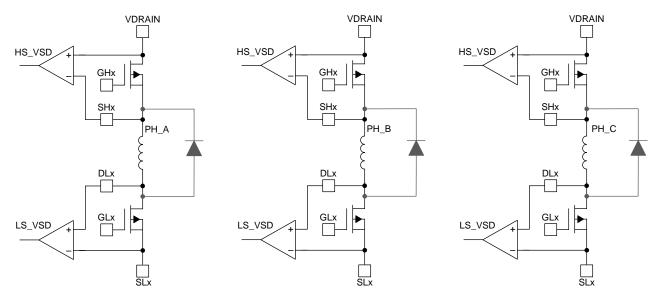

- 3 Integrated Current Sense Amplifiers (CSAs)

- Adjustable Gain (5, 10, 20, 40 V/V)

- Bidirectional or Unidirectional Support

- SPI and Hardware Interface Available

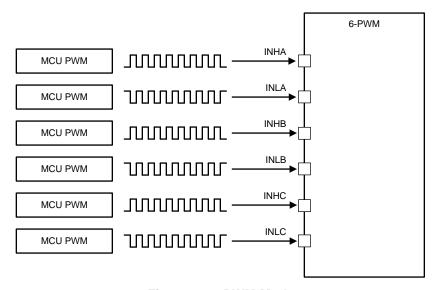

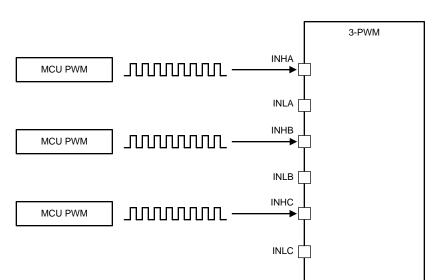

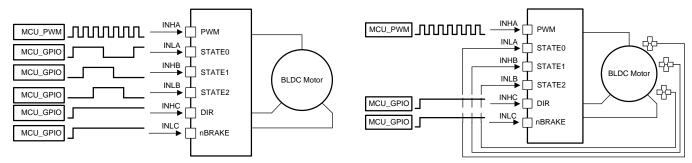

- 6x, 3x, 1x, and Independent PWM Modes

- Supports 3.3-V, and 5-V Logic Inputs

- Charge Pump Output can be used to Drive the Reverse Supply Protection MOSFET

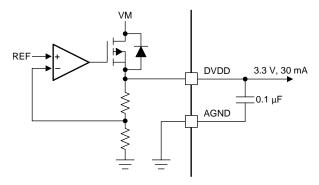

- Linear Voltage Regulator, 3.3 V, 30 mA

- **Integrated Protection Features**

- VM Undervoltage Lockout (UVLO)

- Charge Pump Undervoltage (CPUV)

- Short to Battery (SHT\_BAT)

- Short to Ground (SHT\_GND)

- MOSFET Overcurrent Protection (OCP)

- Gate Driver Fault (GDF)

- Thermal Warning and Shutdown (OTW/OTSD)

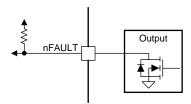

- Fault Condition Indicator (nFAULT)

## 2 Applications

- 12-V and 24-V Automotive Motor-Control **Applications**

- **BLDC** and BDC Motor Modules

- Fans and Blowers

- Fuel and Water Pumps

- Solenoid Drive

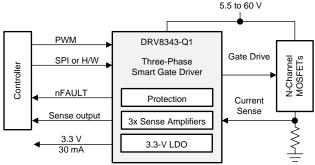

## 3 Description

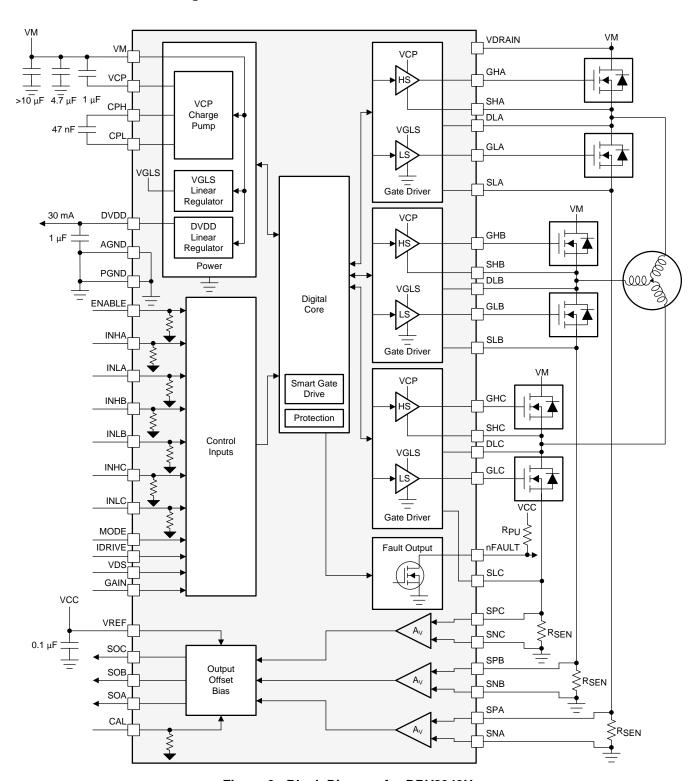

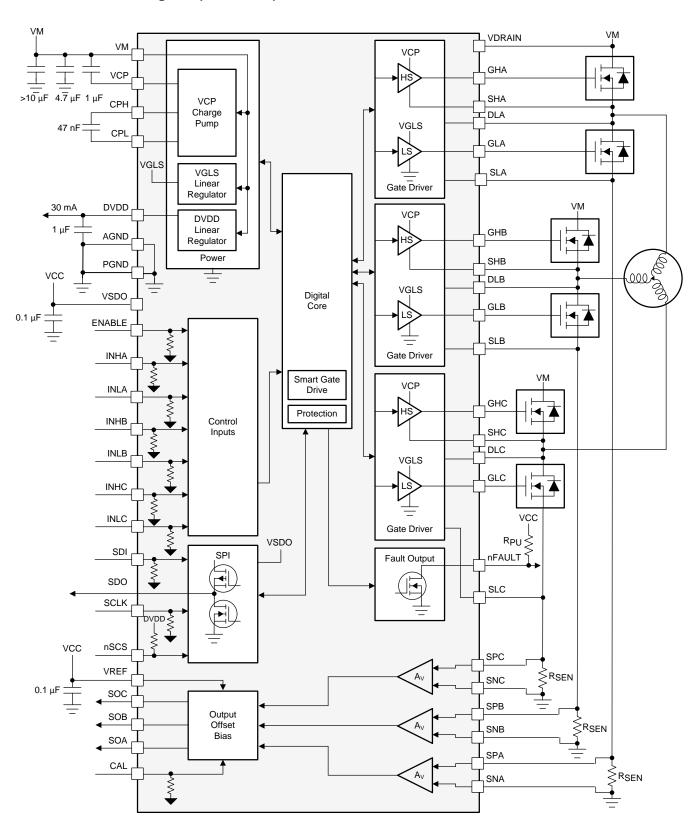

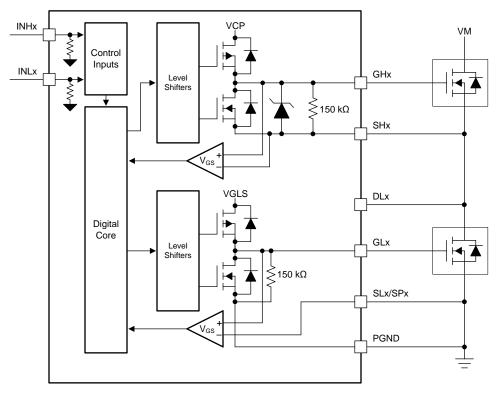

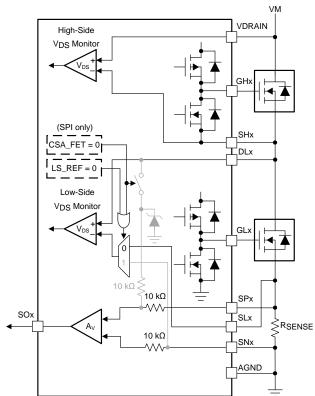

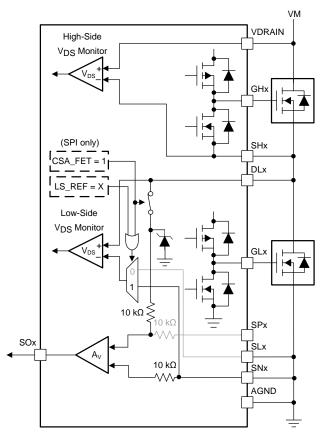

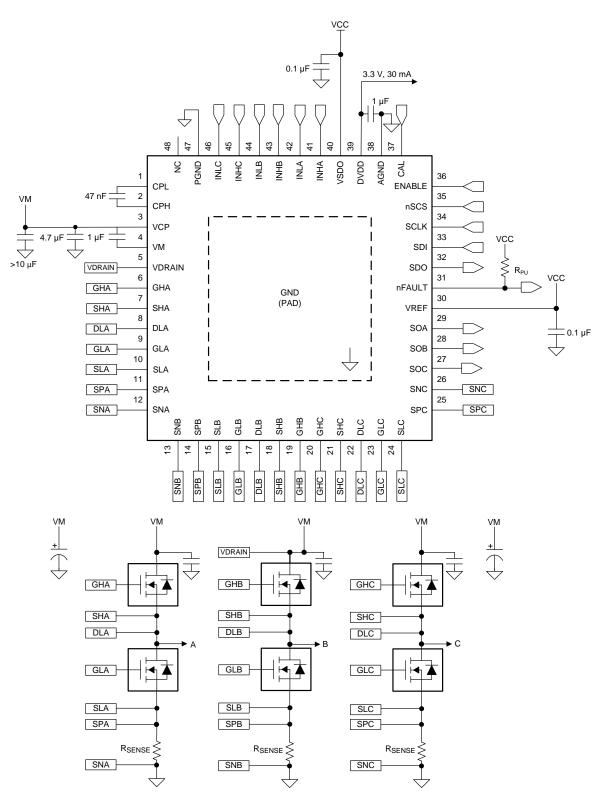

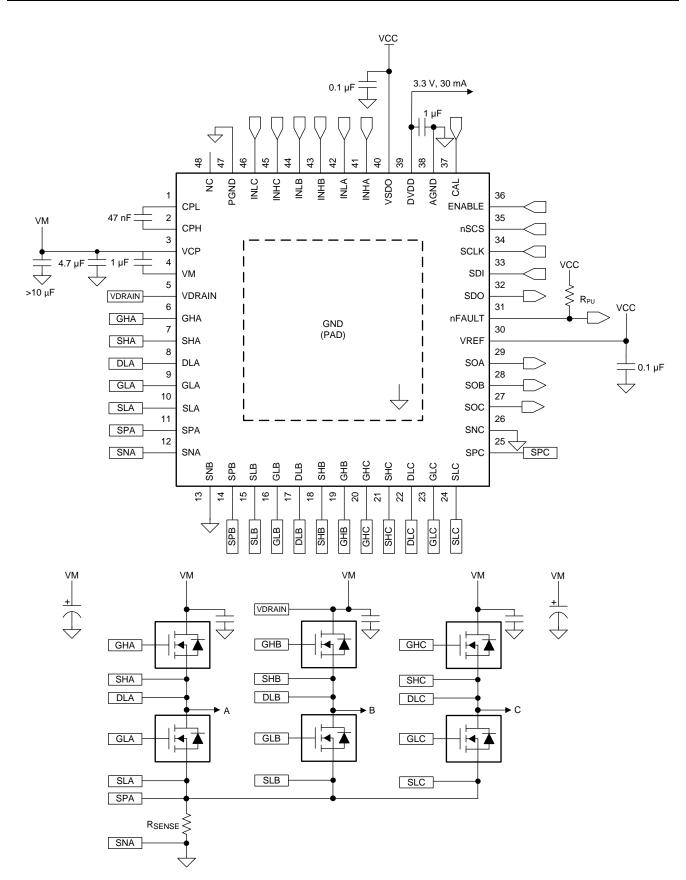

The DRV8343-Q1 device is an integrated gate driver for three-phase applications. The device provides three half-bridge gate drivers, each capable of driving high-side and low-side N-channel power MOSFETs. The dedicated Source and Drain pins enable the independent MOSFET control for application. The DRV8343-Q1 generates the correct gate drive voltages using an integrated charge pump for the high-side MOSFETs and a linear regulator for the low-side MOSFETs. The Smart Gate Drive architecture supports peak gate drive currents up to 1-A source and 2-A. The DRV8343-Q1 can operate from a single power supply and supports a wide input supply range of 5.5 to 60 V for the gate driver.

The 6x, 3x, 1x, and independent input PWM modes allow for simple interfacing to controller circuits. The configuration settings for the gate driver and device are highly configurable through the SPI or hardware (H/W) interface. The DRV8343-Q1 device integrates three low-side current sense amplifiers that allow bidirectional current sensing on all three phases of the drive stage.

A low-power sleep mode is provided to achieve low quiescent current. Internal protection functions are provided for undervoltage lockout, charge pump fault, MOSFET overcurrent, MOSFET short circuit, phasenode short to supply and ground, gate driver fault, and overtemperature. Fault conditions are indicated on the nFAULT pin with details through the device registers for the SPI device variant.

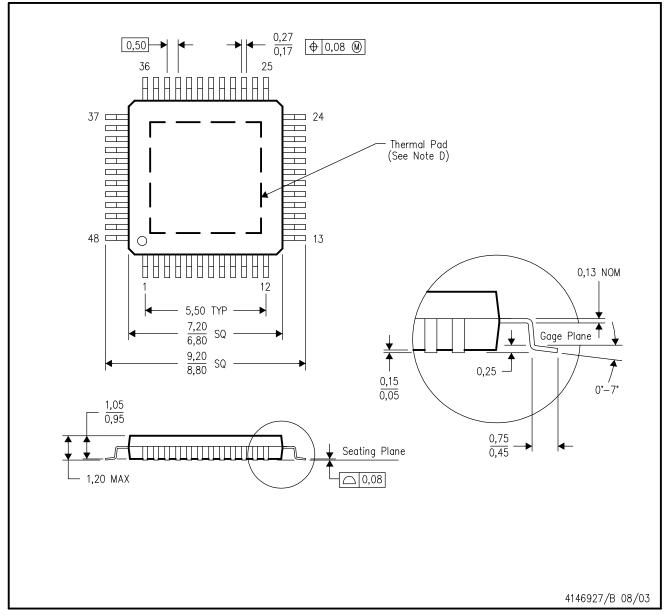

### Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE    | BODY SIZE (NOM)   |

|-------------|------------|-------------------|

| DRV8343-Q1  | HTQFP (48) | 7.00 mm × 7.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

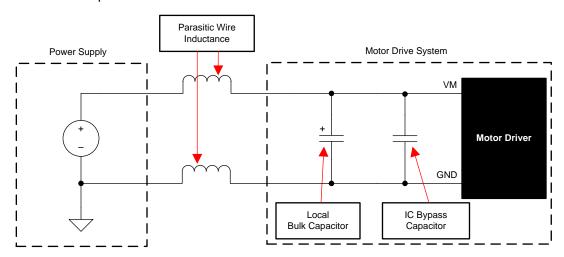

#### Simplified Schematic

Copyright © 2017, Texas Instruments Incorporated

# **Table of Contents**

| 1 | Features 1                           | 8.6 Register Maps                                   | 53          |

|---|--------------------------------------|-----------------------------------------------------|-------------|

| 2 | Applications 1                       | 9 Application and Implementation                    |             |

| 3 | Description 1                        | 9.1 Application Information                         |             |

| 4 | Revision History2                    | 9.2 Typical Application                             | 68          |

| 5 | Device Comparison Table3             | 10 Power Supply Recommendations                     | . 75        |

| 6 | Pin Configuration and Functions3     | 10.1 Bulk Capacitance Sizing                        | 75          |

| 7 | Specifications7                      | 11 Layout                                           | . <b>76</b> |

|   | 7.1 Absolute Maximum Ratings 7       | 11.1 Layout Guidelines                              | 76          |

|   | 7.2 ESD Ratings                      | 11.2 Layout Example                                 | 77          |

|   | 7.3 Recommended Operating Conditions | 12 Device and Documentation Support                 | . 78        |

|   | 7.4 Thermal Information              | 12.1 Device Support                                 | 78          |

|   | 7.5 Electrical Characteristics9      | 12.2 Documentation Support                          | 78          |

|   | 7.6 SPI Timing Requirements          | 12.3 Receiving Notification of Documentation Update | s 78        |

| 8 | Detailed Description 16              | 12.4 Community Resources                            | 78          |

| • | 8.1 Overview                         | 12.5 Trademarks                                     | 78          |

|   | 8.2 Functional Block Diagram         | 12.6 Electrostatic Discharge Caution                | 79          |

|   | 8.3 Feature Description              | 12.7 Glossary                                       | 79          |

|   | 8.4 Device Functional Modes          | 13 Mechanical, Packaging, and Orderable             |             |

|   | 8.5 Programming                      | Information                                         | . 79        |

# 4 Revision History

NOTE: Page numbers for previous revisions may differ from page numbers in the current version.

| DATE          | REVISION | NOTES                                                                                                                                                                                          |

|---------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| March 2018    | 0.1      | Initial Release                                                                                                                                                                                |

| December 2018 | 0.2      | <ul> <li>ADVANCE INFORMATION</li> <li>Recommended Operating Conditions updated</li> <li>Electrical Characteristics updated</li> <li>Table 10 updated</li> <li>Register Maps updated</li> </ul> |

Product Folder Links: DRV8343-Q1

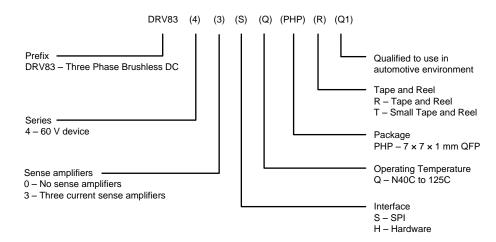

# 5 Device Comparison Table

| DEVICE     | VARIANT <sup>(1)</sup> | INTERFACE <sup>(1)</sup> |

|------------|------------------------|--------------------------|

| DRV8343-Q1 | DRV8343H               | Hardware                 |

| DRV6343-Q1 | DRV8343S               | SPI                      |

(1) For more information on the device name and device options, see the *Device Nomenclature* section.

## 6 Pin Configuration and Functions

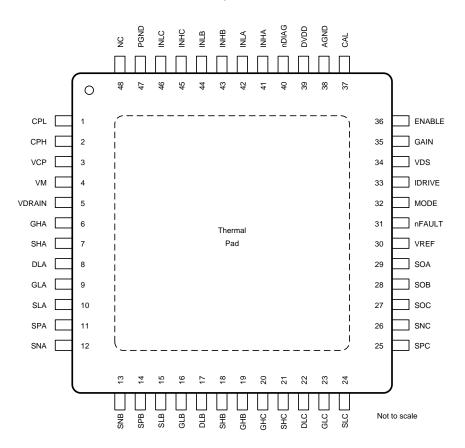

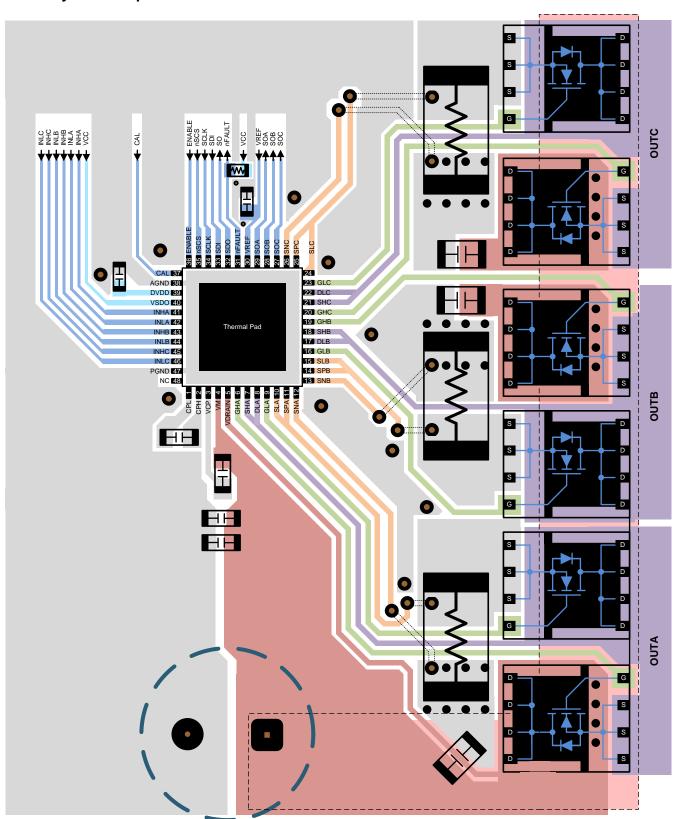

#### DRV8343H PHP PowerPAD™ Package 48-Pin HTQFP With Exposed Thermal Pad Top View

#### Pin Functions—DRV8343H

|     | PIN    |                     | DESCRIPTION                                                                                                                                                                                          |  |

|-----|--------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NO. | NAME   | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                          |  |

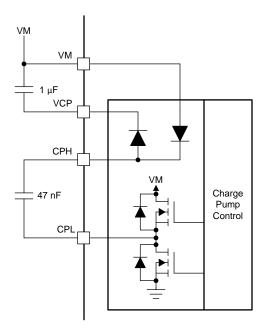

| 1   | CPL    | PWR                 | Charge pump switching node. Connect a X5R or X7R, 47-nF, VM-rated ceramic capacitor between the CPH and CPL pins                                                                                     |  |

| 2   | CPH    | PWR                 | Charge pump switching node. Connect a X5R or X7R, 47-nF, VM-rated ceramic capacitor between the CPH and CPL pins                                                                                     |  |

| 3   | VCP    | PWR                 | Charge pump output. Connect a X5R or X7R, 1-µF, 50-V ceramic capacitor between the VCP and VM pins                                                                                                   |  |

| 4   | VM     | PWR                 | Gate driver power supply input. Connect to the bridge power supply. Connect a X5R or X7R, 0.1-μF, VM-rated ceramic and greater than or equal to 10-uF local capacitance between the VM and PGND pins |  |

| 5   | VDRAIN | I                   | ligh-side MOSFET drain sense input. Connect to the common point of the MOSFET drains                                                                                                                 |  |

| 6   | GHA    | 0                   | igh-side gate driver output. Connect to the gate of the high-side power MOSFET                                                                                                                       |  |

| 7   | SHA    | 1                   | High-side source sense input. Connect to the high-side power MOSFET source. If high-side power MOSFET is not used, connect to GND                                                                    |  |

(1) PWR = power, I = input, O = output, NC = no connection, OD = open-drain output

### Pin Functions—DRV8343H (continued)

|     | PIN            |                     |                                                                                                                                                                                                                                                              |

|-----|----------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NO. | NAME           | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                  |

| 8   | DLA            | ı                   | Low-side MOSFET drain sense input. Connect to the low-side MOSFET drain                                                                                                                                                                                      |

| 9   | GLA            | 0                   | Low-side gate driver output. Connect to the gate of the low-side power MOSFET                                                                                                                                                                                |

| 10  | SLA            | ı                   | Low-side source sense input. Connect to the low-side power MOSFET source                                                                                                                                                                                     |

| 4.4 | SPA            | ı                   | Low-side current shunt amplifier input. Connect to the low-side power MOSFET source and high-side of the current shunt                                                                                                                                       |

| 11  | SPA            | ı                   | resistor                                                                                                                                                                                                                                                     |

| 12  | SNA            | I                   | Current sense amplifier input. Connect to the low-side of the current shunt resistor                                                                                                                                                                         |

| 13  | SNB            | I                   | Low-side source sense input. Connect to the low-side power MOSFET source                                                                                                                                                                                     |

| 14  | SPB            | I                   | Low-side current shunt amplifier input. Connect to the low-side power MOSFET source and high-side of the current shunt resistor                                                                                                                              |

| 15  | SLB            | I                   | Low-side source sense input. Connect to the low-side power MOSFET source                                                                                                                                                                                     |

| 16  | GLB            | 0                   | Low-side gate driver output. Connect to the gate of the low-side power MOSFET                                                                                                                                                                                |

| 17  | DLB            | I                   | Low-side MOSFET drain sense input. Connect to the low-side MOSFET drain                                                                                                                                                                                      |

| 18  | SHB            | I                   | High-side source sense input. Connect to the high-side power MOSFET source. If high-side power MOSFET is not used, connect to GND                                                                                                                            |

| 19  | GHB            | 0                   | High-side gate driver output. Connect to the gate of the high-side power MOSFET                                                                                                                                                                              |

| 20  | GHC            | 0                   | High-side gate driver output. Connect to the gate of the high-side power MOSFET                                                                                                                                                                              |

| 21  | SHC            | 1                   | High-side source sense input. Connect to the high-side power MOSFET source. If high-side power MOSFET is not used, connect to GND                                                                                                                            |

| 22  | DLC            | I                   | Low-side MOSFET drain sense input. Connect to the low-side MOSFET drain                                                                                                                                                                                      |

| 23  | GLC            | 0                   | Low-side gate driver output. Connect to the gate of the low-side power MOSFET                                                                                                                                                                                |

| 24  | SLC            | I                   | Low-side source sense input. Connect to the low-side power MOSFET source                                                                                                                                                                                     |

| 25  | SPC            | I                   | Low-side current shunt amplifier input. Connect to the low-side power MOSFET source and high-side of the current shunt resistor                                                                                                                              |

| 26  | SNC            | I                   | Current sense amplifier input. Connect to the low-side of the current shunt resistor                                                                                                                                                                         |

| 27  | SOC            | 0                   | Current sense amplifier output                                                                                                                                                                                                                               |

| 28  | SOB            | 0                   | Current sense amplifier output                                                                                                                                                                                                                               |

| 29  | SOA            | 0                   | Current sense amplifier output                                                                                                                                                                                                                               |

| 30  | VREF           | PWR                 | Current sense amplifier power supply input and reference. Connect a X5R or X7R, 0.1-μF, 6.3-V ceramic cap between VREF and AGND                                                                                                                              |

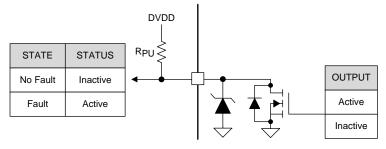

| 31  | nFAULT         | OD                  | Fault indicator output. This pin is pulled logic low during a fault condition and requires an external pullup resistor                                                                                                                                       |

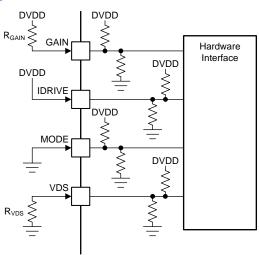

| 32  | MODE           | I                   | PWM input mode setting. This pin is a 4-level input pin set by an external resistor                                                                                                                                                                          |

| 33  | IDRIVE         | I                   | Gate drive output current setting. This pin is a 7-level input pin set by an external resistor                                                                                                                                                               |

| 34  | VDS            | I                   | VDS monitor trip point setting. This pin is a 7-level input pin set by an external resistor                                                                                                                                                                  |

| 35  | GAIN           | I                   | Amplifier gain setting. The pin is a 4-level input pin set by an external resistor                                                                                                                                                                           |

| 36  | ENABLE         | I                   | Gate driver enable. When this pin is logic low the device goes to a low-power sleep mode. An 8 to 40-µs low pulse can be used to reset fault conditions                                                                                                      |

| 37  | CAL            | I                   | Amplifier calibration input. Set logic high to internally short amplifier inputs                                                                                                                                                                             |

| 38  | AGND           | PWR                 | Device analog ground. Connect to system ground                                                                                                                                                                                                               |

| 39  | DVDD           | PWR                 | 3.3-V internal regulator output. Connect a X5R or X7R, 1- $\mu$ F, 6.3-V ceramic capacitor between the DVDD and AGND pins. This regulator can externally source up to 30 mA.                                                                                 |

| 40  | nDIAG          | I                   | Control pin for open load diagnostic and offline short-to-battery and short-to-ground diagnostic. To enable the diagnostics at device power-up, do not connect this pin (or tie it to ground). To disable the diagnostics, connect this pin to the DVDD pin. |

| 41  | INHA           | I                   | High-side gate driver control input. This pin controls the output of the high-side gate driver                                                                                                                                                               |

| 42  | INLA           | I                   | Low-side gate driver control input. This pin controls the output of the low-side gate driver                                                                                                                                                                 |

| 43  | INHB           | I                   | High-side gate driver control input. This pin controls the output of the high-side gate driver                                                                                                                                                               |

| 44  | INLB           | I                   | Low-side gate driver control input. This pin controls the output of the low-side gate driver                                                                                                                                                                 |

| 45  | INHC           | I                   | High-side gate driver control input. This pin controls the output of the high-side gate driver                                                                                                                                                               |

| 46  | INLC           | I                   | Low-side gate driver control input. This pin controls the output of the low-side gate driver                                                                                                                                                                 |

| 47  | PGND           | PWR                 | Device power ground. Connect to system ground                                                                                                                                                                                                                |

| 48  | NC             | NC                  | No connect. Do not connect anything to this pin                                                                                                                                                                                                              |

| _   | Thermal<br>Pad | PWR                 | Must be connected to ground                                                                                                                                                                                                                                  |

Submit Documentation Feedback

www.ti.com

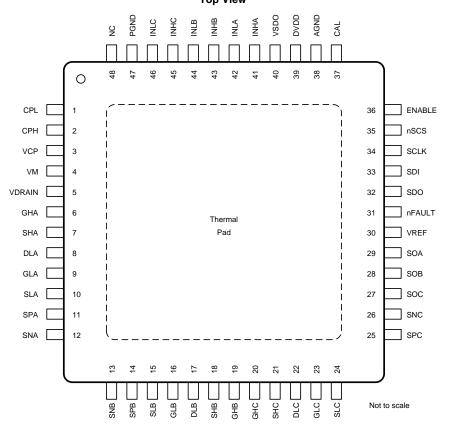

#### DRV8343S PHP PowerPAD™ Package 48-Pin HTQFP With Exposed Thermal Pad Top View

### Pin Functions—DRV8343S

|     | PIN    |                     | DECODINE                                                                                                                                                                                             |  |

|-----|--------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NO. | NAME   | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                          |  |

| 1   | CPL    | PWR                 | Charge pump switching node. Connect a X5R or X7R, 47-nF, VM-rated ceramic capacitor between the CPH and CPL pins                                                                                     |  |

| 2   | CPH    | PWR                 | Charge pump switching node. Connect a X5R or X7R, 47-nF, VM-rated ceramic capacitor between the CPH and CPL pins                                                                                     |  |

| 3   | VCP    | PWR                 | Charge pump output. Connect a X5R or X7R, 1-µF, 50-V ceramic capacitor between the VCP and VM pins                                                                                                   |  |

| 4   | VM     | PWR                 | Gate driver power supply input. Connect to the bridge power supply. Connect a X5R or X7R, 0.1-μF, VM-rated ceramic and greater than or equal to 10-uF local capacitance between the VM and PGND pins |  |

| 5   | VDRAIN | I                   | High-side MOSFET drain sense input. Connect to the common point of the MOSFET drains                                                                                                                 |  |

| 6   | GHA    | 0                   | High-side gate driver output. Connect to the gate of the high-side power MOSFET                                                                                                                      |  |

| 7   | SHA    | I                   | igh-side source sense input. Connect to the high-side power MOSFET source. If high-side power MOSFET is not used, onnect to GND                                                                      |  |

| 8   | DLA    | I                   | Low-side MOSFET drain sense input. Connect to the low-side MOSFET drain                                                                                                                              |  |

| 9   | GLA    | 0                   | Low-side gate driver output. Connect to the gate of the low-side power MOSFET                                                                                                                        |  |

| 10  | SLA    | I                   | Low-side source sense input. Connect to the low-side power MOSFET source                                                                                                                             |  |

| 11  | SPA    | I                   | ow-side current shunt amplifier input. Connect to the low-side power MOSFET source and high-side of the current shunt sistor                                                                         |  |

| 12  | SNA    | I                   | Current sense amplifier input. Connect to the low-side of the current shunt resistor                                                                                                                 |  |

| 13  | SNB    | I                   | Low-side source sense input. Connect to the low-side power MOSFET source                                                                                                                             |  |

| 14  | SPB    | I                   | Low-side current shunt amplifier input. Connect to the low-side power MOSFET source and high-side of the current shunt resistor                                                                      |  |

| 15  | SLB    | I                   | Low-side source sense input. Connect to the low-side power MOSFET source                                                                                                                             |  |

| 16  | GLB    | 0                   | Low-side gate driver output. Connect to the gate of the low-side power MOSFET                                                                                                                        |  |

| 17  | DLB    | I                   | Low-side MOSFET drain sense input. Connect to the low-side MOSFET drain                                                                                                                              |  |

Product Folder Links: DRV8343-Q1

(1) PWR = power, I = input, O = output, NC = no connection, OD = open-drain output, PP = push-pull

# Pin Functions—DRV8343S (continued)

|     | PIN            |                     |                                                                                                                                                                              |  |  |

|-----|----------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NO. | NAME           | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                  |  |  |

| 18  | SHB            | ı                   | High-side source sense input. Connect to the high-side power MOSFET source. If high-side power MOSFET is not used, connect to GND                                            |  |  |

| 19  | GHB            | 0                   | High-side gate driver output. Connect to the gate of the high-side power MOSFET                                                                                              |  |  |

| 20  | GHC            | 0                   | High-side gate driver output. Connect to the gate of the high-side power MOSFET                                                                                              |  |  |

| 21  | SHC            | 1                   | High-side source sense input. Connect to the high-side power MOSFET source. If high-side power MOSFET is not used, connect to GND                                            |  |  |

| 22  | DLC            | I                   | Low-side MOSFET drain sense input. Connect to the low-side MOSFET drain                                                                                                      |  |  |

| 23  | GLC            | 0                   | Low-side gate driver output. Connect to the gate of the low-side power MOSFET                                                                                                |  |  |

| 24  | SLC            | I                   | Low-side source sense input. Connect to the low-side power MOSFET source                                                                                                     |  |  |

| 25  | SPC            | I                   | Low-side current shunt amplifier input. Connect to the low-side power MOSFET source and high-side of the current shunt resistor                                              |  |  |

| 26  | SNC            | I                   | Current sense amplifier input. Connect to the low-side of the current shunt resistor                                                                                         |  |  |

| 27  | SOC            | 0                   | Current sense amplifier output                                                                                                                                               |  |  |

| 28  | SOB            | 0                   | Current sense amplifier output                                                                                                                                               |  |  |

| 29  | SOA            | 0                   | Current sense amplifier output                                                                                                                                               |  |  |

| 30  | VREF           | PWR                 | Current sense amplifier power supply input and reference. Connect a X5R or X7R, 0.1-μF, 6.3-V ceramic cap between VREF and AGND                                              |  |  |

| 31  | nFAULT         | OD                  | Fault indicator output. This pin is pulled logic low during a fault condition and requires an external pullup resistor                                                       |  |  |

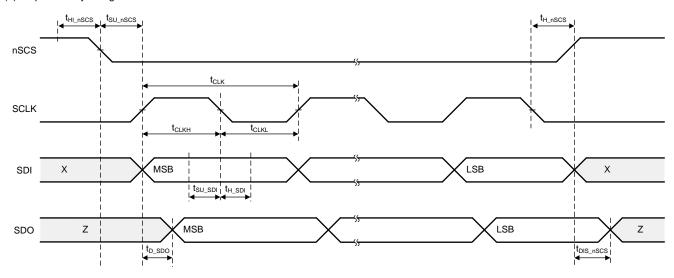

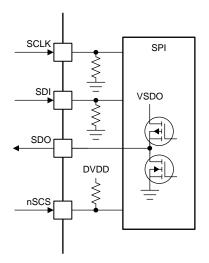

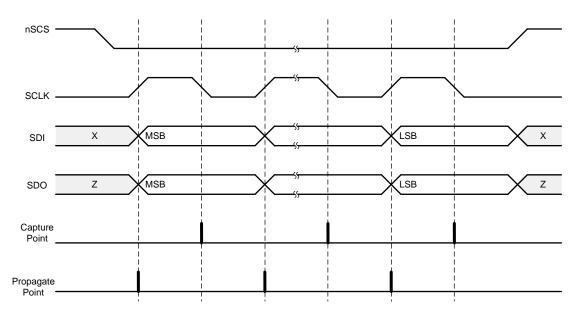

| 32  | SDO            | PP                  | Serial data output. Data is shifted out on the rising edge of the SCLK pin. VSDO determines logic level on the output                                                        |  |  |

| 33  | SDI            | I                   | Serial data input. Data is captured on the falling edge of the SCLK pin                                                                                                      |  |  |

| 34  | SCLK           | I                   | Serial clock input. Serial data is shifted out and captured on the corresponding rising and falling edge on this pin                                                         |  |  |

| 35  | nSCS           | I                   | Serial chip select. A logic low on this pin enables serial interface communication                                                                                           |  |  |

| 36  | ENABLE         | I                   | Gate driver enable. When this pin is logic low the device goes to a low-power sleep mode. An 8- to 40-μs low pulse can be used to reset fault conditions                     |  |  |

| 37  | CAL            | I                   | Amplifier calibration input. Set logic high to internally short amplifier inputs                                                                                             |  |  |

| 38  | AGND           | PWR                 | Device analog ground. Connect to system ground                                                                                                                               |  |  |

| 39  | DVDD           | PWR                 | 3.3-V internal regulator output. Connect a X5R or X7R, 1- $\mu$ F, 6.3-V ceramic capacitor between the DVDD and AGND pins. This regulator can externally source up to 30 mA. |  |  |

| 40  | VSDO           | PWR                 | Supply pin for SDO output. Connect to 5-V or 3.3-V depending on the desired logic level                                                                                      |  |  |

| 41  | INHA           | I                   | High-side gate driver control input. This pin controls the output of the high-side gate driver                                                                               |  |  |

| 42  | INLA           | I                   | Low-side gate driver control input. This pin controls the output of the low-side gate driver                                                                                 |  |  |

| 43  | INHB           | I                   | High-side gate driver control input. This pin controls the output of the high-side gate driver                                                                               |  |  |

| 44  | INLB           | I                   | Low-side gate driver control input. This pin controls the output of the low-side gate driver                                                                                 |  |  |

| 45  | INHC           | I                   | High-side gate driver control input. This pin controls the output of the high-side gate driver                                                                               |  |  |

| 46  | INLC           | I                   | Low-side gate driver control input. This pin controls the output of the low-side gate driver                                                                                 |  |  |

| 47  | PGND           | PWR                 | Device power ground. Connect to system ground                                                                                                                                |  |  |

| 48  | NC             | NC                  | No connect. Do not connect anything to this pin                                                                                                                              |  |  |

| _   | Thermal<br>Pad | PWR                 | Must be connected to ground                                                                                                                                                  |  |  |

Submit Documentation Feedback

### 7 Specifications

### 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                                                                                                             | MIN               | MAX                    | UNIT |

|-------------------------------------------------------------------------------------------------------------|-------------------|------------------------|------|

| GATE DRIVER                                                                                                 |                   |                        |      |

| Power supply pin voltage (VM)                                                                               | -0.3              | 65                     | V    |

| Voltage differential between ground pins (AGND, BGND, DGND, PGND)                                           | -0.3              | 0.3                    | V    |

| MOSFET drain sense pin voltage (VDRAIN)                                                                     | -0.3              | 65                     | V    |

| Charge pump pin voltage (CPH, VCP)                                                                          | -0.3              | V <sub>VM</sub> + 13.5 | V    |

| Charge-pump negative-switching pin voltage (CPL)                                                            | -0.3              | $V_{VM}$               | V    |

| Internal logic regulator pin voltage (DVDD)                                                                 | -0.3              | 3.8                    | V    |

| Voltage difference between VM and VDRAIN                                                                    | -10               | 10                     | V    |

| Digital pin voltage (CAL, ENABLE, GAIN, IDRIVE, INHx, INLx, MODE, nFAULT, nSCS, SCLK, SDI, SDO, VDS, nDIAG) | -0.3              | 5.75                   | V    |

| Continuous high-side gate drive pin voltage (GHx)                                                           | -5 <sup>(2)</sup> | V <sub>VCP</sub> + 0.5 | V    |

| Transient 200-ns high-side gate drive pin voltage (GHx)                                                     | -7                | V <sub>VCP</sub> + 0.5 | V    |

| High-side gate drive pin voltage with respect to SHx (GHx)                                                  | -0.3              | 13.5                   | V    |

| Continuous high-side source sense pin voltage (SHx, DLx)                                                    | -5 <sup>(2)</sup> | V <sub>VM</sub> + 5    | V    |

| Transient 200-ns high-side source sense pin voltage (SHx, DLx)                                              | -7                | V <sub>VM</sub> + 7    | V    |

| Continuous high-side source sense pin voltage (SHx, DLx)                                                    | -5 <sup>(2)</sup> | V <sub>DRAIN</sub> + 5 | V    |

| Transient 200-ns high-side source sense pin voltage (SHx, DLx)                                              | -7                | V <sub>DRAIN</sub> + 7 | V    |

| Continuous low-side gate drive pin voltage (GLx)                                                            | -0.5              | 18                     | V    |

| Gate drive pin source current (GHx, GLx)                                                                    | I                 | nternally limited      | Α    |

| Gate drive pin sink current (GHx, GLx)                                                                      | I                 | nternally limited      | Α    |

| Continuous low-side source sense pin voltage (SLx)                                                          | -1                | 1                      | V    |

| Transient 200-ns low-side source sense pin voltage (SLx)                                                    | -3                | 3                      | V    |

| Continuous shunt amplifier input pin voltage (SNx, SPx)                                                     | -1                | 1                      | V    |

| Transient 200-ns shunt amplifier input pin voltage (SNx, SPx)                                               | -3                | 3                      | V    |

| Reference input pin voltage (VREF)                                                                          | -0.3              | 5.75                   | V    |

| Shunt amplifier output pin voltage (SOx)                                                                    | -0.3              | $V_{VREF} + 0.3$       | V    |

| Shunt amplifier output current (SOx)                                                                        | 0                 | 8                      | mA   |

| Push-pull output buffer reference voltage (VSDO)                                                            | -0.3              | 5.75                   | V    |

| Push-pull output current (SDO)                                                                              | 0                 | 10                     | mA   |

| Open drain pullup voltage (nFAULT)                                                                          | -0.3              | 5.75                   | V    |

| Open drain output current (nFAULT)                                                                          | 0                 | 10                     | mA   |

| Operating junction temperature, T <sub>J</sub>                                                              | -40               | 150                    | °C   |

| Storage temperature, T <sub>stg</sub>                                                                       | -65               | 150                    | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 7.2 ESD Ratings

|                                            |                         |                                       |                                                 | VALUE | UNIT |

|--------------------------------------------|-------------------------|---------------------------------------|-------------------------------------------------|-------|------|

| V <sub>(ESD)</sub> Electrostatic discharge |                         | Human-body model (HBM), per AEC Q100- | -002 <sup>(1)</sup>                             | ±2000 |      |

|                                            | Electrostatic discharge | Channed devices medal (CDM) man ACC   | All pins                                        | ±500  | V    |

|                                            |                         | Q100-011                              | Corner pins (1, 10, 11, 20, 21, 30, 31, and 40) | ±750  | V    |

(1) AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

<sup>2)</sup> Continuous high-side gate pin (GHx) and phase node pin voltage (SHx) should be limited to -2 V minimum for an absolute maximum of 65 V on VM. At 60 V and below, the full specification of -5 V continuous on GHx and SHx is allowable.

### 7.3 Recommended Operating Conditions

|                      |                                                                                                | MIN | MAX               | UNIT |

|----------------------|------------------------------------------------------------------------------------------------|-----|-------------------|------|

| GATE DRIV            | ER                                                                                             |     |                   |      |

| \ /                  | Power supply voltage (VM) Continuous                                                           | 5.5 | 50                | V    |

| $V_{VM}$             | Power supply voltage (VM) Transient over voltage (1)                                           | 5.5 | 60                | V    |

| V <sub>I</sub>       | Input voltage (CAL, ENABLE, GAIN, IDRIVE, INHx, INLx, MODE, nSCS, SCLK, SDI, VDS, VSDO, nDIAG) | 0   | 5.5               | V    |

| f <sub>PWM</sub>     | Applied PWM signal (INHx, INLx)                                                                | 0   | 200 (2)           | kHz  |

| I <sub>GATE_HS</sub> | High-side average gate-drive current (GHx)                                                     | 0   | 25 <sup>(2)</sup> | mA   |

| I <sub>GATE_LS</sub> | Low-side average gate-drive current (GLx)                                                      | 0   | 25 <sup>(2)</sup> | mA   |

| I <sub>DVDD</sub>    | External load current (DVDD)                                                                   | 0   | 30 <sup>(2)</sup> | mA   |

| V <sub>VREF</sub>    | Reference voltage input (VREF)                                                                 | 3   | 5.5               | V    |

| V <sub>SDO</sub>     | Push-pull voltage (SDO)                                                                        | 3   | 5.5               | V    |

| V <sub>OD</sub>      | Open drain pullup voltage (nFAULT)                                                             | 0   | 5.5               | V    |

| T <sub>A</sub>       | Operating ambient temperature                                                                  | -40 | 125               | °C   |

<sup>(1)</sup> VM recommended operating condition for electrical characteristic table. Product life time depends on VM voltage. The device is intended for 12–V and 24–V battery automotive system.

#### 7.4 Thermal Information

|                        |                                              | DRV8343-Q1  |      |

|------------------------|----------------------------------------------|-------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | PHP (HTQFP) | UNIT |

|                        |                                              | 48 PINS     |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 26.5        | °C/W |

| $R_{\theta JC(top)}$   | Junction-to-case (top) thermal resistance    | 16.3        | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 6.7         | °C/W |

| ΨЈТ                    | Junction-to-top characterization parameter   | 0.2         | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 6.8         | °C/W |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | 1.0         | °C/W |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

Submit Documentation Feedback

<sup>(2)</sup> Power dissipation and thermal limits must be observed

### 7.5 Electrical Characteristics

Over recommended operating conditions unless otherwise noted. Typical limits apply for  $T_A = 25$ °C and  $V_{VM} = 24$  V

|                       | PARAMETER                         | TEST CONDITIONS                                                                   | MIN      | TYP  | MAX  | UNIT      |

|-----------------------|-----------------------------------|-----------------------------------------------------------------------------------|----------|------|------|-----------|

| POWER SUI             | PPLIES (DVDD, VCP, VM)            |                                                                                   |          |      |      |           |

| I <sub>VM</sub>       | VM operating supply current       | $V_{VM}$ = 24 V, ENABLE = 3.3 V, INHx/INLx = 0 V, SHx = 0 V                       |          | 8    | 14   | mA        |

|                       | VM close mode cumply current      | ENABLE = 0 V, V <sub>VM</sub> = 24 V, T <sub>A</sub> = 25°C                       |          | 12   | 20   |           |

| $I_{VMQ}$             | VM sleep mode supply current      | ENABLE = 0 V, $V_{VM}$ = 24 V, $T_A$ = 125°C <sup>(1)</sup>                       |          |      | 50   | μA        |

| t <sub>RST</sub> (1)  | Reset pulse time                  | ENABLE = 0 V period to reset faults 5                                             |          |      | 40   | μs        |

| t <sub>WAKE</sub> (2) | Turnon time                       | ENABLE = 3.3 V to outputs ready, $V_{VM} > V_{UVLO}$                              |          |      | 1    | ms        |

| t <sub>SLEEP</sub>    | Turnoff time                      | ENABLE = 0 V to device sleep mode                                                 |          |      | 1    | ms        |

| V                     | DV/DD regulator valtage           | $V_{VM} > 6 \text{ V}, I_{DVDD} = 0 \text{ to } 30 \text{ mA}$                    | 3        | 3.3  | 3.6  | V         |

| $V_{DVDD}$            | DVDD regulator voltage            | $V_{VM}$ = 5.5 to 6 V, $I_{DVDD}$ = 0 to 20 mA                                    | 3        | 3.3  | 3.6  | V         |

|                       |                                   | $V_{VM}$ = 13 V, $I_{VCP}$ = 0 to 25 mA                                           | 8.4      | 11   | 12.5 | •         |

| VCP ope               | VCP operating voltage             | $V_{VM}$ = 10 V, $I_{VCP}$ = 0 to 20 mA                                           | 6.3      | 9    | 10   | V         |

| $V_{VCP}$             | with respect to VM                | $V_{VM} = 8 \text{ V}, I_{VCP} = 0 \text{ to } 15 \text{ mA}$                     | 5.4      | 7    | 8    | V         |

|                       |                                   | $V_{VM} = 5.5 \text{ V}, I_{VCP} = 0 \text{ to 5 mA}$                             | 4        | 5    | 6    |           |

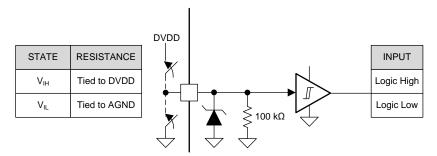

| LOGIC-LEVI            | EL INPUTS (CAL, ENABLE, INHx, INI | Lx, SCLK, SDI)                                                                    | <u> </u> |      |      |           |

| V <sub>IL</sub>       | Input logic low voltage           |                                                                                   | 0        |      | 0.7  | V         |

| V <sub>IH</sub>       | Input logic high voltage          |                                                                                   | 1.6      |      | 5.5  | V         |

| V <sub>HYS</sub>      | Input logic hysteresis            |                                                                                   |          | 100  |      | mV        |

| I <sub>IL</sub>       | Input logic low current           | V <sub>VIN</sub> = 0 V                                                            | -5       |      | 5    | μΑ        |

| I <sub>IH</sub>       | Input logic high current          | V <sub>VIN</sub> = 5 V                                                            |          | 50   | 70   | μA        |

| R <sub>PD</sub>       | Pulldown resistance               | To AGND                                                                           | 100      |      |      | $k\Omega$ |

| t <sub>PD</sub>       | Propagation delay                 | INHx/INLx input buffer and digital core propagation delay. Dead time is excluded. |          | 200  |      | ns        |

| LOGIC LEVI            | EL INPUT (nSCS)                   | •                                                                                 | •        |      | •    | •         |

| V <sub>IL,nSCS</sub>  | Input logic low voltage           |                                                                                   | 0        |      | 0.7  | V         |

| V <sub>IH,nSCS</sub>  | Input logic high voltage          |                                                                                   | 1.6      |      | 5.5  | V         |

| R <sub>PU,nSCS</sub>  | Pullup resistance                 | To DVDD                                                                           |          | 50   |      | kΩ        |

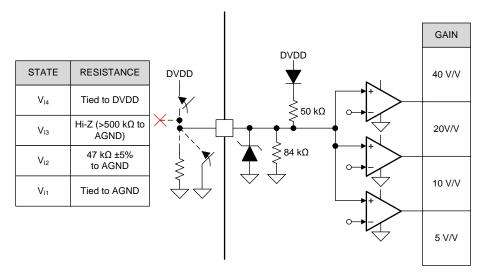

| FOUR-LEVE             | L H/W INPUT (GAIN)                |                                                                                   |          |      | ,    |           |

| V <sub>I1</sub>       | Input mode 1 voltage              | Tied to AGND                                                                      |          | 0    |      | V         |

| V <sub>I2</sub>       | Input mode 2 voltage              | 47 kΩ ± 5% to tied AGND                                                           |          | 1.2  |      | V         |

| V <sub>I3</sub>       | Input mode 3 voltage              | Hi-Z                                                                              |          | 2    |      | V         |

| V <sub>I4</sub>       | Input mode 4 voltage              | Tied to DVDD                                                                      |          | 3.3  |      | V         |

| R <sub>PU</sub>       | Pullup resistance                 | Internal pullup to DVDD                                                           |          | 50   |      | kΩ        |

| R <sub>PD</sub>       | Pulldown resistance               | Internal pulldown to AGND                                                         |          | 84   |      | kΩ        |

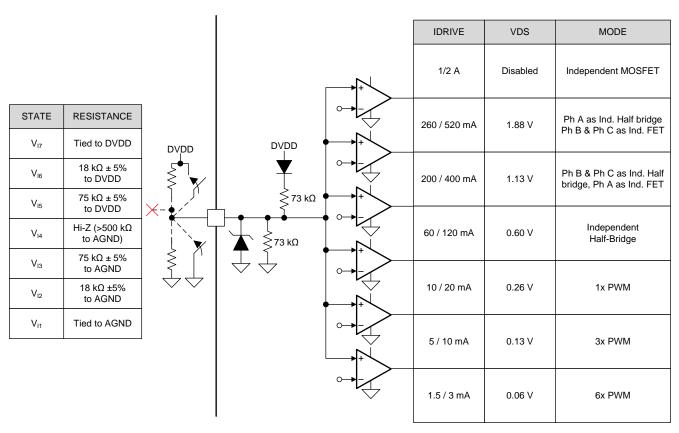

| SEVEN-LEV             | EL H/W INPUTS (MODE, IDRIVE, VD   | S)                                                                                |          |      | '    |           |

| V <sub>I1</sub>       | Input mode 1 voltage              | Tied to AGND                                                                      |          | 0    |      | V         |

| V <sub>I2</sub>       | Input mode 2 voltage              | 18 k $\Omega$ ± 5% tied to AGND                                                   |          | 0.5  |      | V         |

| V <sub>I3</sub>       | Input mode 3 voltage              | 75 k $\Omega$ ± 5% tied to AGND                                                   |          | 1.1  |      | V         |

| V <sub>I4</sub>       | Input mode 4 voltage              | Hi-Z                                                                              |          | 1.65 |      | V         |

| V <sub>I5</sub>       | Input mode 5 voltage              | 75 k $\Omega$ ± 5% tied to DVDD                                                   |          | 2.2  |      | V         |

| V <sub>I6</sub>       | Input mode 6 voltage              | 18 k $\Omega$ ± 5% tied to DVDD                                                   |          | 2.8  |      | V         |

| V <sub>I7</sub>       | Input mode 7 voltage              | Tied to DVDD                                                                      |          | 3.3  |      | V         |

| R <sub>PU</sub>       | Pullup resistance                 | Internal pullup to DVDD                                                           |          | 73   |      | kΩ        |

| R <sub>PD</sub>       | Pulldown resistance               | Internal pulldown to AGND                                                         |          | 73   |      | kΩ        |

|                       | OUTPUT (SDO)                      | <u>'</u>                                                                          | 1        |      |      |           |

<sup>(1)</sup> Specified by design and characterization data

<sup>(2)</sup> Does not include OLP/Shorts diagnostic delay time in the H/W device

Over recommended operating conditions unless otherwise noted. Typical limits apply for  $T_A = 25$ °C and  $V_{VM} = 24$  V

|                                 | PARAMETER                               |               | TEST CONDITIONS                                                           | MIN  | TYP  | MAX  | UNIT |

|---------------------------------|-----------------------------------------|---------------|---------------------------------------------------------------------------|------|------|------|------|

| D                               | latera el mullur                        |               | To VSDO = 5 V                                                             |      | 40   | 65   | 0    |

| $R_{PU,SDO}$                    | Internal pullup                         |               | To VSDO = 3.3 V                                                           |      | 60   | 95   | Ω    |

| R <sub>PD,SDO</sub>             | Internal pulldown                       |               | To GND                                                                    |      | 30   | 50   | Ω    |

| OPEN DRAIN                      | NOUTPUT (nFAULT)                        |               |                                                                           |      |      |      |      |

| V <sub>OL</sub>                 | Output logic low vol                    | tage          | I <sub>O</sub> = 5 mA                                                     |      |      | 0.1  | V    |

| l <sub>OZ</sub>                 | Output high impeda                      | nce leakage   | V <sub>O</sub> = 5 V                                                      | -2   |      | 2    | μΑ   |

| GATE DRIVE                      | ERS (GHx, GLx)                          |               |                                                                           |      |      |      |      |

|                                 |                                         |               | $V_{VM}$ = 13 V, $I_{VCP}$ = 0 to 25 mA, GHx no output load               | 8.4  | 11   | 12.5 |      |

| V <sub>GSH</sub> <sup>(1)</sup> | High-side gate drive                    | -             | V <sub>VM</sub> = 10 , I <sub>VCP</sub> = 0 to 20 mA, GHx no output load  | 6.3  | 9    | 10   | V    |

| 0011                            | with respect to SHx                     |               | V <sub>VM</sub> = 8 V, I <sub>VCP</sub> = 0 to 15 mA, GHx no output load  | 5.4  | 7    | 8    |      |

|                                 |                                         |               | $V_{VM}$ = 5.5 V, $I_{VCP}$ = 0 to 5 mA, GHx no output load               | 4    | 5    | 6    |      |

|                                 |                                         |               | $V_{VM}$ = 12 V, $I_{VCP}$ = 0 to 25 mA, GLx no output load               | 9    | 11   | 12   |      |

| V <sub>GSL</sub> <sup>(1)</sup> | Low-side gate drive with respect to PGN | •             | $V_{VM}$ = 10 V, $I_{VCP}$ = 0 to 20 mA, GLx no output load               | 9.9  | 10.0 | 10.1 | V    |

|                                 |                                         |               | V <sub>VM</sub> = 8 V, I <sub>VCP</sub> = 0 to 15 mA, GLx no output load  | 7.9  | 8.0  | 8.1  |      |

|                                 |                                         |               | V <sub>VM</sub> = 5.5 V, I <sub>VCP</sub> = 0 to 5 mA, GLx no output load | 5.4  | 5.5  | 5.6  |      |

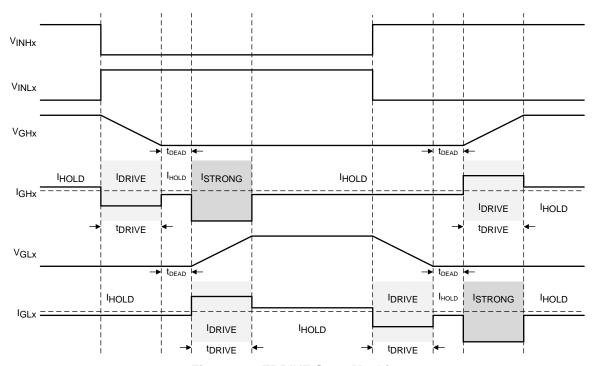

|                                 |                                         |               | DEAD_TIME = 00b                                                           |      | 500  |      |      |

|                                 |                                         | SPI Device    | DEAD_TIME = 01b                                                           |      | 1000 |      |      |

| t <sub>DEAD</sub>               | Gate drive dead time                    | SPI Device    | DEAD_TIME = 10b                                                           |      | 2000 |      | ns   |

|                                 | acaa iiiio                              |               | DEAD_TIME = 11b                                                           |      | 4000 |      |      |

|                                 |                                         | H/W Device    |                                                                           |      | 1000 |      |      |

| t <sub>DRIVE</sub>              |                                         |               | TDRIVE = 00b                                                              |      | 500  |      |      |

|                                 | Da ala assessa d                        | SPI Device    | TDRIVE = 01b                                                              |      | 1000 |      |      |

|                                 | Peak current gate drive time            | OF I DEVICE   | TDRIVE = 10b                                                              | 2000 |      | ns   |      |

|                                 | 34.0 40                                 |               | TDRIVE = 11b                                                              |      | 3000 |      |      |

|                                 |                                         | H/W Device    |                                                                           | 3000 |      |      |      |

| t <sub>DRIVE_MAX</sub>          | Peak current gate of                    | rive max time | IDRIVEP_Hx = 0000b, 0001b, 0010b, 0011b                                   |      | 20   |      | μs   |

0 Submit Documentation Feedback

Over recommended operating conditions unless otherwise noted. Typical limits apply for  $T_A = 25$ °C and  $V_{VM} = 24$  V

|                     | PARAMETER    |            | TEST CONDITIONS                                    |  | TYP  | MAX | UNIT |

|---------------------|--------------|------------|----------------------------------------------------|--|------|-----|------|

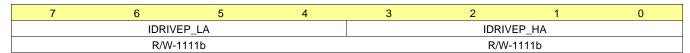

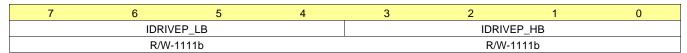

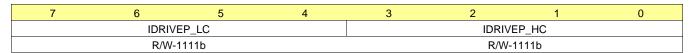

|                     |              |            | IDRIVEP_Hx or IDRIVEP_Lx = 0000b (GHx)             |  | 1.5  |     |      |

|                     |              |            | IDRIVEP_Hx or IDRIVEP_Lx = 0000b (GLx)             |  | 2.7  |     |      |

|                     |              |            | IDRIVEP_Hx or IDRIVEP_Lx = 0001b (GHx)             |  | 3.5  |     |      |

|                     |              |            | IDRIVEP_Hx or IDRIVEP_Lx = 0001b (GLx)             |  | 3.9  |     |      |

|                     |              |            | IDRIVEP_Hx or IDRIVEP_Lx = 0010b (GHx)             |  | 5    |     |      |

|                     |              |            | IDRIVEP_Hx or IDRIVEP_Lx = 0010b (GLx)             |  | 6.5  |     |      |

|                     |              |            | IDRIVEP_Hx or IDRIVEP_Lx = 0011b (GHx/GLx)         |  | 10   |     |      |

|                     |              |            | IDRIVEP_Hx or IDRIVEP_Lx = 0100b (GHx/GLx)         |  | 15   |     |      |

|                     |              |            | IDRIVEP_Hx or IDRIVEP_Lx = 0101b (GHx/GLx)         |  | 50   |     |      |

|                     |              | SPI Device | IDRIVEP_Hx or IDRIVEP_Lx = 0110b (GHx/GLx)         |  | 60   |     |      |

|                     |              |            | IDRIVEP_Hx or IDRIVEP_Lx = 0111b (GHx/GLx)         |  | 65   |     |      |

|                     |              |            | IDRIVEP_Hx or IDRIVEP_Lx = 1000b (GHx/GLx)         |  | 200  |     |      |

|                     |              |            | IDRIVEP_Hx or IDRIVEP_Lx = 1001b (GHx/GLx)         |  | 210  |     | mA   |

| 1                   | Peak source  |            | IDRIVEP_Hx or IDRIVEP_Lx = 1010b (GHx/GLx)         |  | 260  |     |      |

| I <sub>DRIVEP</sub> | gate current |            | IDRIVEP_Hx or IDRIVEP_Lx = 1011b (GHx/GLx)         |  | 265  |     |      |

|                     |              |            | IDRIVEP_Hx or IDRIVEP_Lx = 1100b (GHx/GLx)         |  | 735  |     |      |

|                     |              |            | IDRIVEP_Hx or IDRIVEP_Lx = 1101b (GHx/GLx)         |  | 800  |     |      |

|                     |              |            | IDRIVEP_Hx or IDRIVEP_Lx = 1110b (GHx/GLx)         |  | 935  |     |      |

|                     |              |            | IDRIVEP_Hx or IDRIVEP_Lx = 1111b (GHx/GLx)         |  | 1000 |     |      |

|                     |              |            | IDRIVE = Tied to AGND (GHx)                        |  | 1.5  |     |      |

|                     |              |            | IDRIVE = Tied to AGND (GLx)                        |  | 2.7  |     |      |

|                     |              |            | IDRIVE = 18 k $\Omega$ ± 5% tied to AGND (GHx)     |  | 5    |     |      |

|                     |              |            | IDRIVE = 18 k $\Omega$ ± 5% tied to AGND (GLx)     |  | 6.5  |     |      |

|                     |              | H/W Device | IDRIVE = 75 k $\Omega$ ± 5% tied to AGND (GHx/GLx) |  | 10   |     |      |

|                     |              |            | IDRIVE = Hi-Z (GHx/GLx)                            |  | 60   |     |      |

|                     |              |            | IDRIVE = 75 k $\Omega$ ± 5% tied to DVDD (GHx/GLx) |  | 200  |     |      |

|                     |              |            | IDRIVE = 18 k $\Omega$ ± 5% tied to DVDD (GHx/GLx) |  | 260  |     |      |

|                     |              |            | IDRIVE = Tied to DVDD (GHx/GLx)                    |  | 1000 |     |      |

Over recommended operating conditions unless otherwise noted. Typical limits apply for  $T_A = 25$ °C and  $V_{VM} = 24$  V

|                  | PARAMETER                        |                                       | TEST CONDITIONS                          | MIN TYP | MAX | UNIT |  |

|------------------|----------------------------------|---------------------------------------|------------------------------------------|---------|-----|------|--|

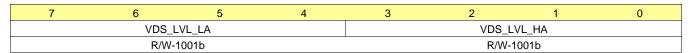

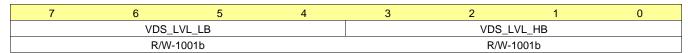

|                  |                                  |                                       | IDRIVEP_Hx or IDRIVEP_Lx = 0000b         | 3       |     |      |  |

|                  |                                  |                                       | IDRIVEP_Hx or IDRIVEP_Lx = 0001b         | 7       |     |      |  |

|                  |                                  |                                       | IDRIVEP_Hx or IDRIVEP_Lx = 0010b         | 10      |     |      |  |

|                  |                                  |                                       | IDRIVEP_Hx or IDRIVEP_Lx = 0011b         | 20      |     |      |  |

|                  |                                  |                                       | IDRIVEP_Hx or IDRIVEP_Lx = 0100b         | 30      |     |      |  |

|                  |                                  |                                       | IDRIVEP_Hx or IDRIVEP_Lx = 0101b         | 100     |     |      |  |

|                  |                                  |                                       | IDRIVEP_Hx or IDRIVEP_Lx = 0110b         | 120     |     |      |  |

|                  |                                  |                                       | IDRIVEP_Hx or IDRIVEP_Lx = 0111b         | 130     |     |      |  |

|                  |                                  | SPI Device                            | IDRIVEP_Hx or IDRIVEP_Lx = 1000b         | 400     |     |      |  |

|                  |                                  |                                       | IDRIVEP Hx or IDRIVEP Lx = 1001b         | 420     |     |      |  |

|                  |                                  |                                       | IDRIVEP_Hx or IDRIVEP_Lx = 1010b         | 520     |     |      |  |

| DRIVEN           | Peak sink                        |                                       | IDRIVEP_Hx or IDRIVEP_Lx = 1011b         | 530     |     | mA   |  |

| DRIVEN           | gate current                     |                                       | IDRIVEP_Hx or IDRIVEP_Lx = 1100b         | 1470    |     |      |  |

|                  |                                  |                                       | IDRIVEP_Hx or IDRIVEP_Lx = 1101b         | 1600    |     |      |  |

|                  |                                  |                                       | IDRIVEP_Hx or IDRIVEP_Lx = 1110b         | 1870    |     |      |  |

|                  |                                  | IDR IDR IDR IDR IDR IDR IDR IDR IDR   | IDRIVEP_Hx or IDRIVEP_Lx = 1111b         | 2000    |     |      |  |

|                  |                                  |                                       | IDRIVE = Tied to AGND                    | 3       |     |      |  |

|                  |                                  |                                       |                                          |         |     |      |  |

|                  |                                  |                                       | IDRIVE = 18 k $\Omega$ ± 5% tied to AGND | 10      |     |      |  |

|                  |                                  |                                       | IDRIVE = 75 k $\Omega$ ± 5% tied to AGND | 20      |     |      |  |

|                  |                                  |                                       |                                          | 120     |     |      |  |

|                  |                                  |                                       | IDRIVE = 75 k $\Omega$ ± 5% tied to DVDD | 400     |     |      |  |

|                  |                                  |                                       | IDRIVE = 18 kΩ ± 5% tied to DVDD         | 520     |     |      |  |

|                  |                                  |                                       | IDRIVE = Tied to DVDD                    | 2000    |     |      |  |

|                  |                                  |                                       | IDRIVEP_Hx = 0000b                       | 1.5     |     |      |  |

|                  |                                  |                                       | IDRIVEP_Hx = 0001b                       | 3.5     |     |      |  |

|                  |                                  | SPI Device                            | IDRIVEP_Hx = 0010b                       | 5       |     |      |  |

|                  | Gate holding                     |                                       | IDRIVEP_Hx = 0011b                       | 10      |     |      |  |

| HOLDP            | source current                   |                                       | All other IDRIVE settings                | 15      |     | mA   |  |

|                  | after t <sub>DRIVE</sub>         |                                       | IDRIVE tied to AGND                      | 1.5     |     |      |  |

|                  |                                  | H/W Device                            | IDRIVE = 18 k $\Omega$ ± 5% tied to AGND | 5       |     |      |  |

|                  |                                  | n/w Device                            | IDRIVE = 75 k $\Omega$ ± 5% tied to AGND | 10      |     |      |  |

|                  |                                  |                                       | All other IDRIVE settings                | 15      |     |      |  |

|                  |                                  |                                       | IDRIVEP_Hx = 0000b                       | 3       |     |      |  |

|                  |                                  |                                       | IDRIVEP_Hx = 0001b                       | 7       |     |      |  |

|                  |                                  | SPI Device                            | IDRIVEP_Hx = 0010b                       | 10      |     |      |  |

|                  |                                  |                                       | IDRIVEP_Hx = 0011b                       | 20      |     |      |  |

| HOLDN            | Gate holding sink                |                                       | All other IDRIVE settings                | 30      |     | mA   |  |

|                  | current after t <sub>DRIVE</sub> |                                       | IDRIVE tied to AGND                      | 3       |     |      |  |

|                  |                                  |                                       | IDRIVE = 18 kΩ ± 5% tied to AGND         | 10      |     |      |  |

|                  |                                  | H/W Device                            | IDRIVE = 75 kΩ ± 5% tied to AGND         | 20      |     |      |  |

|                  |                                  |                                       | All other IDRIVE settings                | 30      |     |      |  |

|                  | Gate strong pulldow              | n current                             | IDRIVEP Hx = 0000b, 0001b, 0010b, 0011b  | 30      |     | mA   |  |

| STRONG           | (GHx to SHx and GI               |                                       | All other IDRIVE settings                | 2       |     | A    |  |

| R <sub>OFF</sub> | Gate hold off resisto            | · · · · · · · · · · · · · · · · · · · | GHx to SHx and GLx to PGND               | 150     |     | kΩ   |  |

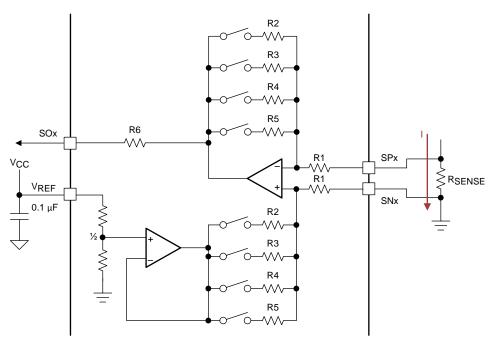

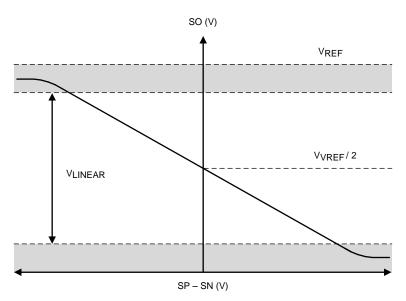

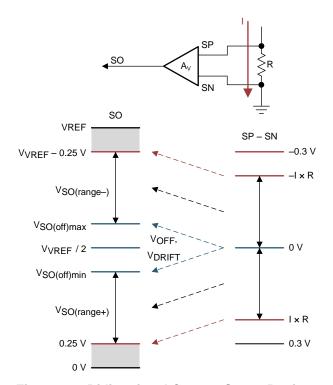

|                  | SHUNT AMPLIFIER (SNx,            |                                       |                                          | 130     |     | L/7  |  |

Submit Documentation Feedback

www.ti.com

### **Electrical Characteristics (continued)**

Over recommended operating conditions unless otherwise noted. Typical limits apply for  $T_A = 25$ °C and  $V_{VM} = 24$  V

|                        | PARAMETER                 |               | TEST CONDITIONS                                                                          | MIN                   | TYP                   | MAX                      | UNIT  |  |

|------------------------|---------------------------|---------------|------------------------------------------------------------------------------------------|-----------------------|-----------------------|--------------------------|-------|--|

|                        | TANAMETER                 |               | CSA_GAIN = 00b, CSA_FET = 0b                                                             | 4.9                   | 5                     | 5.1                      | Oldii |  |

|                        |                           |               | CSA_GAIN = 01b, CSA_FET = 0b                                                             | 9.8                   | 10                    | 10.2                     |       |  |

|                        |                           | SPI Device    | CSA_GAIN = 10b, CSA_FET = 0b                                                             | 19.6                  | 20                    | 20.4                     |       |  |

|                        |                           |               | CSA_GAIN = 10b, CSA_FET = 0b                                                             | 39.2                  | 40                    | 40.8                     |       |  |

|                        |                           |               | CSA_GAIN = 00b, CSA_FET = 1b                                                             | 4.85                  | 5                     | 5.15                     |       |  |

|                        |                           |               | CSA_GAIN = 01b, CSA_FET = 1b                                                             | 9.7                   | 10                    | 10.3                     |       |  |

| G <sub>CSA</sub>       | Amplifier gain            | SPI Device    | CSA GAIN = 10b, CSA FET = 1b                                                             | 19.4                  | 20                    | 20.6                     | V/V   |  |

|                        |                           |               | CSA GAIN = 11b, CSA FET = 1b                                                             | 38.8                  | 40                    | 41.2                     |       |  |

|                        |                           |               | GAIN = Tied to AGND                                                                      | 4.9                   | 5                     | 5.1                      |       |  |

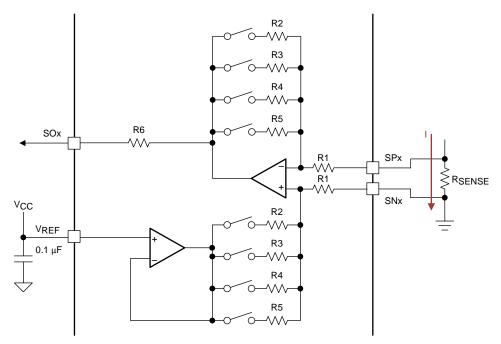

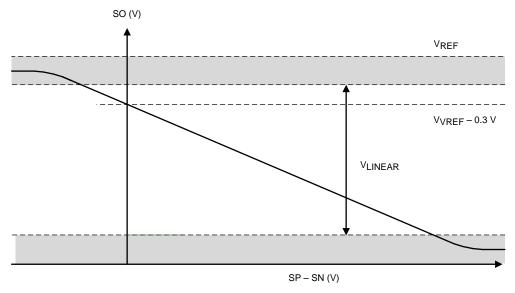

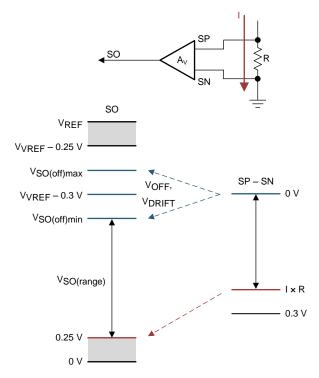

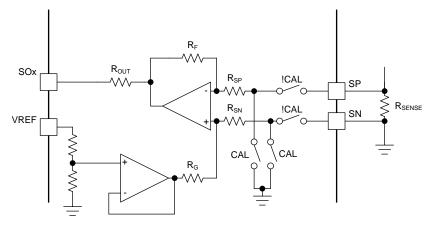

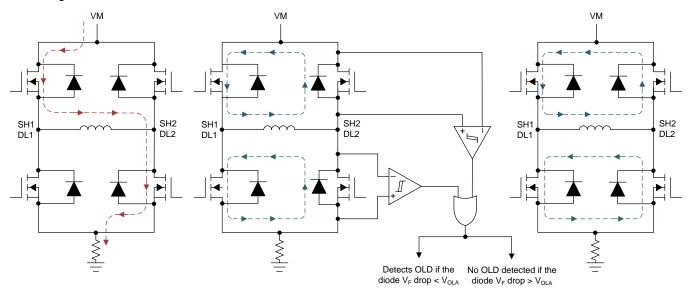

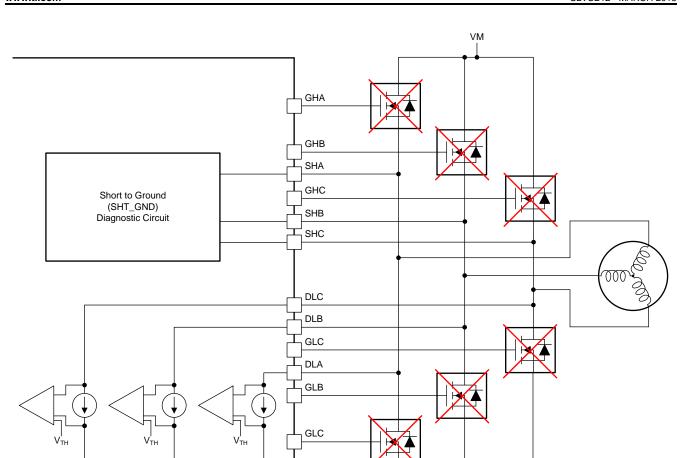

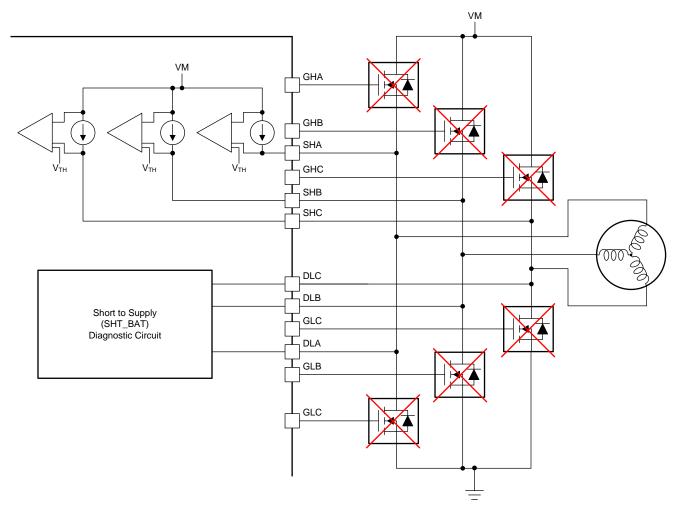

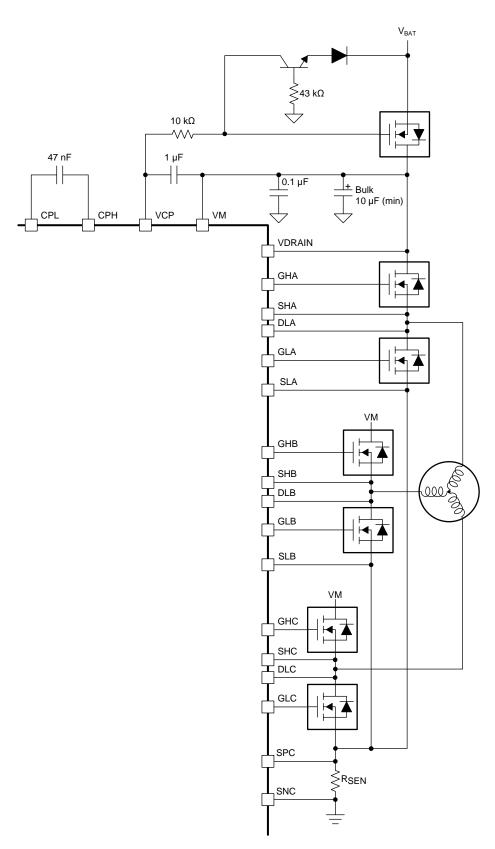

|                        |                           |               | GAIN = $47 \text{ k}\Omega \pm 5\%$ tied to AGND                                         | 9.8                   | 10                    | 10.2                     |       |  |