# ANALOG Linear Li-Ion Battery Charger with Power DEVICES Path and IICR Compatibility in LEGER Path and USB Compatibility in LFCSP

**ADP5062 Data Sheet**

#### **FEATURES**

4 mm × 4 mm LFCSP package Fully programmable via I<sup>2</sup>C Flexible digital control inputs Up to 2.1 A current from an ac charger in LDO mode Operating input voltage from 4.0 V to 6.7 V Tolerant input voltage from -0.5 V to +20 V (USB VBUS) Fully compatible with USB 3.0 and USB Battery Charging Specification 1.2

**Built-in current sensing and limiting**

As low as 54 m $\Omega$  battery isolation FET between battery and charger output

Thermal regulation prevents overheating

Compliant with JEITA 1 and JEITA 2 Li-lon battery charging temperature specifications

SYS\_EN flag permits the system to be disabled until battery is at the minimum required level for guaranteed system start-up

#### **APPLICATIONS**

Digital still cameras Digital video cameras Single cell Li-Ion portable equipment PDAs, audio, and GPS devices Portable medical devices **Mobile phones**

#### GENERAL DESCRIPTION

The ADP5062 charger is fully compliant with USB 3.0 and the USB Battery Charging Specification 1.2 and enables charging via the mini USB VBUS pin from a wall charger, car charger, or USB host port.

The ADP5062 operates from a 4 V to 6.7 V input voltage range but is tolerant of voltages up to 20 V thereby alleviating concerns about USB bus spikes during disconnect or connect scenarios.

The ADP5062 features an internal FET between the linear charger output and the battery. This permits battery isolation and, hence, system powering under a dead battery or no battery scenario, which allows for immediate system function on connection to a USB power supply.

Based on the type of USB source, which is detected by an external USB detection chip, the ADP5062 can be set to apply the correct current limit for optimal charging and USB compliance.

The ADP5062 has three factory-programmable digital input/output pins that provide maximum flexibility for different systems. These digital input/output pins permit combinations of features such as, input current limits, charging enable and disable, charging current limits, and a dedicated interrupt output pin.

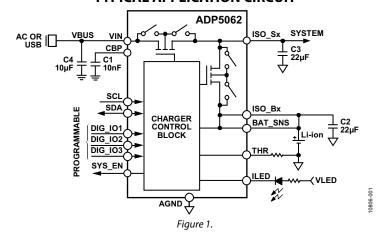

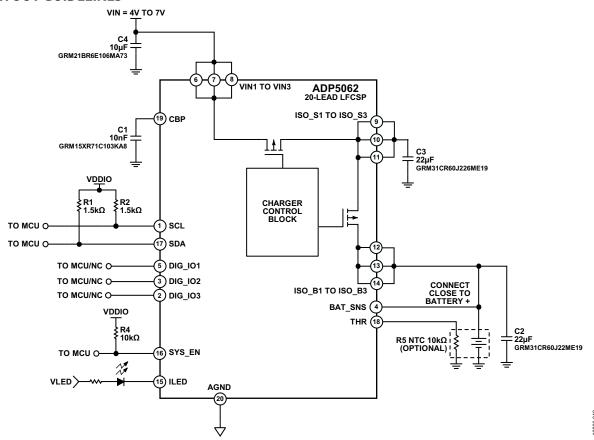

#### TYPICAL APPLICATION CIRCUIT

## **TABLE OF CONTENTS**

| Features 1                                                   |

|--------------------------------------------------------------|

| Applications                                                 |

| General Description                                          |

| Typical Application Circuit                                  |

| Revision History                                             |

| Specifications                                               |

| Recommended Input and Output Capacitances6                   |

| I <sup>2</sup> C-Compatible Interface Timing Specifications6 |

| Absolute Maximum Ratings 8                                   |

| Thermal Resistance                                           |

| ESD Caution8                                                 |

| Pin Configuration and Function Descriptions9                 |

| Typical Performance Characteristics                          |

| Temperature Characteristics                                  |

| Typical Waveforms14                                          |

| Theory of Operation                                          |

| Summary of Operation Modes15                                 |

| Introduction                                                 |

| Charger Modes18                                              |

| Thermal Management                                           |

| DEVISION LISTORY                                             |

| REVISION HISTORY                                             |

| 10/13—Rev. A to Rev. B                                       |

| Changes to Table 19                                          |

| Changes to Table 20                                          |

| Changes to Ordering Guide                                    |

| 4/13—Rev. 0 to Rev. A                                        |

| Changes to Figure 3                                          |

| 9/12—Revision 0: Initial Version                             |

| Battery Isolation FET                        | 21 |

|----------------------------------------------|----|

| Battery Detection                            | 21 |

| Battery Pack Temperature Sensing             | 22 |

| I <sup>2</sup> C Interface                   | 26 |

| I <sup>2</sup> C Register Map                | 27 |

| Register Bit Descriptions                    | 28 |

| Applications Information                     | 36 |

| External Components                          | 36 |

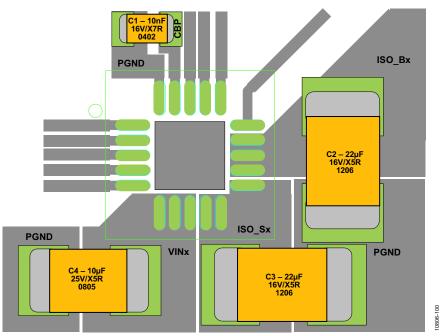

| PCB Layout Guidelines                        | 38 |

| Power Dissipation and Thermal Considerations | 39 |

| Charger Power Dissipation                    | 39 |

| Junction Temperature                         | 39 |

| Factory-Programmable Options                 | 40 |

| Charger Options                              | 40 |

| I <sup>2</sup> C Register Defaults           | 41 |

| Digital Input and Output Options             | 41 |

| Packaging and Ordering Information           | 43 |

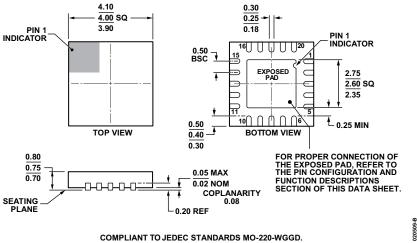

| Outline Dimensions                           | 43 |

| Ordering Guide                               | 43 |

## **SPECIFICATIONS**

$-40^{\circ}C < T_{J} < +125^{\circ}C, \ V_{VINx} = 5.0 \ V, \ R_{HOT\_RISE} < R_{THR} < R_{COLD\_FALL}, \ V_{BAT\_SNS} = 3.6 \ V, \ V_{ISO\_Bx} = V_{BAT\_SNS}, \ C_{VIN} = 10 \ \mu\text{F}, \ C_{ISO\_S} = 22 \ \mu\text{F}, \ C_{ISO\_B} = 22 \ \mu\text{F}, \ C_{COLD\_FALL}, \ V_{COLD\_FALL}, \$

Table 1.

| Parameter                                         | Symbol                 | Min   | Тур                       | Max   | Unit | Test Conditions/Comments                                                                                                                                                                                                |

|---------------------------------------------------|------------------------|-------|---------------------------|-------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GENERAL PARAMETERS                                |                        |       |                           |       |      |                                                                                                                                                                                                                         |

| Undervoltage Lockout                              | V <sub>UVLO</sub>      | 2.25  | 2.35                      | 2.5   | V    | Falling threshold, higher of V <sub>VINx</sub> and V <sub>BAT_SNS</sub> <sup>1</sup>                                                                                                                                    |

| Hysteresis                                        |                        | 50    | 100                       | 150   | mV   | Hysteresis, higher of V <sub>VINx</sub> and V <sub>BAT_SNS</sub> rising <sup>1</sup>                                                                                                                                    |

| Total Input Current                               | I <sub>LIM</sub>       | 74    | 92                        | 100   | mA   | Nominal USB initialized current level <sup>2</sup>                                                                                                                                                                      |

| ·                                                 |                        | 114   |                           | 150   | mA   | USB super speed                                                                                                                                                                                                         |

|                                                   |                        |       |                           | 300   | mA   | USB enumerated current level (specification for China)                                                                                                                                                                  |

|                                                   |                        | 425   | 470                       | 500   | mA   | USB enumerated current level                                                                                                                                                                                            |

|                                                   |                        |       |                           | 900   | mA   | Dedicated charger input                                                                                                                                                                                                 |

|                                                   |                        |       |                           | 1500  | mA   | Dedicated wall charger                                                                                                                                                                                                  |

| VINx Current Consumption                          | I <sub>QVIN</sub>      |       | 2                         |       | mA   | Charging or LDO mode                                                                                                                                                                                                    |

| ·                                                 | I <sub>QVIN DIS</sub>  |       | 280                       | 450   | μΑ   | DIS_IC1 = high, V <sub>ISO_Bx</sub> < VINx < 5.5 V                                                                                                                                                                      |

| Battery Current Consumption                       | I <sub>QBATT</sub>     |       | 20                        |       | μA   | LDO mode, V <sub>ISO Sx</sub> > V <sub>BAT SNS</sub>                                                                                                                                                                    |

| ·                                                 |                        |       |                           | 5     | μA   | Standby, includes ISO_Sx pin leakage, $V_{VINx} = 0 V$ , $T_J = -40^{\circ}C$ to $+85^{\circ}C$                                                                                                                         |

|                                                   |                        |       | 0.5                       | 0.9   | mA   | Standby, battery monitor active                                                                                                                                                                                         |

| CHARGER                                           |                        |       |                           |       |      |                                                                                                                                                                                                                         |

| Fast Charge Current CC Mode                       | Існ                    | 700   | 750                       | 790   | mA   | $V_{ISO\_Bx} = 3.9 \text{ V}$ ; fast charge current accuracy is guaranteed at temperatures from $T_J = -40^{\circ}\text{C}$ to the isothermal regulation limit (typically $T_J = +115^{\circ}\text{C}$ ) <sup>2,3</sup> |

| Fast Charge Current Accuracy                      |                        | -8    |                           | +7    | %    | I <sub>CHG</sub> = 400 mA to 1300 mA                                                                                                                                                                                    |

|                                                   |                        | -33   |                           | +29   | mA   | I <sub>CHG</sub> = 250 mA to 350 mA                                                                                                                                                                                     |

|                                                   |                        | -45   |                           | +40   | mA   | I <sub>CHG</sub> = 50 mA to 200 mA                                                                                                                                                                                      |

| Trickle Charge Current <sup>2</sup>               | I <sub>TRK_DEAD</sub>  | 16    | 20                        | 25    | mA   |                                                                                                                                                                                                                         |

| Weak Charge Current <sup>2, 3</sup>               | I <sub>CHG_WEAK</sub>  |       | $I_{TRK\_DEAD} + I_{CHG}$ |       | mA   |                                                                                                                                                                                                                         |

| Trickle to Weak Charge Threshold                  |                        |       |                           |       |      |                                                                                                                                                                                                                         |

| Dead Battery                                      | V <sub>TRK_DEAD</sub>  | 2.4   | 2.5                       | 2.6   | V    | V <sub>TRK_DEAD</sub> < V <sub>BAT_SNS</sub> < V <sub>WEAK</sub> <sup>2, 4</sup>                                                                                                                                        |

| Hysteresis                                        | ΔV <sub>TRK_DEAD</sub> |       | 100                       |       | mV   | On BAT_SNS <sup>2</sup>                                                                                                                                                                                                 |

| Weak Battery Threshold                            |                        |       |                           |       |      |                                                                                                                                                                                                                         |

| Weak to Fast Charge Threshold                     | V <sub>WEAK</sub>      | 2.89  | 3.0                       | 3.11  | V    | On BAT_SNS <sup>2,4</sup>                                                                                                                                                                                               |

|                                                   | $\Delta V_{WEAK}$      |       | 100                       |       | mV   |                                                                                                                                                                                                                         |

| Battery Termination Voltage                       | V <sub>TRM</sub>       |       | 4.200                     |       | V    |                                                                                                                                                                                                                         |

| Termination Voltage Accuracy                      |                        | -0.25 |                           | +0.25 | %    | On BAT_SNS, $T_J = 25^{\circ}\text{C}$ , $I_{END} = 52.5 \text{ mA}^2$                                                                                                                                                  |

|                                                   |                        | -1.04 |                           | +0.89 | %    | $T_{J} = 0^{\circ}C \text{ to } 115^{\circ}C^{2}$                                                                                                                                                                       |

|                                                   |                        | -1.16 |                           | +1.20 | %    | $T_J = -40^{\circ}\text{C to} + 125^{\circ}\text{C}$                                                                                                                                                                    |

| Battery Overvoltage Threshold                     | V <sub>BATOV</sub>     |       | $V_{IN} - 0.075$          |       | V    | Relative to VINx voltage, BAT_SNS rising                                                                                                                                                                                |

| Charge Complete Current                           | I <sub>END</sub>       | 15    | 52.5                      | 98    | mA   | V <sub>RAT SNS</sub> = V <sub>TRM</sub>                                                                                                                                                                                 |

| Charging Complete Current Threshold<br>Accuracy   |                        | 17    |                           | 83    | mA   | $I_{END} = 52.5 \text{ mA, } T_J = 0^{\circ}\text{C to } 115^{\circ}\text{C}^2$                                                                                                                                         |

|                                                   |                        | 59    |                           | 123   | mA   | $I_{END} = 92.5 \text{ mA}, T_J = 0^{\circ}\text{C to } 115^{\circ}\text{C}$                                                                                                                                            |

| Recharge Voltage Differential                     | $V_{RCH}$              | 160   | 260                       | 390   | mV   | Relative to V <sub>TRM</sub> , BAT_SNS falling <sup>2</sup>                                                                                                                                                             |

| Battery Node Short Threshold Voltage <sup>2</sup> | V <sub>BAT_SHR</sub>   | 2.2   | 2.4                       | 2.5   | V    |                                                                                                                                                                                                                         |

| Battery Short Detection Current                   | I <sub>TRK_SHORT</sub> |       | 20                        |       | mA   | $I_{TRK\_SHORT} = I_{TRK\_DEAD}^2$                                                                                                                                                                                      |

| Charging Start Voltage Limit                      | V <sub>CHG_VLIM</sub>  | 3.6   | 3.7                       | 3.8   | V    | Voltage limit is not active by default                                                                                                                                                                                  |

| Charging Soft Start Current                       | I <sub>CHG</sub> START | 185   | 260                       | 365   | mA   | V <sub>BAT</sub> SNS > V <sub>TRK</sub> DEAD                                                                                                                                                                            |

| Charging Soft Start Timer                         | t <sub>CHG_START</sub> |       | 3                         |       | ms   |                                                                                                                                                                                                                         |

| Parameter                                                             | Symbol                      | Min    | Тур    | Max    | Unit | Test Conditions/Comments                                                              |

|-----------------------------------------------------------------------|-----------------------------|--------|--------|--------|------|---------------------------------------------------------------------------------------|

| BATTERY ISOLATION FET                                                 |                             |        |        |        |      |                                                                                       |

| Pin to Pin Resistance Between ISO_Sx and ISO_Bx                       | R <sub>DSON_ISO</sub>       |        | 54     | 89     | mΩ   | On battery supplement mode, VINx = 0 V, $V_{ISO\_Bx}$ = 4.2 V, $I_{ISO\_Bx}$ = 500 mA |

| Regulated System Voltage: VBAT Low                                    | V <sub>ISO_SFC</sub>        | 3.6    | 3.8    | 4.0    | V    | VTRM[5:0] programming ≥ 4.00 V                                                        |

|                                                                       |                             | 3.2    | 3.4    | 3.5    | V    | VTRM[5:0] programming < 4.00 V                                                        |

| Battery Supplementary Threshold                                       | V <sub>THISO</sub>          | 0      | 5      | 12     | mV   | $V_{ISO\_Sx} < V_{ISO\_Bx}$ , $V_{SYS}$ rising                                        |

| LDO AND HIGH VOLTAGE BLOCKING                                         |                             |        |        |        |      |                                                                                       |

| Regulated System Voltage                                              | V <sub>ISO_STRK</sub>       | 4.214  | 4.3    | 4.386  | V    | VSYSTEM[2:0] = 000 (binary) = 4.3 V, $I_{ISO\_Sx}$ = 100 mA, LDO mode <sup>2</sup>    |

| Load Regulation                                                       |                             |        | -0.56  |        | %/A  | $I_{ISO_Sx} = 0 \text{ m A to } 1500 \text{ mA}$                                      |

| High Voltage Blocking FET (LDO FET) On Resistance                     | R <sub>DS(ON)HV</sub>       |        | 330    | 485    | mΩ   | $I_{MNx} = 500 \text{ mA}$                                                            |

| Maximum Output Current                                                |                             |        | 2.1    |        | Α    | $V_{ISO\_Sx} = 4.3 \text{ V, LDO mode}$                                               |

| VINx Input Voltage, Good Threshold<br>Rising                          | V <sub>VIN_OK_RISE</sub>    | 3.75   | 3.9    | 4.0    | V    |                                                                                       |

| VINx Falling                                                          | V <sub>VIN_OK_FALL</sub>    |        | 3.6    | 3.7    | V    |                                                                                       |

| VINx Input Overvoltage Threshold                                      | V <sub>VIN_OV</sub>         | 6.7    | 6.9    | 7.2    | V    |                                                                                       |

| Hysteresis                                                            | $\Delta V_{\text{VIN\_OV}}$ |        | 0.1    |        | V    |                                                                                       |

| VINx Transition Timing                                                | T <sub>VIN_RISE</sub>       | 10     |        |        | μs   | Minimum rise time for VINx from 5 V to 20 V                                           |

|                                                                       | T <sub>VIN_FALL</sub>       | 10     |        |        | μs   | Minimum fall time for VINx from 4 V to 0 V                                            |

| THERMAL CONTROL                                                       |                             |        |        |        |      |                                                                                       |

| Isothermal Charging Temperature                                       | T <sub>LIM</sub>            |        | 115    |        | °C   |                                                                                       |

| Thermal Early Warning Temperature                                     | T <sub>SDL</sub>            |        | 130    |        | °C   |                                                                                       |

| Thermal Shutdown Temperature                                          | T <sub>SD</sub>             |        | 140    |        | °C   | T <sub>J</sub> rising                                                                 |

|                                                                       |                             |        | 110    |        | °C   | T <sub>J</sub> falling                                                                |

| THERMISTOR CONTROL                                                    |                             |        |        |        |      |                                                                                       |

| Thermistor Current                                                    |                             |        |        |        |      |                                                                                       |

| 10,000 NTC                                                            | I <sub>NTC_10k</sub>        |        |        | 400    | μΑ   |                                                                                       |

| 100,000 NTC                                                           | I <sub>NTC_100k</sub>       |        |        | 40     | μΑ   |                                                                                       |

| Thermistor Capacitance                                                | C <sub>NTC</sub>            |        | 100    |        | pF   |                                                                                       |

| Cold Temperature Threshold                                            | T <sub>NTC_COLD</sub>       |        | 0      |        | ℃    | No battery charging occurs                                                            |

| Resistance Thresholds                                                 |                             |        |        |        |      |                                                                                       |

| Cool to Cold Resistance                                               | R <sub>COLD_FALL</sub>      | 20,500 | 25,600 | 30,720 | Ω    |                                                                                       |

| Cold to Cool Resistance                                               | R <sub>COLD_RISE</sub>      |        | 24,400 |        | Ω    |                                                                                       |

| Hot Temperature Threshold                                             | T <sub>NTC_HOT</sub>        |        | 60     |        | °C   | No battery charging occurs                                                            |

| Resistance Thresholds                                                 |                             |        |        |        | _    |                                                                                       |

| Hot to Typical Resistance                                             | RHOT_FALL                   |        | 3700   |        | Ω    |                                                                                       |

| Typical to Hot Resistance                                             | R <sub>HOT_RISE</sub>       | 2750   | 3350   | 3950   | Ω    |                                                                                       |

| JEITA1 LI-ION BATTERY CHARGING<br>SPECIFICATION DEFAULTS <sup>5</sup> |                             |        |        |        |      |                                                                                       |

| JEITA Cold Temperature                                                | T <sub>JEITA_COLD</sub>     |        | 0      |        | °C   | No battery charging occurs                                                            |

| Resistance Thresholds                                                 |                             | 20.555 | 25.622 | 20     |      |                                                                                       |

| Cool to Cold Resistance                                               | R <sub>COLD_FALL</sub>      | 20,500 | 25,600 | 30,720 | Ω    |                                                                                       |

| Cold to Cool Resistance                                               | R <sub>COLD_RISE</sub>      |        | 24,400 |        | Ω    |                                                                                       |

| JEITA Cool Temperature                                                | T <sub>JEITA_COOL</sub>     |        | 10     |        | ℃    | Battery charging occurs at 50% of programmed level                                    |

| Resistance Thresholds                                                 |                             |        |        |        |      |                                                                                       |

| Typical to Cool Resistance                                            | R <sub>TYP_FALL</sub>       | 13,200 | 16,500 | 19,800 | Ω    |                                                                                       |

| Cool to Typical Resistance                                            | R <sub>TYP_RISE</sub>       |        | 15,900 |        | Ω    |                                                                                       |

| JEITA Warm Temperature                                                | T <sub>JEITA_WARM</sub>     |        | 45     |        | ℃    | Battery termination voltage (V <sub>TRM</sub> ) is reduced by 100 mV                  |

| Resistance Thresholds                                                 |                             |        |        |        |      |                                                                                       |

| Warm to Typical Resistance                                            | R <sub>WARM_FALL</sub>      |        | 5800   |        | Ω    |                                                                                       |

| Typical to Warm Resistance                                            | Rwarm_rise                  | 4260   | 5200   | 6140   | Ω    |                                                                                       |

| Parameter                                                             | Symbol                  | Min    | Тур    | Max    | Unit | Test Conditions/Comments                                                |

|-----------------------------------------------------------------------|-------------------------|--------|--------|--------|------|-------------------------------------------------------------------------|

| JEITA Hot Temperature                                                 | T <sub>JEITA_HOT</sub>  |        | 60     |        | °C   | No battery charging occurs                                              |

| Resistance Thresholds                                                 |                         |        |        |        |      |                                                                         |

| Hot to Warm Resistance                                                | R <sub>HOT_FALL</sub>   |        | 3700   |        | Ω    |                                                                         |

| Warm to Hot Resistance                                                | R <sub>HOT_RISE</sub>   | 2750   | 3350   | 3950   | Ω    |                                                                         |

| JEITA2 LI-ION BATTERY CHARGING<br>SPECIFICATION DEFAULTS <sup>5</sup> |                         |        |        |        |      |                                                                         |

| JEITA Cold Temperature                                                | T <sub>JEITA_COLD</sub> |        | 0      |        | °C   | No battery charging occurs                                              |

| Resistance Thresholds                                                 |                         |        |        |        |      |                                                                         |

| Cool to Cold Resistance                                               | R <sub>COLD_FALL</sub>  | 20,500 | 25,600 | 30,720 | Ω    |                                                                         |

| Cold to Cool Resistance                                               | R <sub>COLD_RISE</sub>  |        | 24,400 |        | Ω    |                                                                         |

| JEITA Cool Temperature                                                | T <sub>JEITA_COOL</sub> |        | 10     |        | ℃    | Battery termination voltage (V <sub>TRM</sub> ) is reduced by 100 mV    |

| Resistance Thresholds                                                 |                         |        |        |        |      |                                                                         |

| Typical to Cool Resistance                                            | R <sub>TYP_FALL</sub>   | 13,200 | 16,500 | 19,800 | Ω    |                                                                         |

| Cool to Typical Resistance                                            | R <sub>TYP_RISE</sub>   |        | 15,900 |        | Ω    |                                                                         |

| JEITA Warm Temperature                                                | T <sub>JEITA_WARM</sub> |        | 45     |        | ℃    | Battery termination voltage (V <sub>TRM</sub> ) is reduced by 100 mV    |

| Resistance Thresholds                                                 |                         |        |        |        |      |                                                                         |

| Warm to Typical Resistance                                            | R <sub>WARM_FALL</sub>  |        | 5800   |        | Ω    |                                                                         |

| Typical to Warm Resistance                                            | Rwarm_rise              | 4260   | 5200   | 6140   | Ω    |                                                                         |

| JEITA Hot Temperature                                                 | T <sub>JEITA_HOT</sub>  |        | 60     |        | °C   | No battery charging occurs                                              |

| Resistance Thresholds                                                 |                         |        |        |        |      |                                                                         |

| Hot to Warm Resistance                                                | R <sub>HOT_FALL</sub>   |        | 3700   |        | Ω    |                                                                         |

| Warm to Hot Resistance                                                | R <sub>HOT_RISE</sub>   | 2750   | 3350   | 3950   | Ω    |                                                                         |

| BATTERY DETECTION                                                     |                         |        |        |        |      |                                                                         |

| Sink Current                                                          | Isink                   | 13     | 20     | 34     | mA   |                                                                         |

| Source Current                                                        | Isource                 | 7      | 10     | 13     | mA   |                                                                         |

| Battery Threshold                                                     |                         |        |        |        |      |                                                                         |

| Low                                                                   | V <sub>BATL</sub>       | 1.8    | 1.9    | 2.0    | V    |                                                                         |

| High                                                                  | V <sub>BATH</sub>       |        | 3.4    |        | V    |                                                                         |

| Battery Detection Timer                                               | <b>t</b> BATOK          |        | 333    |        | ms   |                                                                         |

| TIMERS                                                                |                         |        |        |        |      |                                                                         |

| Clock Oscillator Frequency                                            | f <sub>CLK</sub>        | 2.7    | 3      | 3.3    | MHz  |                                                                         |

| Start Charging Delay                                                  | t <sub>START</sub>      |        | 1      |        | sec  |                                                                         |

| Trickle Charge                                                        | t <sub>TRK</sub>        |        | 60     |        | min  |                                                                         |

| Fast Charge                                                           | t <sub>CHG</sub>        |        | 600    |        | min  |                                                                         |

| Charge Complete                                                       | t <sub>END</sub>        |        | 7.5    |        | min  | $V_{BAT\_SNS} = V_{TRM}$ , $I_{CHG} < I_{END}$                          |

| Deglitch                                                              | t <sub>DG</sub>         |        | 31     |        | ms   | Applies to Vtrk_dead, Vrch, Iend, Vweak, Vvin_ok_rise, and Vvin_ok_fall |

| Watchdog <sup>2</sup>                                                 | t <sub>wD</sub>         |        | 32     |        | sec  |                                                                         |

| Safety                                                                | t <sub>SAFE</sub>       | 36     | 40     | 44     | min  |                                                                         |

| Battery Short <sup>2</sup>                                            | t <sub>BAT_SHR</sub>    |        | 30     |        | sec  |                                                                         |

| ILED OUTPUT PINS                                                      |                         |        |        |        |      |                                                                         |

| Voltage Drop over ILED                                                | VILED                   |        | 200    |        | mV   | I <sub>ILED</sub> = 20 mA                                               |

| Maximum Operating Voltage over ILED                                   | V <sub>MAXILED</sub>    |        |        | 5.5    | V    |                                                                         |

| SYS_EN OUTPUT PIN                                                     |                         |        |        |        |      |                                                                         |

| SYS_EN FET On Resistance                                              | R <sub>ON_SYS_EN</sub>  |        | 10     |        | Ω    | $I_{SYS EN} = 20 \text{ mA}$                                            |

| Parameter                         | Symbol               | Min | Тур | Max | Unit | Test Conditions/Comments                       |

|-----------------------------------|----------------------|-----|-----|-----|------|------------------------------------------------|

| LOGIC INPUT PINS                  |                      |     |     |     |      |                                                |

| Maximum Voltage on Digital Inputs | V <sub>DIN_MAX</sub> |     |     | 5.5 | V    | Applies to SCL, SDA, DIG_IO1, DIG_IO2, DIG_IO3 |

| Maximum Logic Low Input Voltage   | V <sub>IL</sub>      |     |     | 0.5 | V    | Applies to SCL, SDA, DIG_IO1, DIG_IO2, DIG_IO3 |

| Minimum Logic High Input Voltage  | V <sub>IH</sub>      | 1.2 |     |     | V    | Applies to SCL, SDA, DIG_IO1, DIG_IO2, DIG_IO3 |

| Pull-Down Resistance              |                      | 215 | 350 | 610 | kΩ   | Applies to DIG_IO1, DIG_IO2, DIG_IO3           |

<sup>&</sup>lt;sup>1</sup> Undervoltage lockout generated normally from ISO\_Sx or ISO\_Bx; in certain transition cases, it can be generated from VINx. <sup>2</sup> These values are programmable via I<sup>2</sup>C. Values are given with default register values. <sup>3</sup> The output current during charging may be limited by the input current limit or by the isothermal charging mode.

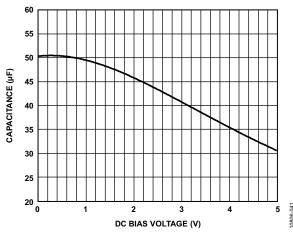

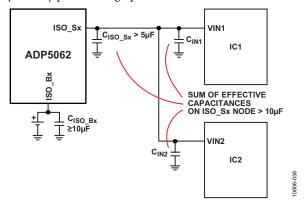

### RECOMMENDED INPUT AND OUTPUT CAPACITANCES

Table 2.

| Parameter    | Symbol              | Min | Тур | Max | Unit | Test Conditions/Comments |

|--------------|---------------------|-----|-----|-----|------|--------------------------|

| CAPACITANCES |                     |     |     |     |      |                          |

| VINx         | C <sub>VINx</sub>   | 4   |     | 10  | μF   | Effective capacitance    |

| CBP          | ССВР                | 6   | 10  | 14  | nF   | Effective capacitance    |

| ISO_Sx       | C <sub>ISO_Sx</sub> | 10  | 22  | 100 | μF   | Effective capacitance    |

| ISO_Bx       | C <sub>ISO_Bx</sub> | 10  | 22  |     | μF   | Effective capacitance    |

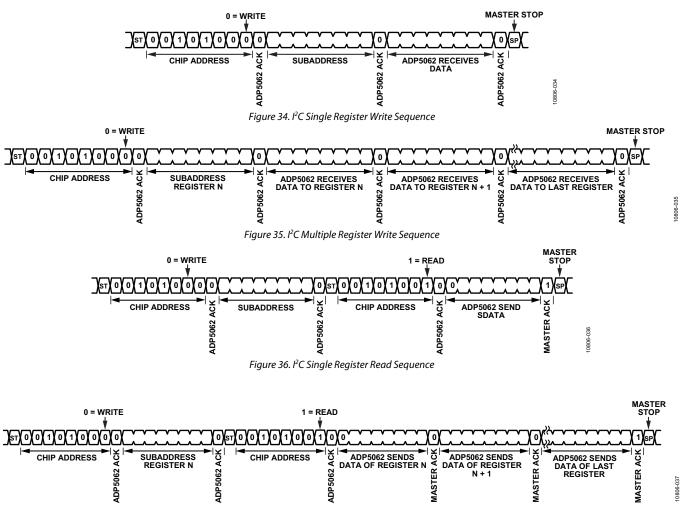

### I<sup>2</sup>C-COMPATIBLE INTERFACE TIMING SPECIFICATIONS

Table 3.

| Parameter <sup>1</sup>                             | Symbol                | Min | Тур | Max | Unit |

|----------------------------------------------------|-----------------------|-----|-----|-----|------|

| I <sup>2</sup> C-COMPATIBLE INTERFACE <sup>2</sup> |                       |     |     |     |      |

| Capacitive Load for Each Bus Line                  | Cs                    |     |     | 400 | pF   |

| SCL Clock Frequency                                | f <sub>SCL</sub>      |     |     | 400 | kHz  |

| SCL High Time                                      | tнібн                 | 0.6 |     |     | μs   |

| SCL Low Time                                       | t <sub>LOW</sub>      | 1.3 |     |     | μs   |

| Data Setup Time                                    | t <sub>SU</sub> , DAT | 100 |     |     | ns   |

| Data Hold Time                                     | t <sub>HD</sub> , DAT | 0   |     | 0.9 | μs   |

| Setup Time for Repeated Start                      | <b>t</b> su, sta      | 0.6 |     |     | μs   |

| Hold Time for Start/Repeated Start                 | t <sub>HD</sub> , sta | 0.6 |     |     | μs   |

| Bus Free Time Between a Stop and a Start Condition | t <sub>BUF</sub>      | 1.3 |     |     | μs   |

| Setup Time for Stop Condition                      | t <sub>su</sub> , sto | 0.6 |     |     | μs   |

| Rise Time of SCL/SDA                               | t <sub>R</sub>        | 20  |     | 300 | ns   |

| Fall Time of SCL/SDA                               | t <sub>F</sub>        | 20  |     | 300 | ns   |

| Pulse Width of Suppressed Spike                    | t <sub>SP</sub>       | 0   |     | 50  | ns   |

<sup>&</sup>lt;sup>1</sup> Guaranteed by design.

<sup>&</sup>lt;sup>4</sup> During weak charging mode, the charger provides at least 20 mA of charging current via the trickle charge branch to the battery unless trickle charging is disabled. Any residual current that is not required by the system is also used to charge the battery.

<sup>&</sup>lt;sup>5</sup> Either JEITA1 (default) or JEITA2 can be selected in I<sup>2</sup>C, or both JEITA functions can be enabled or disabled in I<sup>2</sup>C.

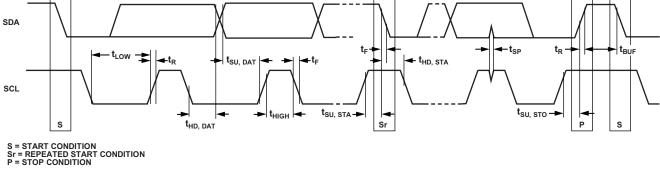

<sup>&</sup>lt;sup>2</sup> A master device must provide a hold time of at least 300 ns for the SDA signal to bridge the undefined region of the falling edge of SCL (see Figure 2).

Figure 2. I<sup>2</sup>C Timing Diagram

#### ABSOLUTE MAXIMUM RATINGS

**Table 4. Absolute Maximum Ratings**

| Parameter                                                                   | Rating          |

|-----------------------------------------------------------------------------|-----------------|

| VIN1, VIN2, VIN3 to AGND                                                    | –0.5 V to +20 V |

| All Other Pins to AGND                                                      | –0.3 V to +6 V  |

| Continuous Drain Current, Battery Supplementary Mode, from ISO_Bx to ISO_Sx | 2.1 A           |

| Storage Temperature Range                                                   | −65°C to +150°C |

| Operating Junction Temperature Range                                        | −40°C to +125°C |

| Soldering Conditions                                                        | JEDEC J-STD-020 |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is,  $\theta_{JA}$  is specified for a device soldered in a circuit board for surface-mount packages.

**Table 5. Thermal Resistance**

| Package Type  | θја  | θις  | Unit |

|---------------|------|------|------|

| 20-Lead LFCSP | 35.6 | 3.65 | °C/W |

#### **Maximum Power Dissipation**

The maximum safe power dissipation in the ADP5062 package is limited by the associated rise in junction temperature ( $T_1$ ) on the die. At a die temperature of approximately 150°C (the glass transition temperature), the properties of the plastic change. Even temporarily exceeding this temperature limit may change the stresses that the package exerts on the die, thereby permanently shifting the parametric performance of the ADP5062. Exceeding a junction temperature of 175°C for an extended period can result in changes in the silicon devices, potentially causing failure.

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

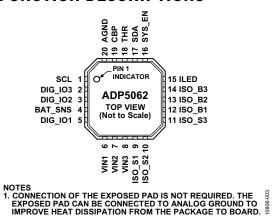

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 3. Pin Configuration

**Table 6. Pin Function Descriptions**

| Pin No.          | Name                      | Type <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------|---------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9, 10, 11        | ISO_S1, ISO_S2,<br>ISO_S3 | I/O               | Linear Charger Supply Side Input to Internal Isolation FET/Battery Current Regulation FET. High current input/output.                                                                                                                                                                                                                                                                                                                      |

| 6, 7, 8          | VIN1, VIN2, VIN3          | I/O               | Power Connections to USB VBUS. These pins are high current inputs when in charging mode.                                                                                                                                                                                                                                                                                                                                                   |

| 20               | AGND                      | G                 | Analog Ground.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 12, 13, 14       | ISO_B1, ISO_B2, ISO_B3    | I/O               | Battery Supply Side Input to Internal Isolation FET/Battery Current Regulation FET.                                                                                                                                                                                                                                                                                                                                                        |

| 1                | SCL                       | 1                 | I <sup>2</sup> C-Compatible Interface Serial Clock.                                                                                                                                                                                                                                                                                                                                                                                        |

| 17               | SDA                       | I/O               | I <sup>2</sup> C-Compatible Interface Serial Data.                                                                                                                                                                                                                                                                                                                                                                                         |

| 5                | DIG_IO1                   | GPIO              | Set Input Current Limit. This pin sets the input current limit directly. When DIG_IO1 = low or high-Z, the input limit is 100 mA. When DIG_IO1 = high, the input limit is 500 mA. <sup>2, 3</sup>                                                                                                                                                                                                                                          |

| 3                | DIG_IO2                   | GPIO              | Disable IC1. The DIG_IO2 pin sets the charger to the low current mode. When DIG_IO2 = low or high-Z, the charger operates in normal mode. When DIG_IO2 = high, the LDO and the charger are disabled and VINx current consumption is 280 $\mu$ A (typical). In addition, when DIG_IO2 is high, 20 V VINx input protection is disabled and the VINx voltage level must fulfill the condition, $V_{ISO_Bx} < V_{VINx} < 5.5 \text{ V.}^{2.3}$ |

| 2                | DIG_IO3                   | GPIO              | Enable Charging. When DIG_IO3 = low or high-Z, charging is disabled. When DIG_IO3 = high, charging is enabled. <sup>2,3</sup>                                                                                                                                                                                                                                                                                                              |

| 18               | THR                       | 1                 | Battery Pack Thermistor Connection. If this pin is not used, connect a dummy 10 k $\Omega$ resistor from THR to GND.                                                                                                                                                                                                                                                                                                                       |

| 4                | BAT_SNS                   | 1                 | Battery Voltage Sense Pin.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 15               | ILED                      | 0                 | Open-Drain Output to Indicator LED.                                                                                                                                                                                                                                                                                                                                                                                                        |

| 16               | SYS_EN                    | 0                 | System Enable. This pin is the battery OK flag/open-drain pull-down FET to enable the system when the battery reaches the VWEAK level.                                                                                                                                                                                                                                                                                                     |

| 19               | CBP                       | I/O               | Bypass Capacitor Input.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| N/A <sup>4</sup> | EP                        | N/A <sup>4</sup>  | Exposed Pad. Connection of the exposed pad is not required. The exposed pad can be connected to analog ground to improve heat dissipation from the package to the board.                                                                                                                                                                                                                                                                   |

$<sup>^1\</sup>mathrm{I}$  is input, O is output, I/O is input/output, G is ground, and GPIO is the factory programmable general-purpose input/output.

<sup>&</sup>lt;sup>2</sup> See the Digital Input and Output Options section for details.

<sup>&</sup>lt;sup>3</sup> The DIG\_IOx setting defines the initial state of the ADP5062. If the parameter or the mode that is related to each DIG\_IOx pin setting is changed (by programming an equivalent I<sup>2</sup>C register bit or bits), the I<sup>2</sup>C register setting takes precedence over the DIG\_IOx pin setting. VINx connection or disconnection resets control to the DIG\_IOx pin.

<sup>&</sup>lt;sup>4</sup> N/A means not applicable.

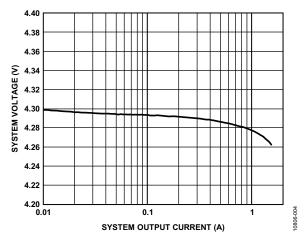

## TYPICAL PERFORMANCE CHARACTERISTICS

$V_{VINx} = 5.0 \text{ V}, C_{VINx} = 10 \text{ } \mu\text{F}, C_{ISO\_Sx} = 44 \text{ } \mu\text{F}, C_{ISO\_Bx} = 22 \text{ } \mu\text{F}, C_{CBP} = 10 \text{ } n\text{F}, all registers at default values, unless otherwise noted.}$

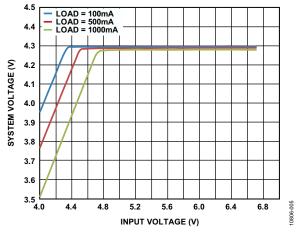

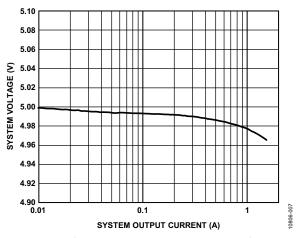

Figure 4. System Voltage vs. System Output Current, LDO Mode, VSYSTEM[2:0] = 000 (Binary) = 4.3 V

Figure 5. System Voltage vs. Input Voltage (in Dropout), LDO Mode, VSYSTEM[2:0] = 000 (Binary) = 4.3 V

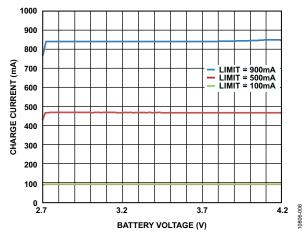

Figure 6. Input Current-Limited Charge Current vs. Battery Voltage

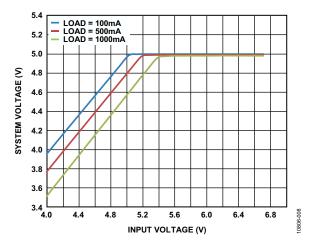

Figure 7. System Voltage vs. System Output Current, LDO Mode,  $V_{VINx} = 6.0 V$ , VSYSTEM[2:0] = 111 (Binary) = 5.0 V

Figure 8. System Voltage vs. Input Voltage (in Dropout), LDO Mode, VSYSTEM[2:0] = 111 (Binary) = 5.0 V

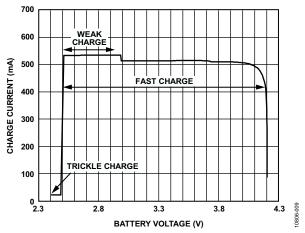

Figure 9. Battery Charge Current vs. Battery Voltage, ICHG[4:0] = 01001 (Binary) = 500 mA, ILIM[3:0] = 1111 (Binary) = 2100 mA

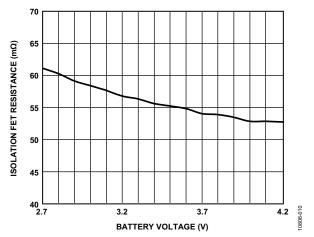

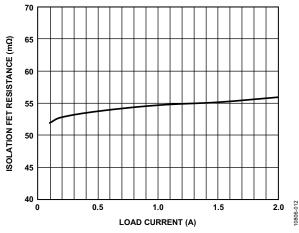

Figure 10. Ideal Diode  $R_{ON}$  vs. Battery Voltage,  $I_{ISO\_Sx} = 500$  mA, VINx Open

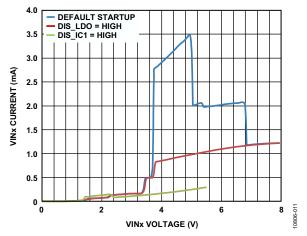

Figure 11. VINx Current vs. VINx Voltage, No Battery

Figure 12. Ideal Diode  $R_{ON}$  vs. Load Current,  $V_{ISO\_Bx} = 3.6 \text{ V}$

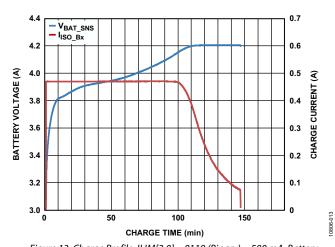

Figure 13. Charge Profile, ILIM[3:0] = 0110 (Binary) = 500 mA, Battery Capacity = 925 mAh

### **TEMPERATURE CHARACTERISTICS**

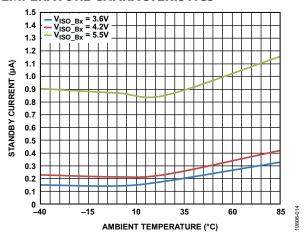

Figure 14. Battery Leakage Current vs. Ambient Temperature

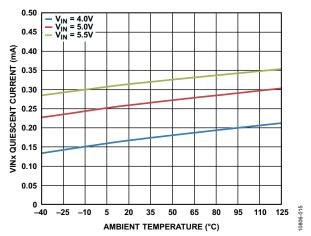

Figure 15. VINx Quiescent Current vs. Ambient Temperature, DIS\_IC1 = High

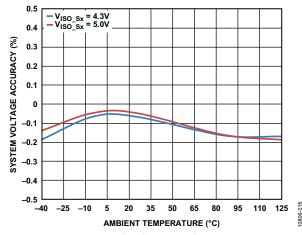

Figure 16. LDO Mode Voltage vs. Ambient Temperature,  $Load = 100 \text{ mA}, V_{VINx} = 5.5 \text{ V}$

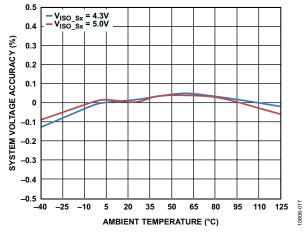

Figure 17. System Voltage vs. Temperature, Trickle Charge Mode,  $V_{ISO\_Sx} = 4.3 \text{ V}$  and VINx = 5.0 V, or  $V_{ISO\_Sx} = 5.0 \text{ V}$  and VINx = 6.0 V

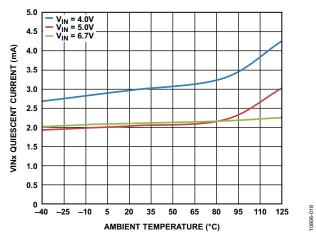

Figure 18. VINx Quiescent Current vs. Ambient Temperature, LDO Mode

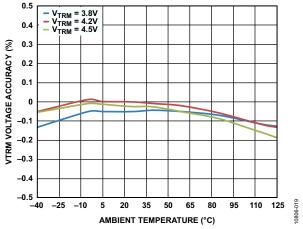

Figure 19. Termination Voltage vs. Ambient Temperature

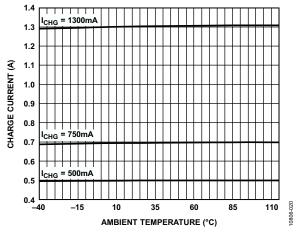

Figure 20. Fast Charge CC Mode Current vs. Ambient Temperature

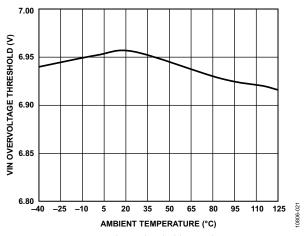

Figure 21. VINx Overvoltage Threshold vs. Ambient Temperature

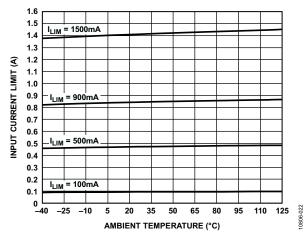

Figure 22. Input Current Limit vs. Ambient Temperature

### **TYPICAL WAVEFORMS**

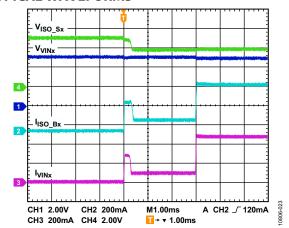

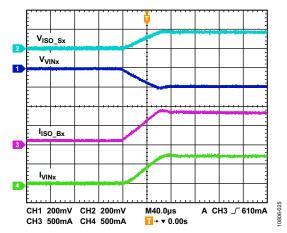

Figure 23. Charging Startup,  $V_{VINx} = 5.0 V$ , ILIM[3:0] = 0110 (Binary) = 500 mA, ICHG[4:0] = 01110 (Binary) = 750 mA

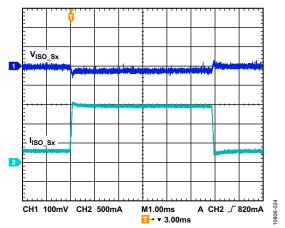

Figure 24. Load Transient,  $I_{ISO\_Sx}$  Load = 300 mA to 1500 mA to 300 mA

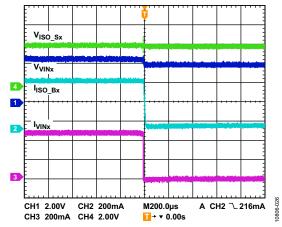

Figure 25. Input Current-Limit Transition from 100 mA to 900 mA, ISO\_Sx Load =  $66 \Omega$ , Charging = 750 mA

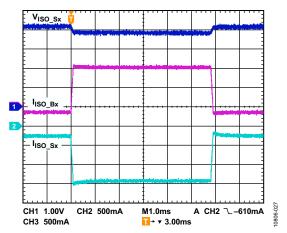

Figure 26. USB VBUS Disconnect

Figure 27. Load Transient,  $I_{ISO\_Sx}$  Load = 300 mA to 1500 mA to 300 mA,  $EN\_CHG = High$ , ILIM[3:0] = 0110 (Binary) = 500 mA

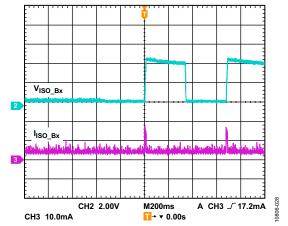

Figure 28. Battery Detection Waveform, VSYSTEM[2:0] = 000 (Binary) = 4.3 V, No Battery

## THEORY OF OPERATION

## **SUMMARY OF OPERATION MODES**

Table 7. Summary of the ADP5062 Operation Modes

| Mode Name                                       | VINx<br>Condition | Battery Condition                                   | Trickle<br>Charge | LDO FET<br>State | Battery<br>Isolation FET | System Voltage<br>ISO_Sx | Additional Conditions <sup>1</sup>   |

|-------------------------------------------------|-------------------|-----------------------------------------------------|-------------------|------------------|--------------------------|--------------------------|--------------------------------------|

| IC Off, Standby                                 | 0 V               | Any battery condition                               | Off               | Off              | On/Off                   | Battery voltage or 0 V   | Disable IC1                          |

| IC Off, Suspend                                 | 5 V               | Any battery condition                               | Off               | Off              | On                       | Battery voltage          | Disable IC1                          |

| LDO Mode Off, Isolation<br>FET On               | 5 V               | Any battery condition                               | Off               | Off              | On                       | Battery voltage          | Disable LDO and enable isolation FET |

| LDO Mode Off, Isolation<br>FET Off (System Off) | 5 V               | Any battery condition                               | Off               | Off              | Off                      | 0 V                      | Enable battery charging              |

| LDO Mode, Charger Off                           | 5 V               | Any battery condition                               | Off               | LDO              | Off                      | 5.0 V                    | Enable battery charging              |

| Trickle Charge Mode                             | 5 V               | Battery < V <sub>TRK_DEAD</sub>                     | On                | LDO              | Off                      | 5.0 V                    | Enable battery charging              |

| Weak Charge Mode                                | 5 V               | V <sub>TRK_DEAD</sub> ≤ battery < V <sub>WEAK</sub> | On                | CHG              | CHG                      | 3.8 V                    | Enable battery charging              |

| Fast Charge Mode                                | 5 V               | Battery ≥ V <sub>WEAK</sub>                         | Off               | CHG              | CHG                      | 3.8 V (minimum)          | Enable battery charging              |

| Charge Mode, No Battery                         | 5 V               | Open                                                | Off               | LDO              | Off                      | 5.0 V                    | Enable battery charging              |

| Charge Mode, Battery<br>(ISO_Bx) Shorted        | 5 V               | Shorted                                             | On                | LDO              | Off                      | 5.0 V                    | Enable battery charging              |

<sup>&</sup>lt;sup>1</sup> See Table 8 for details.

**Table 8. Operation Mode Controls**

|                                      |         | Equivalent I <sup>2</sup> C |                                                              |                          |                 |          |

|--------------------------------------|---------|-----------------------------|--------------------------------------------------------------|--------------------------|-----------------|----------|

| Pin Configuration                    | DIG_IOx | Address, Data Bit(s)        | Description                                                  |                          |                 |          |

| Enable Battery Charging              | DIG_IO3 | 0x07, D0                    | Low = all charg                                              | jing modes disabled (fa  | st, weak, tricl | de).     |

|                                      |         |                             | High = all char                                              | ging modes enabled (fa   | ast, weak, tric | kle).    |

| Disable IC1                          | DIG_IO2 | 0x07, D6                    |                                                              | VINx <sup>1</sup> Supply |                 |          |

|                                      |         |                             | Disable IC1                                                  | Connected                | LDO_FET         | ISO_FET  |

|                                      |         |                             | Low                                                          | No                       | Off             | On       |

|                                      |         |                             |                                                              | Yes                      | CHG             | CHG      |

|                                      |         |                             | High                                                         | No <sup>2</sup>          | Off             | On       |

|                                      |         |                             |                                                              | Yes                      | Off             | On       |

| Disable LDO and Enable Isolation FET |         | 0x07, D3, D0                | Low = LDO enabled.                                           |                          |                 |          |

|                                      |         |                             | High = LDO disabled. In addition, when EN_CHG = low, the     |                          |                 | low, the |

|                                      |         |                             | battery isolation FET is on; when EN_CHG = high, the battery |                          |                 |          |

|                                      |         |                             | isolation FET is                                             | off.                     |                 |          |

<sup>1</sup> When disable IC1 mode is active, the VINx supply must always be connected and the supply voltage level must fulfill the following condition: VISO\_BX < VINX < 5.5 V.

<sup>&</sup>lt;sup>2</sup> When disable IC1 mode is active, the back gate of the LDO FET is not controlled. If the VINx pins are not connected to any voltage supply, the body diode of the LDO FET can become forward biased and the voltage at VINx is  $V_{SO\_Bx} - V_F$  ( $V_F$  is the forward voltage of the LDO FET body diode).

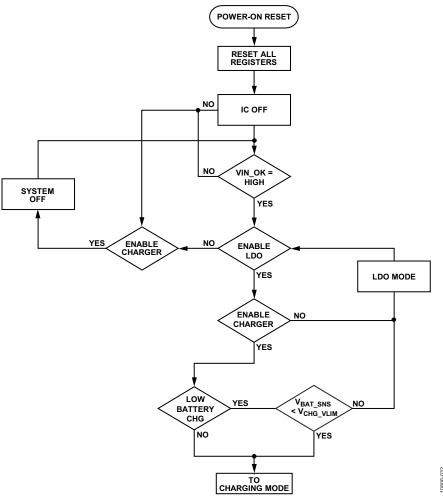

#### INTRODUCTION

The ADP5062 is a fully-programmable I<sup>2</sup>C charger for single cell lithium-ion or lithium-polymer batteries suitable for a wide range of portable applications.

The linear charger architecture enables up to 2.1 A output current at 4.3 V to 5.0 V (I<sup>2</sup>C programmable) on the system power supply, and up to 1.3 A charge current into the battery from a dedicated charger.

The ADP5062 operates from an input voltage of 4 V up to 6.7 V but is tolerant of voltages of up to 20 V. The 20 V voltage tolerance alleviates the concerns of the USB bus spiking during disconnection or connection scenarios.

The ADP5062 features an internal FET between the linear charger output and the battery. This feature permits battery isolation and, hence, system powering under a dead battery or no battery scenario, which allows for immediate system function upon connection to a USB power supply.

The ADP5062 is fully compliant with USB 3.0 and the USB Battery Charging Specification 1.2. The ADP5062 is chargeable via the mini USB VBUS pin from a wall charger, car charger, or USB host port. Based on the type of USB source, which is detected

by an external USB detection device, the ADP5062 can be set to apply the correct current limit for optimal charging and USB compliance. The USB charger permits correct operation under all USB compliant sources such as wall chargers, host chargers, hub chargers, and standard host and hubs.

A processor can control the USB charger using the  $\rm I^2C$  to program the charging current and numerous other parameters, including

- Trickle charge current level

- Trickle charge voltage threshold

- Weak charge (constant current) current level

- Fast charge (constant current) current level

- Fast charge (constant voltage) voltage level at 1% accuracy

- Fast charge safety timer period

- Watchdog safety timer parameters

- Weak battery threshold detection

- Charge complete threshold

- Recharge threshold

- Charge enable/disable

- Battery pack temperature detection and automatic charger shutdown

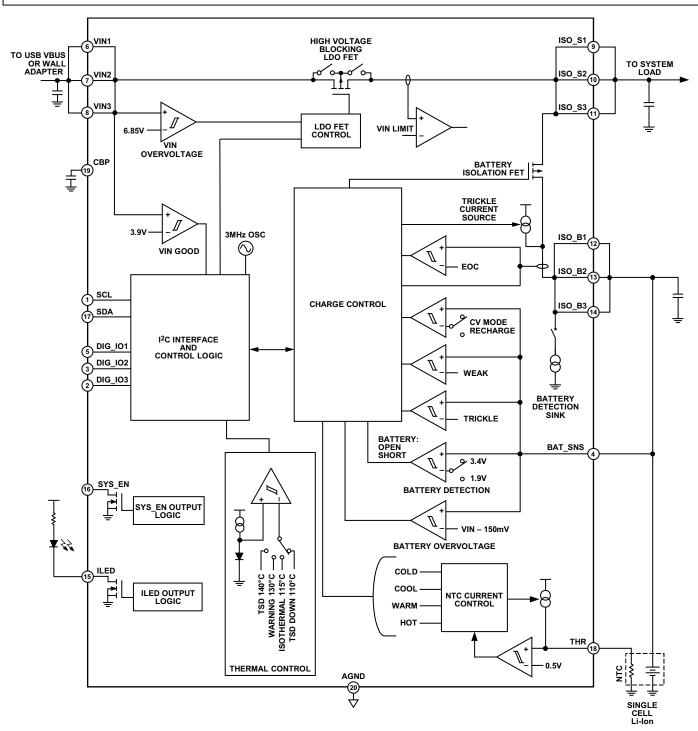

Figure 29. Block Diagram

The ADP5062 includes a number of significant features to optimize charging and functionality including

- Thermal regulation for maximum performance.

- USB host current limit.

- Termination voltage accuracy: ±1%.

- Battery thermistor input with automatic charger shutdown in the event that the battery temperature exceeds limits (compliant with the JEITA Li-Ion battery charging temperature specification).

- Three external pins (DIG\_IO1, DIG\_IO2, and DIG\_IO3)

that directly control a number of parameters. These pins

are factory programmable for maximum flexibility. They

can be factory programmed for functions such as

- Enable/disable charging.

- Control of 100 mA or 500 mA input current limit.

- Control of 1500 mA input current limit.

- Control of the battery charge current.

- Interrupt output pin.

See the Digital Input and Output Options section for details.

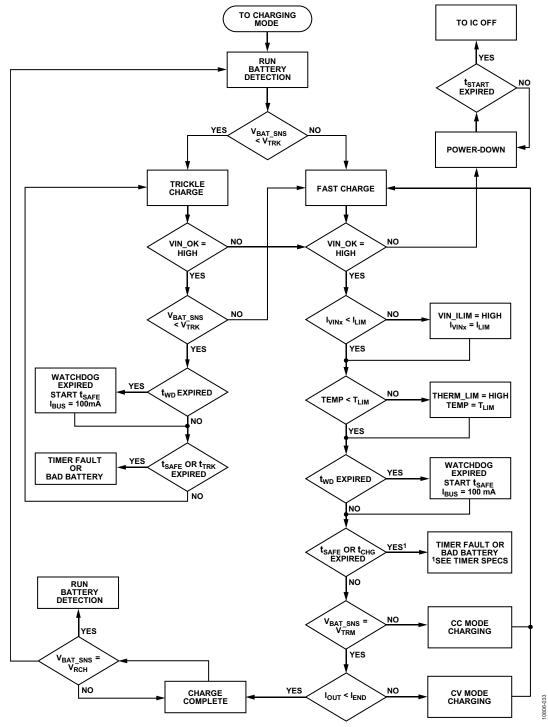

## **CHARGER MODES**

#### **Input Current Limit**

The VINx input current limit is controlled via the internal I<sup>2</sup>C ILIM bits. The input current limit can also be controlled via the DIG\_IO1 pin (if factory programmed to do so) as outlined in Table 9. Any change in the I<sup>2</sup>C default from 100 mA takes precedence over the pin setting.

Table 9. DIG\_IO1 Operation

| DIG_IO1 | Function                                                                                                                     |

|---------|------------------------------------------------------------------------------------------------------------------------------|

| 0       | 100 mA input current limit or I <sup>2</sup> C programmed value                                                              |

| 1       | 500 mA input current limit or I <sup>2</sup> C programmed value (or reprogrammed I <sup>2</sup> C value from 100 mA default) |

#### **USB Compatibility**

The ADP5062 features an I<sup>2</sup>C-programmable input current limit to ensure compatibility with the requirements listed in Table 10. The current limit defaults to 100 mA to allow compatibility with a USB host or hub that is not configured.

The I<sup>2</sup>C register default is 100 mA. An I<sup>2</sup>C write command to the ILIM register overrides the DIG\_IOx pins and the I<sup>2</sup>C register default value can be reprogrammed for alternative requirements.

When the input current-limit feature is used, the available input current may be too low for the charger to meet the programmed charging current, I<sub>CHG</sub>, thereby reducing the rate of charge and setting the VIN\_ILIM flag.

When connecting voltage to VINx without the proper voltage level on the battery side, the high voltage blocking mechanism is in a state wherein it draws only the current of <1 mA until  $V_{\rm IN}$  reaches the VIN\_OK level.

The ADP5062 charger provides support for the following connections through the single connector VINx pin, as shown in Table 10.

Table 10. Input Current Compatibility with Standard USB Limits

| Mode              | Standard USB Limit                                                            | ADP5062 Function                                                 |

|-------------------|-------------------------------------------------------------------------------|------------------------------------------------------------------|

| USB (China Only)  | 100 mA limit for standard USB host or hub                                     | 100 mA input current limit or I <sup>2</sup> C programmed value  |

|                   | 300 mA limit for Chinese USB specification                                    | 300 mA input current limit or I <sup>2</sup> C programmed value  |

| USB 2.0           | 100 mA limit for standard USB host or hub                                     | 100 mA input current limit or I <sup>2</sup> C programmed value  |

|                   | 500 mA limit for standard USB host or hub                                     | 500 mA input current limit or I <sup>2</sup> C programmed value  |

| USB 3.0           | 150 mA limit for superspeed USB 3.0 host or hub                               | 150 mA input current limit or I <sup>2</sup> C programmed value  |

|                   | 900 mA limit for superspeed, high speed USB host or hub charger               | 900 mA input current limit or I <sup>2</sup> C programmed value  |

| Dedicated Charger | 1500 mA limit for dedicated charger or low/full speed USB host or hub charger | 1500 mA input current limit or I <sup>2</sup> C programmed value |

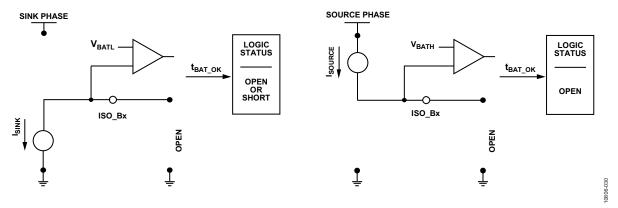

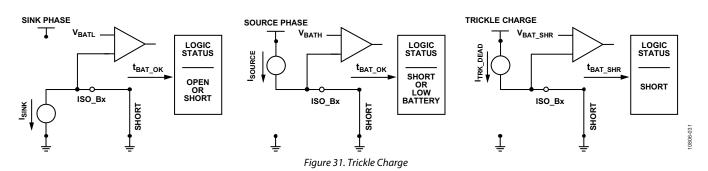

#### Trickle Charge Mode

A deeply discharged Li-Ion cell can exhibit a very low cell voltage making it unsafe to charge the cell at high current rates. The ADP5062 charger uses a trickle charge mode to reset the battery pack protection circuit and lift the cell voltage to a safe level for fast charging. A cell with a voltage below  $V_{\text{TRK\_DEAD}}$  is charged with the trickle mode current,  $I_{\text{TRK\_DEAD}}$ . During trickle charging mode, the CHARGER STATUS bits are set.

During trickle charging, the ISO\_Sx node is regulated to  $V_{\text{ISO\_STRK}}$  by the LDO and the battery isolation FET is off, which means that the battery is isolated from the system power supply.

## Trickle Charge Mode Timer

The duration of trickle charge mode is monitored to ensure that the battery is revived from its deeply discharged state. If trickle charge mode runs for longer than 60 minutes without the cell voltage reaching  $V_{TRK\_DEAD}$ , a fault condition is assumed and charging stops. The fault condition is asserted on the CHARGER\_STATUS bits, allowing the user to initiate the fault recovery procedure specified in the Fault Recovery section.

#### Weak Charge Mode (Constant Current)

When the battery voltage exceeds  $V_{\text{TRK\_DEAD}}$  but is less than  $V_{\text{WEAK}}$ , the charger switches to intermediate charge mode.

During the weak charge mode, the battery voltage is too low to allow the full system to power-up. Because of the low battery level, the USB transceiver cannot be powered and, therefore, cannot enumerate for more current from a USB host. Consequently, the USB limit remains at 100 mA.

The system microcontroller may or may not be powered by the charger output voltage ( $V_{\rm ISO\_SFC}$ ), depending upon the amount of current that the microcontroller and/or the system architecture requires. When the ISO\_Sx pins power the microcontroller, the battery charge current ( $I_{\rm CHG\_WEAK}$ ) cannot be increased above 20 mA to ensure microcontroller operation (if doing so), nor can  $I_{\rm CHG\_WEAK}$  be increased above the 100 mA USB limit. Therefore, set the battery charging current as follows:

- Set the default 20 mA via the linear trickle charger branch (to ensure that the microprocessor remains alive if powered by the main charger output, ISO\_Sx.). Any residual current on the main charger output, ISO\_Sx, is used to charge the battery.

- During weak current mode, other features may prevent the weak charging current from reaching its full programmed value. Isothermal charging mode or input current limiting for USB compatibility can affect the programmed weak charging current value under certain operating conditions. During weak charging, the ISO\_Sx node is regulated to V<sub>ISO\_SFC</sub> by the battery isolation FET.

## Fast Charge Mode (Constant Current)

When the battery voltage exceeds  $V_{TRK\_DEAD}$  and  $V_{WEAK}$ , the charger switches to fast charge mode, charging the battery with the constant current,  $I_{CHG}$ . During fast charge mode (constant current), the CHARGER\_STATUS bits are set to 010.

During constant current mode, other features may prevent the current,  $I_{CHG}$ , from reaching its full programmed value. Isothermal charging mode or input current limiting for USB compatibility can affect the value of  $I_{CHG}$  under certain operating conditions. The voltage on ISO\_Sx is regulated to stay at  $V_{ISO\_SFC}$  by the battery isolation FET when  $V_{ISO\_Bx} < V_{ISO\_SFC}$ .

## Fast Charge Mode (Constant Voltage)