#### ISL68201

Single-Phase R4 Digital Hybrid PWM Controller with PMBus/SMBus/I<sup>2</sup>C and PFM

FN8696 Rev.4.00 Oct 17, 2017

The ISL68201 is a single-phase, synchronous buck PWM controller featuring Intersil's proprietary R4 $^{\rm TM}$  Technology. It supports a wide 4.5V to 24V input voltage range and a wide 0.5V to 5.5V output range. Integrated LDOs provide controller bias voltage, allowing for single supply operation. The ISL68201 includes a PMBus/SMBus/I $^2$ C interface for device configuration and telemetry (V $_{\rm IN}$ , V $_{\rm OUT}$ , I $_{\rm OUT}$ , and temperature) and fault reporting.

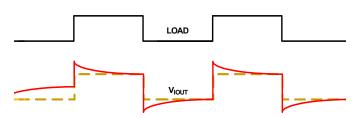

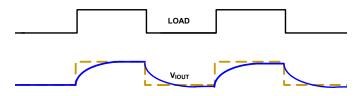

Intersil's proprietary R4 control scheme has extremely fast transient performance, accurately regulated frequency control and all internal compensation. An efficiency enhancing PFM mode can be enabled to greatly improve light-load efficiency. The ISL68201's serial bus allows for easy R4 loop optimization, resulting in fast transient performance over a wide range of applications, including all ceramic output filters.

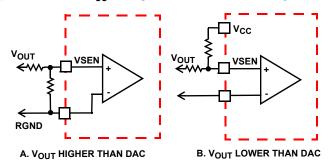

The ISL68201 has four 8-bit configuration pins, which provide very flexible configuration options (frequency,  $V_{OUT}$ , R4 gain, etc.) without the need for built-in NVM memory. This results in a design flow that closely matches traditional analog controllers, while still offering the design flexibility and feature set of a digital PMBus/SMBus/I $^2$ C interface. The ISL68201 also features remote voltage sensing and completely eliminates any potential difference between remote and local grounds. This improves regulation and protection accuracy. A precision enable input is available to coordinate the start-up of the ISL68201 with other voltage rails, especially useful for power sequencing.

## **Applications**

- · High efficiency and high density POL digital power

- FPGA, ASIC, and memory supplies

- · Data center: servers, storage systems

- Wired infrastructure: routers, switches, and optical networking

- · Wireless infrastructure: base station

### **Related Literature**

• ISL68201 product page

#### **Features**

- Intersil's proprietary R4 Technology

- Linear control loop for optimal transient response

- Variable frequency and duty cycle control during load transient for fastest possible response

- Inherent voltage feed-forward for wide range input

- Input voltage range: 4.5V to 24V

- · Output voltage range: 0.5V to 5.5V

- ±0.5% DAC accuracy with remote sense

- · Support all ceramic solutions

- · Integrated LDOs for single input rail solution

- SMBus/PMBus/I<sup>2</sup>C compatible, up to 1.25MHz

- · 256 boot-up voltage levels with a configuration pin

- Eight switching frequency options from 300kHz to 1.5MHz

- PFM operation option, compatible with ISL99140 for improved light-load efficiency

- · Start-up into precharged load

- Precision enable input to set higher input UVLO and power sequence as well as fault reset

- · Power-good monitor for soft-start and fault detection

- · Comprehensive fault protection for high system reliability

- Over-temperature protection

- Output overcurrent and short-circuit protection

- Output overvoltage and undervoltage protection

- Open remote sense protection

- Compatible with 5V or 3.3V PWM input DrMOS or Smart Power Stage (SPS)

- Compatible with Intersil's **PowerNavigator** software

#### TABLE 1. SINGLE-PHASE R4 DIGITAL HYBRID PWM CONTROLLER OPTIONS

| PART<br>NUMBER | INTEGRATED<br>DRIVER | PWM<br>OUTPUT | PMBus/SMBus/I <sup>2</sup> C<br>INTERFACE | COMPATIBLE DEVICES                                                                                                                     |

|----------------|----------------------|---------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| ISL68200       | Yes                  | No            | Yes                                       | Discrete MOSFETs or Dual Channel MOSFETs                                                                                               |

| ISL68201       | No                   | Yes           |                                           | Intersil Power Stages:<br>ISL99140, ISL99227, ISL99125B, ISL99135B<br>Intersil Drivers:<br>ISL6596, ISL6609, ISL6627, ISL6622, ISL6208 |

## **Table of Contents**

| Typical Applications Circuits                | 3    |

|----------------------------------------------|------|

| Block Diagram                                | 4    |

| Ordering Information                         | 5    |

| Pin Configuration                            | 5    |

| Functional Pin Descriptions                  |      |

| Absolute Maximum Ratings                     |      |

| Thermal Information                          |      |

| Recommended Operating Conditions             |      |

| Electrical Specifications                    |      |

| •                                            |      |

| Operation                                    |      |

| IC Supplies                                  | . 10 |

| Enable and Disable                           | . 10 |

| Resistor Reader (Patented)                   | . 10 |

| Soft-Start                                   | . 12 |

| Boot-Up Voltage Programming                  | . 12 |

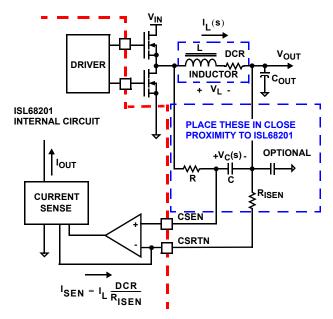

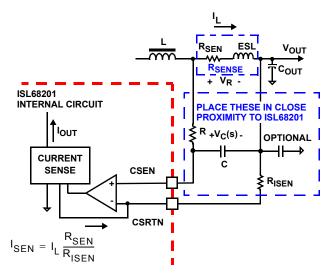

| Current Sensing                              |      |

| Thermal Monitoring and Compensation          |      |

| I <sub>OUT</sub> Calibration                 |      |

| Fault Protection                             |      |

| PGOOD Monitor                                |      |

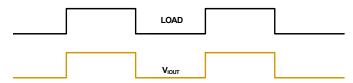

| PFM Mode Operation                           | . 21 |

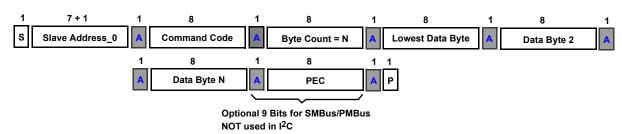

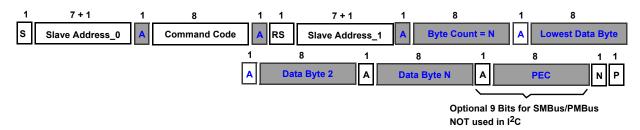

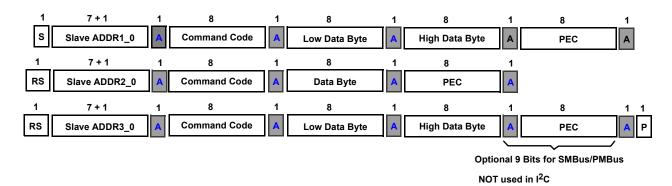

| SMBus, PMBus, and I <sup>2</sup> C Operation |      |

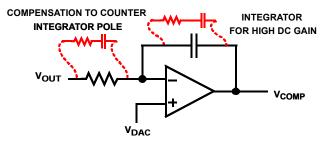

| R4 Modulator                                 | . 26 |

| General Application Design Guide             | . 28 |

| Output Filter Design                         | . 28 |

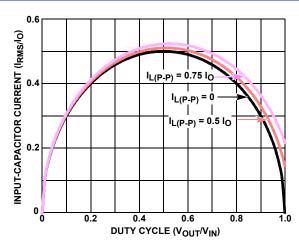

| Input Capacitor Selection                    |      |

| Design and Layout Considerations             |      |

| Voltage Regulator Design Materials           | . 30 |

| Revision History                             | . 31 |

| About Intersil                               | . 31 |

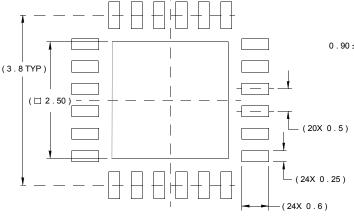

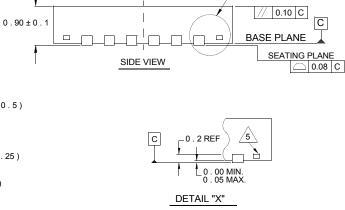

| Packado Autlino Drawind                      | 33   |

## **Typical Applications Circuits**

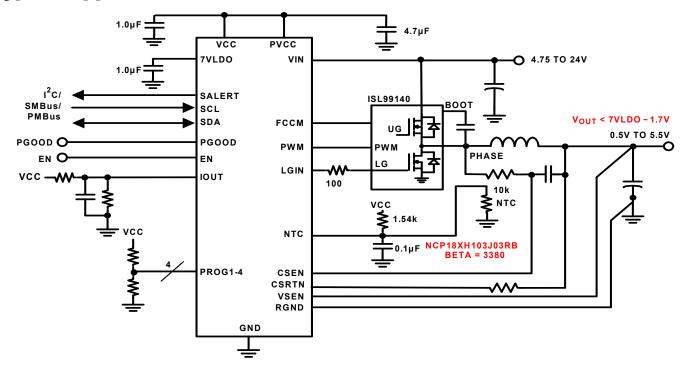

FIGURE 1. WIDE RANGE INPUT AND OUTPUT APPLICATIONS

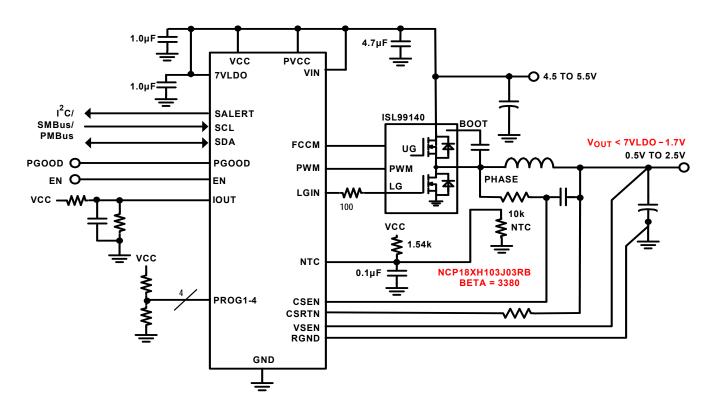

FIGURE 2. 5V INPUT APPLICATION

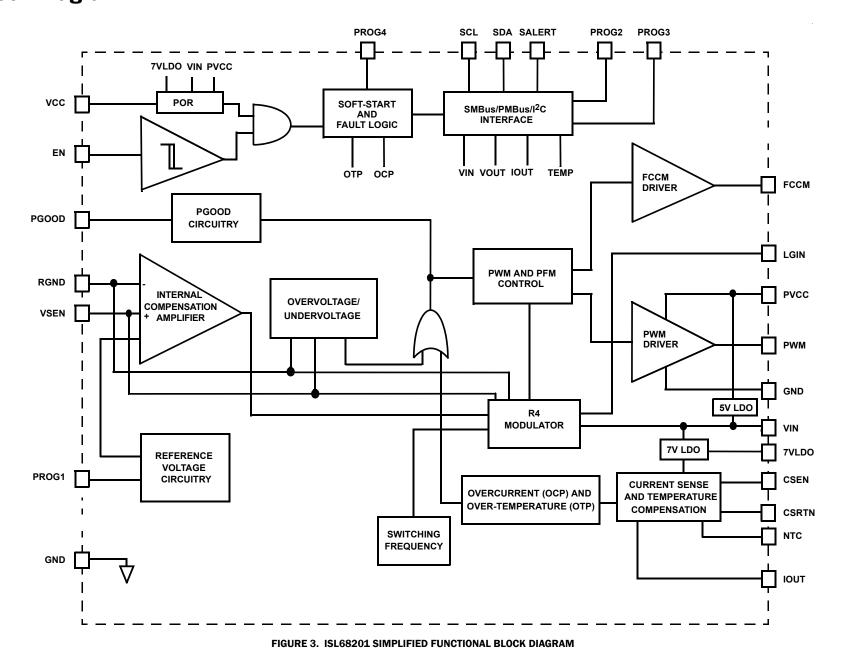

## **Block Diagram**

## **Ordering Information**

| PART NUMBER<br>(Notes 1, 2, 3)                              | PART<br>MARKING              | TEMP RANGE<br>(°C)                     | PACKAGE<br>(RoHS Compliant) | PKG.<br>DWG. # |  |  |  |

|-------------------------------------------------------------|------------------------------|----------------------------------------|-----------------------------|----------------|--|--|--|

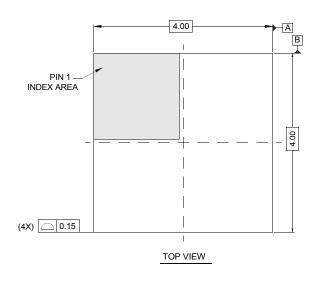

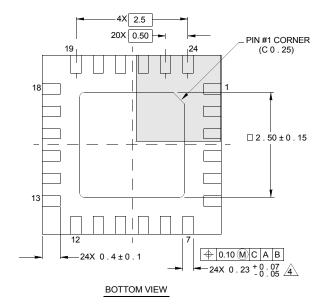

| ISL68201IRZ                                                 | ISL 68201I                   | -40 to +85                             | 24 Ld 4x4 QFN               | L24.4x4C       |  |  |  |

| ISL68201-99125DEM01Z                                        | 16A Demo Board with On-Board | 16A Demo Board with On-Board Transient |                             |                |  |  |  |

| ISL68201-99135DEM01Z                                        | 20A Demo Board with On-Board | 20A Demo Board with On-Board Transient |                             |                |  |  |  |

| ISL68201-99140DEM01Z 35A Demo Board with On-Board Transient |                              |                                        |                             |                |  |  |  |

#### NOTES:

- 1. Add "-T" suffix for 6k unit, "-T7A" suffix for 250 unit or "-TK" for 1k unit for tape and reel options. Refer to TB347 for details on reel specifications.

- 2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 3. For Moisture Sensitivity Level (MSL), see the product information page for ISL68201. For more information on MSL, see TB363.

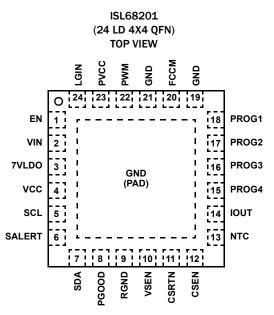

## **Pin Configuration**

## **Functional Pin Descriptions**

| PIN NUMBER | SYMBOL | DESCRIPTION                                                                                                                                                                                                  |

|------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | EN     | Precision enable input. Pulling EN above the rising threshold voltage initiates the soft-start sequence, while pulling EN below the failing threshold voltage suspends the Voltage Regulator (VR) operation. |

| 2          | VIN    | Input voltage pin for R4 loop and LDOs (5V and 7V). Place a high quality low ESR ceramic capacitor (1.0µF, X7R) in close proximity to the pin. External series resistor is not advised.                      |

| 3          | 7VLDO  | 7V LDO from VIN is used to bias current sensing amplifier. Place a high quality low ESR ceramic capacitor (1.0μF, X7R, 10V+) in close proximity to the pin.                                                  |

| 4          | vcc    | Logic bias supply that should be connected to PVCC rail externally. Place a high quality low ESR ceramic capacitor (1µF, X7R) from this pin to GND.                                                          |

| 5          | SCL    | Synchronous clock signal input of SMBus/PMBus/I <sup>2</sup> C.                                                                                                                                              |

| 6          | SALERT | Output pin for transferring the active low signal driven asynchronously from the VR controller to SMBus/PMBus.                                                                                               |

| 7          | SDA    | I/O pin for transferring data signals between SMBus/PMBus/I <sup>2</sup> C host and VR controller.                                                                                                           |

| 8          | PGOOD  | Power-good open-drain indicator output.                                                                                                                                                                      |

| 9          | RGND   | This pin monitors the negative rail of regulator output. Connect to ground at point of regulation.                                                                                                           |

## Functional Pin Descriptions (Continued)

| PIN NUMBER | SYMBOL | DESCRIPTION                                                                                                                                                                                                                                                                                                       |

|------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10         | VSEN   | This pin monitors the positive rail of regulator output. Connect to point of regulation.                                                                                                                                                                                                                          |

| 11         | CSRTN  | This pin monitors the negative flow of output current with a series resistor and for overcurrent protection and telemetry. The series resistor sets the current gain and should be within $40\Omega$ and $3.5k\Omega$ .                                                                                           |

| 12         | CSEN   | This pin monitors the positive flow of output current for overcurrent protection and telemetry.                                                                                                                                                                                                                   |

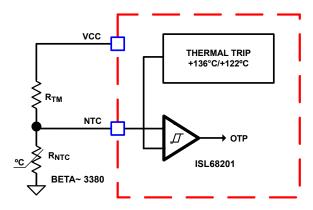

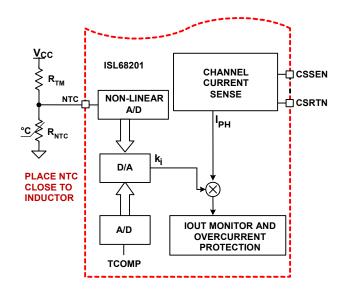

| 13         | NTC    | Input pin for the temperature measurement. Connect this pin through an NTC thermistor ( $10k\Omega$ , $\beta$ ~ 3380) and a decoupling capacitor ( $\sim$ 0.1 $\mu$ F) to GND and a resistor ( $1.54k\Omega$ ) to VCC of the controller. The voltage at this pin is inversely proportional to the VR temperature. |

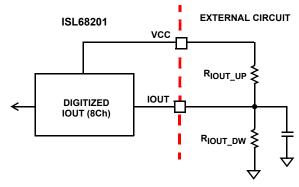

| 14         | IOUT   | Output current monitor pin. An external resistor sets the gain and an external capacitor provides the averaging function; an external pull-up resistor to VCC is recommended to calibrate the no load offset. See "I <sub>QUT</sub> Calibration" on page 19.                                                      |

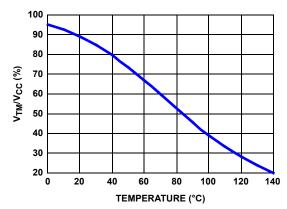

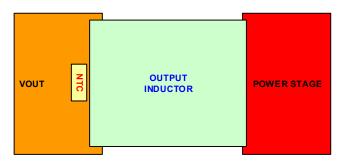

| 15         | PROG4  | Programming pin for Modulator (R4) RR impedance and output slew rate during Soft-Start (SS) and Dynamic VID (DVID). It also sets AV gain multiplier to 1x or 2x and determines the AV gain on PROG3.                                                                                                              |

| 16         | PROG3  | Programming pin for ultrasonic PFM operation, fault behavior, switching frequency, and R4 (AV) control loop gain.                                                                                                                                                                                                 |

| 17         | PROG2  | Programming pin for PWM/PFM mode, temperature compensation, and serial bus (SMBus/PMBus/I <sup>2</sup> C) address.                                                                                                                                                                                                |

| 18         | PROG1  | Programming pin for boot-up voltage.                                                                                                                                                                                                                                                                              |

| 19, 21     | GND    | Ground pin, connect directly to system ground plane.                                                                                                                                                                                                                                                              |

| 20         | FCCM   | Output signal low to work with DrMOS ISL99140 for diode emulation in PFM mode; signal high for PWM mode.                                                                                                                                                                                                          |

| 22         | PWM    | PWM output and is compatible with 3.3V or 5V PWM input external driver, DrMOS, or Smart Power Stage.                                                                                                                                                                                                              |

| 23         | PVCC   | Output of the 5V LDO and input for the LGATE and UGATE MOSFET driver circuits. Place a high quality low ESR ceramic capacitors (4.7µF or higher, X7R) in close proximity to the pin.                                                                                                                              |

| 24         | LGIN   | Low-side gate signal input to complete the internal FLL loop. A $100\Omega$ series impedance from low-side gate drive signal to this pin is required.                                                                                                                                                             |

| PAD        | GND    | Return of logic bias supply VCC. Connect directly to system ground plane with at least four vias.                                                                                                                                                                                                                 |

#### **Absolute Maximum Ratings**

| VCC, PVCC, VSEN0.3V to +7.0V                                    |

|-----------------------------------------------------------------|

| Input Voltage, VIN+27V                                          |

| 7VLDO0.3V to GND, 7.75V                                         |

| All Other Pins0.3V to GND, VCC + 0.3V                           |

| ESD Rating                                                      |

| Human Body Model (Tested per JS-001-2010)2.5kV                  |

| Machine Model (Tested per JESD22-A115C) 200V                    |

| Charge Device Model (Tested per JS-002-2014) 1kV                |

| Latch-Up (Tested per JESD78D, Class 2, Level A)±100mA at +125°C |

#### **Thermal Information**

| Thermal Resistance (Typical) | $\theta_{JA}$ (° C/W) | $\theta_{JC}$ (°C/W) |

|------------------------------|-----------------------|----------------------|

| 24 Ld QFN (Notes 4, 5)       | 39                    | 2.5                  |

| Junction Temperature Range   | 5!                    | 5°C to +150°C        |

| Storage Temperature          | 6!                    | 5°C to +150°C        |

| Pb-Free Reflow Profile       |                       | see <u>TB493</u>     |

#### **Recommended Operating Conditions**

| Ambient Temperature Range                                                        | 40°C to +85°C |

|----------------------------------------------------------------------------------|---------------|

| Wide Range Input Voltage, V <sub>IN</sub> , Figure 1                             | 4.75V to 24V  |

| 5V Application Input Voltage, V <sub>IN</sub> , V <sub>CC</sub> , PVCC, Figure 2 | 4.5V to 5.5V  |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 4. θ<sub>JA</sub> is measured in free air with the component mounted on a high-effective thermal conductivity test board with "direct attach" features. See <u>TB379</u>.

- 5. For  $\theta_{\text{JC}}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

# **Electrical Specifications** All typical specifications $T_A = +25 \,^{\circ}$ C, $V_{CC} = 5$ V. Boldface limits apply across the operating temperature range, -40 $^{\circ}$ C to +85 $^{\circ}$ C, unless otherwise stated.

| PARAMETER                                             | SYMBOL             | TEST CONDITIONS                                                   | MIN<br>(Note 6) | TYP  | MAX<br>(Note 6) | UNIT |

|-------------------------------------------------------|--------------------|-------------------------------------------------------------------|-----------------|------|-----------------|------|

| VCC AND PVCC                                          | •                  |                                                                   | '               |      |                 |      |

| VCC Input Bias Current                                | l <sub>vcc</sub>   | EN = 5V, V <sub>CC</sub> = 5V, f <sub>SW</sub> = 500kHz, DAC = 1V |                 | 14   | 16.5            | mA   |

|                                                       |                    | EN = 0V, V <sub>CC</sub> = 5V                                     |                 | 14   | 16.5            | mA   |

| PVCC Input Bias Current                               | I <sub>PVCC</sub>  | EN = 5V, V <sub>CC</sub> = 5V, f <sub>SW</sub> = 500kHz, DAC = 1V |                 | 2    |                 | mA   |

|                                                       |                    | EN = 0V, V <sub>CC</sub> = 5V                                     |                 |      | 1.0             | mA   |

| VCC AND VIN POR THRESHOLD                             |                    |                                                                   |                 |      |                 |      |

| VCC, PVCC Rising POR Threshold Voltage                |                    |                                                                   |                 | 4.2  | 4.35            | V    |

| VCC, PVCC Falling POR Threshold Voltage               |                    |                                                                   | 3.80            | 3.95 | 4.15            | ٧    |

| V <sub>IN</sub> , 7VLDO Rising POR Threshold Voltage  |                    |                                                                   |                 | 4.2  | 4.35            | V    |

| V <sub>IN</sub> , 7VLDO Falling POR Threshold Voltage |                    |                                                                   | 3.80            | 3.95 | 4.15            | V    |

| ENABLE INPUT                                          |                    |                                                                   |                 |      |                 |      |

| EN High Threshold Voltage                             | V <sub>ENTHR</sub> |                                                                   | 0.81            | 0.84 | 0.87            | ٧    |

| EN Low Threshold Voltage                              | V <sub>ENTHF</sub> |                                                                   | 0.71            | 0.76 | 0.81            | V    |

| DAC ACCURACY                                          |                    |                                                                   |                 |      |                 |      |

| DAC Accuracy                                          |                    | 2.5V < DAC ≤ 5.5V                                                 | -0.5            |      | 0.5             | %    |

| $(T_A = 0 \degree C \text{ to } +85 \degree C)$       |                    | 1.6V < DAC ≤ 2.5V                                                 | -0.75           |      | 0.75            | %    |

|                                                       |                    | 1.2V < DAC ≤ 1.6V                                                 | -10             |      | 10              | m۷   |

|                                                       |                    | 0.5V ≤ DAC ≤ 1.2V                                                 | -8              |      | 8               | mV   |

| DAC Accuracy                                          |                    | 2.5V < DAC ≤ 5.5V                                                 | -0.75           |      | 0.75            | %    |

| $(T_A = -45^{\circ}C \text{ to } +85^{\circ}C)$       |                    | 1.6V < DAC ≤ 2.5V                                                 | -1.0            |      | 1.0             | %    |

|                                                       |                    | 1.2V < DAC ≤ 1.6V                                                 | -11             |      | 11              | mV   |

|                                                       |                    | 0.5V ≤ DAC ≤ 1.2V                                                 | -9              |      | 9               | mV   |

| CHANNEL FREQUENCY                                     |                    |                                                                   |                 | 1    |                 |      |

| 300kHz Configuration                                  |                    | PWM mode                                                          | 260             | 300  | 335             | kHz  |

| 400kHz Configuration                                  |                    | PWM mode                                                          | 345             | 400  | 450             | kHz  |

# **Electrical Specifications** All typical specifications $T_A = +25 \,^{\circ}$ C, $V_{CC} = 5V$ . Boldface limits apply across the operating temperature range, -40 $^{\circ}$ C to +85 $^{\circ}$ C, unless otherwise stated. (Continued)

| PARAMETER                          | SYMBOL               | TEST CONDITIONS                                    | MIN<br>(Note 6) | TYP   | MAX<br>( <u>Note 6</u> ) | UNIT               |

|------------------------------------|----------------------|----------------------------------------------------|-----------------|-------|--------------------------|--------------------|

| 500kHz Configuration               |                      | PWM mode                                           | 435             | 500   | 562                      | kHz                |

| 600kHz Configuration               |                      | PWM mode                                           | 510             | 600   | 670                      | kHz                |

| 700kHz Configuration               |                      | PWM mode                                           | 610             | 700   | 790                      | kHz                |

| 850kHz Configuration               |                      | PWM mode                                           | 730             | 850   | 950                      | kHz                |

| 1000kHz Configuration              |                      | PWM mode                                           | 865             | 1000  | 1120                     | kHz                |

| 1500kHz Configuration              |                      | PWM mode                                           | 1320            | 1500  | 1660                     | kHz                |

| SOFT-START AND DYNAMIC VID         |                      |                                                    |                 |       |                          |                    |

| Soft-Start and DVID Slew Rate      |                      |                                                    | 0.0616          | 0.078 | 0.096                    | mV/μs              |

|                                    |                      |                                                    | 0.13            | 0.157 | 0.18                     | mV/μs              |

|                                    |                      |                                                    | 0.25            | 0.315 | 0.37                     | mV/μs              |

|                                    |                      |                                                    | 0.53            | 0.625 | 0.70                     | mV/μs              |

|                                    |                      |                                                    | 1.05            | 1.25  | 1.40                     | mV/μs              |

|                                    |                      |                                                    | 2.10            | 2.50  | 2.80                     | mV/μs              |

|                                    |                      |                                                    | 4.20            | 5.00  | 5.60                     | mV/μs              |

|                                    |                      |                                                    | 8.60            | 10.0  | 10.9                     | mV/μs              |

| Soft-Start Delay from Enable High  |                      | Excluding 5.5ms POR timeout. See Figures 21 and 22 | 140             | 200   | 260                      | μs                 |

| REMOTE SENSE                       |                      |                                                    |                 |       |                          |                    |

| Bias Current of VSEN and RGND Pins |                      |                                                    |                 |       | 250                      | μΑ                 |

| Maximum Differential Input Voltage |                      |                                                    | 6.0             |       |                          | V                  |

| POWER-GOOD                         |                      |                                                    |                 |       |                          | 1                  |

| PGOOD Pull-Down Impedance          | R <sub>PG</sub>      | PGOOD = 5mA sink                                   |                 | 10    | 50                       | Ω                  |

| PGOOD Leakage Current              | I <sub>PG</sub>      | PGOOD = 5V                                         |                 |       | 1.0                      | μΑ                 |

| LDOs                               |                      |                                                    |                 |       |                          |                    |

| 5V LDO Regulation                  |                      | V <sub>IN</sub> = 12V, load = 50mA                 | 4.85            | 5.00  | 5.15                     | V                  |

| 5V Dropout                         |                      | V <sub>IN</sub> = 4.75V, load = 50mA               | 4.45            |       |                          | V                  |

| 5V LDO Current Capability          |                      |                                                    | 125             |       |                          | mA                 |

| 7V LDO Regulation                  |                      | 250µA load                                         | 7.2             | 7.4   | 7.5                      | V                  |

| 7V Dropout                         |                      | V <sub>IN</sub> = 4.75V, 250μA load                | 4.50            |       |                          | V                  |

| 7V LDO Current Capability          |                      | Not recommended for external use                   | 2               |       |                          | mA                 |

| CURRENT SENSE                      |                      |                                                    | I               |       |                          |                    |

| Average OCP Trip Level             | I <sub>OC_TRIP</sub> |                                                    | 82              | 100   | 123                      | μΑ                 |

| Short-Circuit Protection Threshold |                      |                                                    |                 | 130   |                          | % I <sub>OCP</sub> |

| Sensed Current Tolerance           |                      |                                                    | 74              | 78    | 83                       | μΑ                 |

| Sensed Current Tolerance           |                      |                                                    | 35              | 38    | 42                       | μA                 |

| Maximum Common-Mode Input Voltage  |                      | 7VLDO = 7.4V                                       | 5.7             |       |                          | V                  |

|                                    |                      | VCC = PVCC = 7VLDO = 4.5V                          | 2.8             |       |                          | V                  |

# **Electrical Specifications** All typical specifications $T_A = +25 \,^{\circ}$ C, $V_{CC} = 5V$ . Boldface limits apply across the operating temperature range, -40 $^{\circ}$ C to +85 $^{\circ}$ C, unless otherwise stated. (Continued)

| PARAMETER                                    | SYMBOL             | TEST CONDITIONS                   | MIN<br>( <u>Note 6</u> ) | TYP      | MAX<br>( <u>Note 6</u> ) | UNIT  |

|----------------------------------------------|--------------------|-----------------------------------|--------------------------|----------|--------------------------|-------|

| FAULT PROTECTION                             |                    |                                   | <u> </u>                 | <u> </u> |                          | Į.    |

| UVP Threshold Voltage                        |                    | Latch                             | 68                       | 74       | 80                       | % DAC |

| Start-Up OVP Threshold Voltage               |                    | 0V ≤ V <sub>BOOT</sub> ≤ 1.08V    | 1.10                     | 1.15     | 1.25                     | V     |

|                                              |                    | 1.08V < V <sub>BOOT</sub> ≤ 1.55V | 1.58                     | 1.65     | 1.75                     | V     |

|                                              |                    | 1.55V < V <sub>BOOT</sub> ≤ 1.85V | 1.88                     | 1.95     | 2.05                     | V     |

|                                              |                    | 1.85V < V <sub>BOOT</sub> ≤ 2.08V | 2.09                     | 2.15     | 2.25                     | V     |

|                                              |                    | 2.08V < V <sub>BOOT</sub> ≤ 2.53V | 2.56                     | 2.65     | 2.75                     | ٧     |

|                                              |                    | 2.53V < V <sub>BOOT</sub> ≤ 3.33V | 3.36                     | 3.45     | 3.6                      | ٧     |

|                                              |                    | 3.33V < V <sub>BOOT</sub> ≤ 5.5V  | 5.52                     | 5.65     | 5.85                     | V     |

| Start-Up OVP Hysteresis                      |                    |                                   |                          | 100      |                          | m۷    |

| OVP Rising Threshold Voltage                 | V <sub>OVRTH</sub> | 0.5 ≤ DAC ≤ 5.5                   | 114                      | 120      | 127                      | % DAC |

| OVP Falling Threshold Voltage                | V <sub>OVFTH</sub> | 0.5 ≤ DAC ≤ 5.5                   | 96                       | 100      | 108                      | % DAC |

| Over-Temperature Shutdown Threshold          |                    | READ_TEMP = 72h                   | 20                       | 22.31    | 26                       | % VCC |

| Over-Temperature Shutdown Reset Threshold    |                    | READ_TEMP = 8Eh                   | 25                       | 27.79    | 30                       | % VCC |

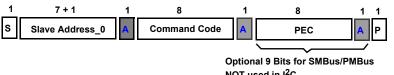

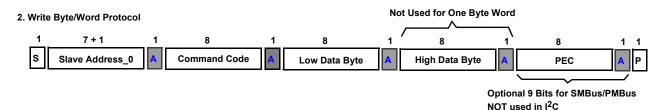

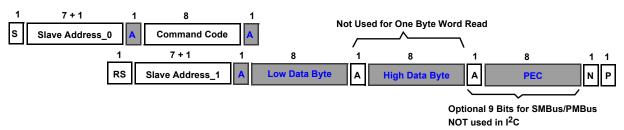

| SMBus/PMBus/I <sup>2</sup> C                 | ı                  |                                   |                          |          |                          |       |

| Signal Input Low Voltage                     |                    |                                   |                          |          | 1                        | V     |

| Signal Input High Voltage                    |                    |                                   | 1.6                      |          |                          | V     |

| Signal Output Low Voltage                    |                    | 4mA pull-up current               |                          |          | 0.4                      | ٧     |

| DATE, ALERT # Pull-Down Impedance            |                    |                                   |                          | 11       | 50                       | Ω     |

| CLOCK Maximum Speed                          |                    |                                   | 1.25                     |          |                          | MHz   |

| CLOCK Minimum Speed                          |                    |                                   |                          |          | 0.05                     | MHz   |

| Telemetry Update Rate                        |                    |                                   |                          | 108      |                          | μs    |

| Timeout                                      |                    |                                   | 25                       | 30       | 35                       | ms    |

| PMBus Accessible Timeout from All Rails' POR |                    | See Figure 21                     |                          | 5.5      | 6.5                      | ms    |

#### NOTE:

$<sup>\</sup>textbf{6. Compliance to datasheet limits is assured by one or more methods: production test, characterization, and/or design.}\\$

## **Operation**

The following sections provide a detailed description of the ISL68201 operation.

#### **IC Supplies**

The ISL68201 has four bias pins: VIN, 7VLDO, PVCC, and VCC. The PVCC and 7VLDO voltage rails are 5V LDO and 7.4V LDO supplied by VIN, respectively, while the VCC pin needs to connect to the PVCC rail externally to be biased. For 5V input applications, all these pins should be tied together and biased by a 5V supply. Because the VIN pin voltage information is used by the R4 Modulator loop, the user CANNOT bias VIN with a series resistor. In addition, the VIN pin CANNOT be biased independently from other rails.

#### **Enable and Disable**

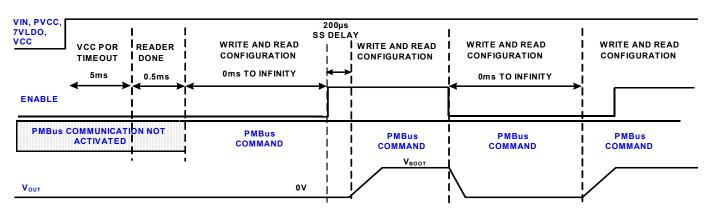

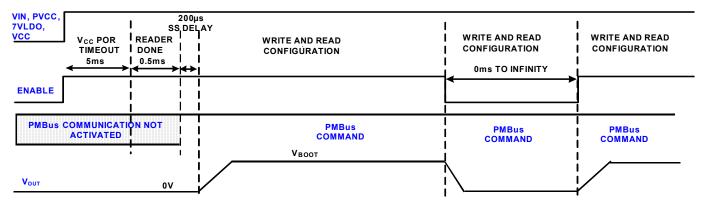

The IC is disabled until the 7VLDO, PVCC, VCC, VIN, and EN pins increase above their respective rising threshold voltages and the typical 5.5ms timeout (worst case = 6.5ms) expires, as shown in Figures 21 and 22 on page 22. The controller will become disabled when the 7VLDO, PVCC, VCC, VIN, or EN pins drop below their respective falling POR threshold voltages.

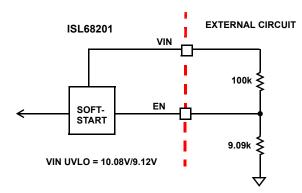

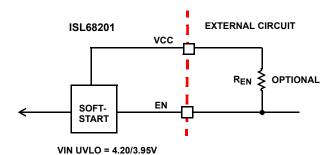

The precision threshold EN pin allows the user to set a precision input UVLO level with an external resistor divider, as shown in Figure 4. For 5V input applications or wide range input applications, the EN pin can directly connect to VCC, as shown in Figure 5. If an external enable control signal is available and is an open-drain signal, a pull-up impedance (100k or higher) can be used.

FIGURE 4. INPUT UVP CONFIGURATION

R<sub>EN</sub> is needed ONLY if the user wants to control the IC with an external enable signal

FIGURE 5. 5V INPUT OR WIDE RANGE INPUT CONFIGURATION

In addition, based on the ON\_OFF\_CONFIG [02h] setting, the IC can be enabled or disabled by the serial bus command "OPERATION [01h]" and/or EN pin. See <u>Table 11 on page 25</u> for more details.

#### **Resistor Reader (Patented)**

The ISL68201 offers four programming pins to customize their regulator specifications. The details of these pins are summarized in <u>Table 2</u>, followed by the detailed description of resistor reader operation.

**TABLE 2. DEFINITION OF PROG PINS**

| PIN   | BIT   | NAME                        | DESCRIPTION                                                                              |

|-------|-------|-----------------------------|------------------------------------------------------------------------------------------|

| PROG1 | [7:0] | BOOT-UP<br>VOLTAGE          | Set output boot-up voltage, 256 different options: 0, 0.5V to 5.5V (see <u>Table 7</u> ) |

| PROG2 | [7:7] | PWM/PFM                     | Enables PFM mode or forced PWM.                                                          |

|       | [6:5] | Temperature<br>Compensation | Adjust NTC temperature compensation: OFF, +5, +15, +30 °C.                               |

|       | [4:0] | ADDR                        | Set serial bus 32 different addresses (see Table 10).                                    |

| PROG3 | [7:7] | USPFM                       | Ultrasonic (25kHz Clamp) PFM enable                                                      |

|       | [6:6] | Fault Behavior              | OCP fault behavior:<br>Latch, Infinite 9ms retry                                         |

|       | [5:3] | f <sub>SW</sub>             | Set switching frequency (f <sub>SW</sub> ).                                              |

|       | [2:0] | R4 Gain                     | Set error amplifier gain (AV).                                                           |

| PROG4 | [7:5] | RAMP_RATE                   | Set soft-start and DVID ramp rate.                                                       |

|       | [4:3] | RR                          | Select RR impedance for R4 loop.                                                         |

|       | [2:2] | AVMLTI                      | Select AV gain multiplier (1x or 2x)                                                     |

|       | [1:0] | Not Used                    |                                                                                          |

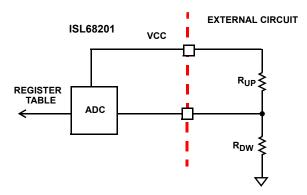

Intersil has developed a high resolution ADC using a patented technique with a simple 1%, 100ppm/K or better temperature coefficient resistor divider. The same type of resistors are preferred so that it has similar change over temperature. In addition, the divider is compared to the internal divider off  $V_{CC}$  and GND nodes and therefore must refer to VCC and GND pins, not through any RC decoupling network.

FIGURE 6. SIMPLIFIED RESISTOR DIVIDER ADC

The  $R_{UP}$  and  $R_{DW}$  values for a particular parameter set can be found using the Power Navigator GUI. Data for corresponding registers can be read out using the serial PMBus command (DC to DF). Note: The case of  $10 k\Omega~R_{UP}$  or  $R_{DW}$  is the same as  $0 k\Omega~R_{UP}$  or  $R_{DW}$ .

TABLE 3. PROG 1 RESISTOR READER EXAMPLE

| PROG1<br>(DC) | R <sub>UP</sub><br>(kΩ) | R <sub>DW</sub><br>(kΩ) | V <sub>ОUТ</sub><br>(V) |

|---------------|-------------------------|-------------------------|-------------------------|

| 00h           | Open                    | 0                       | 0.797                   |

| 20h           | Open                    | 21.5                    | 0.852                   |

| 40h           | Open                    | 34.8                    | 0.898                   |

| 60h           | Open                    | 52.3                    | 0.953                   |

| 80h           | Open                    | 75                      | 1.000                   |

| A0h           | Open                    | 105                     | 1.047                   |

| COh           | Open                    | 147                     | 1.102                   |

| EOh           | Open                    | 499                     | 1.203                   |

| 1Fh           | 0                       | Open                    | 1.352                   |

| 3Fh           | 21.5                    | Open                    | 1.500                   |

| 5Fh           | 34.8                    | Open                    | 1.797                   |

| 7Fh           | 52.3                    | Open                    | 2.500                   |

| 9Fh           | 75                      | Open                    | 3.000                   |

| BFh           | 105                     | Open                    | 3.297                   |

| DFh           | 147                     | Open                    | 5.000                   |

| FFh           | 499                     | Open                    | 0.000                   |

#### TABLE 4. PROG 2 RESISTOR READER EXAMPLE

| PROG2<br>(DD) | R <sub>UP</sub><br>(kΩ) | R <sub>DW</sub><br>(kΩ) | PWM/PFM  | TEMP<br>COMP | PM_ADDR<br>(7-BIT) |

|---------------|-------------------------|-------------------------|----------|--------------|--------------------|

| 00h           | Open                    | 0                       | Enabled  | 30           | 60h                |

| 20h           | Open                    | 21.5                    | Enabled  | 15           | 60h                |

| 40h           | Open                    | 34.8                    | Enabled  | 5            | 60h                |

| 60h           | Open                    | 52.3                    | Enabled  | OFF          | 60h                |

| 80h           | Open                    | 75                      | Disabled | 30           | 60h                |

| A0h           | Open                    | 105                     | Disabled | 15           | 60h                |

| COh           | Open                    | 147                     | Disabled | 5            | 60h                |

| E0h           | Open                    | 499                     | Disabled | OFF          | 60h                |

| 1Fh           | 0                       | Open                    | Enabled  | 30           | 7F                 |

| 3Fh           | 21.5                    | Open                    | Enabled  | 15           | 7F                 |

| 5Fh           | 34.8                    | Open                    | Enabled  | 5            | 7F                 |

| 7Fh           | 52.3                    | Open                    | Enabled  | OFF          | 7F                 |

| 9Fh           | 75                      | Open                    | Disabled | 30           | 7F                 |

| BFh           | 105                     | Open                    | Disabled | 15           | 7F                 |

| DFh           | 147                     | Open                    | Disabled | 5            | 7F                 |

| FFh           | 499                     | Open                    | Disabled | OFF          | 7F                 |

#### TABLE 5. PROG 3 RESISTOR READER EXAMPLE

| PROG3 | Rup         | R <sub>DW</sub> | Row ULTRASONIC FAUI |          | <b>f</b> a               | R4 0 | AIN |

|-------|-------------|-----------------|---------------------|----------|--------------------------|------|-----|

| (DE)  | KUP<br>(kΩ) | (kΩ)            | PFM                 | BEHAVIOR | <sup>f</sup> sw<br>(kHz) | 1x   | 2x  |

| 00h   | Open        | 0               | Disabled            | Retry    | 300                      | 42   | 84  |

| 20h   | Open        | 21.5            | Disabled            | Retry    | 700                      | 42   | 84  |

| 40h   | Open        | 34.8            | Disabled            | Latch    | 300                      | 42   | 84  |

| 60h   | Open        | 52.3            | Disabled            | Latch    | 700                      | 42   | 84  |

| 80h   | Open        | 75              | Enabled             | Retry    | 300                      | 42   | 84  |

| A0h   | Open        | 105             | Enabled             | Retry    | 700                      | 42   | 84  |

| COh   | Open        | 147             | Enabled             | Latch    | 300                      | 42   | 84  |

| E0h   | Open        | 499             | Enabled             | Latch    | 700                      | 42   | 84  |

| 1Fh   | 0           | Open            | Disabled            | Retry    | 600                      | 1    | 2   |

| 3Fh   | 21.5        | Open            | Disabled            | Retry    | 1500                     | 1    | 2   |

| 5Fh   | 34.8        | Open            | Disabled            | Latch    | 600                      | 1    | 2   |

| 7Fh   | 52.3        | Open            | Disabled            | Latch    | 1500                     | 1    | 2   |

| 9Fh   | 75          | Open            | Enabled             | Retry    | 600                      | 1    | 2   |

| BFh   | 105         | Open            | Enabled             | Retry    | 1500                     | 1    | 2   |

| DFh   | 147         | Open            | Enabled             | Latch    | 600                      | 1    | 2   |

| FFh   | 499         | Open            | Enabled             | Latch    | 1500                     | 1    | 2   |

#### **TABLE 6. PROG 4 RESISTOR READER EXAMPLE**

| PROG4<br>(DF | R <sub>UP</sub><br>(kΩ) | R <sub>DW</sub><br>(kΩ) | SS RATE<br>(mV/µs) | $ m RR \ (k\Omega)$ | AVMLTI     |

|--------------|-------------------------|-------------------------|--------------------|---------------------|------------|

| 00h          | Open                    | 0                       | 1.25               | 200                 | <b>1</b> x |

| 20h          | Open                    | 21.5                    | 2.5                | 200                 | <b>1</b> x |

| 40h          | Open                    | 34.8                    | 5                  | 200                 | <b>1</b> x |

| 60h          | Open                    | 52.3                    | 10                 | 200                 | <b>1</b> x |

| 80h          | Open                    | 75                      | 0.078              | 200                 | <b>1</b> x |

| A0h          | Open                    | 105                     | 0.157              | 200                 | <b>1</b> x |

| C0h          | Open                    | 147                     | 0.315              | 200                 | <b>1</b> x |

| E0h          | Open                    | 499                     | 0.625              | 200                 | <b>1</b> x |

| 1Fh          | 0                       | Open                    | 1.25               | 800                 | 2x         |

| 3Fh          | 21.5                    | Open                    | 2.5                | 800                 | 2x         |

| 5Fh          | 34.8                    | Open                    | 5                  | 800                 | 2x         |

| 7Fh          | 52.3                    | Open                    | 10                 | 800                 | 2x         |

| 9Fh          | 75                      | Open                    | 0.078              | 800                 | 2x         |

| BFh          | 105                     | Open                    | 0.157              | 800                 | 2x         |

| DFh          | 147                     | Open                    | 0.315              | 800                 | 2x         |

| FFh          | 499                     | Open                    | 0.625              | 800                 | 2x         |

#### **Soft-Start**

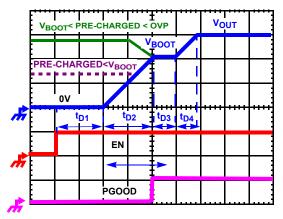

The ISL68201-based regulator has four periods during soft-start, as shown in Figure 7 on page 12. After a 5.5ms timeout (worst case = 6.5ms) of bias supplies, as shown in Figures 21 and 22 on page 22, when the EN pin reaches above its enable threshold, the controller begins the first soft-start ramp after a fixed soft-start delay period  $t_{D1}.$  The output voltage reaches the boot-up voltage (VBOOT) at a fixed slew rate in period  $t_{D2}.$  Then, the controller will regulate the output voltage at VBOOT for another period  $t_{D3}$  until SMBus/PMBus/  $I^2C$  sends a new VOUT command. If the VOUT command is valid, the ISL68201 will initiate the ramp until the voltage reaches the new VOUT\_COMMAND voltage in period  $t_{D4}.$  The soft-start time is the sum of the four periods, as shown in Equation 1.

$$t_{SS} = t_{D1} + t_{D2} + t_{D3} + t_{D4}$$

(EQ. 1)

$t_{D1}$  is a fixed delay with the typical value as  $200\mu s.\ t_{D3}$  is determined by the time to obtain a new valid VOUT\_COMMAND voltage from SMBus/PMBus/I $^2C$  bus. If the VOUT\_COMMAND is valid before the output reaches the boot-up voltage, the output will turn around to respond to the new VOUT\_COMMAND code.

FIGURE 7. SOFT-START WAVEFORMS

During  $t_{D2}$  and  $t_{D4}$ , the ISL68201 digitally controls the DAC voltage change. The ramp time  $t_{D2}$  and  $t_{D4}$  can be calculated based on Equations 2 and 3, after the slew rate is set by the PROG4 pin.

$$t_{D2} = \frac{V_{BOOT}}{RAMP\_RATE}(\mu s)$$

(EQ. 2)

$$t_{D4} = \frac{V_{OUT} - V_{BOOT}}{RAMP RATE}(\mu s)$$

(EQ. 3)

The ISL68201 supports precharged start-up, which initiates the first PWM pulse until the internal reference (DAC) reaches the precharged level at RAMP\_RATE, programmed by PROG4 or D5[2:0]. When the precharged level is below  $V_{BOOT}$ , the output walks up to the  $V_{BOOT}$  at RAMP\_RATE and releases PGOOD at  $t_{D1} + t_{D2}.$  When the precharged output is above  $V_{BOOT}$  but below OVP, it walks down to  $V_{BOOT}$  at RAMP\_RATE and then releases PGOOD at  $t_{D1} + t_{D2},$  in which  $t_{D2}$  is defined in Equation 4 and longer than a normal start-up.

The ISL68201 supports precharged load start-up to the maximum  $V_{OUT}$  of 5.5V with sufficient boot capacitor charge. For

$$t_{D2} = \frac{V_{PRECHARGED}}{RAMP\_RATE} + \frac{V_{PRECHARGED} - V_{BOOT}}{RAMP\_RATE} (\mu s) \tag{EQ. 4}$$

an extended precharged load, the boot capacitor will be discharged to "PVCC -  $V_{OUT}$  -  $V_{D}$ " by the high-side drive circuits' standby current. For instance, an extended 4V precharged load, the boot capacitor will reduce to a less-than-1V boot capacitor voltage, which is insufficient to power up the VR; in this case, it is recommended to let the output drop below 2.5V with an external bleed resistor before issuing another soft-start command.

#### **Boot-Up Voltage Programming**

An 8-bit pin PROG1 is dedicated for the boot-up voltage programmability, which offers 256 options OV and 0.5V to 5.5V, as in <u>Table 7</u>. The most popular boot-up voltage levels are placed on the tie-low spots (0h, 20h, 40h, 60h, 80h, A0h, C0h, E0h) and the tie-high spots (1Fh, 3Fh, 5Fh, 7Fh, 9Fh, BFh, DFh, FFh) for easy programming, as summarized in <u>Table 3</u>. OV boot-up voltage is considered as "OFF," the driver will be in tri-state and the internal DAC will set to OV.

In addition, if the VOUT\_COMMAND (21h) is executed successfully 5.5ms (typically, worst 6.5ms) after VCC POR and before Enable, it will override the boot-up voltage set by the PROG1 pin.

TABLE 7. PROG1 8-BIT (BOOT-UP VOLTAGE)

| BINARY<br>CODE | HEX<br>CODE | V <sub>BOOT</sub> (V) | VOUT<br>COMMAND<br>CODE (HEX) | DELTA FROM<br>PREVIOUS<br>CODE (mV) |

|----------------|-------------|-----------------------|-------------------------------|-------------------------------------|

| 00000000       | 0           | 0.7969                | 66                            |                                     |

| 0000001        | 1           | 0.5000                | 40                            |                                     |

| 00000010       | 2           | 0.5078                | 41                            | 7.8125                              |

| 00000011       | 3           | 0.5156                | 42                            | 7.8125                              |

| 00000100       | 4           | 0.5234                | 43                            | 7.8125                              |

| 00000101       | 5           | 0.5313                | 44                            | 7.8125                              |

| 00000110       | 6           | 0.5391                | 45                            | 7.8125                              |

| 00000111       | 7           | 0.5469                | 46                            | 7.8125                              |

| 00001000       | 8           | 0.5547                | 47                            | 7.8125                              |

| 00001001       | 9           | 0.5625                | 48                            | 7.8125                              |

| 00001010       | Α           | 0.5703                | 49                            | 7.8125                              |

| 00001011       | В           | 0.5781                | 4A                            | 7.8125                              |

| 00001100       | С           | 0.5859                | 4B                            | 7.8125                              |

| 00001101       | D           | 0.5938                | 4C                            | 7.8125                              |

| 00001110       | E           | 0.6016                | 4D                            | 7.8125                              |

| 00001111       | F           | 0.6094                | 4E                            | 7.8125                              |

| 00010000       | 10          | 0.6172                | 4F                            | 7.8125                              |

| 00010001       | 11          | 0.6250                | 50                            | 7.8125                              |

| 00010010       | 12          | 0.6328                | 51                            | 7.8125                              |

| 00010011       | 13          | 0.6406                | 52                            | 7.8125                              |

| 00010100       | 14          | 0.6484                | 53                            | 7.8125                              |

TABLE 7. PROG1 8-BIT (BOOT-UP VOLTAGE) (Continued)

| TABLE          | TABLE 7. PROG1 8-BIT (BOOT-UP VOLTAGE) (Continued) |                       |                               |                                     |  |  |  |

|----------------|----------------------------------------------------|-----------------------|-------------------------------|-------------------------------------|--|--|--|

| BINARY<br>CODE | HEX<br>CODE                                        | V <sub>BOOT</sub> (V) | VOUT<br>COMMAND<br>CODE (HEX) | DELTA FROM<br>PREVIOUS<br>CODE (mV) |  |  |  |

| 00010101       | 15                                                 | 0.6563                | 54                            | 7.8125                              |  |  |  |

| 00010110       | 16                                                 | 0.6641                | 55                            | 7.8125                              |  |  |  |

| 00010111       | 17                                                 | 0.6719                | 56                            | 7.8125                              |  |  |  |

| 00011000       | 18                                                 | 0.6797                | 57                            | 7.8125                              |  |  |  |

| 00011001       | 19                                                 | 0.6875                | 58                            | 7.8125                              |  |  |  |

| 00011010       | 1A                                                 | 0.6953                | 59                            | 7.8125                              |  |  |  |

| 00011011       | 1B                                                 | 0.7031                | 5A                            | 7.8125                              |  |  |  |

| 00011100       | 10                                                 | 0.7109                | 5B                            | 7.8125                              |  |  |  |

| 00011101       | 1D                                                 | 0.7188                | 5C                            | 7.8125                              |  |  |  |

| 00011110       | 1E                                                 | 0.7266                | 5D                            | 7.8125                              |  |  |  |

| 00011111       | 1F                                                 | 1.3516                | AD                            |                                     |  |  |  |

| 00100000       | 20                                                 | 0.8516                | 6D                            |                                     |  |  |  |

| 00100001       | 21                                                 | 0.7344                | 5E                            | 7.8125                              |  |  |  |

| 00100010       | 22                                                 | 0.7422                | 5F                            | 7.8125                              |  |  |  |

| 00100011       | 23                                                 | 0.7500                | 60                            | 7.8125                              |  |  |  |

| 00100100       | 24                                                 | 0.7578                | 61                            | 7.8125                              |  |  |  |

| 00100101       | 25                                                 | 0.7656                | 62                            | 7.8125                              |  |  |  |

| 00100110       | 26                                                 | 0.7734                | 63                            | 7.8125                              |  |  |  |

| 00100111       | 27                                                 | 0.7813                | 64                            | 7.8125                              |  |  |  |

| 00101000       | 28                                                 | 0.7891                | 65                            | 7.8125                              |  |  |  |

| 00101001       | 29                                                 | 0.7969                | 66                            | 7.8125                              |  |  |  |

| 00101010       | 2A                                                 | 0.8047                | 67                            | 7.8125                              |  |  |  |

| 00101011       | 2B                                                 | 0.8125                | 68                            | 7.8125                              |  |  |  |

| 00101100       | 2C                                                 | 0.8203                | 69                            | 7.8125                              |  |  |  |

| 00101101       | 2D                                                 | 0.8281                | 6A                            | 7.8125                              |  |  |  |

| 00101110       | 2E                                                 | 0.8359                | 6B                            | 7.8125                              |  |  |  |

| 00101111       | 2F                                                 | 0.8438                | 6C                            | 7.8125                              |  |  |  |

| 00110000       | 30                                                 | 0.8516                | 6D                            | 7.8125                              |  |  |  |

| 00110001       | 31                                                 | 0.8594                | 6E                            | 7.8125                              |  |  |  |

| 00110010       | 32                                                 | 0.8672                | 6F                            | 7.8125                              |  |  |  |

| 00110011       | 33                                                 | 0.8750                | 70                            | 7.8125                              |  |  |  |

| 00110100       | 34                                                 | 0.8828                | 71                            | 7.8125                              |  |  |  |

| 00110101       | 35                                                 | 0.8906                | 72                            | 7.8125                              |  |  |  |

| 00110110       | 36                                                 | 0.8984                | 73                            | 7.8125                              |  |  |  |

| 00110111       | 37                                                 | 0.9063                | 74                            | 7.8125                              |  |  |  |

| 00111000       | 38                                                 | 0.9141                | 75                            | 7.8125                              |  |  |  |

| 00111001       | 39                                                 | 0.9219                | 76                            | 7.8125                              |  |  |  |

| 00111010       | 3A                                                 | 0.9297                | 77                            | 7.8125                              |  |  |  |

| 00111011       | 3B                                                 | 0.9375                | 78                            | 7.8125                              |  |  |  |

TABLE 7. PROG1 8-BIT (BOOT-UP VOLTAGE) (Continued)

| BINARY<br>CODE | HEX<br>CODE | V <sub>BOOT</sub> (V) | VOUT<br>COMMAND<br>CODE (HEX) | DELTA FROM<br>PREVIOUS<br>CODE (mV) |

|----------------|-------------|-----------------------|-------------------------------|-------------------------------------|

| 00111100       | 3C          | 0.9453                | 79                            | 7.8125                              |

| 00111101       | 3D          | 0.9531                | 7A                            | 7.8125                              |

| 00111110       | 3E          | 0.9609                | 7B                            | 7.8125                              |

| 00111111       | 3F          | 1.5000                | CO                            |                                     |

| 01000000       | 40          | 0.8984                | 73                            |                                     |

| 01000001       | 41          | 0.9688                | 7C                            | 7.8125                              |

| 01000010       | 42          | 0.9766                | 7D                            | 7.8125                              |

| 01000011       | 43          | 0.9844                | 7E                            | 7.8125                              |

| 01000100       | 44          | 0.9922                | 7F                            | 7.8125                              |

| 01000101       | 45          | 1.0000                | 80                            | 7.8125                              |

| 01000110       | 46          | 1.0078                | 81                            | 7.8125                              |

| 01000111       | 47          | 1.0156                | 82                            | 7.8125                              |

| 01001000       | 48          | 1.0234                | 83                            | 7.8125                              |

| 01001001       | 49          | 1.0313                | 84                            | 7.8125                              |

| 01001010       | 4A          | 1.0391                | 85                            | 7.8125                              |

| 01001011       | 4B          | 1.0469                | 86                            | 7.8125                              |

| 01001100       | 4C          | 1.0547                | 87                            | 7.8125                              |

| 01001101       | 4D          | 1.0625                | 88                            | 7.8125                              |

| 01001110       | 4E          | 1.0703                | 89                            | 7.8125                              |

| 01001111       | 4F          | 1.0781                | 8A                            | 7.8125                              |

| 01010000       | 50          | 1.0859                | 8B                            | 7.8125                              |

| 01010001       | 51          | 1.0938                | 80                            | 7.8125                              |

| 01010010       | 52          | 1.1016                | 8D                            | 7.8125                              |

| 01010011       | 53          | 1.1094                | 8E                            | 7.8125                              |

| 01010100       | 54          | 1.1172                | 8F                            | 7.8125                              |

| 01010101       | 55          | 1.1250                | 90                            | 7.8125                              |

| 01010110       | 56          | 1.1328                | 91                            | 7.8125                              |

| 01010111       | 57          | 1.1406                | 92                            | 7.8125                              |

| 01011000       | 58          | 1.1484                | 93                            | 7.8125                              |

| 01011001       | 59          | 1.1563                | 94                            | 7.8125                              |

| 01011010       | 5A          | 1.1641                | 95                            | 7.8125                              |

| 01011011       | 5B          | 1.1719                | 96                            | 7.8125                              |

| 01011100       | 5C          | 1.1797                | 97                            | 7.8125                              |

| 01011101       | 5D          | 1.1875                | 98                            | 7.8125                              |

| 01011110       | 5E          | 1.1953                | 99                            | 7.8125                              |

| 01011111       | 5F          | 1.7969                | <b>E</b> 6                    |                                     |

| 01100000       | 60          | 0.9531                | 7A                            |                                     |

| 01100001       | 61          | 1.2031                | 9A                            | 7.8125                              |

| 01100010       | 62          | 1.2109                | 9B                            | 7.8125                              |

TABLE 7. PROG1 8-BIT (BOOT-UP VOLTAGE) (Continued)

| BINARY   | HEX  | V <sub>BOOT</sub> | VOUT<br>COMMAND | DELTA FROM<br>PREVIOUS |

|----------|------|-------------------|-----------------|------------------------|

| CODE     | CODE | (V)               | CODE (HEX)      | CODE (mV)              |

| 01100011 | 63   | 1.2188            | 9C              | 7.8125                 |

| 01100100 | 64   | 1.2266            | 9D              | 7.8125                 |

| 01100101 | 65   | 1.2344            | 9E              | 7.8125                 |

| 01100110 | 66   | 1.2422            | 9F              | 7.8125                 |

| 01100111 | 67   | 1.2500            | A0              | 7.8125                 |

| 01101000 | 68   | 1.2578            | A1              | 7.8125                 |

| 01101001 | 69   | 1.2656            | A2              | 7.8125                 |

| 01101010 | 6A   | 1.2734            | А3              | 7.8125                 |

| 01101011 | 6B   | 1.2813            | A4              | 7.8125                 |

| 01101100 | 6C   | 1.2891            | A5              | 7.8125                 |

| 01101101 | 6D   | 1.2969            | A6              | 7.8125                 |

| 01101110 | 6E   | 1.3047            | A7              | 7.8125                 |

| 01101111 | 6F   | 1.3125            | A8              | 7.8125                 |

| 01110000 | 70   | 1.3203            | А9              | 7.8125                 |

| 01110001 | 71   | 1.3281            | AA              | 7.8125                 |

| 01110010 | 72   | 1.3359            | AB              | 7.8125                 |

| 01110011 | 73   | 1.3438            | AC              | 7.8125                 |

| 01110100 | 74   | 1.3516            | AD              | 7.8125                 |

| 01110101 | 75   | 1.3594            | AE              | 7.8125                 |

| 01110110 | 76   | 1.3672            | AF              | 7.8125                 |

| 01110111 | 77   | 1.3750            | В0              | 7.8125                 |

| 01111000 | 78   | 1.3828            | B1              | 7.8125                 |

| 01111001 | 79   | 1.3906            | B2              | 7.8125                 |

| 01111010 | 7A   | 1.3984            | В3              | 7.8125                 |

| 01111011 | 7B   | 1.4063            | B4              | 7.8125                 |

| 01111100 | 7C   | 1.4141            | B5              | 7.8125                 |

| 01111101 | 7D   | 1.4219            | В6              | 7.8125                 |

| 01111110 | 7E   | 1.4297            | В7              | 7.8125                 |

| 01111111 | 7F   | 2.5000            | 140             |                        |

| 10000000 | 80   | 1.0000            | 80              |                        |

| 10000001 | 81   | 1.4375            | В8              | 7.8125                 |

| 10000010 | 82   | 1.4453            | В9              | 7.8125                 |

| 10000011 | 83   | 1.4531            | ВА              | 7.8125                 |

| 10000100 | 84   | 1.4609            | ВВ              | 7.8125                 |

| 10000101 | 85   | 1.4688            | ВС              | 7.8125                 |

| 10000110 | 86   | 1.4766            | BD              | 7.8125                 |

| 10000111 | 87   | 1.4844            | BE              | 7.8125                 |

| 10001000 | 88   | 1.4922            | BF              | 7.8125                 |

| 10001001 | 89   | 1.5000            | CO              | 7.8125                 |

TABLE 7. PROG1 8-BIT (BOOT-UP VOLTAGE) (Continued)

| BINARY<br>CODE | HEX<br>CODE | V <sub>BOOT</sub> (V) | VOUT<br>COMMAND<br>CODE (HEX) | DELTA FROM<br>PREVIOUS<br>CODE (mV) |

|----------------|-------------|-----------------------|-------------------------------|-------------------------------------|

| 10001010       | 8A          | 1.5078                | C1                            | 7.8125                              |

| 10001011       | 8B          | 1.5156                | C2                            | 7.8125                              |

| 10001100       | 8C          | 1.5234                | С3                            | 7.8125                              |

| 10001101       | 8D          | 1.5313                | C4                            | 7.8125                              |

| 10001110       | 8E          | 1.5391                | C5                            | 7.8125                              |

| 10001111       | 8F          | 1.5469                | C6                            | 7.8125                              |

| 10010000       | 90          | 1.5547                | C7                            | 7.8125                              |

| 10010001       | 91          | 1.5625                | C8                            | 7.8125                              |

| 10010010       | 92          | 1.5703                | C9                            | 7.8125                              |

| 10010011       | 93          | 1.5781                | CA                            | 7.8125                              |

| 10010100       | 94          | 1.5859                | СВ                            | 7.8125                              |

| 10010101       | 95          | 1.5938                | СС                            | 7.8125                              |

| 10010110       | 96          | 1.6016                | CD                            | 7.8125                              |

| 10010111       | 97          | 1.6094                | CE                            | 7.8125                              |

| 10011000       | 98          | 1.6172                | CF                            | 7.8125                              |

| 10011001       | 99          | 1.6250                | D0                            | 7.8125                              |

| 10011010       | 9A          | 1.6328                | D1                            | 7.8125                              |

| 10011011       | 9B          | 1.6406                | D2                            | 7.8125                              |

| 10011100       | 9C          | 1.6484                | D3                            | 7.8125                              |

| 10011101       | 9D          | 1.6563                | D4                            | 7.8125                              |

| 10011110       | 9E          | 1.6641                | D5                            | 7.8125                              |

| 10011111       | 9F          | 3.0000                | 180                           |                                     |

| 10100000       | AO          | 1.0469                | 86                            |                                     |

| 10100001       | A1          | 1.6719                | D6                            | 7.8125                              |

| 10100010       | A2          | 1.6797                | D7                            | 7.8125                              |

| 10100011       | А3          | 1.6875                | D8                            | 7.8125                              |

| 10100100       | A4          | 1.6953                | D9                            | 7.8125                              |

| 10100101       | A5          | 1.7031                | DA                            | 7.8125                              |

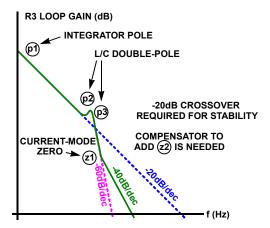

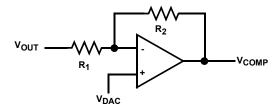

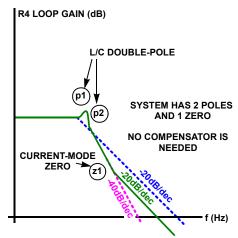

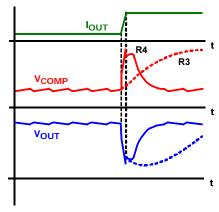

| 10100110       | A6          | 1.7109                | DB                            | 7.8125                              |