#### INSULATED GATE BIPOLAR TRANSISTOR

$$V_{CES} = 1200V$$

$$I_{C(Nominal)} = 50A$$

$$T_{J(max)} = 175^{\circ}C$$

$$V_{CE(on)} typ = 1.9V @ I_{C} = 50A$$

#

# G C E Gate Collector Emitter

## **Applications**

- Medium Power Drives

- UPS

- HEV Inverter

- Welding

- Induction Heating

| Features —                                            | → Benefits                                                                                |

|-------------------------------------------------------|-------------------------------------------------------------------------------------------|

|                                                       | High efficiency in a wide range of applications and switching frequencies                 |

|                                                       | Improved Reliability due to rugged hard switching performance and higher power capability |

| Positive V <sub>CE (ON)</sub> Temperature Coefficient | Excellent current sharing in parallel operation                                           |

| Dogo nort number | Doolsono Tymo | Standa | rd Pack  | Orderable part number |  |

|------------------|---------------|--------|----------|-----------------------|--|

| Base part number | Package Type  | Form   | Quantity |                       |  |

| IRG7CH54K10EF    | Die on Film   | Wafer  | 1        | IRG7CH54K10EF         |  |

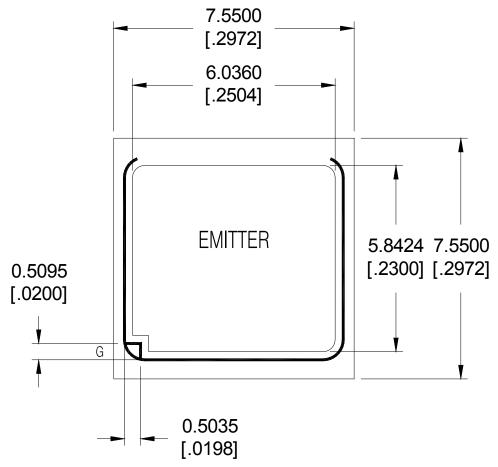

### **Mechanical Parameter**

| Die Size                            | 7.55 x 7.55 mm <sup>2</sup>                    |                 |  |  |  |

|-------------------------------------|------------------------------------------------|-----------------|--|--|--|

| Minimum Street Width                | 75                                             | μm              |  |  |  |

| Emiter Pad Size (Included Gate Pad) | See Die Drawing                                |                 |  |  |  |

| Gate Pad Size                       | 0.509 x 0.503                                  | mm <sup>2</sup> |  |  |  |

| Area Total / Active                 | 57/ 40.1                                       |                 |  |  |  |

| Thickness                           | 140                                            | μm              |  |  |  |

| Wafer Size                          | 200                                            | mm              |  |  |  |

| Notch Position                      | 0                                              | Degrees         |  |  |  |

| Maximum-Possible Chips per Wafer    | 465 pcs.                                       |                 |  |  |  |

| Passivation Front side              | Silicon Nitride                                | Silicon Nitride |  |  |  |

| Front Metal                         | Al, Si (4µm)                                   | Al, Si (4μm)    |  |  |  |

| Backside Metal                      | Al (0.1μm), Ti (0.1μm), Ni (0.4μm), Ag (0.6μm) |                 |  |  |  |

| Die Bond                            | Electrically conductive epoxy or solder        |                 |  |  |  |

| Reject Ink Dot Size                 | 0.25 mm diameter minimum                       |                 |  |  |  |

www.irf.com © 2012 International Rectifier August 30, 2012

**Maximum Ratings**

|                  | Parameter                                       | Max.        | Units |

|------------------|-------------------------------------------------|-------------|-------|

| $V_{CE}$         | Collector-Emitter Voltage, T <sub>J</sub> =25°C | 1200        | V     |

| $I_{C}$          | DC Collector Current                            | ①           | Α     |

| I <sub>LM</sub>  | Clamped Inductive Load Current ④                | 200         | Α     |

| $V_{\sf GE}$     | Gate Emitter Voltage                            | ± 30        | V     |

| $T_{J}, T_{STG}$ | Operating Junction and Storage Temperature      | -40 to +175 | °C    |

# Static Characteristics (Tested on wafers) . T<sub>J</sub>=25°C

|                      | Parameter                              | Min. | Тур. | Max.  | Units | Conditions                                       |

|----------------------|----------------------------------------|------|------|-------|-------|--------------------------------------------------|

| V <sub>(BR)CES</sub> | Collector-to-Emitter Breakdown Voltage | 1200 |      |       | V     | V <sub>GE</sub> = 0V, I <sub>C</sub> = 250μA ⑤   |

| V <sub>CE(sat)</sub> | Collector-to-Emitter Saturated Voltage |      | 1.25 | 1.5   |       | $V_{GE} = 15V, I_{C} = 10A, T_{J} = 25^{\circ}C$ |

| $V_{GE(th)}$         | Gate-Emitter Threshold Voltage         | 5.0  |      | 7.5   |       | $I_C = 2.4 \text{mA}$ , $V_{GE} = V_{CE}$        |

| I <sub>CES</sub>     | Zero Gate Voltage Collector Current    |      | 1.0  | 25    | μA    | V <sub>CE</sub> = 1200V, V <sub>GE</sub> = 0V    |

| I <sub>GES</sub>     | Gate Emitter Leakage Current           |      |      | ± 200 | nA    | $V_{CE} = 0V$ , $V_{GE} = \pm 30V$               |

|                      | Parameter                              | Min.        | Тур. | Max. | Units                                                                                                               | Conditions                                                                                                        |

|----------------------|----------------------------------------|-------------|------|------|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| V <sub>CE(sat)</sub> | Collector-to-Emitter Saturated Voltage |             | 1.9  | 2.3  | V                                                                                                                   | V <sub>GE</sub> = 15V, I <sub>C</sub> = 50A , T <sub>J</sub> = 25°C                                               |

|                      |                                        |             | 2.5  |      |                                                                                                                     | V <sub>GE</sub> = 15V, I <sub>C</sub> = 50A , T <sub>J</sub> = 175°C                                              |

| SCSOA                | Short Circuit Safe Operating Area      | 10          |      |      |                                                                                                                     | V <sub>GE</sub> =15V, V <sub>CC</sub> =600V, ②<br>R <sub>G</sub> =5Ω, V <sub>P</sub> ≤1200V,T <sub>J</sub> =150°C |

| RBSOA                | Reverse Bias Safe Operating Area       | FULL SQUARE |      |      | $T_J = 175^{\circ}C$ , $I_C = 200A$<br>$V_{CC} = 960V$ , $Vp \le 1200V$<br>$Rg = 5\Omega$ , $V_{GE} = +20V$ to $0V$ |                                                                                                                   |

| C <sub>iss</sub>     | Input Capacitance                      |             | 6240 |      | pF                                                                                                                  | V <sub>GE</sub> = 0V                                                                                              |

| $C_{oss}$            | Output Capacitance                     |             | 230  |      |                                                                                                                     | V <sub>CE</sub> = 30V                                                                                             |

| $C_{rss}$            | Reverse Transfer Capacitance           |             | 150  |      |                                                                                                                     | f = 1.0MHz                                                                                                        |

| $Q_g$                | Total Gate Charge (turn-on)            | _           | 290  | _    | nC                                                                                                                  | I <sub>C</sub> = 50A ⑥                                                                                            |

| $Q_{ge}$             | Gate-to-Emitter Charge (turn-on)       | _           | 60   | _    |                                                                                                                     | V <sub>GE</sub> = 15V                                                                                             |

| $Q_{gc}$             | Gate-to-Collector Charge (turn-on)     | _           | 130  | _    |                                                                                                                     | V <sub>CC</sub> = 600V                                                                                            |

|                | Parameter           | Min. | Тур. | Max. | Units | Conditions ③                                      |

|----------------|---------------------|------|------|------|-------|---------------------------------------------------|

|                |                     |      |      |      |       |                                                   |

| $t_{d(on)}$    | Turn-On delay time  |      | 75   | _    |       | $I_{\rm C}$ = 50A, $V_{\rm CC}$ = 600V            |

| t <sub>r</sub> | Rise time           | _    | 60   | _    |       | $R_G = 5\Omega$ , $V_{GE} = 15V$ , $L = 200\mu H$ |

| $t_{d(off)}$   | Turn-Off delay time | _    | 305  | _    |       | $T_J = 25^{\circ}C$                               |

| t <sub>f</sub> | Fall time           | _    | 55   | _    |       |                                                   |

| $t_{d(on)}$    | Turn-On delay time  | _    | 70   | _    |       | $I_{\rm C}$ = 50A, $V_{\rm CC}$ = 600V            |

| t <sub>r</sub> | Rise time           | _    | 60   | _    |       | $R_G = 5\Omega$ , $V_{GE} = 15V$ , $L = 200\mu H$ |

| $t_{d(off)}$   | Turn-Off delay time | _    | 345  | _    |       | T <sub>J</sub> = 175°C                            |

| t <sub>f</sub> | Fall time           | _    | 185  | _    |       |                                                   |

www.irf.com © 2012 International Rectifier August 30, 2012

# Die Drawing

#### NOTES:

- 1. ALL DIMENSIONS ARE SHOWN IN MILLIMETERS [INCHES].

- 2. CONTROLLING DIMENSION: MILLIMETERS

- 3. LETTER DESIGNATION:

S = SOURCE SK = SOURCE KELVIN E = EMITTER

G = GATE IS = CURRENTSENSE

4. DIMENSIONAL TOLERANCES:

BONDING PADS: < 0.635 TOLERANCE = +/- 0.013

WIDTH < [.0250] TOLERANCE = +/- [.0005]

& > 0.635 TOLERANCE = +/- 0.025

LENGTH > [.0250] TOLERANCE = +/- [.0010]

OVERALL DIE: < 1.270 TOLERANCE = +/- 0.102

WIDTH < [.050] TOLERANCE = +/- [.004]

& > 1.270 TOLERANCE = +/- 0.203

LENGTH > [.050] TOLERANCE = +/- [.008]

5. DIE THICKNESS = 0.140 [.0055] TOL: = 0.007 [.0003]

REFERENCE: IRG7CH54K10B

#### Notes:

- ① The current in the application is limited by T<sub>JMax</sub> and the thermal properties of the assembly.

- ② Not subject to production test- Verified by design / characterization.

- 3 Values influenced by parasitic L and C in measurement.

- Φ V<sub>CC</sub> = 80% (V<sub>CES</sub>), V<sub>GE</sub> = 20V, L = 19μH, R<sub>G</sub> = ΦΩ.

- S Refer to AN-1086 for guidelines for measuring V<sub>(BR)CES</sub> safely

- 6 Die Level Characterization.

#### **Additional Testing and Screening**

For Customers requiring product supplied as Known Good Die (KGD) or requiring specific die level testing, please contact your local IR Sales.

#### **Shipping**

Sawn Wafer on Film. Please contact your local IR sales office for non- standard shipping options

#### Handling

- Product must be handled only at ESD safe workstations. Standard ESD precautions and safe work environments are as defined in MIL-HDBK-263.

- Product must be handled only in a class 10,000 or better-designated clean room environment.

- Singulated die are not to be handled with tweezers. A vacuum wand with a non-metallic ESD protected tip should be used.

#### Wafer/Die Storage

- Proper storage conditions are necessary to prevent product contamination and/or degradation after shipment.

- Note: To reduce the risk of contamination or degradation, it is recommended that product not being used in the

assembly process be returned to their original containers and resealed with a vacuum seal process.

- Sawn wafers on a film frame are intended for immediate use and have a limited shelf life.

# **Further Information**

For further information please contact your local IR Sales office or email your enquiry to http://die.irf.com

Data and specifications subject to change without notice. This product has been designed and qualified for Industrial market.

Qualification Standards can be found on IR's Web site.

IR WORLD HEADQUARTERS: 101N. Sepulveda Blvd, El Segundo, California 90245, USA Tel: (310) 252-7105

TAC Fax: (310) 252-7903

Visit us at www.irf.com for sales contact information.