# Fixed Gain Dual Port Class-G Differential xDSL Line Driver

### **ISL1561**

The ISL1561 is a fixed gain dual port class-G differential amplifier designed for driving full rate ADSL2+ and VDSL2 signals at very low power dissipation. The driver runs on a single +14V power supply and internally generates higher supply voltages when needed to enable power efficient operation for high peak-to-average ratio (PAR) ADSL2+ and VDSL2 signals.

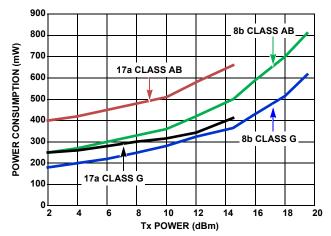

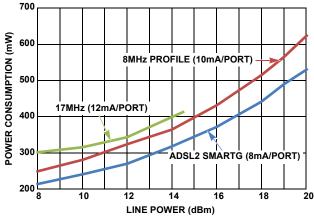

In ADSL2+ mode of operation with full 19.8dBm transmit signal power across 100 $\Omega$  line load, each port consumes only 520mW of power, while with 19.5dBm VDSL2 8b profile a port consumes 610mW of power. In VDSL2 17a mode of operation with 14.5dBm transmit power, a port will consume 411mW of power. These typical power consumption figures account for receiver hybrid loading effects and transformer losses.

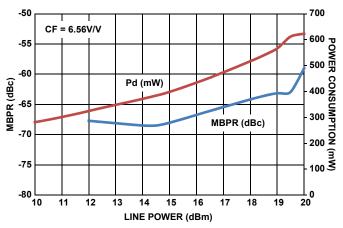

The ISL1561 provides two ports of wideband, current feedback amplifiers optimized for low power consumption in xDSL systems. The drivers achieve an average upstream missing band power ratio (MBPR) distortion of better than -64dBc under 19.8dBm transmit signal power into  $100\Omega$  load. A three pin serial interface is used to program an 8-bit internal register to set each port's supply current with 0.5mA step size. This flexibility allows the DSP to optimize each port separately during modem training.

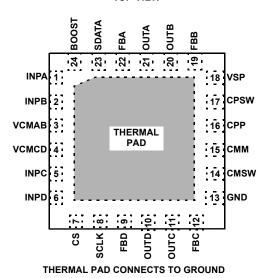

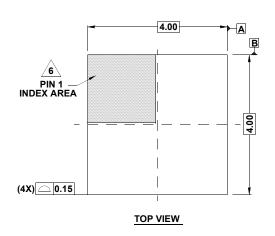

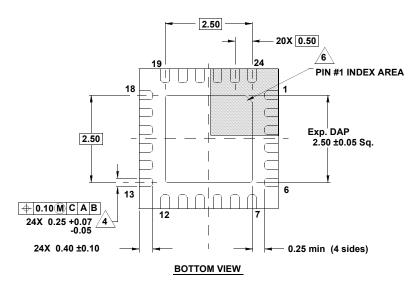

The device is supplied in a thermally-enhanced small footprint (4mmx4mm) 24 lead QFN package. The ISL1561 is specified for operation over the full -40 °C to +85 °C industrial temperature range and is Pb-free RoHS compliant.

### **Features**

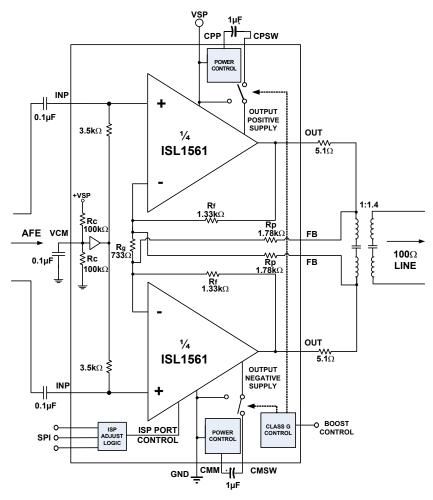

- Internal fixed gain of 11.6V/V to transformer (see Figure 3)

- · 360mA output drive capability

- 41.8V<sub>P-P</sub> differential output drive into 100 $\Omega$  in class G mode

- VDSL2 8b profile MTPR of -64dBc

- VDSL2 17a profile MTPR of -60dBc

- ADSL2+, VDSL2 8b and 17a power consumption of 520mW, 610mW and 411mW respectively

- 8-bit programmable register to set supply current on each port

- · 3 pin serial port interface

## **Applications**

• Dual port ADSL2+ and VDSL2 DSLAM

### Alternate Part

• ISL1591 Class AB VDSL Driver

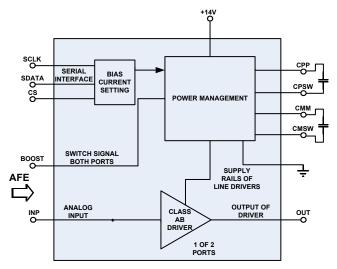

FIGURE 1. BLOCK DIAGRAM

FIGURE 2. CLASS G+ vs CLASS AB DRIVER TOTAL POWER

## **Pin Configuration**

**Pin Descriptions**

| ISL1561<br>(24 Ld QFN) | PIN<br>NAME | FUNCTION                                     |

|------------------------|-------------|----------------------------------------------|

| 1                      | INPA        | Amplifier A non-inverting input              |

| 2                      | INPB        | Amplifier B non-inverting input              |

| 3                      | VCMAB       | Input common mode bias for port AB           |

| 4                      | VCMCD       | Input common mode bias for port CD           |

| 5                      | INPC        | Amplifier C non-inverting input              |

| 6                      | INPD        | Amplifier D non-inverting input              |

| 7                      | CS          | Chip select, low enables data input to logic |

| 8                      | SCLK        | Serial clock input                           |

| 9                      | FBD         | Feedback pin for amplifier D                 |

| 10                     | OUTD        | Amplifier D output                           |

| 11                     | OUTC        | Amplifier C output                           |

| 12                     | FBC         | Feedback pin for amplifier C                 |

| 13                     | GND         | Ground                                       |

| 14                     | CMSW        | Internal negative boost supply               |

| 15                     | СММ         | Internal negative supply                     |

| 16                     | CPP         | Internal positive supply                     |

| 17                     | CPSW        | Internal positive boost supply               |

| 18                     | VSP         | Positive supply voltage                      |

| 19                     | FBB         | Feedback pin for amplifier B                 |

| 20                     | OUTB        | Amplifier B output                           |

| 21                     | OUTA        | Amplifier A output                           |

| 22                     | FBA         | Feedback pin for amplifier A                 |

| 23                     | SDATA       | Serial data write                            |

| 24                     | BOOST       | Class G control input                        |

TYPICAL DIFFERENTIAL I/O LINE DRIVER (1 OF 2 PORTS)

FIGURE 3. CONNECTION DIAGRAM

## **Ordering Information**

| PART NUMBER<br>(Notes 2, 3) | PART<br>MARKING | OPERATING AMBIENT<br>TEMP RANGE<br>(°C) | PACKAGE<br>(Pb-free) | PKG.<br>DWG. # |

|-----------------------------|-----------------|-----------------------------------------|----------------------|----------------|

| ISL1561IRZ                  | 15 61IRZ        | -40 to +85                              | 24 Ld QFN            | L24.4x4H       |

| ISL1561IRZ-T13 (Note 1)     | 15 61IRZ        | -40 to +85                              | 24 Ld QFN            | L24.4x4H       |

#### NOTES:

- 1. Please refer to TB347 for details on reel specifications.

- 2. These Intersil Pb-free plastic packaged products employ special Pb-free material sets, molding compounds/die attach materials, and 100% matte tin plate plus anneal (e3 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations). Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

- 3. For Moisture Sensitivity Level (MSL), please see device information page for ISL1561. For more information on MSL please see tech brief TB363.

## Absolute Maximum Ratings $(T_A = +25$ °C)

| V <sub>S</sub> + Voltage to GND                     | 0.3V to +15V            |

|-----------------------------------------------------|-------------------------|

| Driver V <sub>IN</sub> + Voltage                    | GND to V <sub>S</sub> + |

| SPI and Boost Pin Voltage to GND                    | 0.3V to +6V             |

| V <sub>CM</sub> Voltage to GND                      | GND to V <sub>S</sub> + |

| Current into any Input                              | 8mA                     |

| Continuous Output Current for Long Term Reliability | 50mA                    |

| ESD Rating                                          |                         |

| Human Body Model (Tested per JESD22-A114F)          | 3kV                     |

| Machine Model (Tested per JESD22-A115C)             | 300V                    |

| Charge Device Model (Tested per JESD22-C101E)       |                         |

|                                                     |                         |

#### **Thermal Information**

| Thermal Resistance (Typical)       | θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> (°C/W) |

|------------------------------------|------------------------|------------------------|

| 24 Ld QFN Package (Notes 4, 5)     | 44                     | 5                      |

| Maximum Junction Temperature (Plas | stic Package)          | +150°C                 |

| Power Dissipation                  | See Per                | formance Curve         |

| Storage Temperature Range          | 40                     | 0°C to +150°C          |

| Pb-Free Reflow Profile             |                        | see link below         |

| http://www.intersil.com/pbfree/Pb  | -FreeReflow.asp        |                        |

|                                    |                        |                        |

## **Operating Conditions**

| Ambient Temperature Range  | 40°C to +85°C  |

|----------------------------|----------------|

| Junction Temperature Range | 40°C to +150°C |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 4. θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

- 5. For  $\theta_{1C}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

**Electrical Specifications**  $V_{SP}$  = +14V,  $R_{L-DIFF}$  = 51 $\Omega$  differential (emulating transformer input load), Refer to Figure 3,  $T_A$  = +25°C. Ports tested separately unless otherwise indicated.

| PARAMETER         | DESCRIPTION                                          | CONDITIONS                                                                       | MIN<br>(Note 6) | TYP  | MAX<br>(Note 6) | UNIT               |

|-------------------|------------------------------------------------------|----------------------------------------------------------------------------------|-----------------|------|-----------------|--------------------|

| AC PERFORMANCE    |                                                      |                                                                                  | 1               |      | '               |                    |

| AV                |                                                      | Gain Across the Load, $R_B = 5.1\Omega$                                          |                 | 11.6 |                 | V/V                |

| BW                | -3dB Bandwidth                                       | I <sub>S</sub> = 14mA/port, V <sub>0</sub> < 2V <sub>PP-DIFF</sub>               |                 | 110  |                 | MHz                |

|                   |                                                      | I <sub>S</sub> = 10mA/port, V <sub>0</sub> = 5V <sub>PP-DIFF</sub>               |                 | 70   |                 | MHz                |

| Gain Flatness     | Small Signal Gain Flatness                           | I <sub>S</sub> = 14mA/port, 17.6MHz                                              |                 | 0.3  |                 | dB                 |

|                   |                                                      | I <sub>S</sub> = 14mA/port, 30MHz                                                |                 | 0.9  |                 | dB                 |

| SR                | Slew Rate                                            | V <sub>OUT</sub> = 16V <sub>P-P-DIFF</sub> (20% to 80%)                          | 560             | 1000 |                 | V/µs               |

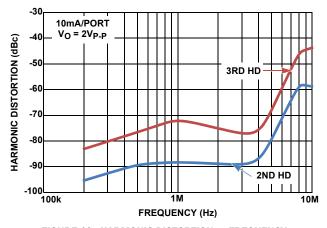

| 200kHz Harmonic   | 2nd Harmonic                                         | 10mA/port, V <sub>OUT</sub> = 10V <sub>P-P-DIFF</sub>                            |                 | -95  |                 | dBc                |

| Distortion        | 3rd Harmonic                                         | 10mA/port, V <sub>OUT</sub> = 10V <sub>P-P-DIFF</sub>                            |                 | -83  |                 | dBc                |

|                   | THD                                                  | 10mA/port, V <sub>OUT</sub> = 10V <sub>P-P-DIFF</sub>                            |                 | -83  |                 | dBc                |

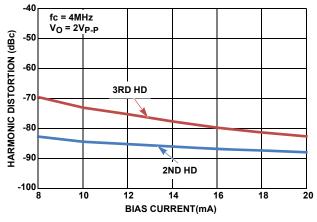

| 4MHz Harmonic     | 2nd Harmonic                                         | 10mA/port, V <sub>OUT</sub> = 10V <sub>P-P-DIFF</sub>                            |                 | -80  |                 | dBc                |

| Distortion        | 3rd Harmonic                                         | 10mA/port, V <sub>OUT</sub> = 10V <sub>P-P-DIFF</sub>                            |                 | -75  |                 | dBc                |

|                   | THD                                                  | 10mA/port, V <sub>OUT</sub> = 10V <sub>P-P-DIFF</sub>                            |                 | -74  |                 | dBc                |

| MBPR              | Average Missing-Band Power Ratio                     | 26kHz to 8MHz, 5kHz Tone Spacing,<br>P <sub>LINE</sub> = 19.5dBm, VDSL2+ 8b, US1 |                 | -64  |                 | dBc                |

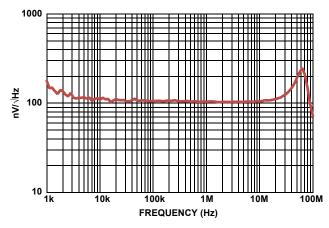

| e <sub>O</sub>    | Output Voltage Noise                                 | f = 1MHz, differential each port                                                 |                 | 110  |                 | nV/√ <del>Hz</del> |

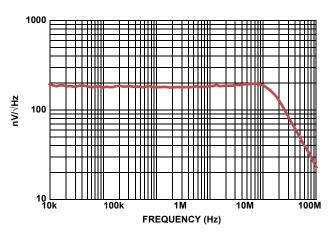

| e <sub>O-CM</sub> | Common Mode Output Noise at each Port Pair           | f = 1MHz                                                                         |                 | 190  |                 | nV/√ <del>Hz</del> |

| CONTROL FEATURI   | ES                                                   |                                                                                  |                 |      |                 |                    |

| V <sub>HIGH</sub> | Input High Voltage                                   | SCLK, SDATA, CS, BOOST inputs                                                    | 2.3             |      |                 | ٧                  |

| V <sub>LOW</sub>  | Input Low Voltage                                    | SCLK, SDATA, CS, BOOST inputs                                                    |                 |      | 0.8             | V                  |

| I <sub>HIGH</sub> | Input High Current for Pull-up Pins CS,<br>BOOST     | V <sub>IN</sub> = 3.3V                                                           | -28             | -23  | -18             | μΑ                 |

| I <sub>HIGH</sub> | Input High Current for Pull-down Pins<br>SCLK, SDATA | V <sub>IN</sub> = 3.3V                                                           | 40              | 50   | 60              | μΑ                 |

intersil FN7941.1 February 26, 2013

## **ISL1561**

**Electrical Specifications**  $V_{SP}$  = +14V,  $R_{L-DIFF}$  = 51 $\Omega$  differential (emulating transformer input load), Refer to Figure 3,  $T_A$  = +25°C. Ports tested separately unless otherwise indicated.(Continued)

| PARAMETER                    | DESCRIPTION                                                                            | CONDITIONS                                                                                  | MIN<br>(Note 6) | TYP  | MAX<br>(Note 6) | UNIT |

|------------------------------|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------|------|-----------------|------|

| I <sub>LOW</sub>             | Input Low Current for Pull-up Pins CS,<br>BOOST                                        | V <sub>IN</sub> = OV                                                                        | -88             | -73  | -58             | μΑ   |

| I <sub>LOW</sub>             | Input Low Current for Pull-down Pins<br>SCLK, SDATA                                    | V <sub>IN</sub> = OV                                                                        | -0.2            | 0    | +0.2            | μΑ   |

| SUPPLY CHARACTE              | ERISTICS                                                                               |                                                                                             | 1               |      | 1               |      |

| V <sub>S</sub>               | Operating Supply Voltage                                                               |                                                                                             | +10             | +14  | +14.7           | ٧    |

| V <sub>CPP</sub>             | Voltage on the CPP Pin                                                                 | BOOST = OV (Class AB)                                                                       |                 | 7    |                 | ٧    |

| V <sub>CPSW</sub>            | Maximum Voltage on the CPSW Pin                                                        | BOOST = OV (Class AB)                                                                       |                 | 14   |                 | ٧    |

| V <sub>CMM</sub>             | Voltage on the CMM Pin                                                                 | BOOST = OV (Class AB)                                                                       |                 | 7    |                 | ٧    |

| V <sub>CMSW</sub>            | Minimum Voltage on the CMSW Pin                                                        | BOOST = OV (Class AB)                                                                       |                 | 0    |                 | ٧    |

| I <sub>SP</sub>              | Positive Supply Current per Port                                                       | All outputs at 0V, BOOST = 0V, SDATA = 8'h7F for Registers 3 and 7                          | 17.5            | 19.5 | 21.5            | mA   |

|                              |                                                                                        | All outputs at 0V, BOOST = 0V, SDATA = 8'h1C for Registers 3 and 7                          | 9.8             | 10.3 | 10.8            | mA   |

|                              |                                                                                        | All outputs at 0V, BOOST = 0V, SDATA = 8'h0F for Registers 3 and 7                          | 6.8             | 7.2  | 7.6             | mA   |

| I <sub>SP</sub> (Power-down) | Supply Current per Port                                                                | All outputs at 0V, BOOST = 0V, SDATA = 8'h80 for Registers 3 and 7                          | 2.0             | 2.5  | 3.0             | mA   |

| OUTPUT CHARACTE              | ERISTICS                                                                               |                                                                                             |                 |      |                 |      |

| V <sub>OUT</sub>             | Loaded Output Swing High (Single-ended to GND)                                         | $R_L = 51\Omega$ , Class AB (see Figure 3)                                                  | 11.9            | 12.4 |                 | V    |

|                              | Loaded Output Swing High (Single-ended to GND)                                         | $R_L = 51\Omega$ , Class AB (see Figure 3)                                                  |                 | 1.6  | 2.1             | V    |

| I <sub>OL</sub>              | Linear Output Current                                                                  | $R_L = 10\Omega$ , f = 100kHz, THD = -60dBc (5 $\Omega$ differential)                       |                 | ±360 |                 | mA   |

| V <sub>OS-DM</sub>           | Differential Output Offset Voltage                                                     | SDATA = 8'h1C                                                                               | -125            | 18   | +125            | m۷   |

| V <sub>OS-CM</sub>           | Common Mode Output Offset Voltage                                                      | SDATA = 8'h1C (Offset from input VCM)                                                       | 6.85            |      | 7.09            | m۷   |

| INPUT CHARACTER              | RISTICS                                                                                |                                                                                             |                 |      |                 |      |

| CMIR                         | Common Mode Input Range at each of the 4 Non-inverting Input Pins                      | Class AB                                                                                    | +4.5            |      | +9.5            | V    |

| CMRR                         | DC Common Mode Rejections for each Port. V <sub>CM</sub> = +4.5V to +9.5V              | V <sub>CM</sub> to Differential Mode Output (Input<br>Referred) I <sub>SP</sub> = 10mA/port |                 | 66   |                 | dB   |

|                              |                                                                                        | V <sub>CM</sub> to Common Mode Output (Output<br>Referred) I <sub>SP</sub> = 10mA/port      |                 | 40   |                 | dB   |

| PSRR                         | DC Power Supply Rejections for each<br>Port to Differential Output (Input<br>Referred) | $+V_S = +7V \text{ to } +14V, \text{ GND} = 0V, I_{SP} = 10\text{mA/port}$                  |                 | 74   |                 | dB   |

|                              | DC Power Supply Rejections for each<br>Port to Common Mode Output (Output<br>Referred) | $+V_S = +7V \text{ to } +14V, \text{ GND} = 0V, I_{SP} = 10\text{mA/port}$                  |                 | 55   |                 | dB   |

| RIN                          | Input Resistance                                                                       | Differential                                                                                | 5.0             | 6.0  | 7.1             | kΩ   |

| DIGITAL                      |                                                                                        |                                                                                             | •               | •    | •               |      |

| f <sub>CLK</sub>             | Clock Frequency                                                                        |                                                                                             |                 | 0.1  | 10              | MHz  |

#### NOTE:

6. Compliance to datasheet limits is assured by one or more methods: production test, characterization and/or design.

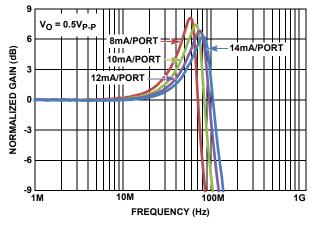

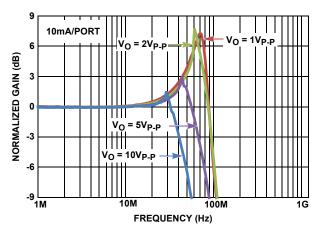

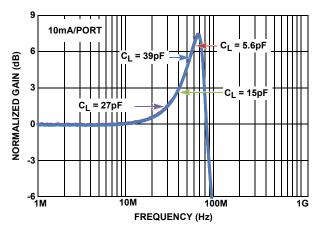

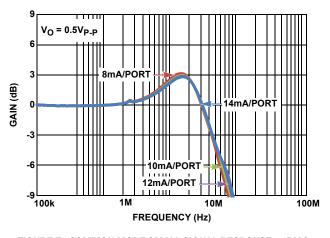

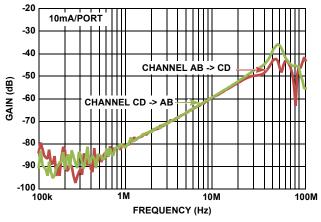

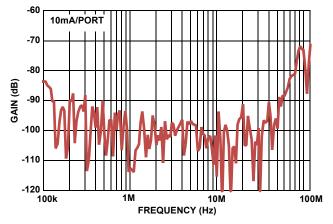

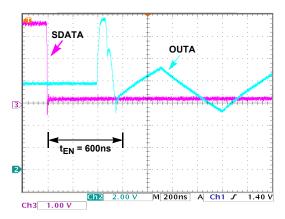

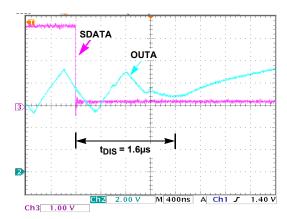

## **Typical Performance Curves**

$\rm V_{CC}$  = +14V, Rb = 5.1 $\Omega$ , Gain at the Load = 11.6V/V (Differential),  $\rm R_{LOAD}$  = 51 $\Omega$ ,

$T_A = +25$ °C, Unless otherwise noted.

FIGURE 4. SMALL SIGNAL FREQUENCY RESPONSE vs BIAS CURRENT

FIGURE 5. LARGE SIGNAL FREQUENCY RESPONSE

FIGURE 6. SMALL SIGNAL FREQUENCY RESPONSE vs  $C_{LOAD}$

FIGURE 7. COMMON MODE SMALL SIGNAL RESPONSE VS BIAS CURRENT

FIGURE 8. POWER CONSUMPTION vs LINE POWER

FIGURE 9. VDSL2+ 8b Avg. MBPR US1 vs LINE POWER

## **Typical Performance Curves** T<sub>A</sub> = +25°C, Unless otherwise noted. (Continued)

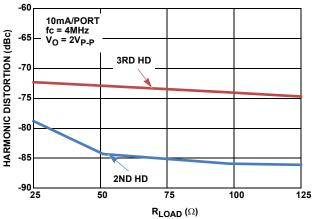

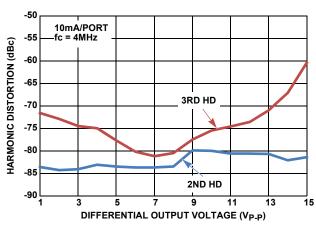

$V_{CC}$  = +14V, Rb = 5.1 $\Omega$ , Gain at the Load = 11.6V/V (Differential),  $R_{LOAD}$  = 51 $\Omega$ ,

FIGURE 10. HARMONIC DISTORTION vs FREQUENCY

FIGURE 11. HARMONIC DISTORTION vs BIAS CURRENT

FIGURE 12. HARMONIC vs R<sub>LOAD</sub>

FIGURE 13. HARMONIC DISTORTION vs OUTPUT AMPLITUDE

FIGURE 14. DIFFERENTIAL OUTPUT VOLTAGE NOISE

FIGURE 15. COMMON MODE OUTPUT VOLTAGE NOISE

## **Typical Performance Curves** T<sub>A</sub> = +25°C, Unless otherwise noted. (Continued)

$V_{CC}$  = +14V, Rb = 5.1 $\Omega$ , Gain at the Load = 11.6V/V (Differential), R<sub>LOAD</sub> = 51 $\Omega$ ,

FIGURE 16. CHANNEL-TO-CHANNEL CROSSTALK

FIGURE 17. OFF-ISOLATION

FIGURE 18. ENABLE RESPONSE

FIGURE 19. DISABLE RESPONSE

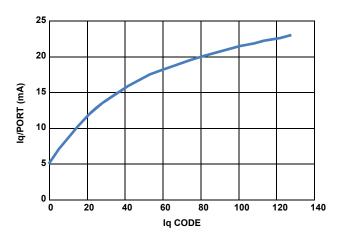

FIGURE 20. QUIESCENT CURRENT PER PORT vs CODES

## **Typical Performance Curves** T<sub>A</sub> = +25°C, Unless otherwise noted. (Continued)

$V_{CC}$  = +14V, Rb = 5.1 $\Omega$ , Gain at the Load = 11.6V/V (Differential), R<sub>LOAD</sub> = 51 $\Omega$ ,

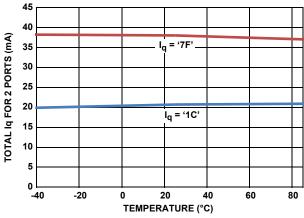

FIGURE 21. QUIESCENT CURRENT vs TEMPERATURE

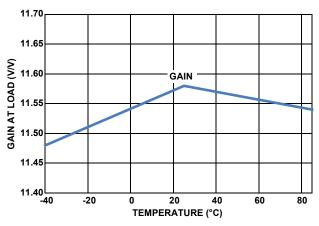

FIGURE 22. GAIN AT LOAD vs TEMPERATURE

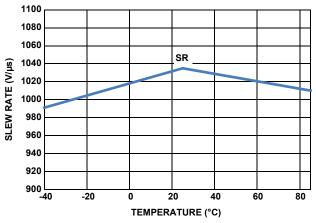

FIGURE 23. SLEW RATE vs TEMPERATURE

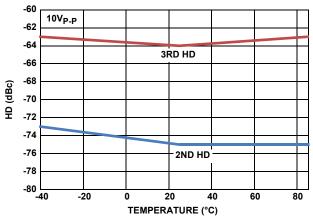

FIGURE 24. 4MHz HARMONIC DISTORTION vs TEMPERATURE

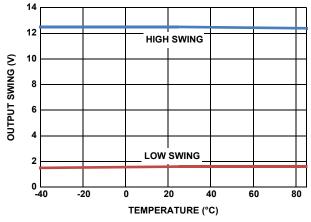

FIGURE 25. OUTPUT SWING vs TEMPERATURE

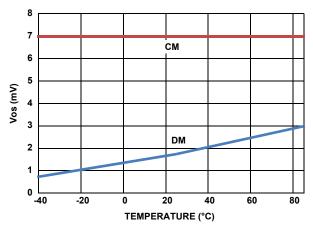

FIGURE 26. OUTPUT OFFSET CM AND DM vs TEMPERATURE

#### **General Description**

The ISL1561 is a class G amplifier designed to reduce power consumption in ADSL2+ and VDSL2 applications compared to class AB. With the high PAR used for xDSL signals, a supply voltage of +14V can be used for the majority of the small amplitude cycles while boosting to a supply voltage of +28V can be used for the few high amplitude cycles.

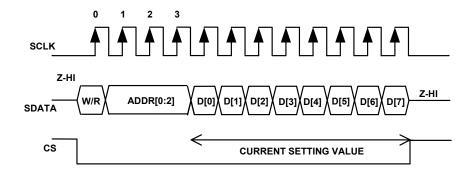

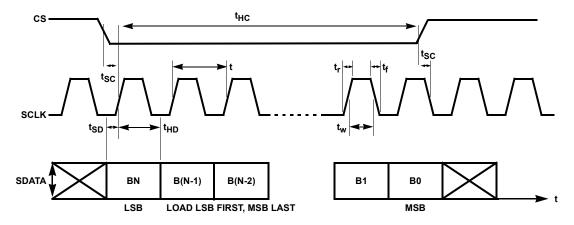

#### **Digital Interface**

A 12-bit serial port interface is used to program ISL1561. The first bit defines the write (1'b1) and read (1'b0) operation to the register. The following 3-bit calls the registers. The last 8-bit programs the registers. Default start-up for ISL1561 is in disable mode with boost and CS pins having internal pull ups and SCLK and SDATA pins having internal pull downs. ISL1561 can only be programmed through the SPI when CS is set low.

## **Register Listing**

| ADDRESS | FUNCTION                                | BIT   | DESCRIPTION                           |

|---------|-----------------------------------------|-------|---------------------------------------|

| 3'h3    | Setting of quiescent current of port AB | [7]   | Boost disable                         |

|         |                                         | [6:0] | Program quiescent current of port AB. |

| 3'h7    | Setting of quiescent current of port CD | [7]   | Boost disable                         |

|         |                                         | [6:0] | Program quiescent current of port CD. |

FIGURE 27. 12 BITS SERIAL ADDRESSING DIAGRAM

FIGURE 28. 12 BITS SERIAL ADDRESSING DIAGRAM

**TABLE 1. SERIAL TIMING DIAGRAM**

| PARAMETER                      | RECOMMENDED OPERATING RANGE | DESCRIPTION           |

|--------------------------------|-----------------------------|-----------------------|

| t                              | ≥100ns                      | Clock Period          |

| t <sub>r</sub> /t <sub>f</sub> | 0.05*t                      | Clock Rise/Clock Fall |

| t <sub>HC</sub>                | ≥7ns                        | Data Hold Time        |

| t <sub>SD</sub>                | ≥10ns                       | Data Setup Time       |

| t <sub>HC</sub>                | ≥2.8ns                      | CS Hold Time          |

| t <sub>SC</sub>                | ≥0.5ns                      | CS Setup Time         |

| t <sub>W</sub>                 | 0.50*t                      | Clock Pulse Width     |

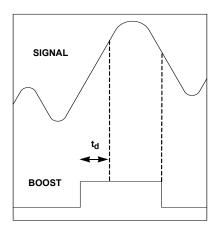

#### **Boost Control**

Table 2 summarizes the logic of register MSB on boost operations followed by Figure 29 with the recommended look ahead timing for the boost signal.

**TABLE 2. REGISTER MSB ON BOOST OPERATION**

| Reg3 8'h[7] | Reg7 8'h[7] | BOOST PIN | BOOST OPERATION |

|-------------|-------------|-----------|-----------------|

| 0           | Х           | 1         | 1               |

| Х           | 0           | 1         | 1               |

| 1           | 1           | X         | 0               |

| Х           | Х           | 0         | 0               |

NOTE: X = do not care

FIGURE 29. SERIAL TIMING DIAGRAM

TABLE 3. EXTERNAL BOOST SIGNAL TIMING PARAMETERS

| PARAMETER      | RECOMMENDED OPERATING RANGE | DESCRIPTION      |

|----------------|-----------------------------|------------------|

| t <sub>d</sub> | 100ns                       | Look ahead boost |

## **Revision History**

The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please go to web to make sure you have the latest revision.

| DATE              | REVISION | CHANGE                                                                                                       |

|-------------------|----------|--------------------------------------------------------------------------------------------------------------|

| January 24, 2013  | FN7941.1 | Changed MIN/MAX specs for "Differential Output Offset Voltage" on page 5 from -75/75mV to -125/125mV.        |

| November 21, 2012 |          | Added resistor values to Figure 3 on page 3. Edited table heading for columns 1 and 2 in Table 2 on page 11. |

| October 5, 2012   | FN7941.0 | Initial Release.                                                                                             |

### **About Intersil**

Intersil Corporation is a leader in the design and manufacture of high-performance analog, mixed-signal and power management semiconductors. The company's products address some of the fastest growing markets within the industrial and infrastructure, personal computing and high-end consumer markets. For more information about Intersil or to find out how to become a member of our winning team, visit our website and career page at <a href="https://www.intersil.com">www.intersil.com</a>.

For a complete listing of Applications, Related Documentation and Related Parts, please see the respective product information page. Also, please check the product information page to ensure that you have the most updated datasheet: <a href="ISL1561">ISL1561</a>

To report errors or suggestions for this datasheet, please go to: www.intersil.com/askourstaff

Reliability reports are available from our website at: http://rel.intersil.com/reports/search.php

For additional products, see www.intersil.com/product\_tree

Intersil products are manufactured, assembled and tested utilizing ISO9000 quality systems as noted in the quality certifications found at www.intersil.com/design/quality

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see <a href="https://www.intersil.com">www.intersil.com</a>

intersil

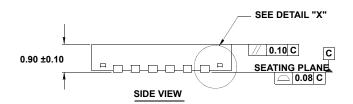

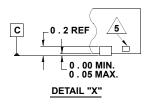

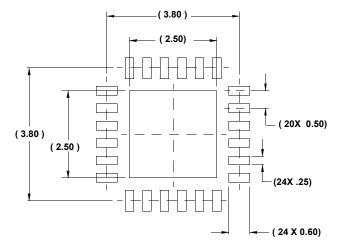

## **Package Outline Drawing**

#### L24.4x4H

24 LEAD QUAD FLAT NO-LEAD PLASTIC PACKAGE Rev 0,09/11

TYPICAL RECOMMENDED LAND PATTERN

#### NOTES:

- Dimensions are in millimeters.

Dimensions in ( ) for Reference Only.

- 2. Dimensioning and tolerancing conform to AMSEY14.5m-1994.

- 3. Unless otherwise specified, tolerance : Decimal  $\pm 0.05$

- 4. Dimension applies to the metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip.

- 5. Tiebar shown (if present) is a non-functional feature.

- The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 identifier may be either a mold or mark feature.

- 7. Compliant to JEDEC MO-220 VGGD-8