# 2/1-Phase PWM Controller with SVID for VR12.5

### General Description

The uP1651Q is a VR12.5 compliant PWM controller that surpports 2/1-phase operation. This device integrates 2 MOSFET gate drivers with embedded bootstrap diode to minimize external component count. To comply with VR12.5 specification, the uP1651Q accurately reports output current and VR temperature.

The uP1651Q provides programmable 2/1 phase operation. uP1651Q integrates 2 bootstrapped drivers that support 12V + 12V driving capability. 2/1 phase operation is enabled by a logic level ISENx output, achieving optimal balance between cost and flexibility.

The uP1651Q supports automatic phase adding/dropping that is activated by PSI command from SVID or H/W PSI setting. The uP1651Q operates in diode emulation mode at extreme light load condition, yielding maximum efficiency over entire load current range.

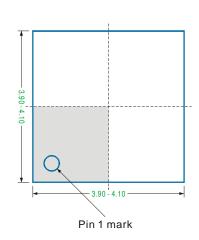

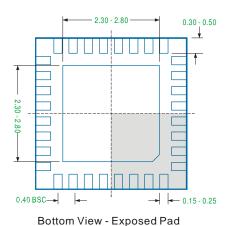

Other features include adjustable soft start, under/over voltage protection, over current protection and thermal shutdown. The uP1651Q is available in WQFN4x4-32L.

## Ordering Information

| Order Number | Package Type | Top Marking |

|--------------|--------------|-------------|

| uP1651QQKI   | WQFN4x4-32L  | uP1651Q     |

#### Note

- (1) Please check the sample/production availability with uPl representatives.

- (2) uPI products are compatible with the current IPC/ JEDEC J-STD-020 requirement. They are halogen-free, RoHS compliant and 100% matte tin (Sn) plating that are suitable for use in SnPb or Pb-free soldering processes.

### **Applications**

Desktop PC Core Power Supplies

### Features

- Intel VR12.5 Compliant

- Output Current and Thermal Reporting

- Programmable ICCMAX,VBOOT

- □ RCOT™ Control Topology

- Easy Setting

- Smooth Mode Transition

- Fast Transient Response

- Selectable 2/1-Phase Operation

- Differential Remote Voltage Sensing

- 2 Embedded 12V MOSFET Gate Drivers with Integrated Bootstrap Diode

- Summed DCR Current Sensing for Load Line Setting

- Lower MOSFET R<sub>DS(ON)</sub> Current Sensing for Current Balance and Channel OCP

- Programmable Auto Phase Reduction per Load Current

- OCP/OVP/UVP/OTP

- Adjustable Soft-Start

- Support Pre-Biased Start Up

- RoHS Compliant and Halogen Free

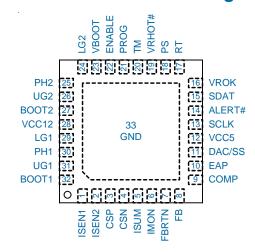

## **Pin Configuration**

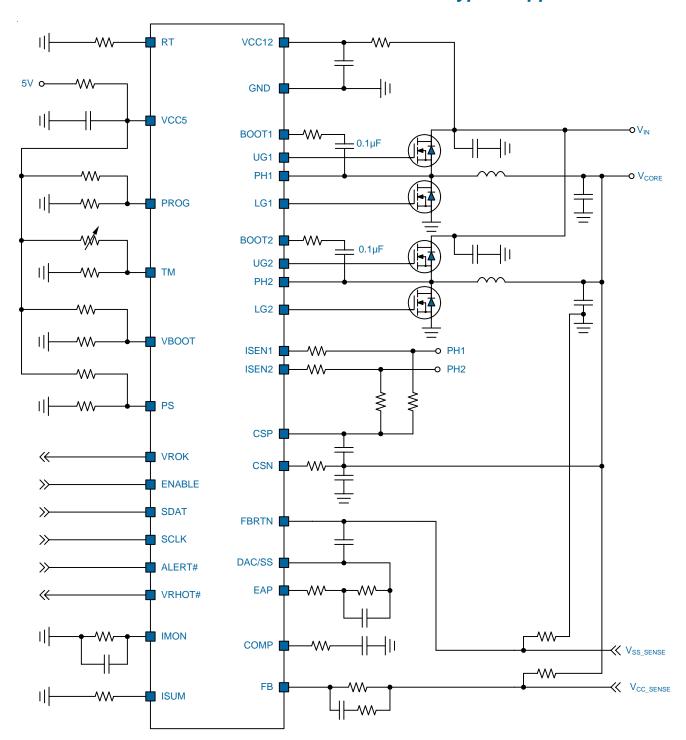

# **Typical Application Circuit**

| for current sensing.    ISEN1   SEN1   for current sensing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | No. | Name   | Pin Function                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

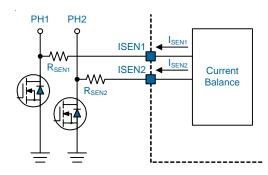

| SENZ   Son Corper Sensing   CSP   Voor   Total Current Sense Positive Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1   | ISEN1  | <b>Current Sensing for Phase 1.</b> Connect a resistor from this pin to phase 1 switching node for current sensing.                                                                                                                                                                                                                                                                                        |

| V <sub>CORE</sub> Output Current Indication. Output current of ISUM pin is proportional to total load current. Connect a resistor between ISUM and GND then the voltage of ISUM is proportional to total load current. When ISUM is equal to 2V, it will thrigger ICCMax Alent# of SVID. The ISUM voltage is also used for over current protection. Avoid add any capacitor to this pin.  Output Current Monitor Pin. The output current of IMON pin is proportional to the total load current. Connect a resistor from this pin to GND. The IMON voltage is decoded by ADC for current reporting. A capacitor may be added to this pin to adjust the response time of current reporting.  FBRTN  V <sub>CORE</sub> Feedback Return. V <sub>CORE</sub> VID DAC and error amplifier reference for remote sensing of the output voltage.  FB  V <sub>CORE</sub> Feedback Pin. Error amplifier inverting input for remote sensing of the V <sub>CORE</sub> output voltage.  COMP  V <sub>CORE</sub> Compensation Output. Error amplifier output and compensation point.  Non-Inverting Input of the Error Amplifier. A resistor between EAP and the DAC/SS sets the load line.  V <sub>CORE</sub> DAC Output. Connect a capacitor from this pin to FBRTN to program the slew rate during soft start and dynamic VID transition.  V <sub>CORE</sub> DAC Output. This pin supplies voltage for logic control circuit.  SVID Clock Pin.  SVID Clock Pin.  V <sub>CORE</sub> Power Good Indication. This pin is an open-drain output that indicates the soft start process is complete and no fault happens.  PWM On Time Setting. Connect a resistor from this pin to GND to set the PWM on time.  Power Saving Mode Setting Input. Connect a resistor voltage divider from VCC5 to GND to set the phase reduction threshold level.  VRHOT# Output. This pin is an open-drain output. When the V <sub>TM</sub> reaches the level that the decoded temperature reaches TEMPMAX (64h), it will trigger VRHOT#. Connect NTC entwork to this pin for sensing VR temperature. UP1631Q uses specific nonlinear A/D converter in thermal reporting. The recommended NTC thermistor is 10K, and the recommended lower dividing resistor is 6kΩ. | 2   | ISEN2  | <b>Current Sensing for Phase 2.</b> Connect a resistor from this pin to phase 2 switching node for current sensing.                                                                                                                                                                                                                                                                                        |

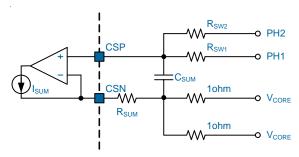

| SUM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3   | CSP    | V <sub>CORE</sub> Total Current Sense Positive Input.                                                                                                                                                                                                                                                                                                                                                      |

| SUM SUM current. Connect a resistor between ISUM and GND then the voltage of ISUM is proportional to total load current. When ISUM is equal to 2V, it will trigger ICCMax Alert# of SVID. The ISUM voltage is also used for over current protection. Avoid add any capacitor to this pin.    Courtent Connect a resistor from this pin to GND. The IMON voltage is decoded by ADC for current reporting. A capacitor may be added to this pin to adjust the response time of current reporting. A capacitor may be added to this pin to adjust the response time of current reporting. A capacitor may be added to this pin to adjust the response time of current reporting.    FBRTN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4   | CSN    | V <sub>CORE</sub> Total Current Sense Negative Input.                                                                                                                                                                                                                                                                                                                                                      |

| 6 IMON current. Connect a resistor from this pin to GND. The IMON voltage is decoded by ADC for current reporting. A capacitor may be added to this pin to adjust the response time of current reporting.  7 FBRTN V <sub>CORE</sub> Feedback Return. V <sub>CORE</sub> VID DAC and error amplifier reference for remote sensing of the output voltage.  8 FB V <sub>CORE</sub> Feedback Pin. Error amplifier inverting input for remote sensing of the V <sub>CORE</sub> output voltage.  9 COMP V <sub>CORE</sub> Compensation Output. Error amplifier output and compensation point.  10 EAP Non-Inverting Input of the Error Amplifier. A resistor between EAP and the DAC/SS sets the load line.  11 DAC/SS V <sub>CORE</sub> DAC Output. Connect a capacitor from this pin to FBRTN to program the slew rate during soft start and dynamic VID transition.  12 VCC5 Supply Input. This pin supplies voltage for logic control circuit.  13 SCLK SVID Clock Pin.  14 ALERT# SVID Alert# Pin.  15 SDAT SVID Data Pin.  16 VROK V <sub>CORE</sub> Power Good Indication. This pin is an open-drain output that indicates the soft start process is complete and no fault happens.  17 RT PWM On Time Setting. Connect a resistor from this pin to GND to set the PWM on time.  18 PS Power Saving Mode Setting Input. Connect a resistor voltage divider from VCC5 to GND to set the phase reduction threshold level.  VRHOT# Output. This pin is an open-drain output. When the V <sub>™</sub> reaches the level that the decoded temperature reaches TEMPMAX (64h), it will trigger VRHOT#. Connect NTC network to this pin for sensing VR temperature. uP1651Q uses specific nonlinear A/D converter in thermal reporting. The recommended NTC thermistor is 10K, and the recommended lower dividing resistor is 6kΩ.                                                                                                                                                                                                                                                                                                                                                                                                       | 5   | ISUM   | <b>V</b> <sub>CORE</sub> <b>Output Current Indication.</b> Output current of ISUM pin is proportional to total load current. Connect a resistor between ISUM and GND then the voltage of ISUM is proportional to total load current. When ISUM is equal to 2V, it will trigger ICCMax Alert# of SVID. The ISUM voltage is also used for over current protection. Avoid add any capacitor to this pin.      |

| FB V <sub>CORE</sub> Feedback Pin. Error amplifier inverting input for remote sensing of the V <sub>CORE</sub> output voltage.  9 COMP V <sub>CORE</sub> Compensation Output. Error amplifier output and compensation point.  10 EAP Non-Inverting Input of the Error Amplifier. A resistor between EAP and the DAC/SS sets the load line.  11 DAC/SS V <sub>CORE</sub> DAC Output. Connect a capacitor from this pin to FBRTN to program the slew rate during soft start and dynamic VID transition.  12 VCC5 Supply Input. This pin supplies voltage for logic control circuit.  13 SCLK SVID Clock Pin.  14 ALERT# SVID Alert# Pin.  15 SDAT SVID Data Pin.  16 VROK V <sub>CORE</sub> Power Good Indication. This pin is an open-drain output that indicates the soft start process is complete and no fault happens.  17 RT PWM On Time Setting. Connect a resistor from this pin to GND to set the PWM on time.  18 PS Power Saving Mode Setting Input. Connect a resistor voltage divider from VCC5 to GND to set the phase reduction threshold level.  VRHOT# Output. This pin is an open-drain output. When the V <sub>TM</sub> reaches the level that the decoded temperature reaches TEMPMAX (64h), it will trigger VRHOT#. Connect NTC network to this pin for sensing VR temperature. uP1651Q uses specific nonlinear A/D converter in thermal reporting. The recommended NTC thermistor is 10K, and the recommended lower dividing resistor is 6kΩ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 6   | IMON   | Output Current Monitor Pin. The output current of IMON pin is proportional to the total load current. Connect a resistor from this pin to GND. The IMON voltage is decoded by ADC for current reporting. A capacitor may be added to this pin to adjust the response time of current reporting.                                                                                                            |

| Voltage.  Voore Compensation Output. Error amplifier output and compensation point.  Non-Inverting Input of the Error Amplifier. A resistor between EAP and the DAC/SS sets the load line.  Voore DAC Output. Connect a capacitor from this pin to FBRTN to program the slew rate during soft start and dynamic VID transition.  VCC5 Supply Input. This pin supplies voltage for logic control circuit.  SVID Clock Pin.  SVID Alert# Pin.  SVID Alert# Pin.  VROK  Voore Power Good Indication. This pin is an open-drain output that indicates the soft start process is complete and no fault happens.  PWM On Time Setting. Connect a resistor from this pin to GND to set the PWM on time.  Power Saving Mode Setting Input. Connect a resistor voltage divider from VCC5 to GND to set the phase reduction threshold level.  VRHOT# Output. This pin is an open-drain output. When the V <sub>TM</sub> reaches the level that the decoded temperature reaches TEMPMAX (64h), it will trigger VRHOT#. Connect NTC network to this pin for sensing VR temperature. uP1651Q uses specific nonlinear A/D converter in thermal reporting. The recommended NTC thermistor is 10K, and the recommended lower dividing resistor is 6kΩ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7   | FBRTN  | $V_{\text{core}}$ Feedback Return. $V_{\text{core}}$ VID DAC and error amplifier reference for remote sensing of the output voltage.                                                                                                                                                                                                                                                                       |

| The load line.  Non-Inverting Input of the Error Amplifier. A resistor between EAP and the DAC/SS sets the load line.  V <sub>CORE</sub> DAC Output. Connect a capacitor from this pin to FBRTN to program the slew rate during soft start and dynamic VID transition.  VCC5 Supply Input. This pin supplies voltage for logic control circuit.  SCLK SVID Clock Pin.  SVID Alert# Pin.  SDAT SVID Data Pin.  VROK V <sub>CORE</sub> Power Good Indication. This pin is an open-drain output that indicates the soft start process is complete and no fault happens.  RT PWM On Time Setting. Connect a resistor from this pin to GND to set the PWM on time.  PS Power Saving Mode Setting Input. Connect a resistor voltage divider from VCC5 to GND to set the phase reduction threshold level.  VRHOT# Output. This pin is an open-drain output. When the V <sub>TM</sub> reaches the level that the decoded temperature reaches TEMPMAX (64h), it will trigger VRHOT#. Connect NTC network to this pin for sensing VR temperature. uP1651Q uses specific nonlinear A/D converter in thermal reporting. The recommended NTC thermistor is 10K, and the recommended lower dividing resistor is 6kΩ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 8   | FB     | $V_{\text{core}}$ Feedback Pin. Error amplifier inverting input for remote sensing of the $V_{\text{core}}$ output voltage.                                                                                                                                                                                                                                                                                |

| The load line.  Non-Inverting Input of the Error Amplifier. A resistor between EAP and the DAC/SS sets the load line.  V <sub>CORE</sub> DAC Output. Connect a capacitor from this pin to FBRTN to program the slew rate during soft start and dynamic VID transition.  VCC5 Supply Input. This pin supplies voltage for logic control circuit.  SCLK SVID Clock Pin.  SVID Alert# Pin.  SDAT SVID Data Pin.  VROK V <sub>CORE</sub> Power Good Indication. This pin is an open-drain output that indicates the soft start process is complete and no fault happens.  RT PWM On Time Setting. Connect a resistor from this pin to GND to set the PWM on time.  PS Power Saving Mode Setting Input. Connect a resistor voltage divider from VCC5 to GND to set the phase reduction threshold level.  VRHOT# Output. This pin is an open-drain output. When the V <sub>TM</sub> reaches the level that the decoded temperature reaches TEMPMAX (64h), it will trigger VRHOT#. Connect NTC network to this pin for sensing VR temperature. uP1651Q uses specific nonlinear A/D converter in thermal reporting. The recommended NTC thermistor is 10K, and the recommended lower dividing resistor is 6kΩ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 9   | COMP   | V <sub>CORE</sub> Compensation Output. Error amplifier output and compensation point.                                                                                                                                                                                                                                                                                                                      |

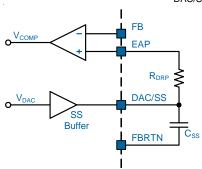

| during soft start and dynamic VID transition.  VCC5  Supply Input. This pin supplies voltage for logic control circuit.  SCLK  SVID Clock Pin.  ALERT#  SVID Alert# Pin.  SDAT  VROK  V <sub>CORE</sub> Power Good Indication. This pin is an open-drain output that indicates the soft start process is complete and no fault happens.  RT  PWM On Time Setting. Connect a resistor from this pin to GND to set the PWM on time.  Power Saving Mode Setting Input. Connect a resistor voltage divider from VCC5 to GND to set the phase reduction threshold level.  VRHOT#  VRHOT# Output. This pin is an open-drain output. When the V <sub>TM</sub> reaches the level that the decoded temperature reaches TEMPMAX (64h), it will trigger VRHOT#. Connect NTC network to this pin for sensing VR temperature. uP1651Q uses specific nonlinear A/D converter in thermal reporting. The recommended NTC thermistor is 10K, and the recommended lower dividing resistor is 6kΩ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 10  | EAP    | Non-Inverting Input of the Error Amplifier. A resistor between EAP and the DAC/SS sets                                                                                                                                                                                                                                                                                                                     |

| SCLK SVID Clock Pin.  SVID Alert# Pin.  SDAT SVID Data Pin.  VROK VCORE Power Good Indication. This pin is an open-drain output that indicates the soft start process is complete and no fault happens.  RT PWM On Time Setting. Connect a resistor from this pin to GND to set the PWM on time.  PS Power Saving Mode Setting Input. Connect a resistor voltage divider from VCC5 to GND to set the phase reduction threshold level.  VRHOT# Output. This pin is an open-drain output. When the VTM reaches the level that the decoded temperature reaches TEMPMAX (64h), it will trigger VRHOT#. Connect NTC network to this pin for sensing VR temperature. uP1651Q uses specific nonlinear A/D converter in thermal reporting. The recommended NTC thermistor is 10K, and the recommended lower dividing resistor is 6kΩ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 11  | DAC/SS | ${f V}_{\tt CORE}$ <b>DAC Output.</b> Connect a capacitor from this pin to FBRTN to program the slew rate during soft start and dynamic VID transition.                                                                                                                                                                                                                                                    |

| ALERT# SVID Alert# Pin.  SDAT SVID Data Pin.  VROK V <sub>CORE</sub> Power Good Indication. This pin is an open-drain output that indicates the soft start process is complete and no fault happens.  RT PWM On Time Setting. Connect a resistor from this pin to GND to set the PWM on time.  PS Power Saving Mode Setting Input. Connect a resistor voltage divider from VCC5 to GND to set the phase reduction threshold level.  VRHOT# Output. This pin is an open-drain output. When the V <sub>TM</sub> reaches the level that the decoded temperature reaches TEMPMAX (64h), it will trigger VRHOT#. Connect NTC network to this pin for sensing VR temperature. uP1651Q uses specific nonlinear A/D converter in thermal reporting. The recommended NTC thermistor is 10K, and the recommended lower dividing resistor is 6kΩ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 12  | VCC5   | Supply Input. This pin supplies voltage for logic control circuit.                                                                                                                                                                                                                                                                                                                                         |

| SDAT  SVID Data Pin.  VROK  V <sub>CORE</sub> Power Good Indication. This pin is an open-drain output that indicates the soft start process is complete and no fault happens.  RT  PWM On Time Setting. Connect a resistor from this pin to GND to set the PWM on time.  Power Saving Mode Setting Input. Connect a resistor voltage divider from VCC5 to GND to set the phase reduction threshold level.  VRHOT# Output. This pin is an open-drain output. When the V <sub>TM</sub> reaches the level that the decoded temperature reaches TEMPMAX (64h), it will trigger VRHOT#. Connect NTC network to this pin for sensing VR temperature. uP1651Q uses specific nonlinear A/D converter in thermal reporting. The recommended NTC thermistor is 10K, and the recommended lower dividing resistor is 6kΩ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 13  | SCLK   | SVID Clock Pin.                                                                                                                                                                                                                                                                                                                                                                                            |

| VROK  VCORE Power Good Indication. This pin is an open-drain output that indicates the soft start process is complete and no fault happens.  RT  PWM On Time Setting. Connect a resistor from this pin to GND to set the PWM on time.  Power Saving Mode Setting Input. Connect a resistor voltage divider from VCC5 to GND to set the phase reduction threshold level.  VRHOT# Output. This pin is an open-drain output. When the V <sub>TM</sub> reaches the level that the decoded temperature reaches TEMPMAX (64h), it will trigger VRHOT#. Connect NTC network to this pin for sensing VR temperature. uP1651Q uses specific nonlinear A/D converter in thermal reporting. The recommended NTC thermistor is 10K, and the recommended lower dividing resistor is 6kΩ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 14  | ALERT# | SVID Alert# Pin.                                                                                                                                                                                                                                                                                                                                                                                           |

| process is complete and no fault happens.  PWM On Time Setting. Connect a resistor from this pin to GND to set the PWM on time.  Power Saving Mode Setting Input. Connect a resistor voltage divider from VCC5 to GND to set the phase reduction threshold level.  VRHOT# Output. This pin is an open-drain output. When the V <sub>TM</sub> reaches the level that the decoded temperature reaches TEMPMAX (64h), it will trigger VRHOT#. Connect NTC network to this pin for sensing VR temperature. uP1651Q uses specific nonlinear A/D converter in thermal reporting. The recommended NTC thermistor is 10K, and the recommended lower dividing resistor is 6kΩ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 15  | SDAT   | SVID Data Pin.                                                                                                                                                                                                                                                                                                                                                                                             |

| Power Saving Mode Setting Input. Connect a resistor voltage divider from VCC5 to GND to set the phase reduction threshold level.  VRHOT# Output. This pin is an open-drain output. When the V <sub>TM</sub> reaches the level that the decoded temperature reaches TEMPMAX (64h), it will trigger VRHOT#. Connect NTC network to this pin for sensing VR temperature. uP1651Q uses specific nonlinear A/D converter in thermal reporting. The recommended NTC thermistor is 10K, and the recommended lower dividing resistor is 6kΩ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 16  | VROK   | <b>V</b> <sub>CORE</sub> <b>Power Good Indication.</b> This pin is an open-drain output that indicates the soft start process is complete and no fault happens.                                                                                                                                                                                                                                            |

| to set the phase reduction threshold level.  VRHOT# Output. This pin is an open-drain output. When the V <sub>TM</sub> reaches the level that the decoded temperature reaches TEMPMAX (64h), it will trigger VRHOT#. Connect NTC network to this pin for sensing VR temperature. uP1651Q uses specific nonlinear A/D converter in thermal reporting. The recommended NTC thermistor is 10K, and the recommended lower dividing resistor is 6kΩ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 17  | RT     | <b>PWM On Time Setting.</b> Connect a resistor from this pin to GND to set the PWM on time.                                                                                                                                                                                                                                                                                                                |

| decoded temperature reaches TEMPMAX (64h), it will trigger VRHOT#. Connect NTC network to this pin for sensing VR temperature. uP1651Q uses specific nonlinear A/D converter in thermal reporting. The recommended NTC thermistor is 10K, and the recommended lower dividing resistor is 6kΩ.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 18  | PS     | <b>Power Saving Mode Setting Input.</b> Connect a resistor voltage divider from VCC5 to GND to set the phase reduction threshold level.                                                                                                                                                                                                                                                                    |

| Thermal Monitoring. Connect NTC network to this pin for V <sub>CORE</sub> thermal monitoring.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 19  | VRHOT# | <b>VRHOT# Output.</b> This pin is an open-drain output. When the $V_{TM}$ reaches the level that the decoded temperature reaches TEMPMAX (64h), it will trigger VRHOT#. Connect NTC network to this pin for sensing VR temperature. uP1651Q uses specific nonlinear A/D converter in thermal reporting. The recommended NTC thermistor is 10K, and the recommended lower dividing resistor is $6k\Omega$ . |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 20  | TM     | <b>Thermal Monitoring.</b> Connect NTC network to this pin for V <sub>CORE</sub> thermal monitoring.                                                                                                                                                                                                                                                                                                       |

| No. | Name     | Pin Function                                                                                                                                                                                                              |

|-----|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21  | PROG     | <b>Function Programming Pin.</b> This pin sets the platform maximum supported current ICCMAX. Connect a resistor voltage divider from VCC5 to GND to set the ICCMAX value.                                                |

| 22  | ENABLE   | <b>Chip Enable.</b> Voltage of this pin higher than 0.7V enables the controller. Lower than 0.3V disables the controller. It is recommended to use this pin to detect whether MOSFET driver power supply is ready.        |

| 23  | VBOOT    | <b>Function Programming Pin.</b> This pin sets two parameters: the initial start up voltage (Vboot) and the over current protection ratio. Connect a resistor voltage divider from VCC5 to GND to set the two parameters. |

| 24  | LG2      | Lower Gate Driver for Phase 2. Connect this pin to the gate of phase 2 lower MOSFET.                                                                                                                                      |

| 25  | PH2      | <b>Phase Pin for Phase 2.</b> This pin is the return path of upper gate driver for phase 2. Connect a capacitor from this pin to BOOT2 to form a bootstrap circuit for upper gate driver of the phase 2.                  |

| 26  | UG2      | Upper Gate Driver for Phase 2. Connect this pin to the gate of phase 2 upper MOSFET.                                                                                                                                      |

| 27  | BOOT2    | <b>BOOT for Phase 2.</b> Connect a capacitor from this pin to PH2 to form a bootstrap circuit for upper gate driver of the phase 2.                                                                                       |

| 28  | VCC12    | Supply Input. This pin supplies current for gate drivers.                                                                                                                                                                 |

| 29  | LG1      | Lower Gate Driver for Phase 1. Connect this pin to the gate of phase 1 lower MOSFET.                                                                                                                                      |

| 30  | PH1      | <b>Phase Pin for Phase 1.</b> This pin is the return path of upper gate driver for phase 1. Connect a capacitor from this pin to BOOT1 to form a bootstrap circuit for upper gate driver of the phase 1.                  |

| 31  | UG1      | Upper Gate Driver for Phase 1. Connect this pin to the gate of phase 1 upper MOSFET.                                                                                                                                      |

| 32  | BOOT1    | <b>BOOT for Phase 1.</b> Connect a capacitor from this pin to PH1 to form a bootstrap circuit for upper gate driver of the phase 1.                                                                                       |

| Ехр | osed Pad | <b>Ground.</b> The exposed pad must be soldered to a large PCB and connected to GND.                                                                                                                                      |

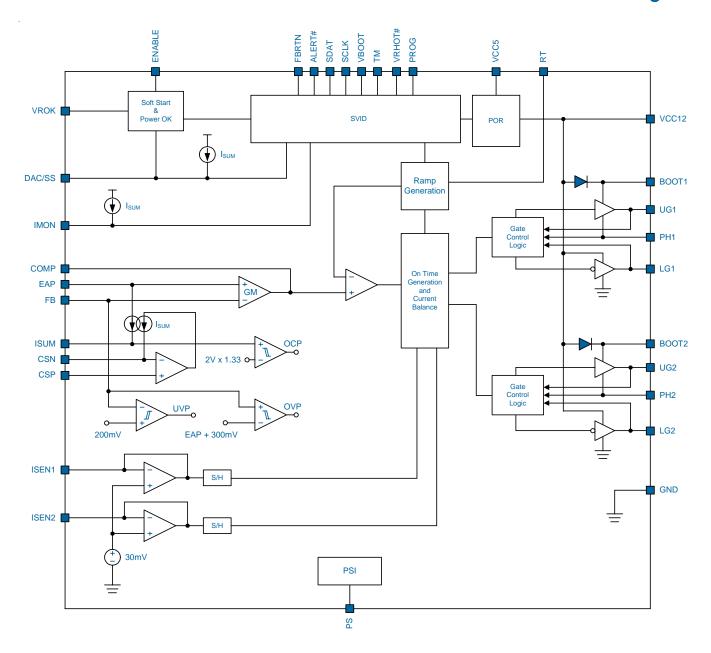

# Functional Block Diagram

The uP1651Q is a VR12.5 compliant PWM controller that supports 2/1-phase operation. This device integrates 2 MOSFET gate drivers with embedded bootstrap to minimize external component count.

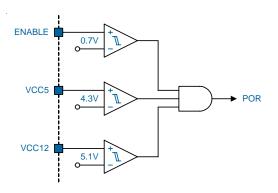

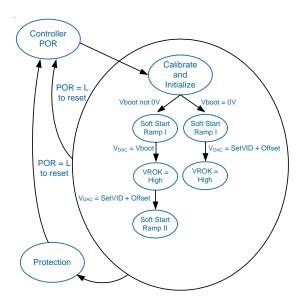

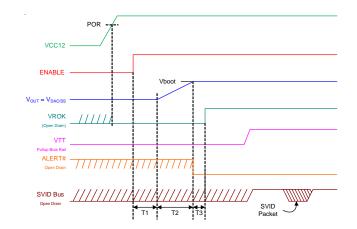

### **Power Ready Detection**

Figure 1 shows the power ready detection of the uP1651Q. The uP1651Q continuously monitors VCC5, ENABLE and VCC12 voltages to ensure all power voltages are ready for normal operation of logic control circuit and companion gate drivers. The VCC5 POR threshold level is VCC5 > 4.3V at the respective rising edge. When VCC5 POR = Low, the uP1651Q sets all gate drivers to turn off both high side and low side MOSFETs.

Figure 1. Circuit for Power Ready Detection

#### **Operation Phase Selection**

The uP1651Q controller supports 2/1-phase operation. The phase number of operation is set and latched by the status of ISEN2 pin at POR rising edge. Normally, the controller operates as a 2-phase PWM controller. Pull ISEN2 to VCC5 for 1-phase operation.

### **Initial Parameters Setting**

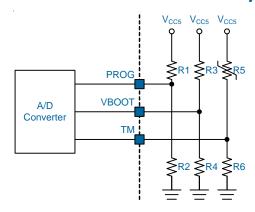

The PROG and VBOOT pins set the parameters required for VR12.5 as shown in Figure 2.

Figure 2. Initial Parameter Setting

The PROG pin is used for ICCMAX setting. The ICCMAX is the maximum supported output current of the VR, this value is stored in SVID register 0x21h.

The ADC scales one-fourth of VCC5 (0V to VCC5/4) into 256 levels for ICCMAX setting (SVID register 0x21h). The ratio of PROG pin voltage to VCC determines the SVID register 0x21h value, which means (VCC5/1024) equals 1A. If the PROG pin voltage is equal to or greater than (VCC5/4), the SVID register 0x21h value will be FFh. When VCC5 = 5V, the LSB = 1.25V/256 = 4.9mV, which means 4.9mV applied to PROG pin equals to 1A setting. For example, if the maximum level of current is 50A, the PROG pin voltage should be  $4.9mV \times 50 = 0.245V$ .

Note that the ICCMAX setting is dependent on VCC5 voltage (it tracks VCC5 voltage). Therefore, make sure to use resistor voltage divider for ICCMAX setting as shown in Table 1.

Table 1. ICCMAX Setting

| V <sub>PROG</sub> = % of VCC | ICCMAX (A) |

|------------------------------|------------|

| 3.92%                        | 40         |

| 4.90%                        | 50         |

| 5.88%                        | 60         |

| 6.86%                        | 70         |

| 7.84%                        | 80         |

| 8.82%                        | 90         |

| 9.80%                        | 100        |

| 10.78%                       | 110        |

The VBOOT pin is used for initial start up voltage Vboot and OCP ratio setting. Connect a resistor voltage divider from VCC5 to GND to set the two parameters. The recommended resistance value is shown in Table 2.

Table 2. Boot Voltage and OCP Ratio Setting

| R3 (kΩ) | R4 (kΩ) | Vboot (V) | OCP Ratio (%) |

|---------|---------|-----------|---------------|

| NC      | 0       | 0         |               |

| 200     | 10      | 1.65      | 133%          |

| 120     | 10      | 1.7       | 133%          |

| 80      | 10      | 1.75      |               |

| 64      | 10      | 1.75      |               |

| 98      | 20      | 1.7       | 1500/         |

| 78      | 20      | 1.65      | 150%          |

| 65      | 20      | 0         |               |

| 55      | 20      | 0         |               |

| 47      | 20      | 1.65      | 171%          |

| 40      | 20      | 1.7       | 171%          |

| 35      | 20      | 1.75      |               |

#### **Thermal Monitor and Reporting**

The TM pin is designed for system thermal monitoring by connecting a NTC thermistor resistive voltage divider from VCC5 to GND. The NTC thermistor should be the upper resistor. The uP1651Q uses specific nonlinear A/D converter for thermal monitor function. The typical ratio of TM pin voltage to VCC5, the corresponding decoded temperature and thermal zone readout value are shown in Table 3.

Note that this A/D conversion is dependent on VCC5 voltage (it tracks VCC5 voltage). Therefore, make sure to use specific NTC thermistor in resistor voltage divider from VCC5 to GND. It is recommended to use Mitsubishi TH11-3H103H NTC as R5 and 6Kohm as R6 for TEMPMAX = 100°C thermal zone reporting.

#### **PWM On Time Setting**

The uP1651Q adopts uPI proprietary RCOT™ (Robust Constant On-Time) topology to have fast transient response and smooth mode transition.

The PWM on time is set by an external resistor connected between RT pin and GND. The PWM on time can be calculated as below.

$$T_{ON} = \frac{VID}{V_{IN}} \times R_{RT} \times 111$$

For example, if  $V_{IN}$  = 12V, VID = 1.7V,  $R_{RT}$  = 30k $\Omega$ , equation gives  $T_{ON}$  = 472ns.

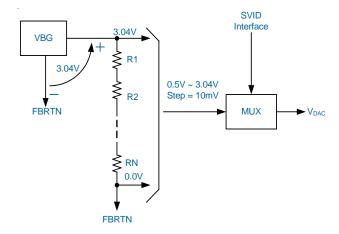

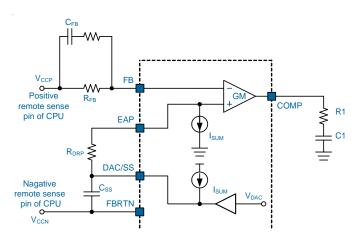

### **V**<sub>DAC</sub> Generator

The uP1651Q builds in precise bandgap reference circuit as shown in Figure 3. The output voltage of bandgap reference is 3.04V with respective to FBRTN. The uP1651Q uses plural resistors to generate precise reference voltage ranging from 0.5V to 3.04V with 10mV increments. All the voltage connect to a multiplexer (MUX). The multiplexer outputs the selected voltage,  $V_{DAC}$ , according to the SVID inputs. Please note that all the voltage values in Figure 3 are referred to FBRTN.

Figure 3.  $V_{DAC}$  Generator Circuit for  $V_{CORE}$ .

The V<sub>DAC</sub> voltage is expressed as:

$$V_{DAC} = VID + Offset$$

where VID and Offset can be programmed by SVID.

Table 4 illustrates the VID voltages according to VID code.

Table 3. Thermal Monitor A/D Conversion

| Temperature (°C) | Reg 0x12h<br>(Temperature<br>Zone) Readout | TM Voltage<br>(% to VCC5) | TM<br>Voltage(V)<br>(VCC5=5V) | Note                               |

|------------------|--------------------------------------------|---------------------------|-------------------------------|------------------------------------|

| 75               | 01                                         | 75.61                     | 3.780                         |                                    |

| 82               | 03                                         | 79.07                     | 3.953                         |                                    |

| 85               | 07                                         | 80.42                     | 4.021                         |                                    |

| 88               | 0F                                         | 81.67                     | 4.083                         |                                    |

| 91               | 1F                                         | 82.84                     | 4.142                         |                                    |

| 94               | 3F                                         | 83.94                     | 4.197                         |                                    |

| 97               | 7F                                         | 84.96                     | 4.248                         | Assert<br>SVID<br>thermal<br>alert |

| 100              | FF                                         | 85.92                     | 4.296                         | Assert<br>VRHOT#                   |

### Table 4. Intel SVID Table

| 0)///D      | \ /                  | 0) (ID      | ١.,                  | 0) (10      |                      | 01/10       |                      | 0)///D      |                      | 0)///D      | \ /                  | 0)///D      | \ /                  |

|-------------|----------------------|-------------|----------------------|-------------|----------------------|-------------|----------------------|-------------|----------------------|-------------|----------------------|-------------|----------------------|

| SVID<br>HEX | V <sub>DAC</sub> (V) |

| 0x00        | 0.00                 | 0x25        | 0.86                 | 0x4A        | 1.23                 | 0x6F        | 1.60                 | 0x94        | 1.97                 | 0xB8        | 2.33                 | 0xDC        | 2.69                 |

| 0x01        | 0.50                 | 0x26        | 0.87                 | 0x4B        | 1.24                 | 0x70        | 1.61                 | 0x95        | 1.98                 | 0xB9        | 2.34                 | 0xDD        | 2.70                 |

| 0x02        | 0.51                 | 0x27        | 0.88                 | 0x4C        | 1.25                 | 0x71        | 1.62                 | 0x96        | 1.99                 | 0xBA        | 2.35                 | 0xDE        | 2.71                 |

| 0x03        | 0.52                 | 0x28        | 0.89                 | 0x4D        | 1.26                 | 0x72        | 1.63                 | 0x97        | 2.00                 | 0xBB        | 2.36                 | 0xDF        | 2.72                 |

| 0x04        | 0.53                 | 0x29        | 0.90                 | 0x4E        | 1.27                 | 0x73        | 1.64                 | 0x98        | 2.01                 | 0xBC        | 2.37                 | 0xE0        | 2.73                 |

| 0x05        | 0.54                 | 0x2A        | 0.91                 | 0x4F        | 1.28                 | 0x74        | 1.65                 | 0x99        | 2.02                 | 0xBD        | 2.38                 | 0xE1        | 2.74                 |

| 0x06        | 0.55                 | 0x2B        | 0.92                 | 0x50        | 1.29                 | 0x75        | 1.66                 | 0x9A        | 2.03                 | 0xBE        | 2.39                 | 0xE2        | 2.75                 |

| 0x07        | 0.56                 | 0x2C        | 0.93                 | 0x51        | 1.30                 | 0x76        | 1.67                 | 0x9B        | 2.04                 | 0xBF        | 2.40                 | 0xE3        | 2.76                 |

| 0x08        | 0.57                 | 0x2D        | 0.94                 | 0x52        | 1.31                 | 0x77        | 1.68                 | 0x9C        | 2.05                 | 0xC0        | 2.41                 | 0xE4        | 2.77                 |

| 0x09        | 0.58                 | 0x2E        | 0.95                 | 0x53        | 1.32                 | 0x78        | 1.69                 | 0x9D        | 2.06                 | 0xC1        | 2.42                 | 0xE5        | 2.78                 |

| 0x0A        | 0.59                 | 0x2F        | 0.96                 | 0x54        | 1.33                 | 0x79        | 1.70                 | 0x9E        | 2.07                 | 0xC2        | 2.43                 | 0xE6        | 2.79                 |

| 0x0B        | 0.60                 | 0x30        | 0.97                 | 0x55        | 1.34                 | 0x7A        | 1.71                 | 0x9F        | 2.08                 | 0xC3        | 2.44                 | 0xE7        | 2.80                 |

| 0x0C        | 0.61                 | 0x31        | 0.98                 | 0x56        | 1.35                 | 0x7B        | 1.72                 | 0xA0        | 2.09                 | 0xC4        | 2.45                 | 0xE8        | 2.81                 |

| 0x0D        | 0.62                 | 0x32        | 0.99                 | 0x57        | 1.36                 | 0x7C        | 1.73                 | 0xA1        | 2.10                 | 0xC5        | 2.46                 | 0xE9        | 2.82                 |

| 0x0E        | 0.63                 | 0x33        | 1.00                 | 0x58        | 1.37                 | 0x7D        | 1.74                 | 0xA2        | 2.11                 | 0xC6        | 2.47                 | 0xEA        | 2.83                 |

| 0x0F        | 0.64                 | 0x34        | 1.01                 | 0x59        | 1.38                 | 0x7E        | 1.75                 | 0xA3        | 2.12                 | 0xC7        | 2.48                 | 0xEB        | 2.84                 |

| 0x10        | 0.65                 | 0x35        | 1.02                 | 0x5A        | 1.39                 | 0x7F        | 1.76                 | 0xA4        | 2.13                 | 0xC8        | 2.49                 | 0xEC        | 2.85                 |

| 0x11        | 0.66                 | 0x36        | 1.03                 | 0x5B        | 1.40                 | 0x80        | 1.77                 | 0xA5        | 2.14                 | 0xC9        | 2.50                 | 0xED        | 2.86                 |

| 0x12        | 0.67                 | 0x37        | 1.04                 | 0x5C        | 1.41                 | 0x81        | 1.78                 | 0xA6        | 2.15                 | 0xCA        | 2.51                 | 0xEE        | 2.87                 |

| 0x13        | 0.68                 | 0x38        | 1.05                 | 0x5D        | 1.42                 | 0x82        | 1.79                 | 0xA7        | 2.16                 | 0xCB        | 2.52                 | 0xEF        | 2.88                 |

| 0x14        | 0.69                 | 0x39        | 1.06                 | 0x5E        | 1.43                 | 0x83        | 1.80                 | 0xA8        | 2.17                 | 0xCC        | 2.53                 | 0xF0        | 2.89                 |

| 0x15        | 0.70                 | 0x3A        | 1.07                 | 0x5F        | 1.44                 | 0x84        | 1.81                 | 0xA9        | 2.18                 | 0xCD        | 2.54                 | 0xF1        | 2.90                 |

| 0x16        | 0.71                 | 0x3B        | 1.08                 | 0x60        | 1.45                 | 0x85        | 1.82                 | 0xAA        | 2.19                 | 0xCE        | 2.55                 | 0xF2        | 2.91                 |

| 0x17        | 0.72                 | 0x3C        | 1.09                 | 0x61        | 1.46                 | 0x86        | 1.83                 | 0xAB        | 2.20                 | 0xCF        | 2.56                 | 0xF3        | 2.92                 |

| 0x18        | 0.73                 | 0x3D        | 1.10                 | 0x62        | 1.47                 | 0x87        | 1.84                 | 0xAC        | 2.21                 | 0xD0        | 2.57                 | 0xF4        | 2.93                 |

| 0x19        | 0.74                 | 0x3E        | 1.11                 | 0x63        | 1.48                 | 0x88        | 1.85                 | 0xAD        | 2.22                 | 0xD1        | 2.58                 | 0xF5        | 2.94                 |

| 0x1A        | 0.75                 | 0x3F        | 1.12                 | 0x64        | 1.49                 | 0x89        | 1.86                 | 0xAE        | 2.23                 | 0xD2        | 2.59                 | 0xF6        | 2.95                 |

| 0x1B        | 0.76                 | 0x40        | 1.13                 | 0x65        | 1.50                 | A8x0        | 1.87                 | 0xAF        | 2.24                 | 0xD3        | 2.60                 | 0xF7        | 2.96                 |

| 0x1C        | 0.77                 | 0x41        | 1.14                 | 0x66        | 1.51                 | 0x8B        | 1.88                 | 0xB0        | 2.25                 | 0xD4        | 2.61                 | 0xF8        | 2.97                 |

| 0x1D        | 0.78                 | 0x42        | 1.15                 | 0x67        | 1.52                 | 0x8C        | 1.89                 | 0xB1        | 2.26                 | 0xD5        | 2.62                 | 0xF9        | 2.98                 |

| 0x1E        | 0.79                 | 0x43        | 1.16                 | 0x68        | 1.53                 | 0x8D        | 1.90                 | 0xB2        | 2.27                 | 0xD6        | 2.63                 | 0xFA        | 2.99                 |

| 0x1F        | 0.80                 | 0x44        | 1.17                 | 0x69        | 1.54                 | 0x8E        | 1.91                 | 0xB3        | 2.28                 | 0xD7        | 2.64                 | 0xFB        | 3.00                 |

| 0x20        | 0.81                 | 0x45        | 1.18                 | 0x6A        | 1.55                 | 0x8F        | 1.92                 | 0xB4        | 2.29                 | 0xD8        | 2.65                 | 0xFC        | 3.01                 |

| 0x21        | 0.82                 | 0x46        | 1.19                 | 0x6B        | 1.56                 | 0x90        | 1.93                 | 0xB5        | 2.30                 | 0xD9        | 2.66                 | 0xFD        | 3.02                 |

| 0x22        | 0.83                 | 0x47        | 1.20                 | 0x6C        | 1.57                 | 0x91        | 1.94                 | 0xB6        | 2.31                 | 0xDA        | 2.67                 | 0xFE        | 3.03                 |