# 2.5V 10/100-TX 8-Port Repeater/7+1 Uplink Port with Integrated Bridge

#### **GENERAL DESCRIPTION**

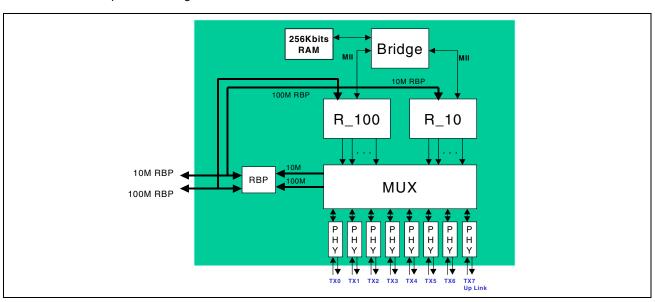

The AC208 is an unmanaged eight-port 10/100 Mbps repeater with an integrated bridge. The AC208 provides a low-cost and integrated solution for unmanaged repeater applications.

The AC208 is a Class II Repeater. In addition, the eighth port supports 10/100 TX interface for uplink function.

The AC208 provides 10/100 Mbps auto-negotiation and parallel detection for all ports. In addition, the option to configure each transceiver port via the EEPROM interface is available. The AC208 provides two internal repeater state machines, one operating at 10 Mbps and the other at 100 Mbps. Once the technology is set, the device automatically connects each port to the appropriate repeater segment.

The AC208 provides two back-planes for expansion, one operates at 10 Mbps and the other operates at 100 Mbps. Up to 32 ports can logically be connected into one repeater using back-plane buses.

The AC208 integrates repeater and bridge technologies with store-and-forward mechanisms.

#### **FEATURES**

- Low-power (less than 1A total current consumption when used with 1.25:1 transformer) eight-port 10/100 Mbps repeater with built-in bridge function.

- MDC/MDIO for control/status of transceiver components.

- Eight integrated 10/100 Mbps IEEE 802.3u compliant transceivers.

- IEEE 802.3u-compliant auto-negotiation.

#### **FEATURES**

- Fully integrated adaptive equalizer provides phase/ amplitude compensation for various cable lengths up to 30 dB at 100 MHz.

- Patent-pending DC restoration technique reduces offset/ baseline wander.

- Unique scrambler seed for all ports for better EMI.

- · Cascadable backplanes compatible with AC206.

- Non-blocking 10/100M bridge with MAC and bridge. One segment of a bridge is fixed to 100 Mbps, while the other segment can be configured for 10 or 100 Mbps.

- Bridge functions include:

- Embedded 32 KB of memory for address table and packet buffer.

- Local MAC address filtering.

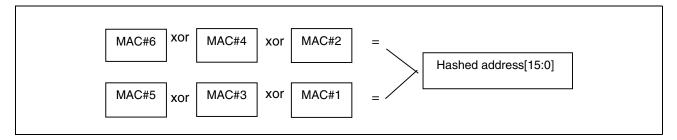

- XOR hashing scheme.

- Short routing decision time.

- Forwarding schemes: store-and-forward.

- Address table up to 1K entries.

- Programmable LED display for activity, link, speed, partition, utilization, and collision rate.

- · Advanced power management includes:

- Each transceiver port can be turned off independently.

- Standby mode, which reduces power when the port is not connected.

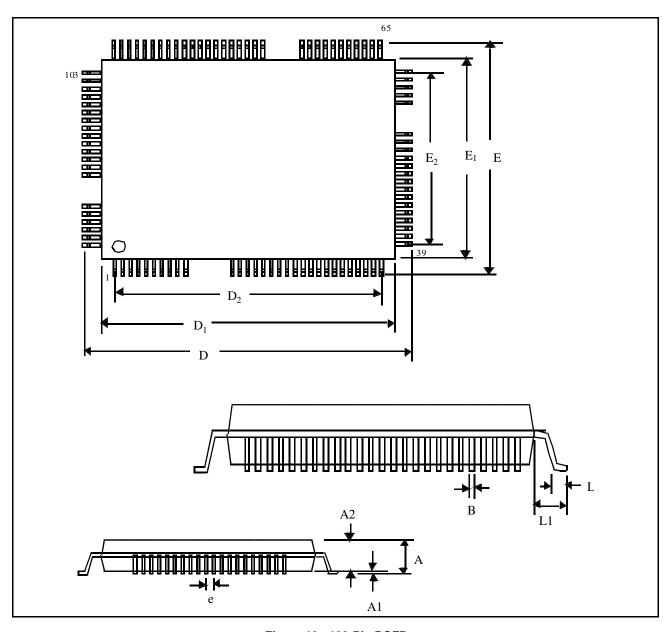

- Low-power 2.5V 0.25 µm CMOS implementation with 128-pin QFP package.

- Input tolerance to 3.3V.

Figure 1: Functional Block Diagram

# **REVISION HISTORY**

| Revision             | Date     | Change Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AC208-DS04-<br>405-R | 07/08/02 | Incorporate MDC/MDIO changes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| AC208-DS03-R         | 06/07/02 | General technical revision.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| AC208-DS02-R         | 06/20/01 | Updated the following tables:  • "LED Connections"  • "Power and Ground"  • "Register Set"  • "Bridge Control Register"  • "BT Control Register"  • "LED Effect with Partition/Isolation Event"  • "EEPROM"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| AC208-DS01-R         | 02/08/01 | <ul> <li>Updated "Scrambler" in the "Functional Description" section to: When the BT Control register 23.11 is set to 1 the data scrambling function is disabled, the 5-bit data stream is clocked directly to the device's PMA sublayer.</li> <li>Added pin #114 to DGND in the "Power and Ground" table.</li> <li>Added pins # 28, 29, 30, 31, 33, 34, 35, 38 to the "No Connects" table.</li> <li>Updated the "Electrical Characteristics" section (replaced the Digital Input Voltage -0.5V to Vcc with -0.5V to 3.3V)</li> <li>Updated the "Digital Timing Characteristics" section</li> <li>Various text changes throughout the whole document.</li> <li>Added the "Mechanical Information" section, outlining the packaging specifications.</li> <li>Updated "LED Timing."</li> </ul> |

| AC208-DS00-R         | 10/9/00  | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

Altima Communications, Inc.

A Broadcom Company

Broadcom Corporation

P.O. Box 57013

16215 Alton Parkway

Irvine, CA 92619-7013

© 2002 by Altima Communications, Inc.

All Rights Reserved Printed in the U.S.A.

Broadcom<sup>®</sup> and the pulse logo<sup>®</sup> are trademarks of Broadcom Corporation and/or its subsidiaries in the United States and certain other countries. All other trademarks are the property of their respective owners.

This data sheet (including, without limitation, the Broadcom component(s) identified herein) is not designed, intended, or certified for use in any military, nuclear, medical, mass transportation, aviation, navigations, pollution control, hazardous substances management, or other high risk application. BROADCOM PROVIDES THIS DATA SHEET "AS-IS", WITHOUT WARRANTY OF ANY KIND. BROADCOM DISCLAIMS ALL WARRANTIES, EXPRESSED AND IMPLIED, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT.

# **TABLE OF CONTENTS**

| Se | ction 1: Functional Description                     |

|----|-----------------------------------------------------|

|    | Functional Description                              |

|    | Clocks, Reset, and Power Management Functions       |

|    | Media Independent Interface                         |

|    | Scrambler                                           |

|    | Parallel to Serial and NRZ—NRZI to MLT-3 Conversion |

|    | PLL Clock Synthesizer                               |

|    | Receive Function                                    |

|    | Adaptive Equalizer                                  |

|    | Link Monitor                                        |

|    | Baseline Wander Compensation                        |

|    | Clock/Data Recovery                                 |

|    | Decoder/Descrambler                                 |

|    | Auto-Negotiation and Miscellaneous Functions        |

|    | Parallel Detection                                  |

|    | Carrier Sense/RXDV for MII Port Only                |

|    | Cable Length Monitor                                |

|    | Media Independent Interface                         |

|    | Forwarding Scheme                                   |

|    | Address Recognition                                 |

|    | Reset and Restart                                   |

|    | Media Access Control                                |

|    | Hardware Configuration                              |

|    | Software Configuration                              |

|    | LEDs                                                |

|    | Address Table                                       |

|    | Routing Decision1                                   |

|    | Learning Process                                    |

|    | Aging Time1                                         |

|    | Forwarding Scheme1                                  |

|    | Bridge Buffer Management and Queues1                |

| Section 2: Pins                                     | 12 |

|-----------------------------------------------------|----|

| Pin Descriptions                                    | 12 |

| Section 3: Register Descriptions                    | 18 |

| Register Description                                | 18 |

| Bridge Configuration Register                       | 22 |

| PHY Configuration Register                          | 23 |

| PHY Identifier 2 Register                           | 25 |

| Auto-Negotiation Advertisement Register             | 25 |

| Auto-Negotiation Expansion Register                 | 26 |

| Cable Length Register                               | 30 |

| Power Management Register                           | 31 |

| LED Effect with Partition/Isolation Event           | 33 |

| LED Effect with Link Event                          | 33 |

| LED Effect with Auto-Negotiating Event              | 34 |

| LED Register Control Mode                           | 35 |

| LED Display Matrix                                  | 38 |

| System Considerations                               | 38 |

| Section 4: Electrical Characteristics               | 39 |

| Absolute Maximum Ratings                            | 39 |

| Operating Range                                     | 39 |

| REFCLK Pins                                         | 40 |

| I/O Characteristics—LED Pins                        | 40 |

| 10BASE-T Transceiver Characteristics                | 41 |

| Section 5: Digital Timing Characteristics           | 42 |

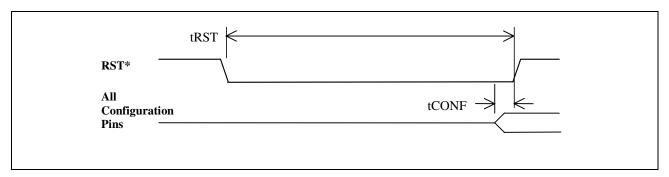

| Power on Reset                                      | 42 |

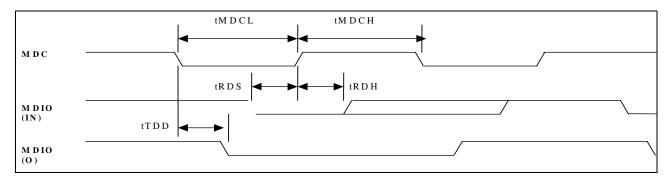

| PHY MDC/MDIO Interface                              | 43 |

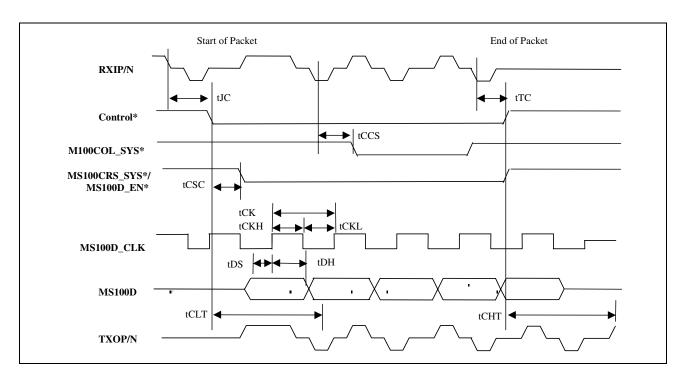

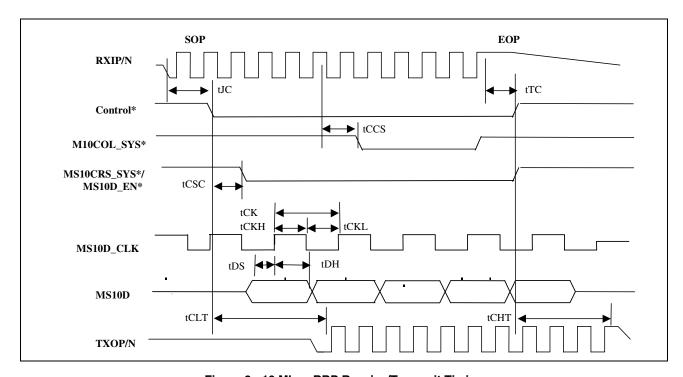

| 100 MBPS Repeater BackPlane Receive/Transmit Timing | 44 |

| 10 MBPS Repeater BackPlane Receive/Transmit Timing  | 45 |

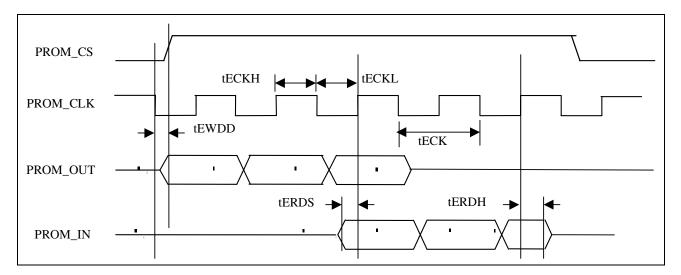

| EEPROM Interface Timing                             | 46 |

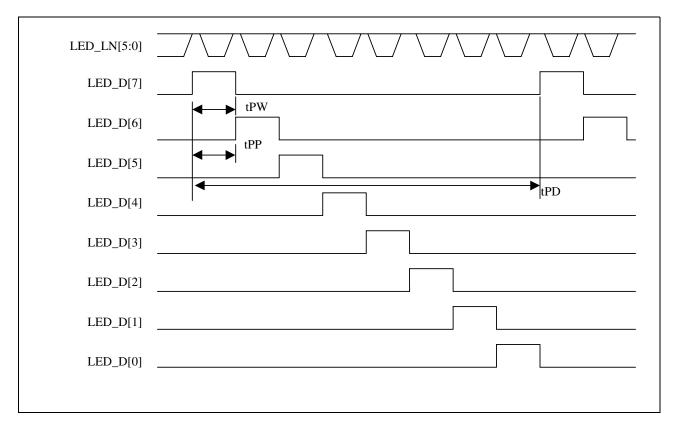

| LED Timing                                          | 47 |

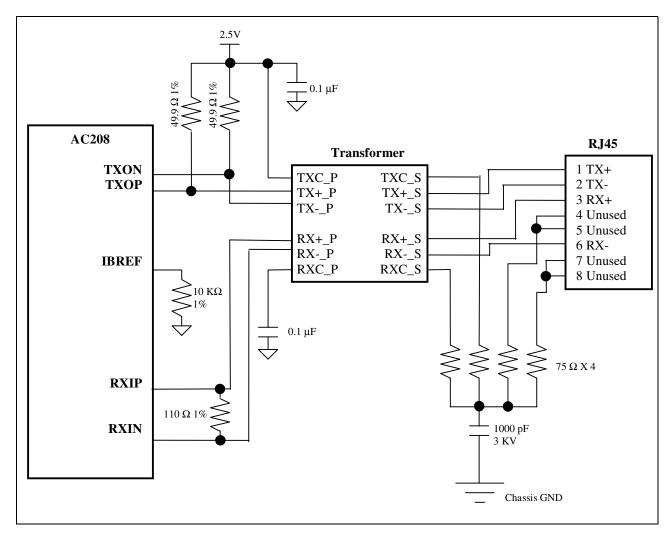

| TX Application Termination                          | 48 |

| Preliminary Data Sheet            | AC208 |

|-----------------------------------|-------|

| 07/08/02                          |       |

| Section 6: Mechanical Information | 49    |

| Section 7: Ordering Information   | 50    |

# **LIST OF TABLES**

| Table 1:  | LED Connections                                 | 8  |

|-----------|-------------------------------------------------|----|

| Table 2:  | Content of Address Lookup Table                 | 9  |

| Table 3:  | Embedded Memory Structure                       | 11 |

| Table 4:  | Media Dependent Interface Pins (TX)             | 12 |

| Table 5:  | EEPROM Interface                                | 13 |

| Table 6:  | MDC/MDIO Interface                              | 13 |

| Table 7:  | 100 Mbps Internal Repeater                      | 14 |

| Table 8:  | 10 Mbps Internal Repeater Bus                   | 15 |

| Table 9:  | LED Pins                                        | 16 |

| Table 10: | Configuration and Setup                         | 17 |

| Table 11: | Clock Reset                                     | 17 |

| Table 12: | Power and Ground                                | 17 |

| Table 13: | No Connects                                     | 17 |

| Table 14: | Register Set                                    | 18 |

| Table 15: | PHY Port Status Register                        | 20 |

| Table 16: | PHY Port Status                                 | 20 |

| Table 17: | Initial Device Configuration Register           | 21 |

| Table 18: | Bridge Configuration Register                   | 22 |

| Table 19: | PHY Configuration Register 0                    | 23 |

| Table 20: | PHY Status Register 1                           | 24 |

| Table 21: | PHY Identifier 1 Register                       | 25 |

| Table 22: | PHY Identifier 2 Register                       | 25 |

| Table 23: | Auto-Negotiation Advertisement Register         | 25 |

| Table 24: | Auto-Negotiation Link Partner Ability Register  | 26 |

| Table 25: | Register 6: Auto-Negotiation Expansion Register | 26 |

| Table 26: | Auto-Negotiation Next Page Transmit Register    | 27 |

| Table 27: | PHY 10BASE-T Configuration Register             | 28 |

| Table 28: | PHY Interrupt Control/Status Register           | 29 |

| Table 29: | Diagnostic Register                             | 30 |

| Table 30: | Cable Length Register                           | 30 |

| Table 31: | Receive Error Count                             | 31 |

| Table 32: | Power Management Register                       | 31 |

# **Preliminary Data Sheet**

# **AC208**

# 07/08/02

| Transceiver Mode Register                           | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LED Effect with Partition/Isolation Event           | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| LED Effect with Link Event                          | 33                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| LED Effect with Activity (CRS) Event                | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| LED Effect with Auto-Negotiating Event              | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| LED Effect with Speed100 Event                      | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| LED Register Control Mode                           | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| EEPROM                                              | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4B/5B Code-Group Table                              | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Total Power Consumption                             | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| TTL I/O Characteristics                             | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| REFCLK Pins                                         | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| I/O Characteristics—LED Pins                        | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 100BASE-TX Transceiver Characteristics              | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 10BASE-T Transceiver Characteristics                | 41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Power on Reset                                      | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PHY MDC/MDIO Interface                              | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 100 Mbps Repeater BackPlane Receive/Transmit Timing | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 10 Mbps Repeater BackPlane Receive/Transmit Timing  | 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| EEPROM Interface Timing                             | 46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| LED Timing                                          | 47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Package Dimensions for the AC208                    | 49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Ordering Information                                | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                     | LED Effect with Partition/Isolation Event  LED Effect with Link Event  LED Effect with Activity (CRS) Event  LED Effect with Auto-Negotiating Event  LED Effect with Speed100 Event  LED Register Control Mode  EEPROM  4B/5B Code-Group Table  Total Power Consumption  TTL I/O Characteristics  REFCLK Pins  I/O Characteristics—LED Pins  100BASE-TX Transceiver Characteristics  10BASE-T Transceiver Characteristics  Power on Reset  PHY MDC/MDIO Interface  100 Mbps Repeater BackPlane Receive/Transmit Timing  10 Mbps Repeater BackPlane Receive/Transmit Timing  EEPROM Interface Timing  LED Timing  Package Dimensions for the AC208 |

# **LIST OF FIGURES**

| Figure 1:  | Functional Block Diagram             | i    |

|------------|--------------------------------------|------|

| Figure 2:  | Exclusive or Hashing Algorithm       | .10  |

| Figure 3:  | Address Learning and Recognition     | .10  |

| Figure 4:  | Basic Memory Management Concept      | . 11 |

| Figure 5:  | LED Display Matrix                   | .38  |

| Figure 6:  | Power on Reset                       | .42  |

| Figure 7:  | PHY MDC/MDIO Interface               | .43  |

| Figure 8:  | 100 Mbps RBP Receive/Transmit Timing | .44  |

| Figure 9:  | 10 Mbps RBP Receive/Transmit Timing  | .45  |

| Figure 10: | EEPROM Interface Timing              | .46  |

| Figure 11: | LED Timing                           | .47  |

| Figure 12: | Application Termination              | .48  |

| Figure 13: | 128-Pin POEP                         | 49   |

# **Section 1: Functional Description**

### **FUNCTIONAL DESCRIPTION**

The AC208 is an unmanaged 10/100 Mbps repeater with integrated bridge functions. The device provides eight 10/100BASE-TX twisted pair interface ports. The AC208 also includes a built-in two-segment bridge for 10/100 Mbps connection. The AC208 provides the highest integration chip solution for dual speed hub systems. The result is ultra low power consumption that consumes less than 1A maximum when all ports are running 100BASE-TX full-speed. The built-in function powers down when not used (no cable detected). This reduces power consumption and improves long-term reliability.

# CLOCKS, RESET, AND POWER MANAGEMENT FUNCTIONS

The AC208 requires a single 25-MHz clock signal at the CLK input pin. An internal PLL generates all of the clock frequencies needed by the device from the single clock input.

The AC208 can be reset in two ways:

- During initial power on.

- Hardware reset: A logic low signal of 10 μs pulse width applies to RST pin.

During reset, all mode pins latch in, the internal address table is initialized, and the internal state machine is reset to known states. At the completion of the reset sequence, all ports are enabled for frame reception and transmission.

The AC208 offers the following power management:

- Power down mode: This can be achieved by writing to register 0.11 plus port based address.

Example: Port 1 has a based address of Hex 00. During power down, the device is able to respond through the MDC/MDIO interface.

- Energy detect mode: The device powers down all of the unused circuitry when the cable is not installed. The Energy

Detect (ED) circuit stays on to monitor incoming signals from the media. The MDC/MDIO interface is turned on in

response to any access transaction. The transmit circuit sends out a link pulse with minimum power consumption. If a

valid signal is received from the media, the device is powered up and resumes normal transmit/receive operation.

# TRANSCEIVER AND TRANSMIT FUNCTION

In 100BASE-TX mode, the Transceiver transmits MLT-3 signal to the cable via isolation transformer. MLT-3 data is a three level signal data. This data is scrambled when transmitted to the media. The MLT-3 data is synchronous to the 25-MHz clock.

In 10BASE-T mode, Manchester code is generated by the 10BASE-T core logic, which synthesizes through the output waveshaping driver. This helps reduce any EMI emission, which eliminates the need for an external filter.

### MEDIA INDEPENDENT INTERFACE

The Media Independent Interface (MII) is for direct connection of an external device to the repeater. The transmit data on the MII interface is 4-bit nibbles at 25/2.5 MHz rate. This MII interface is connected to the repeater via the MII TXD lines. The external device asserts TX\_EN during transmission, or forces an error in the encoded data using TX\_ER.

### **SCRAMBLER**

In 100BASE-TX mode, the internal 5-bit transmit data stream is scrambled as defined by the TP-PMD Stream Cipher function in order to reduce radiated emissions on the twisted pair cable. The scrambler encodes a plain text NRZ bit stream using a key stream periodic sequence of 2047 bits generated by the recursive linear function:

$$X [n] = X [n-11] + X [n-9] (modulo 2)$$

The scrambler reduces peak emissions by randomly spreading the signal energy over the transmit frequency range, thus eliminating peaks at a single frequency. EMI emission can be further reduced by assigning a unique scrambled seed to each port. When the BASE-T Control register 23.11 is set to 1 the data scrambling function is disabled, the 5-bit data stream is clocked directly to the device's PMA sublayer.

### PARALLEL TO SERIAL AND NRZ—NRZI TO MLT-3 CONVERSION

The internal 5-bit NRZ data is clocked into transceiver's shift register with a 25 MHz clock, and clocked out with a 125 MHz clock to convert it into a serial bit stream. Both clocks are generated by an on-chip clock synthesizer, and they are in sync to each other. The serialized data is further converted from NRZ to NRZI format, which produces a transition on every logic 1 and no transition on logic 0. To further reduce EMI emission, the NRZI data is converted to MLT-3 signal. The effect offers a 3 dB to 6 dB reduction in EMI emissions over an un-converted NRZI signals, thus increases the output signals' margin of operating within the FCC Class B limit.

When there is a transition occurring in NRZI data, there is a corresponding transition for MLT-3 data. For NRZI data, it changes the count up/down direction after every single transition. For MLT-3 data, it changes the count up/down direction after every two transitions. The NRZI to MLT-3 data conversion is implemented without reference to the bit timing or clock information. The conversion requires detecting transition of the incoming NRZI data and set up the count up/down direction for the MLT-3 data. Asserting FX\_SEL high bypasses this encoding.

### **MULTIMODE TRANSMIT DRIVER**

The multimode driver transmits MLT-3 coded signal in 100BASE-TX mode and Manchester coded signal in 10BASE-T mode.

The slew rate of the transmitted MLT-3 signal can be controlled to eliminate high frequency EMI component. The MLT-3 signal after the magnetic has a typical rise/fall time of approximately 4 ns, which is within the target range specified in the ANSI TP- PMD standard.

In 10BASE-T mode, high frequency pre-emphasis is performed which extends the cable-driving distance without the need of an external filter. FLP/NLP also drives signals through the 10BASE-T driver. The 10BASE-T and 100BASE-TX transmit signals are multiplexed to the transmit output driver. This arrangement results in using the same external transformer for both the 10BASE-T and the 100BASE-TX. The driver output level is set by a built-in bandgap reference and an external resistor connected to the RIBB output pin. The resistor sets the output current for all modes of operation. Each of the TXOP/N outputs is an open drain device which has a source resistance of  $10\Omega$  maximum and a current rating of 40 mA for the 2  $V_{D-D}$  MLT-3 signal, 100 mA for  $5V_{D-D}$  Manchester signal when used 1:1 transformer.

### **PLL CLOCK SYNTHESIZER**

The Transceiver also includes on-chip PLL clock synthesizer that generates a 125-MHz and a 25-MHz clock for the 100BASE-TX, or a 100-MHz and 20-MHz clock for the 10BASE-T and auto-negotiation operations. The PLL clock generator uses a fully differential VCO cell that induces a very low jitter. The Zero Dead Zone Phase Detection method implemented in this design provides excellent phase tracking. A charge pump with charge sharing compensation is also included to further reduce jitter at different loop filter voltages. On-chip loop filter eliminates the need for external components and avoids external noise pickup. Only one external 25-MHz crystal or a signal source is required as a reference clock.

# **RECEIVE FUNCTION**

In 100BASE-TX mode, the receive function implements the reverse order function in the transmit path. It includes a receiver with adaptive equalization and DC restoration, MLT-3 to NRZI conversion, data and clock recovery at 125 MHz, NRZI to NRZ conversion, Serial-to-Parallel conversion, de-scrambling, and 5B to 4B decoding. The receiver circuit starts with a DC bias for the differential RX± inputs, follows with a low-pass filter to filter out high frequency noise from the transmission channel media. An energy detect circuit is also added to determine whether there is any signal energy on the media. This is useful in the power-saving mode. The amplification ratio and slicer threshold is set by the on-chip bandgap reference.

In 10BASE-T mode, signal first passes through a third order lowpass filter, which filters all the noise from the cable, board, and transformer. This eliminates the need for a 10BASE-T external filter. A Manchester decoder and a Serial-to Parallel follows to generate the 4-bit data in MII mode.

### **ADAPTIVE EQUALIZER**

Each of the eight transceivers is designed to accommodate for maximum cable length of 150m UTP CAT5 cable. A 150m of UTP CAT-5 cable (such as AT&T 1061) has an attenuation of 31 dB at 100 MHz. A typical attenuation of a 100m cable is 20 dB. The worst case attenuation is around 24–26 dB defined by TP-PMD.

The amplitude and phase distortion from the cable causes inter-symbol interference (ISI) which makes clock and data recovery impossible. Adaptive equalizer is done by matching the inverse transfer function of the twist-pair cable. This is a variable equalizer that changes its equalizer frequency response in accordance to cable length. The cable length is estimated based on comparisons of incoming signal strength against some the known cable characteristics. The equalizer has a monotonically frequency response, and tunes itself automatically for any cable length to compensate for the amplitude and phase distortion incurred from the cable.

### **LINK MONITOR**

Signal levels are detected through a squelch detection circuitry. A signal detect (SD) circuit follows the equalizer and is asserted high when the peak detector detects a post-equalized signal with peak to ground voltage level larger than 400 mV. This is approximately 40% of a normal signal voltage level. In addition, the energy level must be sustained longer than  $2\sim3~\mu s$  in order for the signal detects be asserted. It gets de-asserted approximately  $1\sim2~\mu s$  after the energy level is consistently less than 300 mV from peak to ground.

In 100BASE-TX mode, when no signal or invalid signal is detected on the receive pair, the link monitor enters in the link fail state where only scrambled idle code is transmitted. When a valid signal is detected for a minimum period of time, the link monitor enters a link pass state and transmit and receive functions are entered.

In 10BASE-T mode, a link-pulse detection circuit constantly monitors the RXIP/RXIN pins for the presence of valid link pulses.

## **BASELINE WANDER COMPENSATION**

The 100BASE-TX data stream is not always DC balanced. The transformer blocks the DC component of the incoming signal, thus the DC offset of the differential receives inputs can wander. The shift in the signal levels, coupled with non-zero rise and fall times of the serial stream can cause pulse-width distortion, creating jitter and possible increases in error rates. Therefore, a DC restoration circuit is needed to compensate for the attenuation of DC component. The Transceiver implemented is a patent-pending DC restoration circuit, unlike the traditional implementation; it does not need the feedback information from the slicer and clock recovery. This not only simplifies the system/circuit design but also eliminates any random/systematic offset on the receive path. In 10BASE-T mode, the baseline wander correction circuit is not required and is bypassed.

### CLOCK/DATA RECOVERY

The equalized MLT-3 signal passes through a slicer circuit that converts to NRZI format. The transceiver uses a mixed-signal phase locked loop (PLL) to extract clock information of the incoming NRZI data. The extracted clock is used to re-time the data stream and set the data boundaries. The transmit clock is locked to the 25-MHz clock input while the receive clock is locked to the incoming data streams. When initial lock is achieved, the PLL switches to lock to the data stream, extracts a 125-MHz clock and uses that for bit framing to recover data. The recovered 125-MHz clock is also used to generate an internal 25-MHz RX\_CLK. The PLL requires no external components for its operation and has high noise immunity and low jitter. It provides fast phase align (lock) to data in one transition and its data/clock acquisition time after power-on is less than 60 transitions. The PLL can maintain lock on run-lengths of up to 60 data bits in the absence of signal transitions. When no valid data is present (like when the SD is de-asserted), the PLL switches back to lock with TX\_CLK and provides a continuously running RX\_CLK.

### **DECODER/DESCRAMBLER**

The descrambler detects the state of the transmit Linear Feedback Shift Register (LFSR) by looking for a sequence representing consecutive idle codes. The descrambler acquires lock with the data stream by recognizing IDLE bursts of 30 or more bits and locking to its de-ciphering Linear Feedback Shift Register (LFSR).

Once lock is acquired, the device operates with the inter-packet-gap (IPG) as low as 40 ns. Before lock occurs, the descrambler requires a minimum of 720 nS of idle in between packet in order to acquire lock.

The deciphering logic also tracks the number of consecutive receive errors detected while RX\_DV is asserted. Once the error counter exceeds its limit (currently set to 64 consecutive errors), the logic assumes that lock has been lost, and the decipher circuit resets itself. The process of regaining lock begins again.

Stream cipher de-scrambler is not used in 10BASE-T mode.

# **AUTO-NEGOTIATION AND MISCELLANEOUS FUNCTIONS**

Each of the transceivers contain the ability to negotiate its mode of operation over the twisted pair using the auto-negotiation mechanism defined in the clause 28 IEEE 802.3u specification. Auto-negotiation may be disabled by software via EEPROM. The transceiver automatically chooses its mode of operation by detecting the incoming signal.

During auto-negotiation, the auto-negotiation advertisement register is sent to its link partner through a series of fast link pulse (FLP). When auto-negotiation enabled, Transceiver sends FLP during the following conditions:

- Power on

- Link loss

- Restart command

At the same time, the device monitors incoming data to determine its mode of operation. Parallel detection circuit is enabled as soon as 10BASE-T idle or 100BASE-TX idle is detected. The mode of operation is configured based on the technology of the incoming signal. When the device receives a burst of FLP from its link partner with three identical link code words (ignoring acknowledge bit), it stores these code words in the auto-negotiation link partner ability register and waits for the next three identical code words. Once the device detects the second code word, it configures itself to the highest technology that is common to both ends. The technology priorities are:

- 1 100BASE-TX, half-duplex

- 2 10BASE-T half-duplex

Once auto-negotiation is complete, the status register reflects the actual speed that was chosen.

#### PARALLEL DETECTION

The Transceiver also checks for 10BASE-T NLP or 100BASE-TX idle symbols. If either is detected, the device automatically configures to match the detected operating speed in half-duplex mode. This ability allows the device to communicate with legacy 10BASE-T and 100BASE-TX systems.

### CARRIER SENSE/RXDV FOR MII PORT ONLY

Carrier sense is asserted asynchronously on the CRS pins as soon as activity is detected on the receive data stream. RX\_DV is asserted as soon as a valid SSD (Start-of-Stream Delimiter) is detected. Carrier sense and RX\_DV are deasserted synchronously upon detection of a valid end of stream delimiter or two consecutive idle code groups in the receive data stream. If carrier sense is asserted and a valid SSD is not detected immediately, RX\_ER is asserted instead of RX\_DV.

In 10BASE-T mode, carrier sense is asserted asynchronously on the CRS pin when valid preamble activity is detected on the RXIP/RXIN pins. In half-duplex mode, the CRS is activated during transmit and receive of data.

### CABLE LENGTH MONITOR

The AC208 can also detect the length of the cable and display the result in the interrupt control/status register (such as, 0000 stands for less than 10m cable used, 0001 stands for ~ 10m of cable, and 1111 stands for 150m cable).

## **BRIDGE FUNCTION**

### MEDIA INDEPENDENT INTERFACE

The bridge supports MII for 10/100 Mbps. Port 0 of bridge can support either 10 or 100, while port 1 supports only at 100 Mbps. Refer to the mode pin table to configure port 0.

### FORWARDING SCHEME

The bridge supports the store-and-forward scheme only. It does not support cut-through-mode. With store-and-forward, the incoming packet should be completely received to the buffer without error before it can be sent out.

### **ADDRESS RECOGNITION**

The self-learning bridge function is based on source address field of packets. The bridge uses the XOR hashing algorithm to address look-up table. Programmable aging time and fast aging control is supported.

### RESET AND RESTART

At power on, the bridge initially goes to the SRAM self-test mode. It generates eight patterns to evaluate SRAM status.

### MEDIA ACCESS CONTROL

The bridge media access control (MAC) complies with certain IEEE 802.3 MAC protocols such as frame formatting and collision handling, but does not generate CRC codes. It generates a 56-bit preamble and start of frame delimiter while a packet is sending. In half-duplex mode, the device listens before transmitting, to prevent traffic jam. During collision, a packet is retransmitted at a random time.

# INITIALIZATION AND SETUP

### **HARDWARE CONFIGURATION**

Several different states of operation can be chosen through hardware configuration. External pins may be pulled high or low at reset time. The combination of high and low values determines the power on state of the device.

Many of these pins are multi-function pins which change their meaning when reset ends.

### **SOFTWARE CONFIGURATION**

Several different states of transceiver operation may be chosen through the MDC/MDIO interface. For details, see "Register Descriptions" on page 18.

### **LEDs**

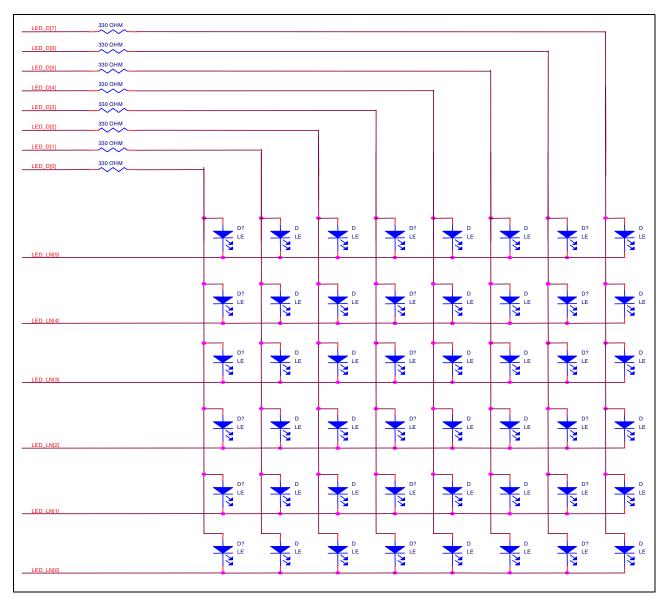

Using an LED display matrix with a refresh technique, only 16 pins are required to drive up to 48 LEDs with unique information. On, Off, and Flash states are used to indicate different information. With a reduced number of signals, the LED display is easier to route on the board, and less costly. The active-low LED data is driven out of LED\_D[0:7] pins for each port and the corresponding LED functions are LED\_LN[5:0] pin. For details, see "LED Display/Configuration/PROM Interface" on page 16 and "LED Display Matrix" on page 38.

The AC208 supports two LEDs per port. The following table describes how each of the LED is connected.

Signals LED\_D[0:7] are indicators of port 1 through 8. Signals LED\_LN[0:5] are events driven of port 1 through 8.

Table 1: LED Connections

| Signals   | Events                                                   | Descriptions                                   |           |           |           |            |           |           |          |      |

|-----------|----------------------------------------------------------|------------------------------------------------|-----------|-----------|-----------|------------|-----------|-----------|----------|------|

| LED_LN[0] | Link Status/Activity                                     | Active low indi                                | cates 10  | 0M link i | s good. I | 3linking i | indicates | 100M a    | ctivity. |      |

| LED_LN[1] | Speed/Partition                                          | Active low indi                                | cates 10  | M link is | good. B   | linking in | dicates 1 | IOM activ | vity.    |      |

| LED_LN[2] | Display utilization<br>on bridge segment<br>A (100 Mbps) | LED_LN[2] is a port basis, but utilization.    |           |           |           |            |           |           |          |      |

|           |                                                          | LED_D[0:7]                                     | 7         | 6         | 5         | 4          | 3         | 2         | 1        | 0    |

|           |                                                          | Percent Util.                                  | non       | non       | 85%       | 65%        | 45%       | 25%       | 12%      | 1%   |

| LED_LN[3] | Display utilization<br>on bridge segment<br>B (10 Mbps)  | LED_LN[3] is a port basis, but utilization.    |           |           |           |            |           |           |          |      |

|           |                                                          | LED_D[0:7]                                     | 7         | 6         | 5         | 4          | 3         | 2         | 1        | 0    |

|           |                                                          | Percent Util.                                  | non       | non       | non       | 65%        | 45%       | 25%       | 12%      | 1%   |

| LED_LN[4] | Display collision on<br>bridge segment A<br>(100 Mbps)   | LED_LN[4] is a basis, but rath collision. How  | er per se | gment b   | asis. The | ELED_D     | [1:7] ind | icates pe |          |      |

|           |                                                          | LED_D[0:7]                                     | 7         | 6         | 5         | 4          | 3         | 2         | 1        | 0    |

|           |                                                          | Percent Col.                                   | 66%       | 32%       | 16%       | 8%         | 4%        | 2%        | 1%       | Col. |

| LED_LN[5] | Display collision on<br>bridge segment B<br>(10 Mbps)    | LED_LN[5] is a basis, but rath collision. Howe | er per se | egment b  | asis. The | e LED_D    | [1:7] ind | icates pe |          |      |

|           |                                                          | LED_D[0:7]                                     | 7         | 6         | 5         | 4          | 3         | 2         | 1        | 0    |

|           |                                                          | Percent Col.                                   | 66%       | 32%       | 16%       | 8%         | 4%        | 2%        | 1%       | Col. |

# ADDRESSING ALGORITHM, ROUTING, LEARNING, AND AGING

# **ADDRESS TABLE**

The address table can store up to 1K entries and each entry consists of 48-bit MAC address, 8-bit port identifier, 1-bit indication flag and 6-bit aging timer.

Table 2: Content of Address Lookup Table

| 3130  |       |       |       |       |  |

|-------|-------|-------|-------|-------|--|

| V     | Timer | Port# | MAC#1 | MAC#2 |  |

| MAC#3 |       | MAC#4 | MAC#5 | MAC#6 |  |

Bit 30: Entry valid/empty indication, 1 = valid entry, 0 = empty entry.

Bit 29-24: Aging timer.

Bit 23-16: Port number

### **ADDRESS RECOGNITION**

The exclusive or addressing algorithm is used for address lookup table addressing (see the following figure).

Figure 2: Exclusive or Hashing Algorithm

The final address of address lookup table is the hashed address[9:0].

### **ROUTING DECISION**

If a record is empty, the packet is broadcast and treated as an unknown frame. Otherwise, the record is read, and compared with the current DA. If two addresses are the same, the port number is decided, and the packet is forwarded to the assigned port. If address collision occurred, different MAC address, the incoming packet is considered an unknown packet.

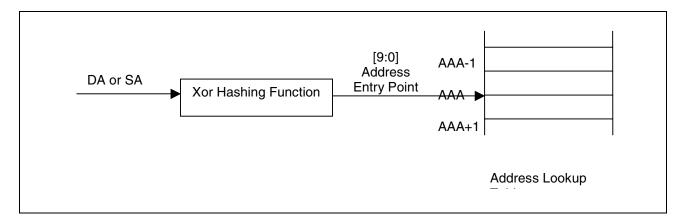

#### LEARNING PROCESS

The address learning process is composed of the SA packets and the addressing algorithm described above. The bridge checks each incoming packets integrity and buffers availability. If a packet is error-free and the buffer is available, the SA/port number pair of the packet is written into the address lookup table. The following figure describes the general operations of address learning and recognition.

Figure 3: Address Learning and Recognition

### **AGING TIME**

The switch automatically examines the status of address lookup table. The round robin speed and checking timer are dependent on the aging time. The switch aging time is set at 300s. When the aging timer is started after power on, the switch guaranties that free spaces can be released from occupied address entries.

### FORWARDING SCHEME

The store-and-forward algorithm is used. The incoming packet has to be completely stored in the buffer and verified error-free before forwarding operations take place.

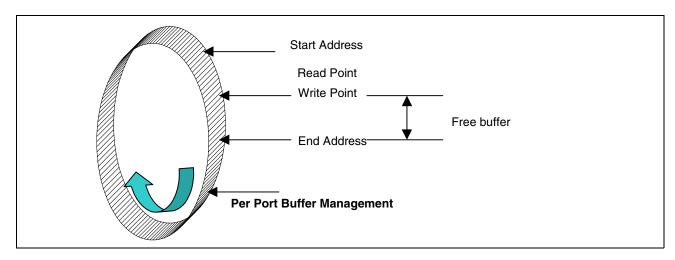

### BRIDGE BUFFER MANAGEMENT AND QUEUES

The bridge buffering management continues to store received packets into memory. The buffer size for 100M port is 16K bytes, and 8K bytes for 10M port.

**Figure 4: Basic Memory Management Concept**

The bridge uses the six pointers to control per port buffer status. Start Address point is the beginning of memory address for each port and the End Address point is the last address of memory for each port. The Read/Write and shadow Read/Write pointers are dynamically changed depending on the current outgoing and incoming packets in the storage. If the Write pointer reaches the Read pointer and the size between write and read pointers is smaller than 2K bytes, buffer is full. On the other hand, when read/write pointers are equal, the buffer is empty.

Table 3: Embedded Memory Structure

|        | 31                               |

|--------|----------------------------------|

| 0x0000 | 2K x 32 for address lookup table |

| 0x07FF |                                  |

| 0x0800 | 4K x 32 for 100M Bridge Port     |

| 0x17FF |                                  |

| 0x1800 | 2K x 32 for 10M Bridge Port      |

| 0x1FFF |                                  |

# Section 2: Pins

## **PIN DESCRIPTIONS**

Many of these device pins have multiple functions. The separate descriptions of each pin are listed in the proper sections. Designers must assure that they have identified all modes of operation prior to final design.

The media dependent interface (MDI) pin assignment shown below and in the pin description table is subject to change without notice. The user is advised to contact Altima Communications, Inc. before implementing any design based on the information provided in this data sheet.

### Signals types:

- I = Input

- O = Output

- Z = High impedance

- $U = Pull up with 10 k\Omega$

- D = Pull down with 10  $k\Omega$

- S = Schimitt Trigger

- A = Analog signal

- P = Power

- G = Ground

- \* = Active low signal

Table 4: Media Dependent Interface Pins (TX)

| Pin Name | Pin # | Туре | Description                                               |

|----------|-------|------|-----------------------------------------------------------|

| RXIP_7   | 107   | Al   | Receiver Input Positive for both 10BASE-T and 100BASE-TX. |

| RXIP_6   | 96    | Al   |                                                           |

| RXIP_5   | 95    | Al   |                                                           |

| RXIP_4   | 84    | Al   |                                                           |

| RXIP_3   | 83    | Al   |                                                           |

| RXIP_2   | 72    | Al   |                                                           |

| RXIP_1   | 71    | Al   |                                                           |

| RXIP_0   | 60    | Al   |                                                           |

| RXIN_7   | 106   | Al   | Receiver Input Negative for both 10BASE-T and 100BASE-TX. |

| RXIN_6   | 97    | ΑI   |                                                           |

| RXIN_5   | 94    | Al   |                                                           |

| RXIN_4   | 85    | ΑI   |                                                           |

| RXIN_3   | 82    | Al   |                                                           |

| RXIN_2   | 73    | Al   |                                                           |

| RXIN_1   | 70    | Al   |                                                           |

| RXIN_0   | 61    | Al   |                                                           |

Table 4: Media Dependent Interface Pins (TX) (Cont.)

| Pin Name | Pin # | Туре | Description                                                   |

|----------|-------|------|---------------------------------------------------------------|

| TXOP_7   | 104   | AO   | Transmitter Output Positive for both 10BASE-T and 100BASE-TX. |

| TXOP_6   | 99    | AO   |                                                               |

| TXOP_5   | 92    | AO   |                                                               |

| TXOP_4   | 87    | AO   |                                                               |

| TXOP_3   | 80    | AO   |                                                               |

| TXOP_2   | 75    | AO   |                                                               |

| TXOP_1   | 68    | AO   |                                                               |

| TXOP_0   | 63    | AO   |                                                               |

| TXON_7   | 103   | AO   | Transmitter Output Negative for both 10BASE-T and 100BASE-TX. |

| TXON_6   | 100   | AO   |                                                               |

| TXON_5   | 91    | AO   |                                                               |

| TXON_4   | 88    | AO   |                                                               |

| TXON_3   | 79    | AO   |                                                               |

| TXON_2   | 76    | AO   |                                                               |

| TXON_1   | 67    | AO   |                                                               |

| TXON_0   | 64    | AO   |                                                               |

## Table 5: EEPROM Interface

| Pin Name          | Pin # | Туре                                                           | Description                                                    |

|-------------------|-------|----------------------------------------------------------------|----------------------------------------------------------------|

| PROM_CS           | 127   | O PROM chip select. Connected to Chip Select pin of 93C EEPROM |                                                                |

| PROM_CLK LED_D[6] | 124   | 0                                                              | PROM Clock. Connected to CLK pin of 93C46 serial EEPROM        |

| PROM_OUT LED_D[5] | 123   | 0                                                              | PROM Data Out. Connected to Data_In pin of 93C46 serial EEPROM |

| PROM_IN LED_D[7]  | 125   | I,D                                                            | PROM Data In. Connected to Data_Out pin of 93C46 serial EEPROM |

### Table 6: MDC/MDIO Interface

| Pin Name      | Pin # | Туре  | Description                                                                                                                                                                                |

|---------------|-------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MDC (PROM_CS) | 127   | I,U   | Clock signal between the external device and PHY registers for communication synchronization                                                                                               |

| MDIO          | 128   | I/O,D | Data Input/Output. It is a bi-directional data interface used by the external device to access only the internal PHY registers within the AC208. This pin has internal pull-down register. |

Table 7: 100 Mbps Internal Repeater

| Pin Name                   | Pin # | Type         | Description                                                                                                                                                              |  |

|----------------------------|-------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| M100COL_LOCAL*             | 3     | I/O, U       | 100M Local Collision. Input when ChipID = 00. Active low to indicate collision on all other ChipIds.                                                                     |  |

| M100ACTO*                  | 4     | O, U         | Output to ChipID=00 for ChipID≠00 to signal local activity. This signal is pure combinational logic and is not in sync with any clock source. (Refer to next 3 signals). |  |

| M100ACTI_0*<br>(M100ACTO*) | 4     | I,U          | Input for ChipID=00 from ChipID≠00 M100ACTO* pins to indicate activities. Open on all other ChipIDs.                                                                     |  |

| M100ACTI_1*                | 6     | I,U          | Connected from ChipID=00 to ChipID=10 M100ACTO* to sense activities. Open on all other ChipIDs.                                                                          |  |

| M100ACTI_2*                | 7     | I,U          | Connected from ChipID=00 to ChipID=11 M100ACTO* to sense activities. Open on all other ChipIDs.                                                                          |  |

| M100COL_SYS*               | 2     | I/O,U        | ChipID=00 drives this pin the same as 100COLBP* to indic local collision.                                                                                                |  |

| M100CRS_SYS*               | 8     | I/O,U        | ChipID=00 drives this pin the same as 100CRSBP* to indical local activity.                                                                                               |  |

| MS100D4                    | 14    | I/O,D        | Multiple/Stacked Data Group. Transmit and receive data in                                                                                                                |  |

| MS100D3                    | 13    | I/O,D        | scrambled 5B data groups for multiple devices. Data is sampled                                                                                                           |  |

| MS100D2                    | 12    | I/O,D        | at the rising edge of MS100D_CLK and driven out on falling edge of MS100D_CLK.                                                                                           |  |

| MS100D1                    | 11    | I/O,D        |                                                                                                                                                                          |  |

| MS100D0                    | 9     | I/O,D        |                                                                                                                                                                          |  |

| MS100D_EN*                 | 1     | I/O,U        | Multiple/Stacked Data Enable. Active-low when data is valid. Signal is driven out on the falling edge of MS100D_CLK, and sampled at the rising edge of MS100D_CLK.       |  |

| MS100D_CLK                 | 16    | I/O, U,<br>S | Multiple/Stacked Data Clock. The bi-directional non-continuous 25 MHz recovered clock for synchronizing with MS100D[4:0], and MS100D_EN*.                                |  |

Table 8: 10 Mbps Internal Repeater Bus

| Pin Name                 | Pin # | Туре         | Description                                                                                                                                                                           |  |

|--------------------------|-------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| M10COL_LOCAL*            | 18    | I/O, U       | 10M Local Collision. Input when ChipID = 00. Active low to indicate collision on all other ChipIds. M10COL_LOCAL# ≠ (local_collision).                                                |  |

| M10ACTO*                 | 19    | O, U         | Output to ChipID = 00 for ChipID $\neq$ 00 to signal local activity. (Refer to next 3 signals).                                                                                       |  |

| M10ACTI_0*<br>(M10ACTO*) | 19    | I,U          | Connected from ChipID = 00 from ChipID = 01 M10ACTO* to sense activities. Open on all other ChipIDs.                                                                                  |  |

| M10ACTI_1*               | 20    | I,U          | Connected from ChipID 00 to ChipID 10 M10ACTO* to sense activities. Open on all other ChipIDs.                                                                                        |  |

| M10ACTI_2*               | 21    | I,U          | Connected from ChipID 00 to ChipID 11 M10ACTO* to sense activities. Open on all other ChipIDs.                                                                                        |  |

| M10COL_SYS*              | 27    | I/O,U        | ChipID 00 drives this pin the same as 10COLBP* to indicate system collision.                                                                                                          |  |

| M10CRS_SYS*              | 22    | I/O,U        | O,U ChipID 00 drives this pin the same as 10CRSBP* to indicate system activity.                                                                                                       |  |

| MS10D                    | 25    | I/O,D        | Multiple/Stacked Data Group. Transmit and receive data in 10BASE-T for multiple devices. Data is sampled at the rising edge of MS10D_CLK and driven out on falling edge of MS10D_CLK. |  |

| MS10D_EN*                | 26    | I/O,U        | Multiple/Stacked Data Enable. Active when data is valid.                                                                                                                              |  |

| MS10D_CLK                | 24    | I/O, U,<br>S | Multiple/Stacked Data Clock. The bi-directional non-continuous 10 MHz recovered clock for synchronizing with MS10D and MS10D_EN*.                                                     |  |

## LED DISPLAY/CONFIGURATION/PROM INTERFACE

The LED pins are shared with reset-read configuration pins, test pins and EEPROM interface. The value applied on the reset-read pins is only valid at the end of the reset cycle. The EEPROM interface is active after the reset cycle. Once the data in the EEPROM is read, the same pins are used for LED display. Forty-eight LED outputs are available through an 6x8 matrix.

Table 9: LED Pins

| Pin Name  | Pin # | Туре   | Description                                                                                                      |

|-----------|-------|--------|------------------------------------------------------------------------------------------------------------------|

| LED_LN[5] | 50    | 0      | Enable corresponding LED display line in the display matrix, active low                                          |

| LED_LN[4] | 51    | 48 mA  | output. The detail of how to program and connect the LEDs is in the LED Setup section.                           |

| LED_LN[3] | 52    |        | •                                                                                                                |

| LED_LN[2] | 53    |        | LED_LN*[5] = Display 10BASE-T Collision rate and segment collision status.                                       |

| LED_LN[1] | 54    |        | LED_LN*[4] = Display 100 Mbps Collision rate and segment collision                                               |

| LED_LN[0] | 55    |        | status                                                                                                           |

|           |       |        | LED_LN*[3] = Display 10M segment utilization rate                                                                |

|           |       |        | LED_LN*[2] = Display 100M segment utilization rate                                                               |

|           |       |        | LED_LN*[1] = Programmable LED display. The default is to display 10M Link/Activity information of each port.     |

|           |       |        | $LED_LN^*[0] = Programmable LED display. The default is to display 100M Link/Activity information of each port.$ |

| LED_D[7]  | 125   | I/O, D | Output for LED display information of each column in the display matrix.                                         |

| LED_D[6]  | 124   |        | Active high output.                                                                                              |

| LED_D[5]  | 123   |        |                                                                                                                  |

| LED_D[4]  | 122   |        |                                                                                                                  |

| LED_D[3]  | 121   |        |                                                                                                                  |

| LED_D[2]  | 120   |        |                                                                                                                  |

| LED_D[1]  | 119   |        |                                                                                                                  |

| LED_D[0]  | 118   |        |                                                                                                                  |

Table 10: Configuration and Setup

| Pin Name             | Pin # | Туре | Description                                                                      |      |  |

|----------------------|-------|------|----------------------------------------------------------------------------------|------|--|

| Mode[3]              | 37    | I,D  | Mode[1:0] Domain A Domain B                                                      |      |  |

| Mode[2] (LED_D[4])   | 122   |      | 00 100M Rptr 10M Rptr (Master)                                                   |      |  |

| Mode[1] (LED_D[1])   | 119   |      | 01 100M Rptr 10M Rptr (Slave, Bridge disab                                       | ole) |  |

| Mode[0] (LED_D[0])   | 118   |      | 10 100M Port 7                                                                   |      |  |

|                      |       |      | 11 100M Rptr 10M Rptr (Slave, Bridge, enal and 10M disable)                      | ole  |  |

|                      |       |      | Mode[3:2] MII                                                                    |      |  |

|                      |       |      | Reserved                                                                         |      |  |

| TP125                | 36    | I    | 1:select 1:1.25 xformer                                                          |      |  |

| ChipID[0] (LED_D[3]) | 120   | I,D  | To assign chip ID for four devices in a single box. One de                       | vice |  |

| ChipID[1] (LED_D[2]) | 121   |      | in the box must be assigned with $ChipID = 0$ .                                  |      |  |

| RBP                  | 112   | I    | Reference bias resistor. Connected to analog ground through a 10K (1%) resistor. |      |  |

## Table 11: Clock Reset

| Pin Name | Pin # | Type  | Description                                                                                                                                                                            |  |

|----------|-------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|