LTC2373-16

# 16-Bit, 1Msps, 8-Channel SAR ADC with 96dB SNR

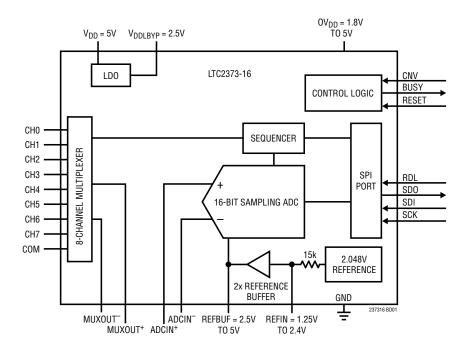

The LTC<sup>®</sup>2373-16 is a low noise, high speed, 8-channel

16-bit successive approximation register (SAR) ADC. Oper-

ating from a single 5V supply, the LTC2373-16 has a highly

configurable. low crosstalk 8-channel input multiplexer.

supporting fully differential, pseudo-differential unipolar

and pseudo-differential bipolar analog input ranges. The

LTC2373-16 achieves ±1LSB INL (maximum) in all input

ranges, no missing codes at 16-bits and 96dB (fully dif-

The LTC2373-16 has an onboard low drift (20ppm/°C max)

2.048V temperature-compensated reference and a single-

shot capable reference buffer. The LTC2373-16 also has a

high speed SPI-compatible serial interface that supports

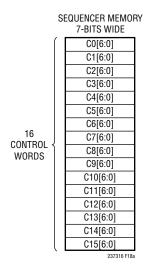

1.8V, 2.5V, 3.3V and 5V logic through which a sequencer

with a depth of 16 may be programmed. An internal os-

cillator sets the conversion time, easing external timing

considerations. The LTC2373-16 dissipates only 40mW

and automatically naps between conversions, leading to

reduced power dissipation that scales with the sampling rate. A sleep mode is also provided to reduce the power

consumption of the LTC2373-16 to 300µW for further

∠ , LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks and

respective owners. Protected by U.S. Patents, including 7705765, 7961132, 8319673.

SoftSpan is a trademark of Analog Devices, Inc. All other trademarks are the property of their

power savings during inactive periods.

ferential)/ 93.4dB (pseudo-differential) SNR (typical).

DESCRIPTION

# FEATURES

- 1Msps Throughput Rate

- 16-Bit Resolution with No Missing Codes

- 8-Channel Multiplexer with Selectable Input Range

- Fully Differential (±4.096V)

- Pseudo-Differential Unipolar (OV to 4.096V)

- Pseudo-Differential Bipolar (±2.048V)

- INL: ±1LSB (Maximum)

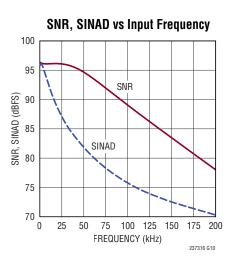

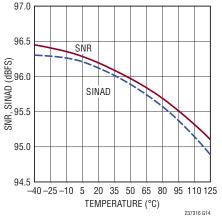

- SNR: 96dB (Fully Differential)/93.4dB (Pseudo-Differential) (Typical) at f<sub>IN</sub> = 1kHz

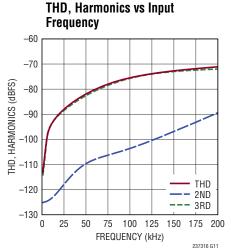

- THD: -110dB (Typical) at f<sub>IN</sub> = 1kHz

- Programmable Sequencer

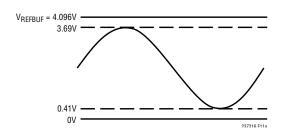

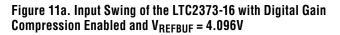

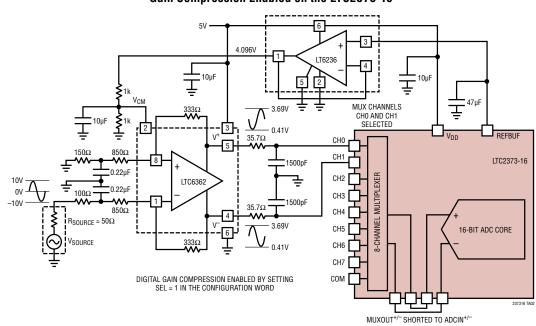

- Selectable Digital Gain Compression

- Single 5V Supply with 1.8V to 5V I/O Voltages

- SPI-Compatible Serial I/O

- Onboard 2.048V Reference and Reference Buffer

- No Pipeline Delay, No Cycle Latency

- Power Dissipation 40mW (Typical)

- Guaranteed Operation to 125°C

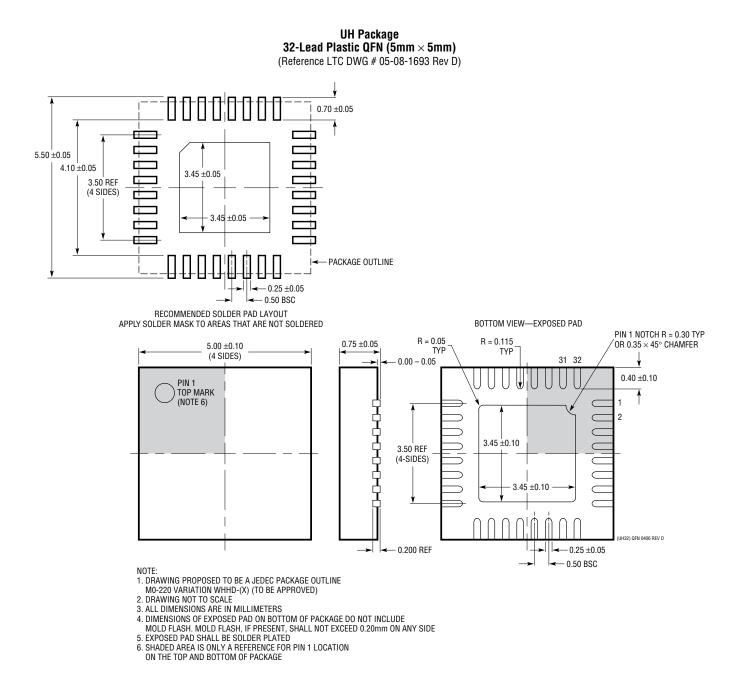

- 32-Lead 5mm × 5mm QFN Package

# **APPLICATIONS**

- Programmable Logic Controllers

- Industrial Process Control

- High Speed Data Acquisition

- Portable or Compact Instrumentation

- ATE

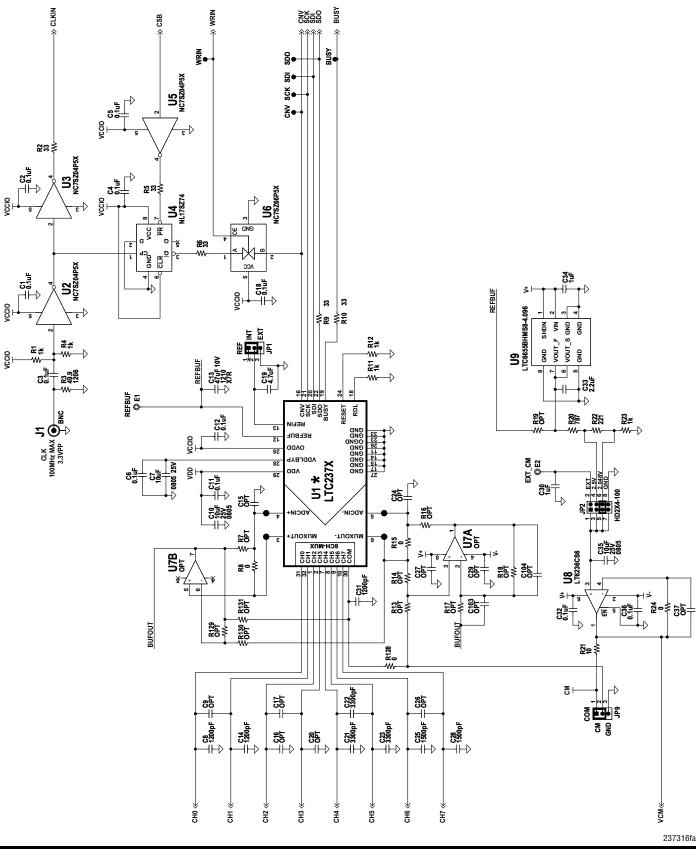

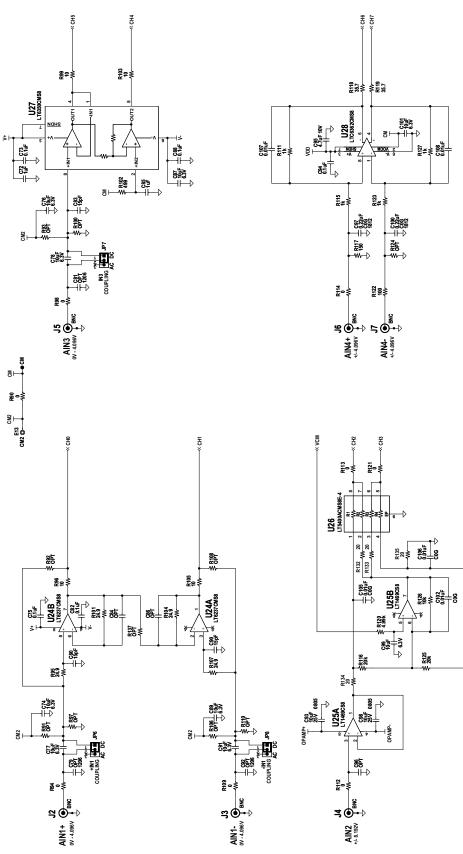

#### **Integral Nonlinearity** vs Output Code 5 4.096V 1.8V TO 5V 10 FULLY DIFFERENTIAL 0V 0.8 10µF 2.2µF BIPOLAR 0.1uF UNIPOLAR 0\ 06 \_ ᆂ \_ 0.4 100 V<sub>DDLBYP</sub> OV<sub>DD</sub> VDD 4.096 (LSB) RESE 0.2 CH1 LTC2373-16 1200pF RDL ERROR ( 0\ CH2 -0.0 СНЗ 4.096 MUX SDO 1200pF 16-BIT -0.2 CH4 SCK SDI SAMPLING ADC CH5 Z NUXOUT -0.4 CH6 CH7 IIIXUII BUS SAMPLE -0.6 4.096\ CNV CLOCK REFRUE REFIN GNE -0.8 0\ 47µF 0.1µF -1.0 2 048V 0 16384 32768 49152 65536 Ŧ OUTPUT CODE 237316 TA018 237316fa

## TYPICAL APPLICATION

# **ABSOLUTE MAXIMUM RATINGS**

| (Notes | 1, | 2) |

|--------|----|----|

|--------|----|----|

| (                                                              |

|----------------------------------------------------------------|

| Supply Voltage (V <sub>DD</sub> )6V                            |

| Supply Voltage (OV <sub>DD</sub> )6V                           |

| Analog Input Voltage (Note 3)                                  |

| CH0 to CH7, COM (GND – $0.3V$ ) to (V <sub>DD</sub> + $0.3V$ ) |

| REFBUF (GND – 0.3V) to (V <sub>DD</sub> + 0.3V)                |

| REFIN                                                          |

| Digital Input Voltage                                          |

| (Note 3)(GND -0.3V) to (OV <sub>DD</sub> + 0.3V)               |

| Digital Output Voltage                                         |

| (Note 3)(GND -0.3V) to (OV <sub>DD</sub> + 0.3V)               |

| Power Dissipation                                              |

| Operating Temperature Range                                    |

| LTC2373C                                                       |

| LTC2373I–40°C to 85°C                                          |

| LTC2373H40°C to 125°C                                          |

| Storage Temperature Range65°C to 150°C                         |

|                                                                |

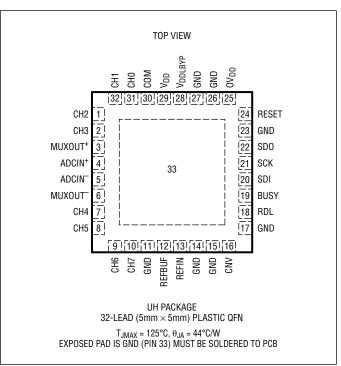

# PIN CONFIGURATION

# ORDER INFORMATION http://www.linear.com/product/LTC2373-16#orderinfo

| LEAD FREE FINISH  | TAPE AND REEL       | PART MARKING* | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|-------------------|---------------------|---------------|---------------------------------|-------------------|

| LTC2373CUH-16#PBF | LTC2373CUH-16#TRPBF | 237316        | 32-Lead (5mm × 5mm) Plastic QFN | 0°C to 70°C       |

| LTC2373IUH-16#PBF | LTC2373IUH-16#TRPBF | 237316        | 32-Lead (5mm × 5mm) Plastic QFN | –40°C to 85°C     |

| LTC2373HUH-16#PBF | LTC2373HUH-16#TRPBF | 237316        | 32-Lead (5mm × 5mm) Plastic QFN | -40°C to 125°C    |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. (Note 4)

| SYMBOL                       | PARAMETER                                 | CONDITIONS                                                                                                                                                      |             | MIN                                                  | ТҮР                         | MAX                                                                  | UNITS          |

|------------------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------------------------------------------------|-----------------------------|----------------------------------------------------------------------|----------------|

| V <sub>IN</sub> +            | Absolute Input Range (CH0 to CH7)         | (Note 5)                                                                                                                                                        | •           | -0.1                                                 |                             | V <sub>REFBUF</sub> + 0.1                                            | V              |

| V <sub>IN</sub> <sup>-</sup> | Absolute Input Range<br>(CH0 to CH7, COM) | Fully Differential (Note 5)<br>Pseudo-Differential Unipolar (Note 5)<br>Pseudo-Differential Bipolar (Note 5)                                                    | •<br>•<br>• | -0.1<br>-0.1<br>V <sub>REFBUF</sub> /2 - 0.1         | 0<br>V <sub>REFBUF</sub> /2 | V <sub>REFBUF</sub> + 0.1<br>0.1<br>V <sub>REFBUF</sub> /2 + 0.1     | V<br>V<br>V    |

| $V_{IN}^+ - V_{IN}^-$        | Input Differential Voltage Range          | Fully Differential<br>Pseudo-Differential Unipolar<br>Pseudo-Differential Bipolar                                                                               | •           | –V <sub>REFBUF</sub><br>0<br>–V <sub>REFBUF</sub> /2 |                             | V <sub>REFBUF</sub><br>V <sub>REFBUF</sub><br>V <sub>REFBUF</sub> /2 | V<br>V<br>V    |

| V <sub>CM</sub>              | Common Mode Input Range                   | Pseudo-Differential Bipolar and<br>Fully Differential (Note 6)                                                                                                  | •           | -V <sub>REFBUF</sub> /2 - 0.1                        | V <sub>REFBUF</sub> /2      | V <sub>REFBUF</sub> /2 + 0.1                                         | V              |

| I <sub>IN</sub>              | Analog Input Leakage Current              |                                                                                                                                                                 | •           | -1                                                   |                             | 1                                                                    | μA             |

| C <sub>IN</sub>              | Analog Input Capacitance                  | Sample Mode<br>Hold Mode                                                                                                                                        |             |                                                      | 75<br>5                     |                                                                      | pF<br>pF       |

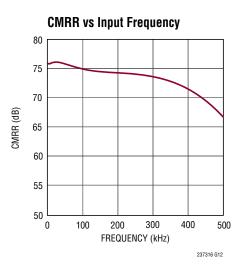

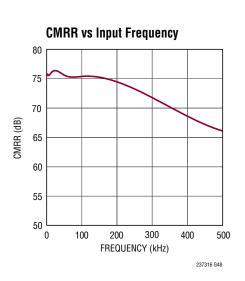

| CMRR                         | Input Common Mode Rejection Ratio         | Fully Differential, f <sub>IN</sub> = 500kHz<br>Pseudo-Differential Unipolar, f <sub>IN</sub> = 500kHz<br>Pseudo-Differential Bipolar, f <sub>IN</sub> = 500kHz |             |                                                      | 67<br>66<br>66              |                                                                      | dB<br>dB<br>dB |

# **CONVERTER CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. (Note 4)

| SYMBOL | PARAMETER                    | CONDITIONS                                                                                                                                           |   | MIN                  | TYP                  | MAX               | UNITS                                                          |

|--------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------------|----------------------|-------------------|----------------------------------------------------------------|

|        | Resolution                   |                                                                                                                                                      | • | 16                   |                      |                   | Bits                                                           |

|        | No Missing Codes             |                                                                                                                                                      | • | 16                   |                      |                   | Bits                                                           |

|        | Transition Noise             | Fully Differential<br>Pseudo-Differential Unipolar<br>Pseudo-Differential Bipolar                                                                    |   |                      | 0.3<br>0.6<br>0.6    |                   | LSB <sub>RMS</sub><br>LSB <sub>RMS</sub><br>LSB <sub>RMS</sub> |

| INL    | Integral Linearity Error     | Fully Differential (Note 7)<br>Pseudo-Differential Unipolar (Note 7)<br>Pseudo-Differential Bipolar (Note 7)                                         | • | -1<br>-1<br>-1       | 0.1<br>0.1<br>0.1    | 1<br>1<br>1       | LSB<br>LSB<br>LSB                                              |

| DNL    | Differential Linearity Error | Fully Differential (Note 6)<br>Pseudo-Differential Unipolar (Note 6)<br>Pseudo-Differential Bipolar (Note 6)                                         | • | -0.5<br>-0.5<br>-0.5 | 0.1<br>0.1<br>0.1    | 0.5<br>0.5<br>0.5 | LSB<br>LSB<br>LSB                                              |

| ZSE    | Zero-Scale Error             | Fully Differential (Note 8)<br>Pseudo-Differential Unipolar (Note 8)<br>Pseudo-Differential Bipolar (Note 8)                                         | • | -6<br>-6<br>-8       | ±0.5<br>±0.5<br>±0.5 | 6<br>6<br>8       | LSB<br>LSB<br>LSB                                              |

|        | Zero-Scale Error Drift       | Fully Differential<br>Pseudo-Differential Unipolar<br>Pseudo-Differential Bipolar                                                                    |   |                      | 1<br>2<br>2          |                   | mLSB/°C<br>mLSB/°C<br>mLSB/°C                                  |

|        | Zero-Scale Error Match       | Fully Differential<br>Pseudo-Differential Unipolar<br>Pseudo-Differential Bipolar                                                                    | • | 6<br>7<br>8          | ±0.5<br>±1<br>±1     | 6<br>7<br>8       | LSB<br>LSB<br>LSB                                              |

| FSE    | Full-Scale Error             | Fully Differential<br>REFBUF = 4.096V (REFBUF Overdriven) (Notes 8, 9)<br>REFIN = 2.048V (REFIN Overdriven) (Note 8)<br>Pseudo-Differential Unipolar | • | -15<br>-25           | ±2<br>±3             | 15<br>25          | LSB<br>LSB                                                     |

|        |                              | REFBUF = 4.096V (REFBUF Overdriven) (Notes 8, 9)<br>REFIN = 2.048V (REFIN Overdriven) (Note 8)<br>Pseudo-Differential Bipolar                        | • | -20<br>-45           | ±1<br>±4             | 20<br>45          | LSB<br>LSB                                                     |

|        |                              | REFBUF = 4.096V (REFBUF Overdriven) (Notes 8, 9)<br>REFIN = 2.048V (REFIN Overdriven) (Note 8)                                                       | • | -15<br>-30           | ±2<br>±3             | 15<br>30          | LSB<br>LSB                                                     |

237316fa

# **CONVERTER CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. (Note 4)

| SYMBOL | PARAMETER              | CONDITIONS                                                                                                  |   | MIN | TYP  | MAX | UNITS  |

|--------|------------------------|-------------------------------------------------------------------------------------------------------------|---|-----|------|-----|--------|

|        | Full-Scale Error Drift | Fully Differential<br>REFBUF = 4.096V (REFBUF Overdriven) (Note 9)                                          |   |     | 0.2  |     | ppm/°C |

|        |                        | Pseudo-Differential Unipolar<br>REFBUF = 4.096V (REFBUF Overdriven) (Note 9)<br>Pseudo-Differential Bipolar |   |     | 0.2  |     | ppm/°C |

|        |                        | REFBUF = 4.096V (REFBUF Overdriven) (Note 9)                                                                |   |     | 0.2  |     | ppm/°C |

|        | Full-Scale Error Match | Fully Differential<br>REFBUF = 4.096V (REFBUF Overdriven) (Note 9)<br>Pseudo-Differential Unipolar          | • | -6  | ±0.5 | 6   | LSB    |

|        |                        | REFBUF = 4.096V (REFBUF Overdriven) (Note 9)                                                                | • | -7  | ±1   | 7   | LSB    |

|        |                        | Pseudo-Differential Bipolar<br>REFBUF = 4.096V (REFBUF Overdriven) (Note 9)                                 | • | -8  | ±1   | 8   | LSB    |

# **DYNAMIC ACCURACY** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ and $A_{IN} = -1dBFS$ . (Notes 4, 10)

| SYMBOL | PARAMETER                            | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   | MIN      | ТҮР  | MAX | UNITS |

|--------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------|------|-----|-------|

| SINAD  | Signal-to-(Noise + Distortion) Ratio | Fully Differential<br>f <sub>IN</sub> = 1kHz, REFIN = 2.048V (REFIN Overdriven)<br>Pseudo-Differential Unipolar                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | • | 93       | 96   |     | dB    |

|        |                                      | f <sub>IN</sub> = 1kHz, REFIN = 2.048V (REFIN Overdriven)<br>Pseudo-Differential Bipolar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | • | 90.5     | 93.4 |     | dB    |

|        |                                      | f <sub>IN</sub> = 1kHz, REFIN = 2.048V (REFIN Overdriven)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | • | 90.5     | 93.4 |     | dB    |

|        |                                      | Fully Differential<br>$f_{IN} = 1 kHz$ , REFBUF = 5V (REFBUF Overdriven) (Note 9)<br>Pseudo-Differential Unipolar<br>$f_{IN} = 1 kHz$ , REFBUF = 5V (REFBUF Overdriven) (Note 9)<br>Pseudo-Differential Bipolar<br>$f_{IN} = 1 kHz$ , REFBUF = 5V (REFBUF Overdriven) (Note 9)94.5Fully Differential<br>$f_{IN} = 1 kHz$ , REFIN = 2.048V (REFIN Overdriven), SEL = 1<br>Pseudo-Differential Bipolar<br>$f_{IN} = 1 kHz$ , REFIN = 2.048V (REFIN Overdriven), SEL = 195Fully Differential<br>$f_{IN} = 1 kHz$ , REFIN = 2.048V (REFIN Overdriven), SEL = 191.5Fully Differential<br> |   | dB       |      |     |       |

|        |                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   | dB<br>dB |      |     |       |

|        |                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |          | 94.0 |     | UD    |

|        |                                      | f <sub>IN</sub> = 1kHz, REFIN = 2.048V (REFIN Overdriven), SEL = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |          | 95   |     | dB    |

|        |                                      | $f_{IN} = 1 \text{kHz}$ , REFIN = 2.048V (REFIN Overdriven), SEL = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |          | 91.5 |     | dB    |

| SNR    | Signal-to-Noise Ratio                | Fully Differential<br>f <sub>IN</sub> = 1kHz, REFIN = 2.048V (REFIN Overdriven)<br>Pseudo-Differential Unipolar                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | • | 93       | 96   | 5   | dB    |

|        |                                      | f <sub>IN</sub> = 1kHz, REFIN = 2.048V (REFIN Overdriven)<br>Pseudo-Differential Bipolar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | • | 90.5     | 93.4 |     | dB    |

|        |                                      | f <sub>IN</sub> = 1kHz, REFIN = 2.048V (REFIN Overdriven)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | • | 90.5     | 93.4 |     | dB    |

|        |                                      | Fully Differential<br>f <sub>IN</sub> = 1kHz, REFBUF = 5V (REFBUF Overdriven) (Note 9)<br>Pseudo-Differential Unipolar                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |          | 97   |     | dB    |

|        |                                      | f <sub>IN</sub> = 1kHz, REFBUF = 5V (REFBUF Overdriven) (Note 9)<br>Pseudo-Differential Bipolar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |          | 94.5 |     | dB    |

|        |                                      | $f_{IN} = 1 \text{kHz}, \text{REFBUF} = 5 \text{V} (\text{REFBUF Overdriven}) (\text{Note 9})$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |          | 94.5 |     | dB    |

|        |                                      | Fully Differential<br>f <sub>IN</sub> = 1kHz, REFIN = 2.048V (REFIN Overdriven), SEL = 1<br>Pseudo-Differential Bipolar                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |          | 95   |     | dB    |

|        |                                      | $f_{IN} = 1 \text{kHz}$ , REFIN = 2.048V (REFIN Overdriven), SEL = 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |          | 91.5 |     | dB    |

# **DYNAMIC ACCURACY** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C and A<sub>IN</sub> = -1dBFS. (Notes 4, 10)

| SYMBOL | PARAMETER                    | CONDITIONS                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | MIN      | ТҮР          | MAX          | UNITS             |

|--------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--------------|--------------|-------------------|

| THD 1  | Total Harmonic Distortion    | Fully Differential<br>f <sub>IN</sub> = 1kHz, REFIN = 2.048V (REFIN Overdriven)<br>Pseudo-Differential Unipolar<br>f <sub>IN</sub> = 1kHz, REFIN = 2.048V (REFIN Overdriven) | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          | -114<br>-110 | -101<br>-100 | dB<br>dB          |

|        |                              | Pseudo-Differential Bipolar<br>f <sub>IN</sub> = 1kHz, REFIN = 2.048V (REFIN Overdriven)                                                                                     | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          | -110         | -100         | dB                |

|        |                              | Fully Differential<br>f <sub>IN</sub> = 1kHz, REFBUF = 5V (REFBUF Overdriven) (Note 9)<br>Pseudo-Differential Unipolar                                                       | Dar<br>AV (REFIN Overdriven)<br>ar<br>AV (REFIN Overdriven)-110(REFBUF Overdriven) (Note 9)<br>olar<br>(REFBUF Overdriven) (Note 9)<br>ar<br>(REFBUF Overdriven) (Note 9)-111AV (REFIN Overdriven) (Note 9)<br>ar<br>(REFIN Overdriven), SEL = 1<br>ar<br>V (REFIN Overdriven), SEL = 1-113<br>-110AV (REFIN Overdriven), SEL = 1<br>ar<br>V (REFIN Overdriven)<br>ar<br>V (REFIN Overdriven)<br>ar<br>V (REFIN Overdriven)<br>ar<br>V (REFIN Overdriven)<br>ar<br>V (REFIN Overdriven)101111<br>ar<br>V (REFIN Overdriven)<br>ar<br>V (REFIN Overdriven)<br>ar<br>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          | dB           |              |                   |

|        |                              | $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | dB<br>dB |              |              |                   |

|        |                              | Fully Differential<br>f <sub>IN</sub> = 1kHz, REFIN = 2.048V (REFIN Overdriven), SEL = 1<br>Pseudo-Differential Bipolar                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          | -113         |              | dB                |

| SFDR   | Spurious Free Dynamic Range  | Fully Differential<br>f <sub>IN</sub> = 1kHz, REFIN = 2.048V (REFIN Overdriven)                                                                                              | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 101      |              |              | dB                |

|        |                              | f <sub>IN</sub> = 1kHz, REFIN = 2.048V (REFIN Overdriven)<br>Pseudo-Differential Bipolar                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |              |              | dB<br>dB          |

|        |                              | Fully Differential<br>f <sub>IN</sub> = 1kHz, REFBUF = 5V (REFBUF Overdriven) (Note 9)                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 100      |              |              | dB                |

|        |                              | f <sub>IN</sub> = 1kHz, REFBUF = 5V (REFBUF Overdriven) (Note 9)<br>Pseudo-Differential Bipolar                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |              |              | dB                |

|        |                              |                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          | 112          |              | dB                |

|        |                              | $f_{IN} = 1 \text{kHz}$ , REFIN = 2.048V (REFIN Overdriven), SEL = 1<br>Pseudo-Differential Bipolar                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |              |              | dB                |

|        |                              | f <sub>IN</sub> = 1kHz, REFIN = 2.048V (REFIN Overdriven), SEL = 1                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          | 113.5        |              | dB                |

|        | Channel-to-Channel Crosstalk | $f_{IN} = 100 kHz$ , Signal Applied to an OFF Channel                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          | -107         |              | dB                |

|        | –3dB Input Linear Bandwidth  |                                                                                                                                                                              | 2.048V (REFIN Overdriven)       -110       -100         = 5V (REFBUF Overdriven) (Note 9)       -111       -111         Unipolar       = 5V (REFBUF Overdriven) (Note 9)       -110         = 5V (REFBUF Overdriven) (Note 9)       -110       -110         = 5V (REFBUF Overdriven) (Note 9)       -110       -110         2.048V (REFIN Overdriven), SEL = 1       -113       -110         2.048V (REFIN Overdriven), SEL = 1       -110       -110         2.048V (REFIN Overdriven), SEL = 1       -110       -110         2.048V (REFIN Overdriven)       •       101       114         Unipolar       -2.048V (REFIN Overdriven)       •       100       110         2.048V (REFIN Overdriven)       •       100       110       114         Unipolar       •       100       110       112         = 5V (REFBUF Overdriven) (Note 9)       112       112       112         Unipolar       = 5V (REFBUF Overdriven) (Note 9)       112       112         = 5V (REFBUF Overdriven) (Note 9)       112       112       112.5         Bipolar       = 5V (REFIN Overdriven), SEL = 1       113.5       113.5 | MHz      |              |              |                   |

|        | Aperture Delay               |                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          | 500          |              | ps                |

|        | Aperture Jitter              |                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          | 4            |              | ps <sub>RMS</sub> |

| SFDR   | Transient Response           | Full-Scale Step                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          | 460          |              | ns                |

# **INTERNAL REFERENCE CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25$ °C. (Note 4)

| SYMBOL             | PARAMETER                                  | CONDITIONS                       |   | MIN   | ТҮР   | MAX   | UNITS  |

|--------------------|--------------------------------------------|----------------------------------|---|-------|-------|-------|--------|

| V <sub>REFIN</sub> | Internal Reference Output Voltage          |                                  |   | 2.043 | 2.048 | 2.053 | V      |

|                    | V <sub>REFIN</sub> Temperature Coefficient | (Note 11)                        | • |       | 4     | 20    | ppm/°C |

|                    | REFIN Output Impedance                     |                                  |   |       | 15    |       | kΩ     |

|                    | V <sub>REFIN</sub> Line Regulation         | V <sub>DD</sub> = 4.75V to 5.25V |   |       | 0.06  |       | mV/V   |

|                    | REFIN Input Voltage Range                  | (REFIN Overdriven) (Note 5)      |   | 1.25  |       | 2.4   | V      |

# **REFERENCE BUFFER CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. (Note 4)

| SYMBOL              | PARAMETER                       | CONDITIONS                                                                                                                    |   | MIN   | TYP       | MAX   | UNITS    |

|---------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------------------|---|-------|-----------|-------|----------|

| V <sub>REFBUF</sub> | Reference Buffer Output Voltage | V <sub>REFIN</sub> = 2.048V                                                                                                   |   | 4.088 | 4.096     | 4.104 | V        |

|                     | REFBUF Input Voltage Range      | (REFBUF Overdriven) (Notes 5, 9)                                                                                              |   | 2.5   |           | 5     | V        |

|                     | REFBUF Output Impedance         | V <sub>REFIN</sub> = 0V (Buffer Disabled)                                                                                     |   |       | 13        |       | kΩ       |

| I <sub>REFBUF</sub> | REFBUF Load Current             | V <sub>REFBUF</sub> = 5V (REFBUF Overdriven) (Notes 9, 12)<br>V <sub>REFBUF</sub> = 5V, Nap Mode (REFBUF Overdriven) (Note 9) | • |       | 1<br>0.38 | 1.2   | mA<br>mA |

# **DIGITAL INPUTS AND DIGITAL OUTPUTS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. (Note 4)

| SYMBOL            | PARAMETER                   | CONDITIONS                               |   | MIN                    | ТҮР | MAX                    | UNITS |

|-------------------|-----------------------------|------------------------------------------|---|------------------------|-----|------------------------|-------|

| V <sub>IH</sub>   | High Level Input Voltage    |                                          | • | 0.8 • OV <sub>DD</sub> |     |                        | V     |

| V <sub>IL</sub>   | Low Level Input Voltage     |                                          | • |                        |     | 0.2 • OV <sub>DD</sub> | V     |

| I <sub>IN</sub>   | Digital Input Current       | V <sub>IN</sub> = 0V to 0V <sub>DD</sub> | • | -10                    |     | 10                     | μA    |

| CIN               | Digital Input Capacitance   |                                          |   |                        | 5   |                        | pF    |

| V <sub>OH</sub>   | High Level Output Voltage   | I <sub>0</sub> = −500μA                  | • | 0V <sub>DD</sub> - 0.2 |     |                        | V     |

| V <sub>OL</sub>   | Low Level Output Voltage    | I <sub>0</sub> = 500μA                   | • |                        |     | 0.2                    | V     |

| I <sub>OZ</sub>   | Hi-Z Output Leakage Current | $V_{OUT} = 0V \text{ to } 0V_{DD}$       | • | -10                    |     | 10                     | μA    |

| ISOURCE           | Output Source Current       | $V_{OUT} = 0V$                           |   |                        | -10 |                        | mA    |

| I <sub>SINK</sub> | Output Sink Current         | V <sub>OUT</sub> = OV <sub>DD</sub>      |   |                        | 10  |                        | mA    |

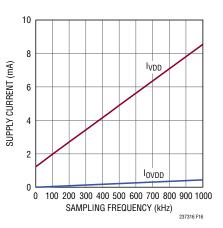

#### **POWER REQUIREMENTS** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . (Note 4)

| SYMBOL                                                  | PARAMETER                                                                  | CONDITIONS                                                                                                                         |   | MIN  | ТҮР                    | MAX              | UNITS                |

|---------------------------------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|---|------|------------------------|------------------|----------------------|

| V <sub>DD</sub>                                         | Supply Voltage                                                             |                                                                                                                                    | • | 4.75 | 5                      | 5.25             | V                    |

| OV <sub>DD</sub>                                        | Supply Voltage                                                             |                                                                                                                                    | • | 1.71 |                        | 5.25             | V                    |

| IVDD<br>IOVDD<br>I <sub>NAP</sub><br>I <sub>SLEEP</sub> | Supply Current<br>Supply Current<br>Nap Mode Current<br>Sleep Mode Current | 1Msps Sample Rate1Msps Sample Rate ( $C_L = 20pF$ )Conversion Done ( $I_{VDD} + I_{OVDD}$ )Sleep Mode ( $I_{VDD} + I_{OVDD}$ )     | • |      | 8<br>0.7<br>1.25<br>60 | 11<br>1.5<br>120 | mA<br>mA<br>mA<br>μA |

| P <sub>D</sub>                                          | Power Dissipation<br>Nap Mode<br>Sleep Mode                                | 1Msps Sample Rate<br>Conversion Done (I <sub>VDD</sub> + I <sub>OVDD</sub> )<br>Sleep Mode (I <sub>VDD</sub> + I <sub>OVDD</sub> ) |   |      | 40<br>6.25<br>300      | 55<br>7.5<br>600 | mW<br>mW<br>µW       |

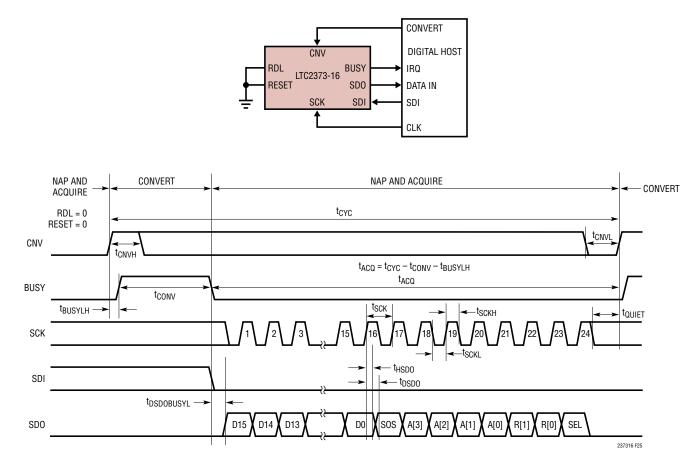

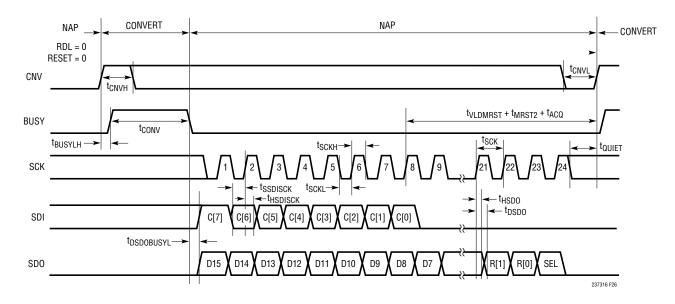

# **ADC TIMING CHARACTERISTICS** The • denotes the specifications which apply over the full operating

temperature range, otherwise specifications are at  $T_{A} = 25^{\circ}C$ . (Note 4)

| SYMBOL              | PARAMETER                             | CONDITIONS                                           |   | MIN | ТҮР | MAX | UNITS |

|---------------------|---------------------------------------|------------------------------------------------------|---|-----|-----|-----|-------|

| f <sub>SMPL</sub>   | Maximum Sampling Frequency            |                                                      | • |     |     | 1   | Msps  |

| t <sub>CONV</sub>   | Conversion Time                       |                                                      | • | 460 |     | 527 | ns    |

| t <sub>ACQ</sub>    | Acquisition Time                      | $t_{ACQ} = t_{CYC} - t_{CONV} - t_{BUSYLH}$ (Note 6) | • | 460 |     |     | ns    |

| t <sub>CYC</sub>    | Time Between Conversions              |                                                      | • | 1   |     |     | μs    |

| t <sub>CNVH</sub>   | CNV High Time                         |                                                      | • | 20  |     |     | ns    |

| t <sub>CNVL</sub>   | Minimum Low Time for CNV              | (Note 13)                                            | • | 20  |     |     | ns    |

| t <sub>BUSYLH</sub> | CNV↑ to BUSY↑ Delay                   | C <sub>L</sub> = 20pF                                | • |     |     | 13  | ns    |

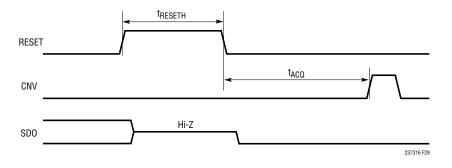

| tRESETH             | RESET Pulse Width                     |                                                      | • | 200 |     |     | ns    |

| t <sub>QUIET</sub>  | SCK, SDI and RDL Quiet Time from CNV↑ | (Note 6)                                             | • | 20  |     |     | ns    |

## **ELECTRICAL CHARACTERISTICS**

temperature range, otherwise specifications are at  $T_A = 25$ °C. (Note 4)

| t <sub>SCK</sub>       | SCK Period                                                                               | (Notes 13, 14)                                                                                                                            | • | 10 |     |                 | ns             |

|------------------------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|---|----|-----|-----------------|----------------|

| t <sub>SCKH</sub>      | SCK High Time                                                                            |                                                                                                                                           | • | 4  |     |                 | ns             |

| t <sub>SCKL</sub>      | SCK Low Time                                                                             |                                                                                                                                           | • | 4  |     |                 | ns             |

| t <sub>SSDISCK</sub>   | SDI Setup Time From SCK↑                                                                 | (Note 13)                                                                                                                                 | • | 4  |     |                 | ns             |

| t <sub>HSDISCK</sub>   | SDI Hold Time From SCK↑                                                                  | (Note 13)                                                                                                                                 | • | 1  |     |                 | ns             |

| t <sub>DSD0</sub>      | SDO Data Valid Delay from SCK↑                                                           | $\begin{array}{l} C_L = 20 p F, \ 0 V_{DD} = 5.25 V \\ C_L = 20 p F, \ 0 V_{DD} = 2.5 V \\ C_L = 20 p F, \ 0 V_{DD} = 1.71 V \end{array}$ | • |    |     | 7.5<br>8<br>9.5 | ns<br>ns<br>ns |

| t <sub>HSD0</sub>      | SDO Data Remains Valid Delay from SCK↑                                                   | C <sub>L</sub> = 20pF (Note 6)                                                                                                            | • | 1  |     |                 | ns             |

| t <sub>DSDOBUSYL</sub> | SDO Data Valid Delay from BUSY↓                                                          | C <sub>L</sub> = 20pF (Note 6)                                                                                                            | • |    |     | 5               | ns             |

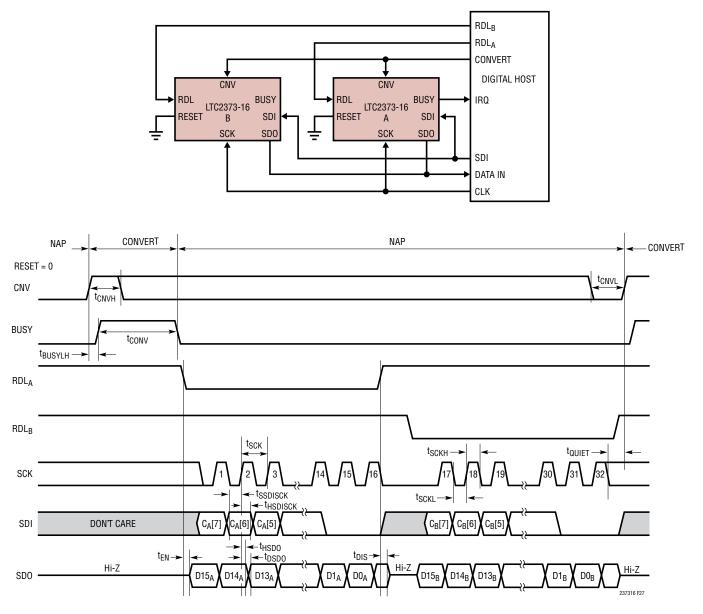

| t <sub>EN</sub>        | Bus Enable Time After RDL↓                                                               | (Note 13)                                                                                                                                 | • |    |     | 16              | ns             |

| t <sub>DIS</sub>       | Bus Relinquish Time After RDL↑                                                           | (Note 13)                                                                                                                                 | • |    |     | 13              | ns             |

| t <sub>WAKE</sub>      | REFBUF Wake-Up Time                                                                      | $C_{\text{REFBUF}} = 47 \mu F, C_{\text{REFIN}} = 0.1 \mu F$                                                                              |   |    | 200 |                 | ms             |

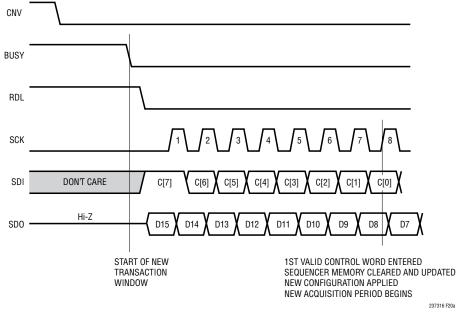

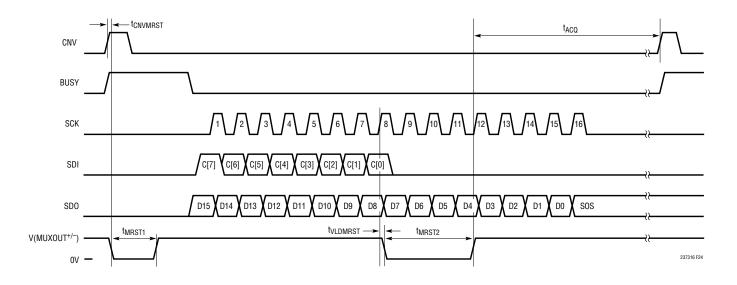

| t <sub>CNVMRST</sub>   | CNV↑ to MUX Starts Resetting Delay                                                       |                                                                                                                                           | • |    |     | 38              | ns             |

| t <sub>MRST1</sub>     | MUX Reset Time During Conversion                                                         |                                                                                                                                           | • |    |     | 36              | ns             |

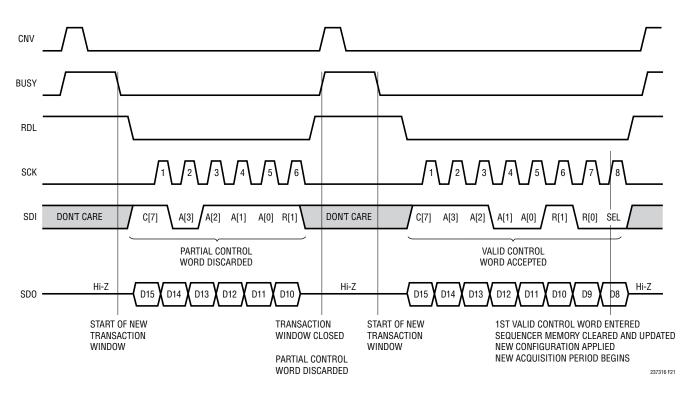

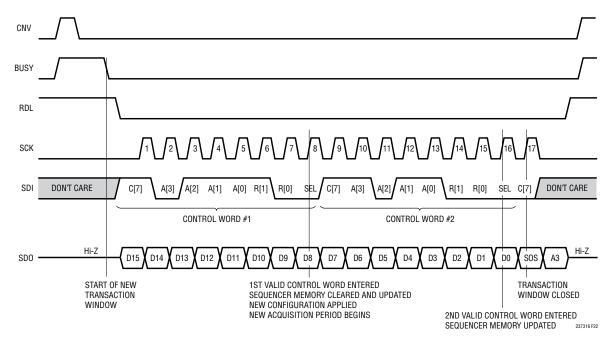

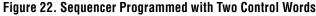

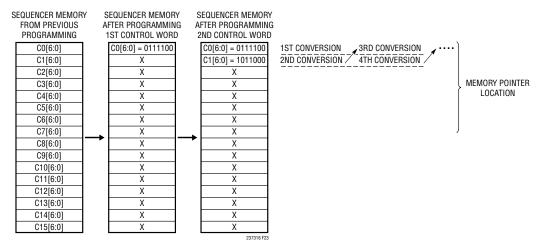

| t <sub>VLDMRST</sub>   | 8th SCK↑ to MUX Starts Resetting Delay After<br>Programming 1st Valid Configuration Word |                                                                                                                                           | • |    |     | 40              | ns             |

| t <sub>MRST2</sub>     | MUX Reset Time During Acquisition After<br>Programming 1st Valid Configuration Word      |                                                                                                                                           | • |    |     | 42              | ns             |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: All voltage values are with respect to ground.

**Note 3:** When these pin voltages are taken below ground or above  $V_{DD}$  or  $OV_{DD}$ , they will be clamped by internal diodes. This product can handle input currents up to 100mA below ground or above  $V_{DD}$  or  $OV_{DD}$  without latchup.

Note 4:  $V_{DD}$  = 5V,  $OV_{DD}$  = 2.5V,  $f_{SMPL}$  = 1MHz, REFIN = 2.048V unless otherwise noted.

Note 5: Recommended operating conditions.

Note 6: Guaranteed by design, not subject to test.

**Note 7:** Integral nonlinearity is defined as the deviation of a code from a straight line passing through the actual endpoints of the transfer curve. The deviation is measured from the center of the quantization band.

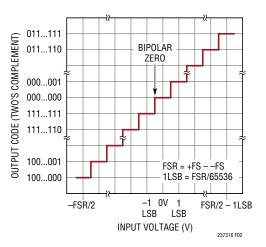

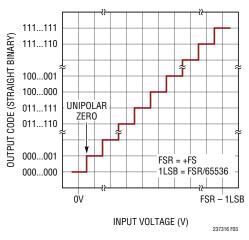

**Note 8:** Fully differential zero-scale error is the offset voltage measured from –0.5LSB when the output code flickers between 0111 1111 1111 1111 and 1000 0000 0000 0000 in straight binary format and 0000 0000 0000 0000 0000 0000 and 1111 1111 1111 1111 in two's complement format. Unipolar zero-scale error is the offset voltage measured from 0.5LSB when

the output code flickers between 0000 0000 0000 0000 and 0000 0000 0000 0001. Bipolar zero-scale error is the offset voltage measured from -0.5LSB when the output code flickers between 0000 0000 0000 0000 and 1111 1111 1111 1111. Fully differential full-scale error is the worst-case deviation of the first and last code transitions from ideal and includes the effect of offset error. Unipolar full-scale error is the deviation of the last code transition from the ideal and includes the effect of offset error. Bipolar full-scale error is the worst-case deviation of the first and last code transitions from ideal and includes the effect of offset error.

The • denotes the specifications which apply over the full operating

**Note 9:** When REFBUF is overdriven, the internal reference buffer must be turned off by setting REFIN = 0V.

**Note 10:** All specifications in dB are referred to a full-scale  $\pm V_{REFBUF}$  (fully differential), 0V to  $V_{REFBUF}$  (pseudo-differential unipolar), or  $\pm V_{REFBUF}/2$  (pseudo-differential bipolar) input.

**Note 11:** Temperature coefficient is calculated by dividing the maximum change in output voltage by the specified temperature range.

**Note 12:**  $f_{SMPL} = 1MHz$ ,  $I_{REFBUF}$  varies proportionally with sample rate. **Note 13:** Parameter tested and guaranteed at  $OV_{DD} = 1.71V$ ,  $OV_{DD} = 2.5V$  and  $OV_{DD} = 5.25V$ .

Note 14:  $t_{SCK}$  of 10ns maximum allows a shift clock frequency up to 100MHz for rising edge capture.

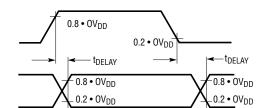

Figure 1. Voltage Levels for Timing Specifications

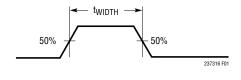

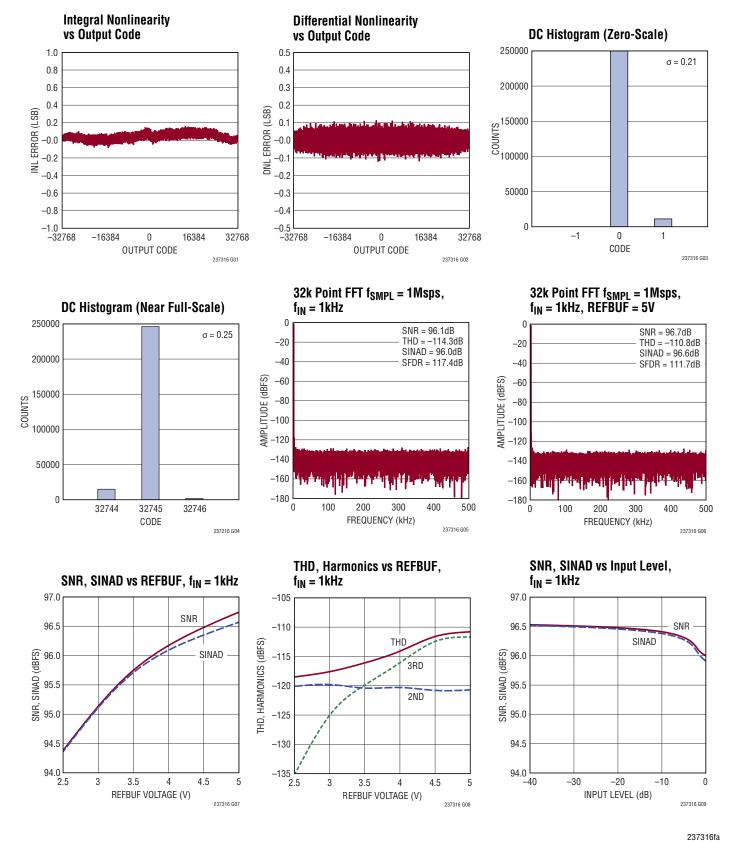

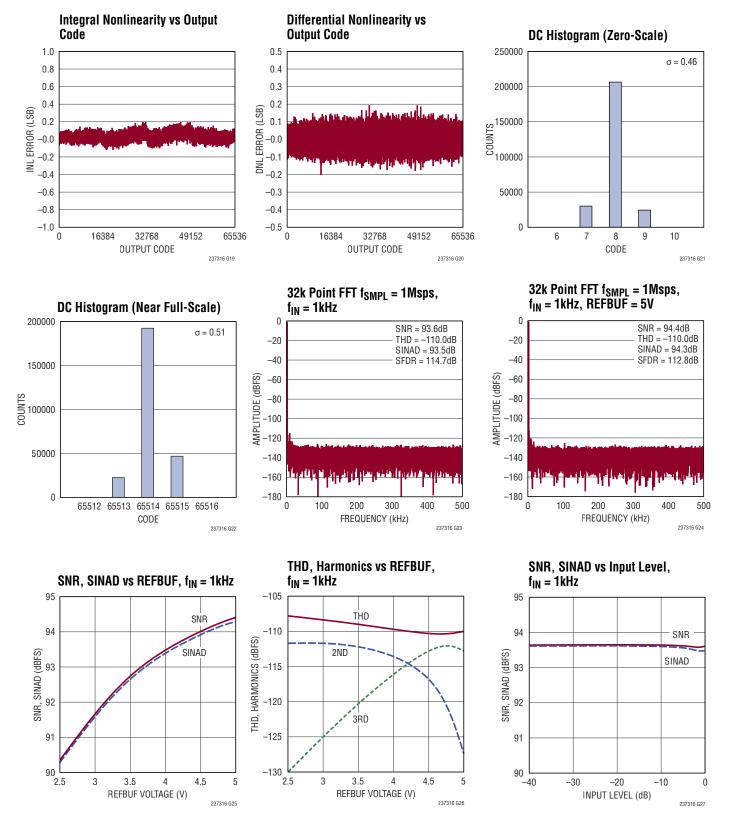

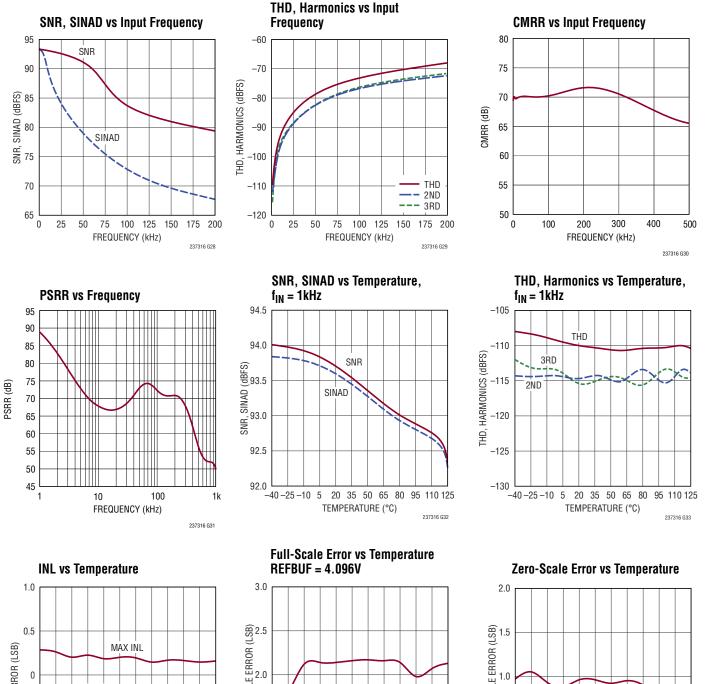

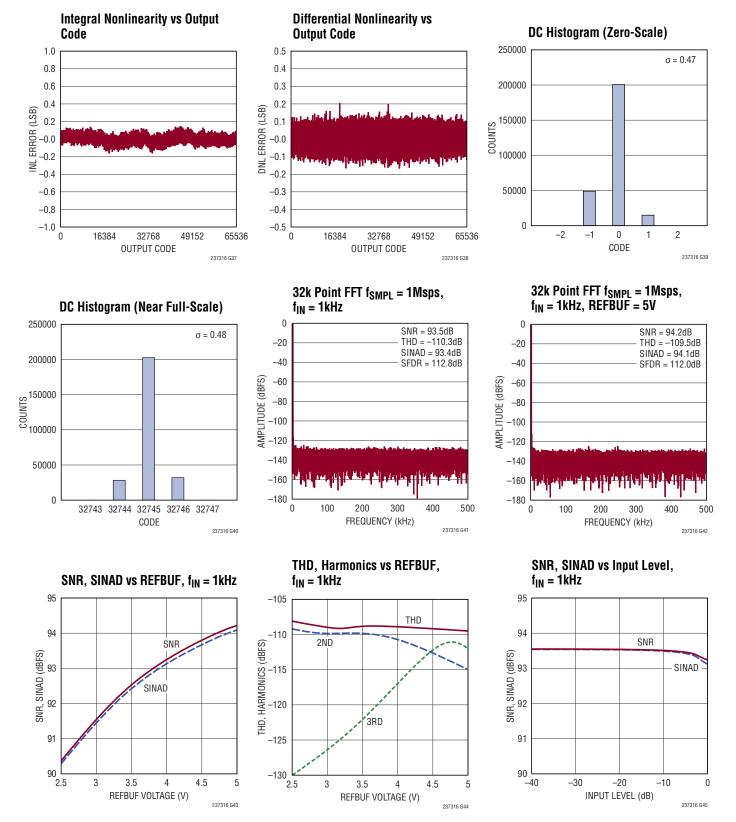

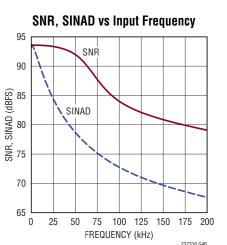

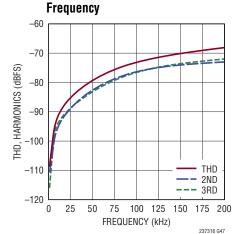

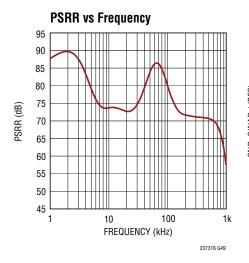

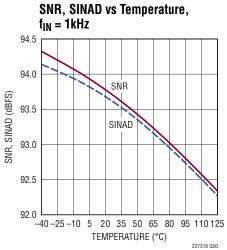

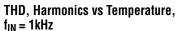

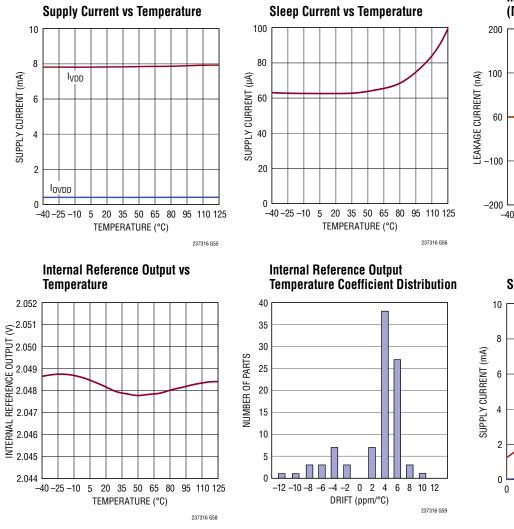

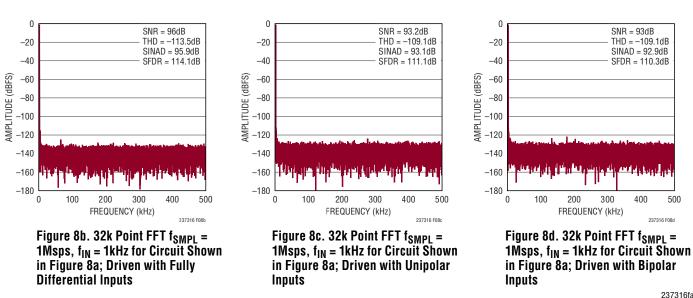

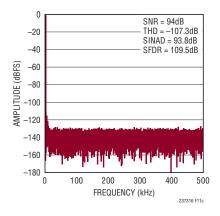

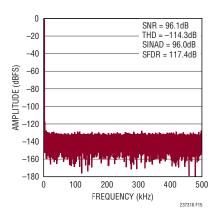

# **TYPICAL PERFORMANCE CHARACTERISTICS** Fully Differential Range, $V_{CM} = 2.048V$ , $f_{SMPL} = 1Msps$ , unless otherwise noted.

$T_A = 25^{\circ}C, V_{DD} = 5V, OV_{DD} = 2.5V, REFIN = 2.048V,$

### **TYPICAL PERFORMANCE CHARACTERISTICS** Fully Differential Range, $V_{CM} = 2.048V$ , $f_{SMPL} = 1Msps$ , unless otherwise noted. $T_A = 25^{\circ}C, V_{DD} = 5V, OV_{DD} = 2.5V, REFIN = 2.048V,$

**PSRR vs Frequency** 95 90 85 80 75 PSRR (dB) 70 65 60 55 50 45 10 100 1k 1 FREQUENCY (kHz) 237316 G13

$f_{IN} = 1 kHz$

SNR, SINAD vs Temperature,

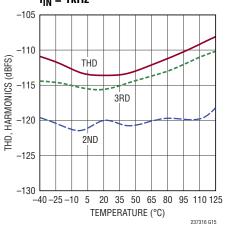

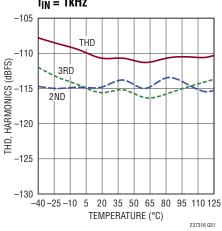

THD, Harmonics vs Temperature,  $f_{IN} = 1 kHz$

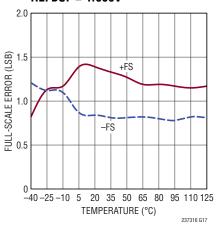

**Full-Scale Error vs Temperature** REFBUF = 4.096V

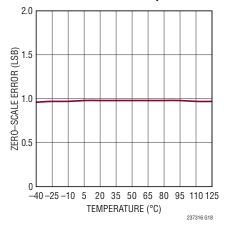

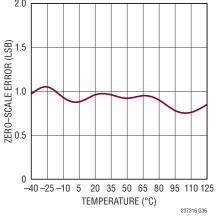

Zero-Scale Error vs Temperature

237316fa

# **TYPICAL PERFORMANCE CHARACTERISTICS** Pseudo-Differential Unipolar Range, f<sub>SMPL</sub> = 1Msps, unless otherwise noted.

$T_A = 25^{\circ}C$ ,  $V_{DD} = 5V$ ,  $OV_{DD} = 2.5V$ , REFIN = 2.048V,

### **TYPICAL PERFORMANCE CHARACTERISTICS** Pseudo-Differential Unipolar Range, f<sub>SMPL</sub> = 1Msps, unless otherwise noted. $T_A = 25^{\circ}C, V_{DD} = 5V, OV_{DD} = 2.5V, REFIN = 2.048V,$

### **TYPICAL PERFORMANCE CHARACTERISTICS** Pseudo-Differential Bipolar Range, f<sub>SMPL</sub> = 1Msps, unless otherwise noted. $T_A = 25^{\circ}C, V_{DD} = 5V, OV_{DD} = 2.5V, REFIN = 2.048V,$

12

237316fa

### **TYPICAL PERFORMANCE CHARACTERISTICS** Pseudo-Differential Bipolar Range, f<sub>SMPL</sub> = 1Msps, unless otherwise noted. $T_A = 25^{\circ}C, V_{DD} = 5V, OV_{DD} = 2.5V, REFIN = 2.048V,$

THD, Harmonics vs Input

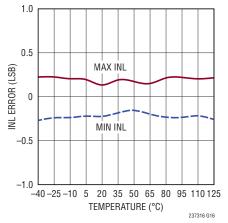

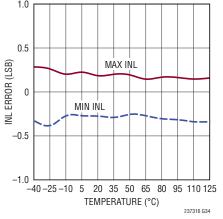

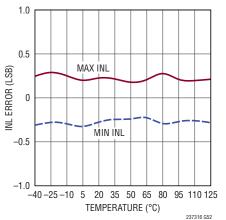

**INL vs Temperature**

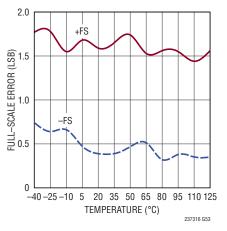

**Full-Scale Error vs Temperature** REFBUF = 4.096V

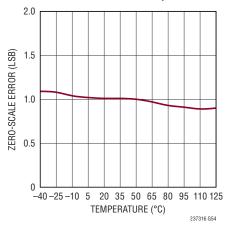

**Zero-Scale Error vs Temperature**

237316fa

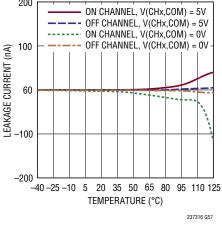

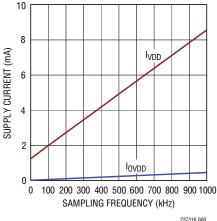

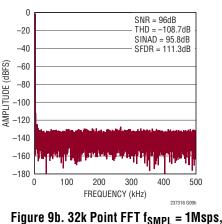

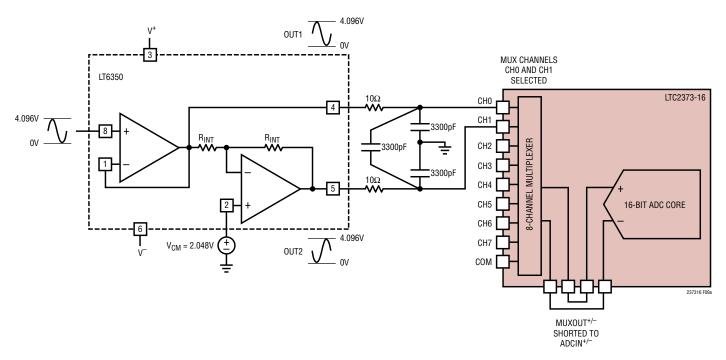

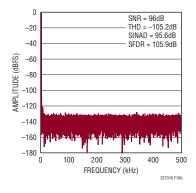

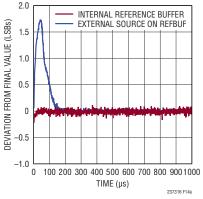

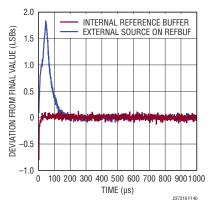

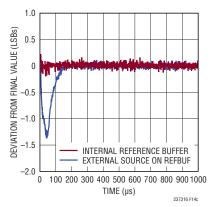

# **TYPICAL PERFORMANCE CHARACTERISTICS** $T_A = 25^{\circ}C$ , $V_{DD} = 5V$ , $0V_{DD} = 2.5V$ , REFIN = 2.048V, $f_{SMPL} = 1Msps$ , unless otherwise noted.

SFDR = 107.3dB

$f_{IN} = 100 \text{kHz}$

Crosstalk FFT (AC Crosstalk-

0

-20

-40

-60

-80

-100

-120

-140

-160

-180

0

100

200

FREQUENCY (kHz)

300

400

500

327316 661

AMPLITUDE (dBFS)

**Channel Adjacent to MUXOUT)**

#### Input Leakage Current vs Temperature (MUXOUT<sub>±</sub> Shorted to ADCIN<sub>±</sub>)

**Supply Current vs Sampling Rate**

0 SFDR = 127dB  $f_{IN} = 100 \text{kHz}$ -20 -40 AMPLITUDE (dBFS) -60 -80 -100 -120 -140-160-180 100 200 300 0 400 500 FREQUENCY (kHz) 237316 662

Crosstalk FFT (AC Crosstalk-**Channel NOT Adjacent to MUXOUT)**

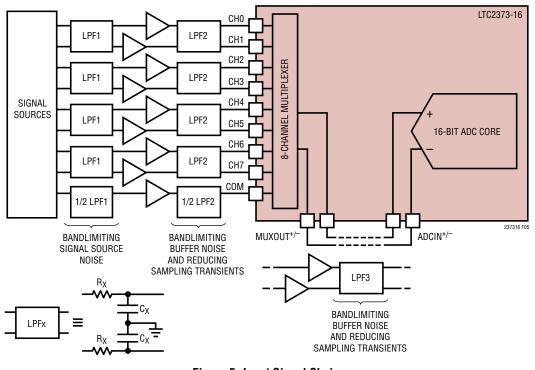

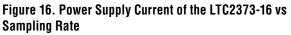

# PIN FUNCTIONS

**CHO to CH7 (Pins 1, 2, 7, 8, 9, 10, 31 and 32):** Analog Inputs. CHO to CH7 can be configured as single-ended inputs relative to COM, or as pairs of differential input channels. See the Analog Input Multiplexer section. Unused analog inputs should be tied to a DC voltage within the analog input voltage range of (GND – 0.3V) to ( $V_{DD}$  + 0.3V) as specified in Absolute Maximum Ratings.

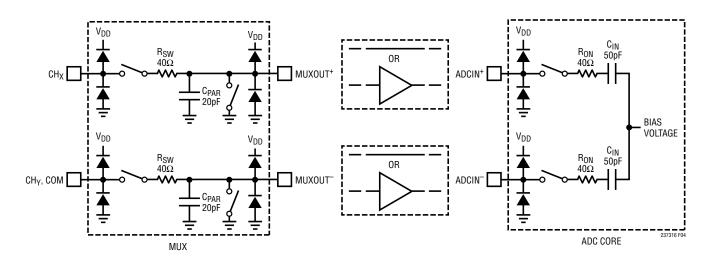

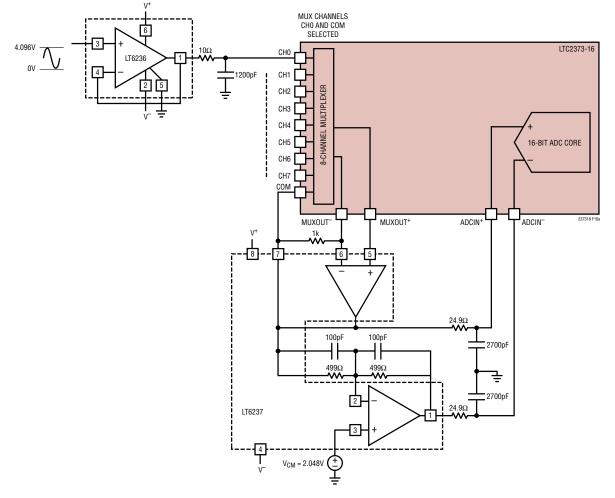

**MUXOUT<sup>+</sup>**, **MUXOUT<sup>-</sup>** (**Pin 3**, **Pin 6**): Analog Output Pins of MUX.

ADCIN<sup>+</sup>, ADCIN<sup>-</sup> (Pin 4, Pin 5): Analog Input Pins of ADC Core.

**GND (Pins 11, 14, 15, 17, 23, 26, 27 and Exposed Pad Pin 33)**: Ground.

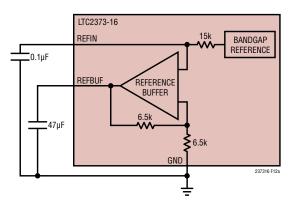

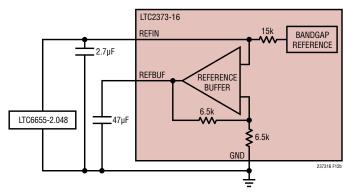

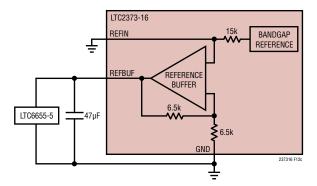

**REFBUF (Pin 12):** Reference Buffer Output. An onboard buffer nominally outputs 4.096V to this pin. This pin is referred to GND and should be decoupled closely to the pin with a  $47\mu$ F ceramic capacitor. The internal buffer driving this pin may be disabled by grounding its input at REFIN. Once the buffer is disabled, an external reference may overdrive this pin in the range of 2.5V to 5V. A resistive load greater than 500k can be placed on the reference buffer output.

**REFIN (Pin 13):** Reference Output/Reference Buffer Input. An onboard bandgap reference nominally outputs 2.048V at this pin. Bypass this pin with a  $0.1\mu$ F ceramic capacitor to GND to limit the reference output noise. If more accuracy is desired, this pin may be overdriven by an external reference in the range of 1.25V to 2.4V.

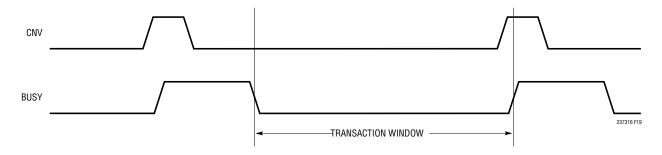

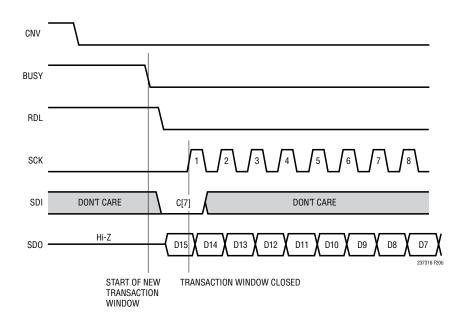

**CNV (Pin 16):** Convert Input. A rising edge on this input powers up the part and initiates a new conversion. Logic levels are determined by OV<sub>DD</sub>.

**RDL (Pin 18):** Read Low Input. When RDL is low, the serial data I/O bus is enabled. When RDL is high, the serial data I/O bus becomes Hi-Z. RDL also gates the external shift clock. Logic levels are determined by OV<sub>DD</sub>.

**BUSY (Pin 19):** BUSY Indicator. Goes high at the start of a new conversion and returns low when the conversion has finished. Logic levels are determined by OV<sub>DD</sub>.

**SDI (Pin 20):** Serial Data Input. Data provided on this pin in synchrony with SCK can be used to program the MUX channel configuration, converter input range and digital gain compression setting via the sequencer. Input data on SDI is latched on rising edges of SCK when the serial data I/O bus is enabled. Logic levels are determined by OV<sub>DD</sub>.

**SCK (Pin 21):** Serial Data Clock Input. When the serial data I/O bus is enabled, the conversion result followed by configuration information is shifted out at SDO on the rising edges of this clock MSB first. Serial input data is latched on the rising edges of this clock at SDI. Logic levels are determined by OV<sub>DD</sub>.

**SDO (Pin 22):** Serial Data Output. The conversion result followed by configuration information is output on this pin on each rising edge of SCK MSB first when the serial data I/O bus is enabled. The output data format is determined by the converter operating mode. Logic levels are determined by  $OV_{DD}$ .

**RESET (Pin 24):** Reset Input. When this pin is brought high, the LTC2373-16 is reset. If this occurs during a conversion, the conversion is halted and the data bus becomes Hi-Z. Logic levels are determined by OV<sub>DD</sub>.

$OV_{DD}$  (Pin 25): I/O Interface Digital Power. The range of  $OV_{DD}$  is 1.71V to 5.25V. This supply is nominally set to the same supply as the host interface (1.8V, 2.5V, 3.3V, or 5V). Bypass  $OV_{DD}$  to GND with a 0.1µF capacitor.

$V_{DDLBYP}$  (Pin 28): 2.5V Supply Bypass Pin. The voltage on this pin is generated via an onboard regulator off of V<sub>DD</sub>. This pin must be bypassed with a 2.2µF ceramic capacitor to GND. Applying an external voltage to this pin can cause damage to the IC or improper operation.

$V_{DD}$  (Pin 29): 5V Power Supply. The range of  $V_{DD}$  is 4.75V to 5.25V. Bypass  $V_{DD}$  to GND with a 10µF ceramic capacitor.

**COM (Pin 30):** Common Input. This is the reference point for all single-ended inputs. It must be free of noise and connected to GND for unipolar conversions and REFBUF/2 for bipolar conversions. If unused, this input should be tied to a DC voltage within the analog input voltage range of (GND – 0.3V) to ( $V_{DD}$  + 0.3V) as specified in Absolute Maximum Ratings.

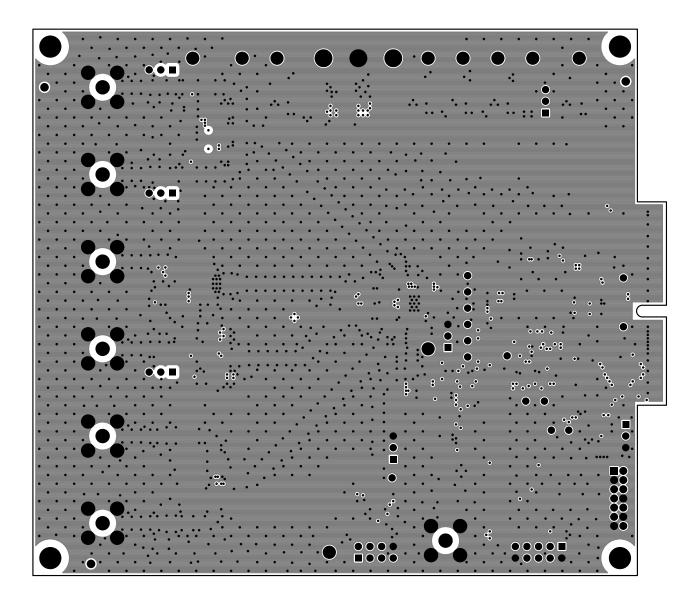

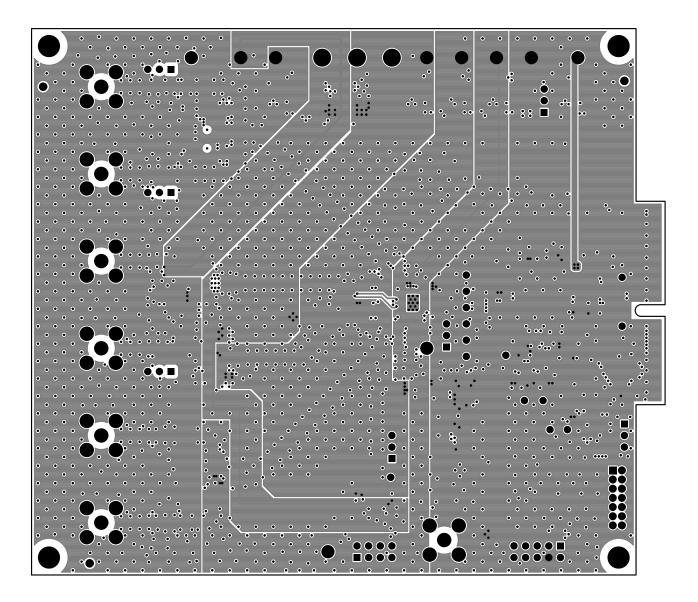

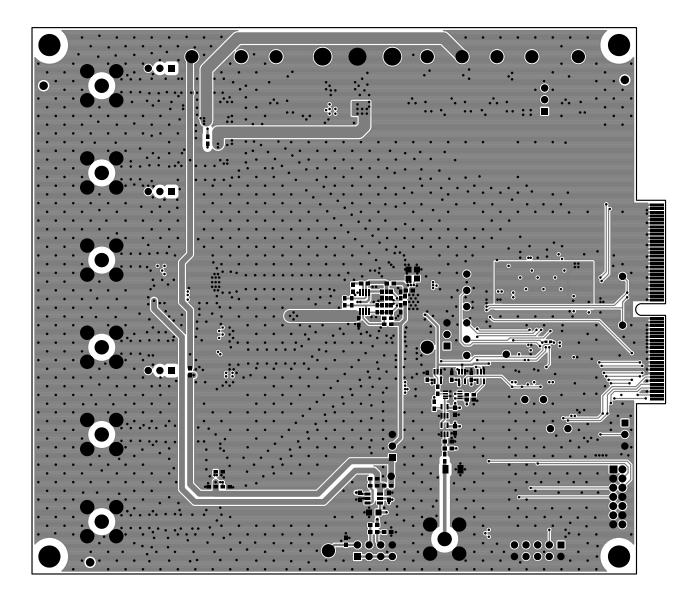

# FUNCTIONAL BLOCK DIAGRAM

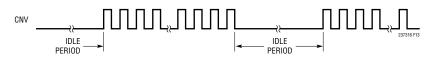

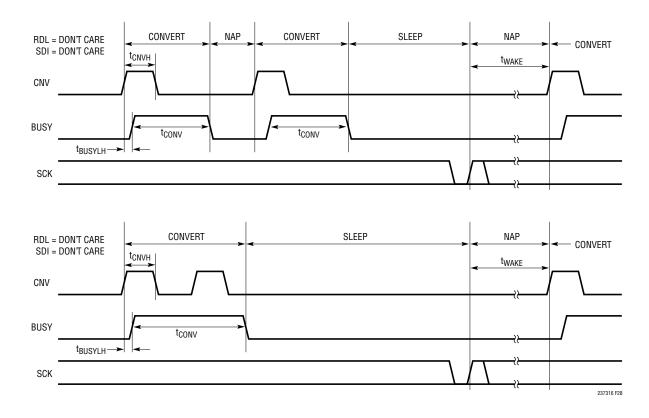

# TIMING DIAGRAM

|           |        | Typical Conversion and Serial Interface Timing                                          |             |

|-----------|--------|-----------------------------------------------------------------------------------------|-------------|

| RESET = 0 | N<br>I |                                                                                         | N + 1       |

| CNV       |        |                                                                                         |             |

|           |        |                                                                                         |             |

| BUSY      |        | NAP                                                                                     |             |

| BUSY      |        | IVAF                                                                                    | -           |

| SCK       |        |                                                                                         |             |

| 50K       |        |                                                                                         |             |

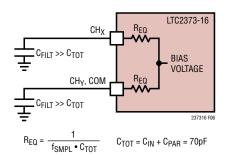

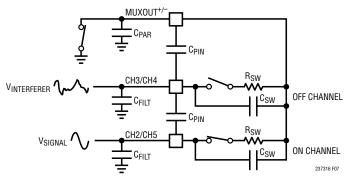

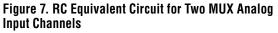

|           |        |                                                                                         |             |