# 10/100BASE-TX Octal-⊕™ Transceiver

#### **GENERAL DESCRIPTION**

The BCM5238 is an octal 10/100BASE-TX transceiver for Fast Ethernet switches. The device contains eight full-duplex 10BASE-T/100BASE-TX Fast Ethernet transceivers, each of which performs all of the physical layer interface functions for 10BASE-T Ethernet on Category 3, 4 or 5 unshielded twisted-pair (UTP) cable and 100BASE-TX Fast Ethernet on Category 5 UTP cable. Pseudo-100BASE-FX mode is supported through external fiber-optic tranceivers.

The BCM5238 is a highly integrated solution using 0.18-micron technology, combining digital adaptive equalizers, ADCs, phase locked loops, line drivers, encoders, decoders and all the required support circuitry into a single monolithic CMOS chip. The BCM5238 complies with the IEEE 802.3 specification, including the auto-negotiation subsections.

The BCM5238 design results in robust performance over a broad range of operating scenarios. Problems inherent to mixed-signal implementations, such as analog offset and on-chip noise, are eliminated by employing field-proven digital adaptive equalization and digital clock recovery techniques.

#### **FEATURES**

- 10BASE-T/100BASE-TX IEEE 802.3u compliant

- Single-chip octal physical interface—SMII to magnetics

- Option—Source Synchronous SMII (SSSMII)

- Fully integrated digital adaptive equalizers

- 125-MHz clock generator and timing recovery

- On-chip multimode transmit waveshaping

- Edge-rate control eliminates external filters

- HP auto-MDIX

- Cable length Indication

- · Cable noise level Indication

- IEEE 802.3u-compliant auto-negotiation

- Shared MII management interface up to 25 Mbps

- Programmable serial LED pins

- Programmable parallel LED pins

- Interrupt output capability

- · Loopback mode for diagnostics

- IEEE 1149.1 (JTAG) and NAND-chain ICT support

- Low-power dual-supply 2.5V/1.8V CMOS technology

- Compatible with 3.3 V I/O

- 128 MQFP and 256-pin FBGA package

#### **APPLICATIONS**

Fast Ethernet switches

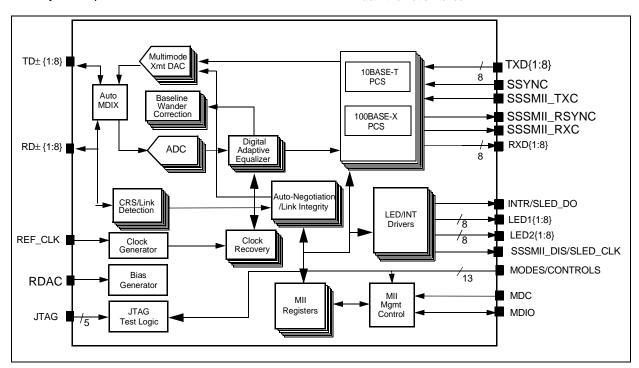

Figure 1: Functional Block Diagram

### **REVISION HISTORY**

| Revision        | Date    | Change description |

|-----------------|---------|--------------------|

| 5238-DS03-405-R | 1/31/03 | Initial Release.   |

Broadcom Corporation

P.O. Box 57013

16215 Alton Parkway

Irvine, California 92619-7013

© 2003 by Broadcom Corporation

All rights reserved

Printed in the U.S.A.

Broadcom<sup>®</sup> and the pulse logo are registered trademarks of Broadcom Corporation and/or its subsidiaries in the United States and certain other countries. All other trademarks are the property of their respective owners.

This data sheet (including, without limitation, the Broadcom component(s) identified herein) is not designed, intended, or certified for use in any military, nuclear, medical, mass transportation, aviation, navigations, pollution control, hazardous substances management, or other high risk application. BROADCOM PROVIDES THIS DATA SHEET "ASIS", WITHOUT WARRANTY OF ANY KIND. BROADCOM DISCLAIMS ALL WARRANTIES, EXPRESSED AND IMPLIED, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, AND NON-INFRINGEMENT.

# **TABLE OF CONTENTS**

| Section 1: Functional Description           | 1   |

|---------------------------------------------|-----|

| Overview                                    | 1   |

| Encoder/Decoder                             | 1   |

| Link Monitor                                | 2   |

| Carrier Sense                               | 2   |

| Auto-negotiation                            | 3   |

| Digital Adaptive Equalizer                  | 3   |

| ADC                                         | 3   |

| Digital Clock Recovery/generator            | 3   |

| Multimode Transmit DAC                      | 4   |

| Stream Cipher                               | 4   |

| MII Management                              | 4   |

| SMII Interface                              | 4   |

| Source Synchronous SMII (SSSMII) Interface  | 5   |

| Interrupt mode                              | 5   |

| Section 2: Hardware Signal Definition Table | 7   |

| •                                           |     |

| Section 3: Pinout Diagram                   | 14  |

| Section 4: Operational Description          | 16  |

| Resetting the BCM5238                       | 16  |

| PHY Address                                 |     |

| Loopback Mode                               |     |

| Full-duplex Mode                            |     |

| 10BASE-T Mode                               |     |

| Isolate Mode                                | 17  |

| Super Isolate Mode                          | 17  |

| Auto Power-Down Mode                        |     |

| Jumbo Packet Mode                           | 17  |

| Costion E. I. ED Diomley Output Made        | 4.0 |

| Section 5: LED Display Output Modes         |     |

| Description                                 | 10  |

| Serial LED Mode                             |     |

| Extended Parallel LED Mode                               | 23 |

|----------------------------------------------------------|----|

| Transmit and Receive LED Behavior                        | 24 |

| Transmit LED                                             | 24 |

| Receive LED                                              | 24 |

| Section 6: Register Summary                              | 25 |

| MII Management Interface: Register Programming           | 25 |

| MII Register Map Summary                                 | 26 |

| MII Status Register                                      | 31 |

| PHY Identifier Registers                                 | 32 |

| Auto-Negotiation Advertisement Register                  | 33 |

| 100BASE-X Auxiliary Control Register                     | 37 |

| 100BASE-X Auxiliary Status Register                      | 39 |

| 100BASE-X Receive Error Counter                          | 40 |

| 100BASE-X False Carrier Sense Counter                    | 40 |

| Auxiliary Control/Status Register                        | 41 |

| 10BASE-T Auxiliary Error and General Status Register     | 46 |

| Auxiliary Mode Register                                  | 47 |

| Auxiliary Multiple PHY Register                          | 48 |

| Broadcom Test Register                                   | 49 |

| Auxiliary Mode 4 (PHY 1 of 8) Register (Shadow Register) | 50 |

| Auxiliary Mode 4 (PHY 2 of 8) Register (Shadow Register) | 50 |

| Auxiliary Mode 4 (PHY 3 of 8) Register (Shadow Register) | 51 |

| Auxiliary Mode 4 (PHY 5 of 8) Register (Shadow Register) | 52 |

| Auxiliary Mode 4 (PHY 7 of 8) Register (Shadow Register) | 53 |

| Auxiliary Status 2 Register (Shadow Register)            | 54 |

| Auxiliary Status 3 Register (Shadow Register)            | 55 |

| Auxiliary Status 4 Register (Shadow Register)            | 56 |

| Section 7: Timing and AC Characteristics      | 57 |

|-----------------------------------------------|----|

| Section 8: Electrical Characteristics         | 60 |

| Section 9: Mechanical Information             | 62 |

| Section 10: Packaging Thermal Characteristics | 64 |

| Section 11: Application Examples              | 65 |

| Section 12: Ordering Information              | 67 |

# **LIST OF FIGURES**

| Figure 1: Functional Block Diagram                                   | i  |

|----------------------------------------------------------------------|----|

| Figure 2: BCM5238U Pin Diagram                                       | 14 |

| Figure 3: BCM5238B Pin Diagram                                       | 15 |

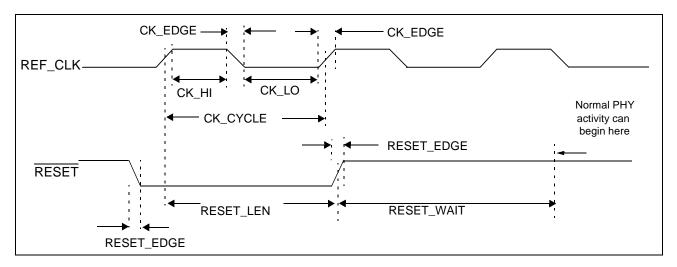

| Figure 4: Clock and Reset Timing                                     | 57 |

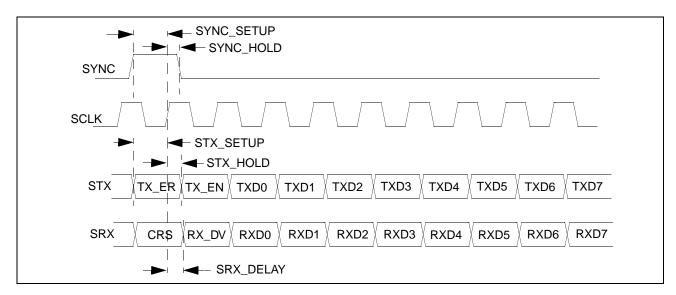

| Figure 5: SMII Timing                                                | 58 |

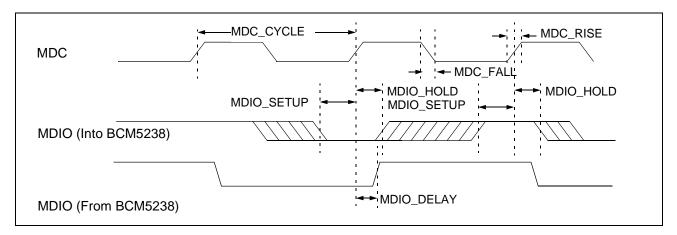

| Figure 6: Management Interface Timing                                | 59 |

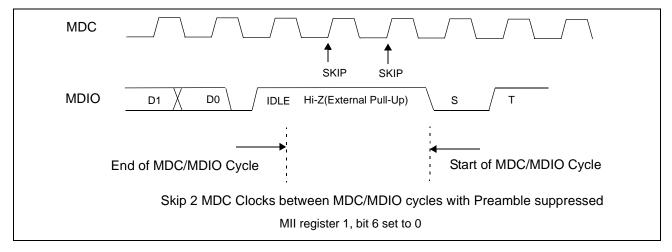

| Figure 7: Management Interface Timing (with Preamble Suppression on) | 59 |

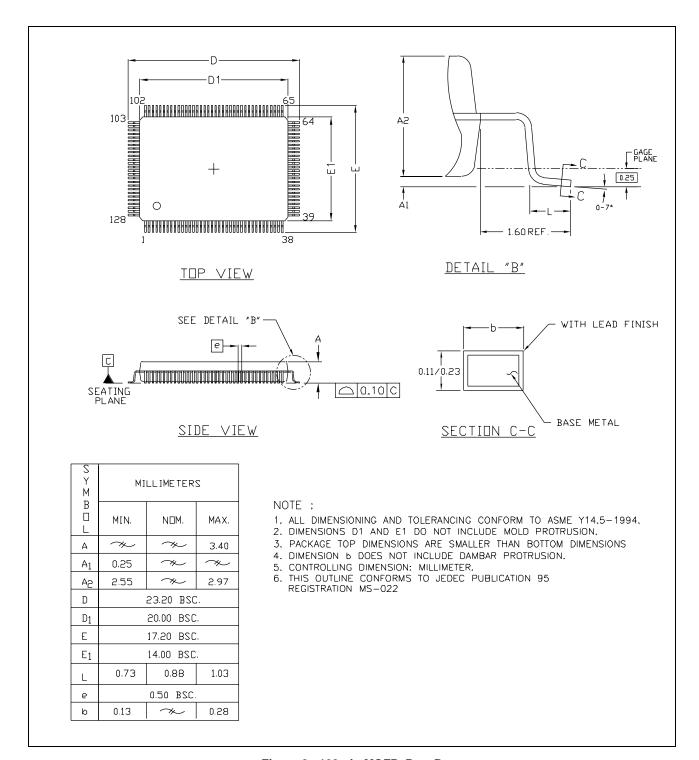

| Figure 8: 128-pin MQFP, Rev. B                                       | 62 |

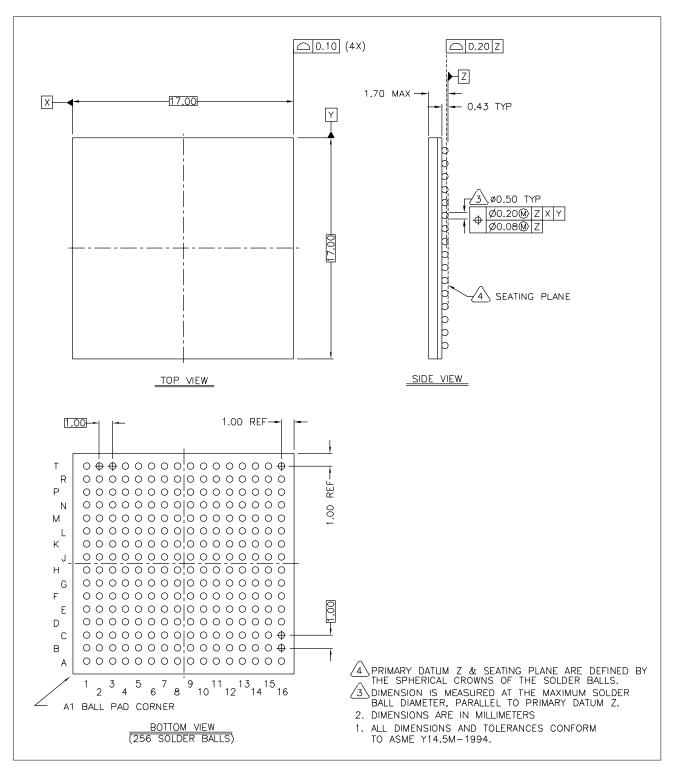

| Figure 9: 256-pin FBGA, Rev. A                                       | 63 |

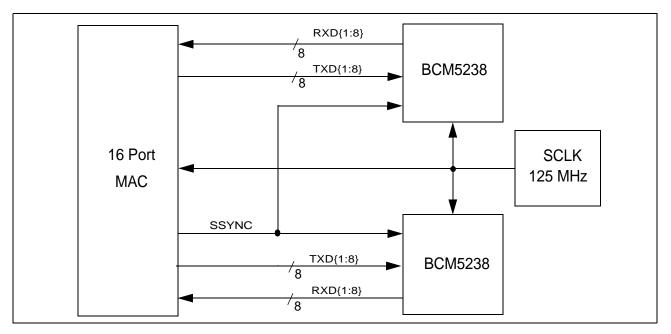

| Figure 10: SMII Application                                          | 65 |

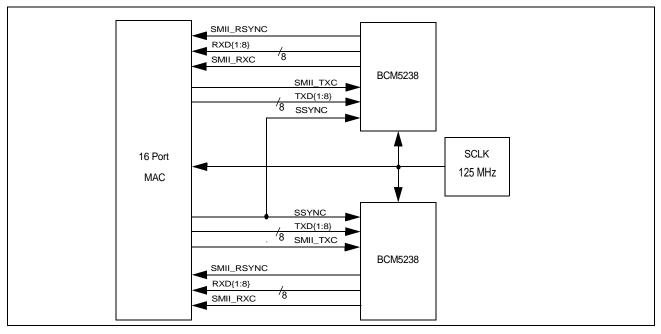

| Figure 11: SMII Application Using Source Synchronous Signals         | 65 |

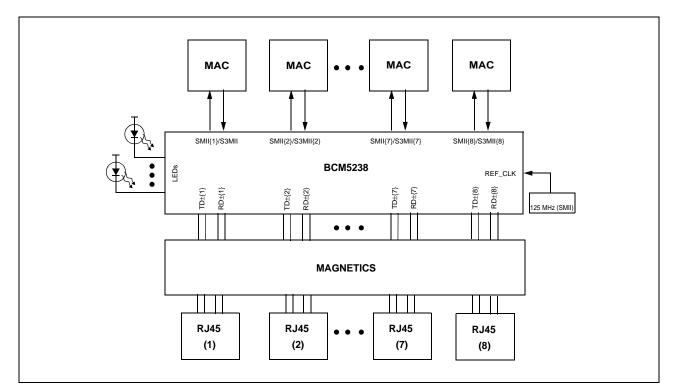

| Figure 12: Switch Application                                        | 66 |

# **LIST OF TABLES**

| Table 1: 4858 encoding                                                      | 1  |

|-----------------------------------------------------------------------------|----|

| Table 2: Pin Definitions                                                    | 7  |

| Table 3: Receive FIFO Size Select                                           | 18 |

| Table 4: Jumbo packet enable and descrambler lock timer                     | 18 |

| Table 5: Serial LED Mode Bit Framing                                        | 19 |

| Table 6: Serial Mode Bank 1 LED Selection                                   | 20 |

| Table 7: Serial Mode Bank 2 LED Selection                                   | 20 |

| Table 8: Serial Mode Bank 3 LED Selection                                   | 21 |

| Table 9: Serial Mode Bank 4 LED Selection                                   | 21 |

| Table 10: Serial Mode Bank 5 LED Selection                                  | 22 |

| Table 11: Serial Mode Bank 6 LED Selection                                  | 22 |

| Table 12: Parallel LED Mode LED1 Selection                                  | 23 |

| Table 13: Parallel LED Mode LED2 Selection                                  | 23 |

| Table 14: Extended Parallel LED Selection                                   | 24 |

| Table 15: MII management frame format                                       | 25 |

| Table 16: MII Register Map Summary                                          | 27 |

| Table 17: MII Shadow Register Map Summary (MII Register 1Fh, bit7 = 1)      | 29 |

| Table 18: MII Control register (Address 00d, 00h)                           | 30 |

| Table 19: MII Status register (Address 01d, 01h)                            | 31 |

| Table 20: PHY Identifier Registers (Addresses 02d and 03d, 02h and 03h)     | 32 |

| Table 21: Auto-Negotiation Advertisement Register (Address 04d, 04h)        | 33 |

| Table 22: Auto-Negotiation Link Partner Ability Register (Address 05d, 05h) | 34 |

| Table 23: Auto-Negotiation Expansion Register (Address 06d, 06h             | 35 |

| Table 24: Next Page Transmit Register (Address 07d, 07h)                    | 36 |

| Table 25: Next Page Transmit Register (Address 08d, 08h)                    | 37 |

| Table 26: 100-BASE-X Auxiliary Control register (Address 16d, 10h)          | 37 |

| Table 27: 100BASE-X Auxiliary Status Register (Address 17d, 11h)            | 39 |

| Table 28: 100BASE-X Receive Error Counter (Address 18d, 12h)                | 40 |

| Table 29: 100BASE-X False Carrier Sense Counter (Address 19d, 13h)          | 40 |

| Table 30: 100BASE-X Disconnect Counter (Address 20d, 14h)                   | 41 |

| Table 31: Auxiliary Control/Status Register (Address 24d, 18h)              | 41 |

| Table 32: Auxiliary Status Summary Register (Address 25d, 19h)              | 43 |

| Table 33: Interrupt Register (Address 26d, 1Ah)                                   | 44 |

|-----------------------------------------------------------------------------------|----|

| Table 34: Auxiliary Mode 2 Register (Address 27d, 1Bh)                            | 45 |

| Table 35: 10BASE-T Auxiliary Error and General Status Register (Address 28d, 1Ch) | 46 |

| Table 36: Auxiliary Mode Register (Address 29d, 1Dh)                              | 47 |

| Table 37: Auxiliary Multiple PHY Register (Address 30d, 1Eh)                      | 48 |

| Table 38: Broadcom Test Register (Address 31d, 1Fh)                               | 49 |

| Table 39: Auxiliary Mode 4 (PHY 1 of 8) Register (Shadow Register 26d, 1Ah)       | 50 |

| Table 40: Auxiliary Mode 4 (PHY 2 of 8) Register (Shadow Register 26d, 1Ah)       | 50 |

| Table 41: Auxiliary Mode 4 (PHY 3 of 8) Register (Shadow Register 26d, 1Ah)       | 51 |

| Table 42: Auxiliary Mode 4 (PHY 4 of 8) Register (Shadow Register 26d, 1Ah)       | 52 |

| Table 43: Auxiliary Mode 4 (PHY 5 of 8) Register (Shadow Register 26d, 1Ah)       | 52 |

| Table 44: Auxiliary Mode 4 (PHY 6 of 8) Register (Shadow Register 26d, 1Ah)       | 53 |

| Table 45: Auxiliary Mode 4 (PHY 7 of 8) Register (Shadow Register 26d, 1Ah)       | 53 |

| Table 46: Auxiliary Mode 4 (PHY 8 of 8) Register (Shadow Register 26d, 1Ah)       | 54 |

| Table 47: Auxiliary Status 2 Register (Shadow Register 27d, 1Bh)                  | 54 |

| Table 48: 100-TX Port Cable Length                                                | 54 |

| Table 49: Auxiliary Status 3 Register (Shadow Register 28d, 1Ch)                  | 55 |

| Table 50: Auxiliary Mode 3 Register (Shadow Register 29d, 1Dh)                    | 56 |

| Table 51: Current Receive FIFO Size                                               | 56 |

| Table 52: Auxiliary Status 4 Register (Shadow Register 30d, 1Eh)                  | 56 |

| Table 53: Clock Timing                                                            | 57 |

| Table 54: Reset Timing                                                            | 57 |

| Table 55: SMII Timing                                                             | 58 |

| Table 56: Auto-negotiation Timing                                                 | 58 |

| Table 57: LED Timing                                                              | 58 |

| Table 58: MII Management Data interface Timing                                    | 58 |

| Table 59: Absolute Maximum Ratings                                                | 60 |

| Table 60: Recommended Operating Conditions                                        | 60 |

| Table 61: Electrical Characteristics                                              | 60 |

| Table 62: ThetaJ <sub>A</sub> vs. Airflow for the BCM5238B Package                | 64 |

| Table 63: ThetaJ <sub>A</sub> vs. Airflow for the BCM5238U Package                | 64 |

## **Section 1: Functional Description**

#### **OVERVIEW**

The BCM5238 is a single-chip device containing eight independent Fast Ethernet transceivers. Each transceiver performs all of the physical layer interface functions for 100BASE-TX full-duplex or half-duplex Ethernet on Category 5 twisted-pair cable and 10BASE-T full-duplex or half-duplex Ethernet on Category 3, 4, or 5 cable.

The chip performs 4B5B, MLT3, NRZI, and Manchester encoding and decoding, clock and data recovery, stream cipher scrambling/descrambling, digital adaptive equalization, line transmission, carrier sense and link integrity monitor, auto-negotiation SMII and SSMII management functions. The BCM5238 may be connected to a MAC through the SMII or SSMII on one side and connects directly to the network media on the other side through isolation transformers. The BCM5238 is compliant with the IEEE 802.3 standard.

### **ENCODER/DECODER**

Document 5238-DS03-405-R

The BCM5238 transmits and receives a continuous data stream on twisted pair. When the transmit enable is asserted, data from the transmit data pins is encoded into 5-bit code-groups and inserted into the transmit data stream. The 4B5B encoding is shown in Table 1. The transmit packet is encapsulated by replacing the first two nibbles of preamble with a start of stream delimiter (J/K codes) and appending an end of stream delimiter (T/R codes) to the end of the packet. The transmitter repeatedly sends the idle code group between packets.

The encoded data stream is scrambled by a stream cipher block and then serialized and encoded into MLT3 signal levels. A multimode transmit DAC is used to drive the MLT3 data onto the twisted pair cable.

Following adaptive equalization, and clock recovery, the receive data stream is converted from MLT3 to serial NRZ data. The NRZ data is descrambled by the stream cipher block and then descrialized and aligned into 5-bit code groups.

The 5-bit code groups are decoded into 4-bit data nibbles, as shown in Table 1. The start of stream delimiter is replaced with preamble nibbles and the end of stream delimiter and idle codes are replaced with all zeros. The decoded data is driven onto the SMII receive data stream. When an invalid code group is detected in the data stream, the BCM5238 asserts the SMII RXER signal in the receive data stream. The chip also asserts RXER for several other error conditions which improperly terminate the data stream.

In 10BASE-T mode, Manchester encoding and decoding is performed on the data stream. The multimode transmit DAC performs pre-equalization for 100 meters of Category 3 cable.

Table 1: 4B5B encoding

| Name | 4B Code | 5B Code | Meaning |

|------|---------|---------|---------|

| 0    | 0000    | 11110   | Data 0  |

| 1    | 0001    | 01001   | Data 1  |

| 2    | 0010    | 10100   | Data 2  |

| 3    | 0011    | 10101   | Data 3  |

| 4    | 0100    | 01010   | Data 4  |

Broadcom Corporation

Table 1: 4B5B encoding (Cont.)

| Name | 4B Code           | 5B Code | Meaning                                          |

|------|-------------------|---------|--------------------------------------------------|

| 5    | 0101              | 01011   | Data 5                                           |

| 6    | 0110              | 01110   | Data 6                                           |

| 7    | 0111              | 01111   | Data 7                                           |

| 8    | 1000              | 10010   | Data 8                                           |

| 9    | 1001              | 10011   | Data 9                                           |

| A    | 1010              | 10110   | Data A                                           |

| В    | 1011              | 10111   | Data B                                           |

| С    | 1100              | 11010   | Data C                                           |

| D    | 1101              | 11011   | Data D                                           |

| E    | 1110              | 11100   | Data E                                           |

| F    | 1111              | 11101   | Data F                                           |

| I    | 0000 <sup>a</sup> | 11111   | Idle                                             |

| J    | 0101 <sup>a</sup> | 11000   | Start-of-stream delimiter, part 1                |

| K    | 0101 <sup>a</sup> | 10001   | Start-of-stream delimiter, part 2                |

| Т    | 0000 <sup>a</sup> | 01101   | End-of-stream delimiter, part 1                  |

| R    | 0000 <sup>a</sup> | 00111   | End-of-stream delimiter, part 2                  |

| Н    | 1000              | 00100   | Transmit error (used to force signalling errors) |

| V    | 0111              | 00000   | Invalid Code                                     |

| V    | 0111              | 00001   | Invalid Code                                     |

| V    | 0111              | 00010   | Invalid Code                                     |

| V    | 0111              | 00011   | Invalid Code                                     |

| V    | 0111              | 00101   | Invalid Code                                     |

| V    | 0111              | 00110   | Invalid Code                                     |

| V    | 0111              | 01000   | Invalid Code                                     |

| V    | 0111              | 01100   | Invalid Code                                     |

| V    | 0111              | 10000   | Invalid Code                                     |

| V    | 0111              | 11001   | Invalid Code                                     |

a. Treated as invalid code (mapped to 0111) when received in data field.

### **LINK MONITOR**

In 100BASE-TX mode, receive signal energy is detected by monitoring the receive pair for transitions in the signal level. Signal levels are qualified using squelch detect circuits. When no signal or certain invalid signals are detected on the receive pair, the link monitor enters and remains in the Link Fail state where only idle codes are transmitted. When a valid signal is detected on the receive pair for a minimum period of time, the link monitor enters the Link Pass state and the transmit and receive functions are enabled.

In 10BASE-T mode, a link-pulse detection circuit constantly monitors the RD± pins for the presence of valid link pulses.

## CARRIER SENSE

In DTE mode, the carrier sense and receive data valid signals are multiplexed on the same pin. The carrier sense is asserted asynchronously on CRS\_DV as soon as valid activity is detected in the receive data stream. Loss of carrier shall result in

the deassertion of CRS\_DV synchronous to the cycle of REF\_CLK which presents the first di-bit of a nibble onto RXD. IF the PHY has additional bits to be presented on RXD following the initial deassertion of CRS\_DV, then the PHY shall assert CRS\_DV on cycles of REF\_CLK which present the second di-bit of each nibble and deassert CRS\_DV on cycles of REF\_CLK which present the first di-bit of each nibble. If carrier sense is asserted and a valid SSD is not detected immediately, then RXER is asserted. A value of 2h (2 hex) is driven on the receive data pins to indicate false carrier sense.

In 10BASE-T mode, carrier sense is asserted asynchronously on the CRS pin when valid preamble activity is detected on the RD+/- input pins.

### **AUTO-NEGOTIATION**

The BCM5238 can negotiate its mode of operation over the twisted pair link using the auto-negotiation mechanism defined in the IEEE 802.3u specification. Auto-negotiation is enabled or disabled by hardware or software control. When the auto-negotiation function is enabled, the BCM5238 automatically chooses its mode of operation by advertising its abilities and comparing them with those received from its link partner. The BCM5238 can be configured to advertise 100BASE-TX full-duplex and/or half-duplex and 10BASE-T full-duplex and/or half-duplex. Each transceiver negotiates independently with its link partner, and chooses the highest level of operation available for its own link.

### **DIGITAL ADAPTIVE EQUALIZER**

The digital adaptive equalizer removes interzonal interference created by the transmission channel media. The equalizer accepts sampled unequalized data from the ADC on each channel and produces equalized data. The BCM5238 achieves an optimum signal to noise ratio by using a combination of feed forward equalization and decision feedback equalization. This powerful technique achieves a 100BASE-TX BER of less than  $1 \times 10^{-12}$  for transmission up to 100 meters on CAT 5 twisted pair cable, even in harsh noise environments. The digital adaptive equalizers in the BCM5238 achieve performance close to theoretical limits. The all-digital nature of the design makes the performance very tolerant to on-chip noise. The filter coefficients are self adapting to any quality of cable or cable length. Due to transmit pre-equalization in 10BASE-T mode, the adaptive equalizer is bypassed in this mode of operation.

### **ADC**

Each receive channel has its 125-MHz analog to digital converter (ADC). The ADC samples the incoming data on the receive channel and produces a digital output. The output of the ADC is fed to the digital adaptive equalizer. Advanced analog circuit techniques achieve low offset, high power supply noise rejection, fast settling time, and low bit error rate.

## **DIGITAL CLOCK RECOVERY/GENERATOR**

The all-digital clock recovery and generator block creates all internal transmit and receive clocks. The transmit clocks are locked to the 50-MHz clock input while the receive clocks are locked to the incoming data streams. Clock recovery circuits optimized to MLT3, NRZI, and Manchester encoding schemes are included for use with each of the three different operating

Document 5238-DS03-405-R Auto-negotiation Page 3

modes. The input data streams are sampled by the recovered clock from each port and fed synchronously to the respective digital adaptive equalizer.

## **MULTIMODE TRANSMIT DAC**

The multimode transmit digital to analog converter (DAC) transmits MLT3-coded symbols in 100BASE-TX mode and Manchester-coded symbols in 10BASE-T mode. It performs programmable edge-rate control in TX mode, which decreases unwanted high-frequency signal components, thus reducing EMI. High-frequency pre-emphasis is performed in 10BASE-T mode. The transmit DAC uses a current drive output that is well balanced and produces very low noise transmit signals.

### STREAM CIPHER

In 100BASE-TX mode, the transmit data stream is scrambled in order to reduce radiated emissions on the twisted pair cable. The data is scrambled by exclusive ORing the NRZ signal with the output of an 11-bit-wide linear feedback shift register (LFSR), which produces a 2047-bit non-repeating sequence. The scrambler reduces peak emissions by randomly spreading the signal energy over the transmit frequency range, and eliminating peaks at certain frequencies. Signal energy is spread further by using unique seeds to generate a different non-repeating sequence for each of the eight ports.

The receiver descrambles the incoming data stream by exclusive ORing it with the same sequence generated at the transmitter. The descrambler detects the state of the transmit LFSR by looking for a sequence representing consecutive idle codes. The descrambler locks to the scrambler state after detecting a sufficient number of consecutive idle code-groups. The receiver does not attempt to decode the data stream unless the descrambler is locked. Once locked, the descrambler continuously monitors the data stream to make sure that it has not lost synchronization. The receive data stream is expected to contain inter-packet idle periods. If the descrambler does not detect enough idle codes within 724  $\mu$ s, it becomes unlocked, and the receive decoder is disabled. If the receiver is put into Token Ring mode (see bit 10, register 1Bh), the descrambler monitors the receiver for 5792  $\mu$ s before unlocking. The descrambler is always forced into the unlocked state when a link failure condition is detected.

Stream cipher scrambling/descrambling is not used in 10BASE-T mode.

## MII MANAGEMENT

Management of each transceiver within the BCM5238 remains the same as it was under the MII specification. Each PHY contains an independent set of MII management registers. They share a single MDC/MDIO serial interface. Each transceiver has a unique address and must be accessed individually. The common base address for the group of eight individual transceivers is defined by configuring the five external PHYAD address input pins.

# SMII INTERFACE

The objective of this interface is to reduce the number of pins required to interconnect the MAC and the PHY. This is accomplished by clocking data and control signals in and out of each PHY on a pair of pins at a rate of 125 MHz.

Document 5238-DS03-405-R

Data and control signals passing from the MAC to the PHY use the serial transmit (STX) line; data and control signals passing from the PHY to the MAC use the serial receive (SRXD) line. All bit transfers are synchronous with clock (SCLK) at 125 MHz; frame sync is provided by a fourth line (SYNC), asserted at the beginning of each frame, which occurs every ten cycles of REF\_CLK. Each PHY is provided with an STX and an SRX pair. Pins TXD0{x} and RXD0{x}, where x is the number of the specific PHY, are used to perform the STX and SRX functions on the BCM5238.

The chip has a single SCLK and SYNC input which is common to all PHYs. Pins REF\_CLK and SSYNC are used for these functions on the BCM5238.

Receive data and control information are passed from the PHY to the MAC in ten-bit frames. In 100 Mbps mode, each frame represents a new byte of data. In 10 Mbps mode, each byte of data is repeated ten times; the MAC can sample any one of every ten frames. Since the timing of data coming from a remote transmitter is not synchronized with the local SCLK or SYNC lines and may contain errors in frequency, a FIFO capable of storing 28 bits is provided in each receive path. The received data bits and the RX\_DV signal are passed through the FIFO; the CRS bit is not. It is asserted for the time the wire is receiving a frame. If the remote transmitter is idle and no data needs to be passed from the receiver, status information becomes available.

Transmit data and control information are passed from the MAC to the PHY in ten-bit frames, as in the receive path. In 100 megabit mode, each frame represents a new byte of data. In 10 Mbps mode, each byte of data is repeated ten times; the PHY can transmit any one of every ten frames.

## Source Synchronous SMII (SSSMII) Interface

From a data signaling standpoint, the source synchronous SMII is essentially identical to standard SMII. The only difference is that source synchronous employs specific 125 MHz clocks and SYNC signals that travel in the same direction as the data, TXD0 and RXD0, and are synchronous to the data.

Therefore, a source synchronous capable MAC which sends TXD0 to the PHY must also send a source synchronous 125-MHz clock and SYNC signal to the PHY. The PHY uses this clock and SYNC to latch-in and delineate the TXD0 data stream.

Similarly, the BCM5238 in source synchronous SMII mode drives RXD0 to the MAC along with a 125 MHz clock and SYNC signals. The MAC should use this clock and SYNC to latch-in and delineate RXD0 data streams.

By using these separate clock and SYNC signals, SMII timing constraints are significantly eased.

### INTERRUPT MODE

The BCM5238 can be programmed to provide an interrupt output consisting of an OR of the eight interrupts, one from each PHY. The interrupt feature is disabled by default. The interrupt capability is enabled by setting MII register 1Ah, bit 14. The status of each interrupt source is also reflected in register 1Ah, bits 1, 2 and 3. The sources of interrupt are change in link, speed or full-duplex status. If any type of interrupt occurs, the Interrupt Status bit, register 1Ah, bit 0 is set.

In addition, each transceiver has its own register controlling the interrupt function.

If the interrupt enable bit is set to 0, no status bits sets and no interrupts are generated. If the interrupt enable bit is set to 1, the following conditions apply:

- If mask status bits are set to 0 and the interrupt mask is set to 1, status bits are set, but no interrupts are generated.

- If mask status bits are set to 0 and the interrupt mask is set to 0, status bits and interrupts are available.

- If mask status bits are set to 1 and the interrupt mask is set to 0, no status bits and no interrupts are available.

Changes from active to inactive, or vice versa, cause an interrupt. Setting register 1Ah, bit 8 high masks all interrupts, regardless of the settings of the individual mask bits.

# Section 2: Hardware Signal Definition Table

#### Note

I = Digital input, O = Digital output, I/O = Bidirectional,  $I_A$  = Analog input,  $O_A$  = Analog output,  $I_{PU}$  = Digital input with internal pull-down,  $O_{OD}$  = Open-drain output,  $O_{3S}$  = Three-state output, I/O<sub>PD</sub> = Bidirectional with internal pull-down, I/O<sub>PU</sub> = Bidirectional with internal pull-up, B = Bias Voltage

Table 2: Pin Definitions

| BCM5238B    | BCM5238U | Pin Label      | 1/0             | Description                                                  |

|-------------|----------|----------------|-----------------|--------------------------------------------------------------|

| Media Conne | ections  |                |                 |                                                              |

| A12,B12     | 4, 3     | RD+{1}, RD-{1} | I <sub>A</sub>  | Receive Pair. Differential data from the media is received   |

| A11,B11     | 6, 7     | RD+{2}, RD-{2} |                 | on the RD± signal pair.                                      |

| A08,B08     | 13, 12   | RD+{3}, RD-{3} |                 |                                                              |

| A07,B07     | 16, 17   | RD+{4}, RD-{4} |                 |                                                              |

| T06,R06     | 23, 22   | RD+{5}, RD-{5} |                 |                                                              |

| T07,R07     | 26, 27   | RD+{6}, RD-{6} |                 |                                                              |

| T10,R10     | 33, 32   | RD+{7}, RD-{7} |                 |                                                              |

| T11,R11     | 35, 36   | RD+{8}, RD-{8} |                 |                                                              |

| A13,B13     | 1, 2     | TD+{1}, TD-{1} | O <sub>A</sub>  | Transmit Pair. Differential data is transmitted to the media |

| A10,B10     | 9, 8     | TD+{2}, TD-{2} |                 | on the TD± signal pair.                                      |

| A09,B09     | 10,11    | TD+{3}, TD-{3} |                 |                                                              |

| A06,B06     | 19, 18   | TD+{4}, TD-{4} |                 |                                                              |

| T05,R05     | 20, 21   | TD+{5}, TD-{5} |                 |                                                              |

| T08,R08     | 29, 28   | TD+{6}, TD-{6} |                 |                                                              |

| T09,R09     | 30, 31   | TD+{7}, TD-{7} |                 |                                                              |

| T12,R12     | 38, 37   | TD+{8}, TD-{8} |                 |                                                              |

| E16         | 99       | TXD0{1}        | $I_{PD}$        | Transmit Data Input. Serial transmit data from MAC to        |

| F16         | 96       | TXD0{2}        |                 | PHY                                                          |

| G16         | 94       | TXD0{3}        |                 |                                                              |

| H16         | 92       | TXD0{4}        |                 |                                                              |

| J16         | 86       | TXD0{5}        |                 |                                                              |

| K16         | 84       | TXD0{6}        |                 |                                                              |

| L16         | 82       | TXD0{7}        |                 |                                                              |

| M16         | 79       | TXD0{8}        |                 |                                                              |

| D15         | 100      | RXD0{1}        | O <sub>3S</sub> | Receive Data Outputs. Serial Receive data from PHY to        |

| E15         | 97       | RXD0{2}        |                 | MAC                                                          |

| F13         | 95       | RXD0{3}        |                 |                                                              |

| G14         | 93       | RXD0{4}        |                 |                                                              |

| H13         | 87       | RXD0{5}        |                 |                                                              |

| J14         | 85       | RXD0{6}        |                 |                                                              |

| K13         | 83       | RXD0{7}        |                 |                                                              |

| L14         | 80       | RXD0{8}        |                 |                                                              |

Table 2: Pin Definitions (Cont.)

| BCM5238B     | BCM5238U     | Pin Label        | 1/0             | Description                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|--------------|--------------|------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Clock Signal | Clock Signal |                  |                 |                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| T15          | 42           | REF_CLK          | I               | Reference Clock Input. This pin must be driven with a continuous 125-MHz clock. It provides timing for RXD0, TXD0, and their associated clocks and SYNC signals. Accuracy shall be ±50 ppm, with a duty cycle between 35% and 65% inclusive.                                                                                                                                                        |  |  |  |

| PHY Control  | and Mode Sig | nals             |                 |                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| C16          | 102          | RESET            | I <sub>PU</sub> | <b>Reset.</b> Active Low. Resets the BCM5238. Pin not included in NAND chain.                                                                                                                                                                                                                                                                                                                       |  |  |  |

| N15          | 127          | F100             | I <sub>PU</sub> | <b>10/100 Mode Select.</b> When high and ANEN is low, all transceivers are forced to 100BASE-X operation. When low and ANEN is low, all transceivers are forced to 10BASE-T operation. When ANEN is high, F100 has no effect on the operation.                                                                                                                                                      |  |  |  |

| M13          | 126          | ANEN             | I <sub>PU</sub> | Auto-Negotiation Enable. Active high. When pulled high, auto-negotiation begins immediately after reset. When low, auto-negotiation is disabled after reset. Auto-negotiation can be enabled under software control (register 0, bit 12) if auto-negotiation is enabled through hardware.                                                                                                           |  |  |  |

| C15          | 101          | FDXEN            | I <sub>PD</sub> | Full-Duplex Mode Enable. The FDXEN pin is logically ORed with an MII control bit to generate an internal full-duplex enable signal. When FDXEN is high, the BCM5238 may operate in full-duplex mode as determined by autonegotiation. When FDXEN is low, the internal control bit (register 0, bit 8) determines the full-duplex operating mode. Initial value of the internal control bit is zero. |  |  |  |

| F05          | 74           | MDIX_DIS         | I <sub>PD</sub> | HP Auto-MDIX Disable. Active high. When pulled high during reset, automatic TX cable swap detection function of the BCM5238 is disabled. Leave this pin unconnected for normal operation.                                                                                                                                                                                                           |  |  |  |

| F04          | 117          | TESTEN           | I <sub>PD</sub> | <b>Test Enable.</b> Active high test control input used along with PHYAD[4:0] to select the NAND-chain test mode. This test mode is latched when TESTEN is pulsed high, then low, with PHYAD[4:0] = 10111. This pin is not included in the NAND chain and must be pulled low or left unconnected during normal operation.                                                                           |  |  |  |

| K02          | 71           | INTR/<br>SLED_DO | O <sub>OD</sub> | PHY Interrupt. Active low output. This pin becomes interrupt output if SER_EN pin is low during power-on reset.  SLED_DO. Serial LED Data. Active low serial LED data. Pin-71 becomes serial LED data output if SERIAL_EN pin is high during power-on reset. See "LED Display Output Modes" on page 18 for details.                                                                                 |  |  |  |

Table 2: Pin Definitions (Cont.)

| BCM5238B                      | BCM5238U              | Pin Label               | 1/0               | Description                                                                                                                                                                                                                                                                                                                                                                            |

|-------------------------------|-----------------------|-------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| H01                           | 65                    | SSSMII_DIS/<br>SLED_CLK | I/O <sub>PU</sub> | <b>SSSMII Disable.</b> Active high. When this pin is high or left unconnected during power-on reset, the BCM5238 enables the Serial Media Independent Interface mode (SMII).                                                                                                                                                                                                           |

|                               |                       |                         |                   | When this pin is low (pull-down) during power-on reset, the SMII source Synchronous SMII mode is enabled. When the SMII Source Synchronous mode is enabled, the BCM5238 provides a source synchronous receive clock (SSSMII_RXC) and a sync (SSSMII_RSYNC) for MAC to use for receiving data from the PHY and the BCM5238 uses SMII_TXC along with SSYNC to receive data from the MAC. |

|                               |                       |                         |                   | SLED_CLK. Serial LED clock. After power-on reset, if serial or low cost serial LED mode is enabled, this pin sources the clock for serial data SLED_DO. See "LED Display Output Modes" on page 18 for details.                                                                                                                                                                         |

| E10                           | 104                   | MODE_5228               | I <sub>PU</sub>   | BCM5228 Mode Select. Active high. During power-on if this pin is left unconnected (or pull-up), the BCM5238 MII registers values default to the BCM5228 MII register default values. Otherwise, it defaults to the BCM5238 default register values.                                                                                                                                    |

| M08                           |                       | LED1TO3                 | I <sub>PLL</sub>  | <b>LED1 to LED3 Option.</b> Active low. When this pin is low, the BCM5228 LED3 will be available on LED1. Refer to the BCM5228 data sheet for hardware default and MII register programming. Note that this option is available only in the BCM5238B.                                                                                                                                  |

| SMII and SS                   | MII Signals           |                         |                   |                                                                                                                                                                                                                                                                                                                                                                                        |

| P15                           | 67                    | SSYNC                   | I <sub>PD</sub>   | <b>SYNC.</b> In SMII mode, this pin must be connected to a free running sync pulse occurring 1 of every 10 clock cycles.                                                                                                                                                                                                                                                               |

|                               |                       |                         |                   | Data and controls are transferred through TXD and RXD between respective MAC and PHY in default SMII mode. If source synchronous enable, SSSMII_DIS, is low, then SSYNC provides sync for TXD only and SSSMII_RSYNC from the BCM5238 provides sync for RXD.                                                                                                                            |

| R16                           | 69                    | SSSMII_RXC              | O <sub>3S</sub>   | SMII Source Synchronous Receive Clock. Optional 125-MHz clock in SMII mode for MAC use to clock in RXD.                                                                                                                                                                                                                                                                                |

| P16                           | 70                    | SSSMII_RSYNC            | O <sub>3S</sub>   | <b>SMII Source Synchronous SYNC.</b> In SMII mode, this pin provides a source synchronous SYNC pulse for MAC to use for RXD if source synchronous is enabled.                                                                                                                                                                                                                          |

| T16                           | 66                    | SSASMII_TXC             | I <sub>PD</sub>   | SMII Source Synchronous Transmit Clock.  125-MHz clock in SSSMII mode for BCM5238 to clock in TXD if source synchronous mode is enabled.                                                                                                                                                                                                                                               |

| MII Register                  | Access Signal         | 's                      |                   |                                                                                                                                                                                                                                                                                                                                                                                        |

| J01                           | 118                   | MDIO                    | I/O <sub>PU</sub> | <b>Management Data I/O.</b> This serial input/output bit is used to read from and write to the MII registers. The data value on the MDIO pin is valid and latched on the rising edge of MDC.                                                                                                                                                                                           |

| K01                           | 119                   | MDC                     | I <sub>PD</sub>   | <b>Management Data Clock.</b> The MDC clock input must be provided to allow MII management functions. Clock frequencies up to 25 MHz are supported.                                                                                                                                                                                                                                    |

| G05, H05,<br>H04, J05,<br>J03 | 47, 48, 49,<br>50, 51 | PHYAD {4:0}             | I <sub>PD</sub>   | PHY ADdress Selects. These inputs set the base address for MII management PHY addresses. Also serve as test control inputs along with TESTEN to select the NAND-chain test mode.                                                                                                                                                                                                       |

Table 2: Pin Definitions (Cont.)

| BCM5238B                                        | BCM5238U                                 | Pin Label            | 1/0               | Description                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------------------------------|------------------------------------------|----------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| H02                                             | 75                                       | MASTERPHY/<br>SFRAME | I/O <sub>PD</sub> | Master PHY Address Mode. Active high. This forces PHY address 0 to be a global write address for all PHYs within the BCM5238. An active high during power-on reset selects the master PHY address mode, while an active low or being left unconnected selects the normal address mode.  SFRAME. Serial LED Frame. After power-on reset, this pin sources the serial LED frame output signal if serial LED mode is enabled. |

| LEDs and LE                                     | ED Control Sign                          | nals                 |                   |                                                                                                                                                                                                                                                                                                                                                                                                                            |

| G03                                             | 76                                       | SERIAL_EN            | I <sub>PD</sub>   | Serial LED Enable. Active high. Serial LED mode is enabled if this pin is high and LC-SER_EN pin is low during power-on reset. Serial LED mode and low cost serial LED mode can not be active at the same time.                                                                                                                                                                                                            |

| 000                                             | 77                                       | LC CED EN            |                   | See "LED Display Output Modes" on page 18 for details.                                                                                                                                                                                                                                                                                                                                                                     |

| G02                                             | //                                       | LC_SER_EN            | I <sub>PU</sub>   | Low Cost Serial LED Enable. Active high. Low cost serial LED mode is enabled if this pin is high and SERIAL_EN pin is high during power-on reset. Low cost serial LED mode and serial LED mode cannot be active at the same time.                                                                                                                                                                                          |

|                                                 |                                          | . = =                |                   | See "LED Display Output Modes" on page 18 for details.                                                                                                                                                                                                                                                                                                                                                                     |

| F01, F02,<br>E01, E02,<br>P01, P02,<br>N02, N01 | 110, 111,<br>113, 114, 59,<br>60, 62, 63 | LED1{1:8}            | I/O <sub>PD</sub> | <b>LED1[1:8].</b> Active low output. This is one of two available parallel LED output signals. These pins are sampled during power-on reset to set the default LED output for LED1 and LED2. See "LED Display Output Modes" on page 18 for details.                                                                                                                                                                        |

| C04, E06,<br>D05, C05,<br>M07, N07,<br>M06, N06 | 105, 106,<br>108, 109, 53,<br>54, 57, 58 | LED2{1:8}            | O <sub>OD</sub>   | LED2. Active low output. This is one of two available parallel LED output signals. See "LED Display Output Modes" on page 18 for details.                                                                                                                                                                                                                                                                                  |

| JTAG Signal                                     | ls                                       |                      |                   |                                                                                                                                                                                                                                                                                                                                                                                                                            |

| L02                                             | 121                                      | TDI                  | I <sub>PU</sub>   | Test Data Input. Single data input to the JTAG TAP controller used to traverse the test-logic state machine. Sampled on the rising edge of TCK. If unused, may be left unconnected.                                                                                                                                                                                                                                        |

| L03                                             | 123                                      | TMS                  | I <sub>PU</sub>   | <b>Test Mode Select.</b> Serial control input to the JTAG TAP controller. Sampled on the rising edge of TCK. If unused, can be left unconnected.                                                                                                                                                                                                                                                                           |

| L05                                             | 122                                      | TCK                  | I <sub>PU</sub>   | <b>Test Clock.</b> Clock input used to synchronize the JTAG TAP control and data transfers. If unused, can be left unconnected.                                                                                                                                                                                                                                                                                            |

| K04                                             | 125                                      | TDO                  | O <sub>3S</sub>   | <b>Test Data Output.</b> Serial data output from the JTAG TAP Controller. Updated on the falling edge of TCK. Actively driven both high and low when enabled; high impedance otherwise.                                                                                                                                                                                                                                    |

| K05                                             | 124                                      | TRST                 | I <sub>PU</sub>   | Test Reset. Asynchronous active-low reset input to the JTAG TAP Controller. Must be held low during power-up to insure the TAP Controller initializes to the test-logic-reset state; must be pulled low continuously when JTAG functions are not used.                                                                                                                                                                     |

| Power, Bias,                                    | , and Reference                          | Signals              |                   |                                                                                                                                                                                                                                                                                                                                                                                                                            |

| A15                                             | 45                                       | RDAC                 | В                 | <b>DAC Bias Resistor.</b> Adjusts the current level of each of the transmit DACs. A resistor of 1.24 K $\Omega$ ±1% must be connected between the RDAC pin and AGND.                                                                                                                                                                                                                                                       |

Table 2: Pin Definitions (Cont.)

| BCM5238B                                                                                                                      | BCM5238U                                       | Pin Label | 1/0 | Description                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-----------|-----|-------------------------------------------------------------------------------|

| T14                                                                                                                           | 41                                             | PLLVDD18  | PWR | Phase Locked Loop Core VDD, 1.8V                                              |

|                                                                                                                               |                                                |           |     | Note: In the BCM5228 Core VDD is 2.5V                                         |

| P14                                                                                                                           | 43                                             | PLLVDDP   | PWR | Phase Locked Loop PAD VDD, same supply as OVDD                                |

| R14                                                                                                                           | 40                                             | PLLGND    | GND | Phase Locked Loop GND                                                         |

| A16                                                                                                                           | 46                                             | BIASVDD33 | В   | Bias VDD, same supply as OVDD                                                 |

| B16                                                                                                                           | 44                                             | BIASGND   | GND | Bias GND                                                                      |

| A05, C07,<br>C10, C13,<br>P07, P11,<br>T04, T13                                                                               | 5, 15, 24, 34                                  | AVDD18    | PWR | Analog VDD, 1.8V<br>Note: In the BCM5228, analog VDD is 2.5V                  |

| B05, B14,<br>B15, C06,<br>C08, C09,<br>C11, C12,<br>D09, D10,<br>E09, P05,<br>P06, P08,<br>P09, P10,<br>P12, P13,<br>R04, R13 | 14, 25, 39,<br>128                             | AGND      | GND | Analog GND                                                                    |

| E04, E13,                                                                                                                     | 56, 73, 90,                                    | DVDD18    | PWR | 1.8V, Digital Core VDD                                                        |

| G04, K14,<br>L04, N13                                                                                                         | 116                                            |           |     | Note that Digital Core VDD in the BCM5228 is 2.5V                             |

| C14, F03,<br>G06, J13,<br>M03, N14                                                                                            | 52, 64, 78,<br>89, 91, 103,<br>115             | DGND      | GND | Digital Core and Output Buffer GND                                            |

| D06, E03,<br>F14, G13,<br>H03, K03,<br>L13, M14,<br>N08                                                                       | 55, 61, 68,<br>81, 88, 98,<br>107, 112,<br>120 | OVDD      | PWR | 3.3V, Digital Periphery (Output Buffer) VDD                                   |

| D13, F06,<br>F07, H11,<br>H14, J04,<br>L06, L07,<br>N16                                                                       | -                                              | OGND      | GND | Digital Periphery (Output Buffer) Ground                                      |

| J2                                                                                                                            | 72                                             | INTERNAL1 | NC  | <b>FACTORY TEST (DP) pin</b> . Must be left unconnected for normal operation. |

Table 2: Pin Definitions (Cont.)

| BCM5238B                                                                                                                                                                                                                                                                                                                                                                                                                                         | BCM5238U | Pin Label | I/O | Description                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------|-----|-------------------------------------------------------------------------------------------|

| A01, A02,<br>A03, A04,<br>A14, B01,<br>B02, B03,<br>B04, C01,<br>C02, C03,<br>D01, D02,<br>D03, D04,<br>D07, D08,<br>D11, D12,<br>D14, D16,<br>E05, E07,<br>E08, E11,<br>E12, E14,<br>F12, F15,<br>G01, G12,<br>G15, H12,<br>H15, J12,<br>J15, K12,<br>K15, L01,<br>L12, L15,<br>M01, M02,<br>M04, M05,<br>M09, M10,<br>M11, M12,<br>M15, N03,<br>N04, N05,<br>N09, N10,<br>N11, N12,<br>P03, P04,<br>R01, R02,<br>R03, R15,<br>T01, T02,<br>T03 |          | NC TOND   |     | No Connect. Do not connect anything to these pins and do not connect these pins together. |

| F08, F09,<br>F10, F11,<br>G07, G08,<br>G09, G10,<br>G11, H06,<br>H07, H08,<br>H09, H10,<br>J06, J07,<br>J08, J09,<br>J10, J11,<br>K06, K07,<br>K08, K09,<br>K10, K11,<br>L08, L09,<br>L10, L11                                                                                                                                                                                                                                                   | _        | TGND      | _   | Thermal Ground. Connect these pins to the ground plane.                                   |

# **Section 3: Pinout Diagram**

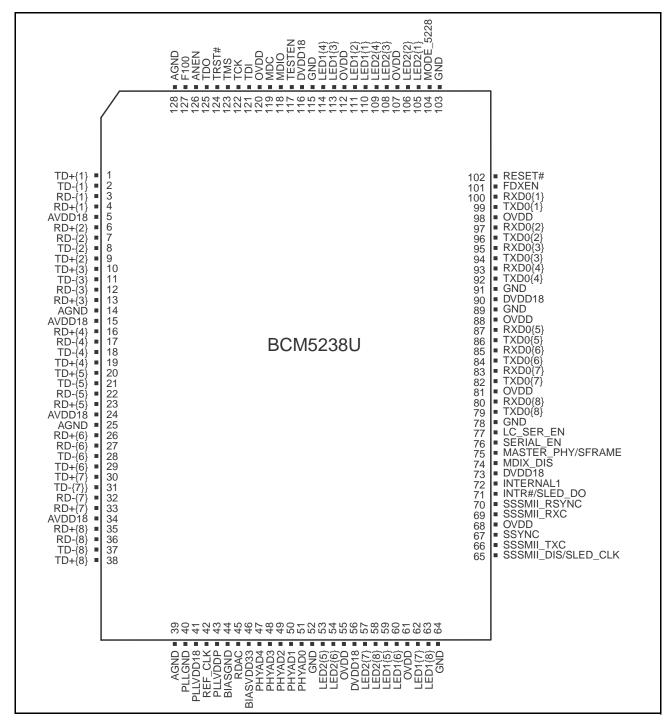

Figure 2 is the pinout diagram for the BCM5238U.

Figure 2: BCM5238U Pin Diagram

The pinout diagram for the BCM5238B 256-pin FBGA package is shown in Figure 3.

|   | 01                          | 02                       | 03            | 04        | 05           | 06      | 07      | 08      | 09     | 10            | 11     | 12     | 13      | 14       | 15      | 16               |   |

|---|-----------------------------|--------------------------|---------------|-----------|--------------|---------|---------|---------|--------|---------------|--------|--------|---------|----------|---------|------------------|---|

| А | NC                          | NC                       | NC            | NC        | AVDD18       | TD+{4}  | RD+{4}  | RD+{3}  | TD+{3} | TD+{2}        | RD+{2} | RD+{1} | TD+{1}  | NC       | RDAC    | BIASVDD3         | А |

| В | NC                          | NC                       | NC            | NC        | AGND         | TD-{4}  | RD-{4}  | RD-{3}  | TD-{3} | TD-{2}        | RD-{2} | RD-{1} | TD-{1}  | AGND     | AGND    | BIASGND          | В |

| С | NC                          | NC                       | NC            | LED2{1}   | LED2{4}      | AGND    | AVDD18  | AGND    | AGND   | AVDD18        | AGND   | AGND   | AVDD18  | DGND     | FDXEN   | RESET#           | С |

| D | NC                          | NC                       | NC            | NC        | LED2{3}      | OVDD    | NC      | NC      | AGND   | AGND          | NC     | NC     | OGND    | NC       | RXD0{1} | NC               | D |

| Е | LED1{3}                     | LED1{4}                  | OVDD          | DVDD18    | NC           | LED2{2} | NC      | NC      | AGND   | MODE_<br>5228 | NC     | NC     | DVDD18  | NC       | RXD0{2} | TXD0{1}          | E |

| F | LED1{1}                     | LED1{2}                  | DGND          | TESTEN    | MDIX_<br>DIS | OGND    | OGND    | TGND    | TGND   | TGND          | TGND   | NC     | RXD0{3} | OVDD     | NC      | TXD0{2}          | F |

| G | NC                          | LC_SER_<br>EN            | SERIAL_<br>EN | DVDD18    | PHYAD4       | DGND    | TGND    | TGND    | TGND   | TGND          | TGND   | NC     | OVDD    | RXD0{4}  | NC      | TXD0{3}          | G |

| н | SSSMII_<br>DIS/<br>SLED_CLK | MASTERP<br>HY/<br>SFRAME | OVDD          | PHYAD2    | PHYAD3       | TGND    | TGND    | TGND    | TGND   | TGND          | OGND   | NC     | RXD0{5} | OGND     | NC      | TXD0{4}          | Н |

| J | MDIO                        | INTERNAL1                | PHYAD0        | OGND      | PHYAD1       | TGND    | TGND    | TGND    | TGND   | TGND          | TGND   | NC     | DGND    | RXD0{6}  | NC      | TXD0{5}          | J |

| К | MDC                         | SLED_<br>DO/<br>INTR#    | OVDD          | TDO       | TRST#        | TGND    | TGND    | TGND    | TGND   | TGND          | TGND   | NC     | RXD0{7} | DVDD18   | NC      | TXD0{6}          | К |

| L | NC                          | TDI                      | TMS           | DVDD18    | TCK          | OGND    | OGND    | TGND    | TGND   | TGND          | TGND   | NC     | OVDD    | RXD0{8}  | NC      | TXD0{7}          | L |

| М | NC                          | NC                       | DGND          | NC        | NC           | LED2{7} | LED2{5} | LED1TO3 | NC     | NC            | NC     | NC     | ANEN    | OVDD     | NC      | TXD0{8}          | М |

| N | LED1{8}                     | LED1{7}                  | NC            | NC        | NC           | LED2{8} | LED2{6} | OVDD    | NC     | NC            | NC     | NC     | DVDD18  | DGND     | F100    | OGND             | N |

| Р | LED1{5}                     | LED1{6}                  | NC            | NC        | AGND         | AGND    | AVDD18  | AGND    | AGND   | AGND          | AVDD18 | AGND   | AGND    | PLLVDDP  | SSYNC   | SSSMII_<br>RSYNC | Р |

| R | NC                          | NC                       | NC            | AGND      | TD-{5}       | RD-{5}  | RD-{6}  | TD-{6}  | TD-{7} | RD-{7}        | RD-{8} | TD-{8} | AGND    | PLLGND   | NC      | SSSMII_<br>RXC   | R |

| Т | NC                          | NC                       | NC            | AVDD18    | TD+{5}       | RD+{5}  | RD+{6}  | TD+{6}  | TD+{7} | RD+{7}        | RD+{8} | TD+{8} | AVDD18  | PLLVDD18 | REF_CLK | SSSMII_<br>TXC   | Т |

|   | 01                          | 02                       | 03            | 04        | 05           | 06      | 07      | 08      | 09     | 10            | 11     | 12     | 13      | 14       | 15      | 16               |   |

|   | NOIE. IC                    | SND balls                | are triell    | nai gioui | 103          |         |         |         |        |               |        |        |         |          |         |                  |   |

Figure 3: BCM5238B Pin Diagram

## **Section 4: Operational Description**

### **RESETTING THE BCM5238**

There are two ways to reset each transceiver in the BCM5238. A hardware reset pin has been provided which resets all internal nodes inside the chip to a known state. The reset pulse must be asserted for at least 2  $\mu$ s. Hardware reset should always be applied to a BCM5238 after power-up.

Each transceiver in the BCM5238 also has an individual software reset capability. To perform software reset, a 1 must be written to bit 15 of the transceiver's MII Control register (see "MII Control Register" on page 29). This bit is self-clearing, meaning that a second write operation is not necessary to end the reset. There is no effect if a 0 is written to the MII Control Register Reset bit.

### **PHY ADDRESS**

Each transceiver in the BCM5238 has a unique PHY address for MII management. The PHY address is determined by the using the base address, which is input on the PHYAD[4:0] pins. The following shows the addressing of the eight PHYs.

PHY0 = PHYAD + 0, PHY1 = PHYAD + 1,... PHY7 = PHYAD + 7

Every time an MII write or read operation is executed, the transceiver compares the PHY address with its own PHY address definition. The operation is executed only when the addresses match.

### **LOOPBACK MODE**

The loopback mode allows in-circuit testing of the BCM5238 chip. All packets sent in through the TXD pins are looped-back internally to the RXD pins, and are not sent out to the cable. Incoming packets on the cable are ignored.

The loopback mode may be entered by writing a 1 to bit 14 of the MII Control register or by writing a 1 to bit 8 and bit 7 of shadow register 1Dh. To resume normal operation, the bits must be 0.

## FULL-DUPLEX MODE

The BCM5238 supports full-duplex operation. While in full-duplex mode, a transceiver can simultaneously transmit and receive packets on the cable. By default, each transceiver in the BCM5238 powers up in half-duplex mode.

When auto-negotiation is disabled, full-duplex operation can be enabled either by a pin (FDXEN) or by an MII register bit (register 0, bit 8).

When auto-negotiation is enabled, full-duplex capability is advertised by default but can be overridden by a write to the Auto-Negotiation Advertisement register (04h).

### **10BASE-T Mode**

The same magnetics module is used to interface the twisted-pair cable in 10BASE-T mode and in 100BASE-TX mode. The data is two-level Manchester coded instead of three-level MLT3, and no scrambling/descrambling or 4B5B coding is performed.

#### **ISOLATE MODE**

Each transceiver in the BCM5238 can be isolated from the RMII/SMII/S3MII interface. When a transceiver is put into isolate mode, all RMII/SMII/S3MII input pins (TXD0, SSYNCS, SMII\_TXC) are ignored and all SMII/S3MII output pins (RXD0, SSMII\_RSYNC, SSMII\_RXC) are set at high impedance. MII management pins (MDC, MDIO,) and analog TD±, RD± pins operate normally. Writing a 1 to bit 10 of the MII Control register 0 puts the port into isolate mode. Writing a 0 to the same bit removes it from isolate mode. Upon resetting the chip or resetting the isolated port, the isolate mode is off.

### SUPER ISOLATE MODE

When the chip is in super isolate mode, in addition to isolate mode actions, the chip also sets the analog TD± pins to high impedance. Writing a 1 to bit 3 of the MII register 1Eh puts the port into super isolate mode. Writing a 0 to the same bit removes it from super isolate mode. Upon resetting the chip or resetting the isolated port, the super isolate mode is off.

## **AUTO POWER-DOWN MODE**

The BCM5238 supports a low power mode called auto power-down mode. Auto power-down mode is enabled by setting bit 5 of shadow register 1Bh. When in this mode, the BCM5238 automatically enters the low power mode if the energy from the link partner is lost. Similarly, the next time energy is detected, the chip resumes full power mode. When the BCM5238 is in this low power mode, it wakes up after approximately 2.5 to 5.0 seconds, as determined by bit 4 of shadow register 1Bh, and sends a link pulse while monitoring energy from the link partner. If energy is detected, the BCM5238 enters full power mode and establishes link with the link partner. Otherwise, the wake-up mode continues for a duration of approximately 40–600 ms, as determined by bits [3:0] of shadow register 1Bh before going to low power mode. See Table 47 on page 53 for details of various bits.

## JUMBO PACKET MODE

In 100BASE-X mode, the BCM5238 can support jumbo packet sizes. The size of the packet that can be handled reliably depends on the descrambler lock timer settings and the receive FIFO size. By default, the BCM5238 provides an effective 10 bits receive FIFO to accommodate the minor clock deviations of the link partner. Additionally, the BCM5238 incorporates

extended FIFO modes to allow for extremely large packet sizes. These modes are enabled by setting appropriate bits in the MII registers. The following table shows the number of effective FIFO bits supported.

Table 3: Receive FIFO Size Select

| Jumbo Packet FIFO Enable<br>Reg 1Bh bit 9 | Extended FIFO Enable<br>Reg 10h bit 2 | Number of Effective FIFO<br>Bits Supported | Packet Size in Bytes <sup>b</sup> |

|-------------------------------------------|---------------------------------------|--------------------------------------------|-----------------------------------|

| 0                                         | 0                                     | 10                                         | 12,500                            |

| 0                                         | 1                                     | 20                                         | 25,000                            |

| 1                                         | 0                                     | 20                                         | 25,000                            |

| 1                                         | 1                                     | 40 (20) <sup>a</sup>                       | 50,000/25,000                     |

a. In this mode, the BCM5238 operation is guaranteed to only to 20 bits effective FIFO depth, although under some circumstances, it could behave as if the FIFO depth is 40 bits.