# MIC23451

3MHz, 2A Triple Synchronous Buck Regulator with HyperLight Load<sup>®</sup> and Power Good

### **General Description**

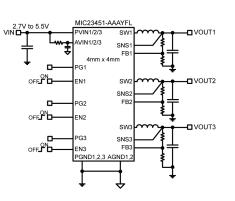

The MIC23451 is a high-efficiency, 3MHz, triple 2A, synchronous buck regulator with HyperLight Load<sup>®</sup> mode. HyperLight Load provides very-high efficiency at light loads and ultra-fast transient response, which is ideal for supplying processor core voltages. An additional benefit of this proprietary architecture is very low output ripple voltage throughout the entire load range with the use of small output capacitors. The 4mm x 4mm QFN package saves board space and requires only five external components for each channel.

The MIC23451 is designed for use with a very small inductor, down to  $0.47\mu$ H, and an output capacitor as small as  $2.2\mu$ F that enables a total solution size that is less than 1mm height.

The MIC23451 has a very-low quiescent current of  $24\mu$ A each channel and achieves as high as 81% efficiency at 1mA. At higher loads, the MIC23451 provides a constant switching frequency around 3MHz while achieving peak efficiencies up to 93%.

The MIC23451 is available in a 26-pin 4mm x 4mm QFN package with an operating junction temperature range from  $-40^{\circ}$ C to  $+125^{\circ}$ C.

Datasheets and support documentation are available on Micrel's web site at: <u>www.micrel.com</u>.

### Features

- 2.7V to 5.5V input voltage

- Three independent 2A outputs

- Up to 93% peak efficiency

- 81% typical efficiency at 1mA

- Three independent power good indicators

- 24µA typical quiescent current (per channel)

- 3MHz PWM operation in continuous mode

- Ultra-fast transient response

- Low voltage output ripple

- 30mV<sub>PP</sub> ripple in HyperLight Load mode

- 5mV output voltage ripple in full PWM mode

- Fully integrated MOSFET switches

- 0.1µA shutdown current (per channel)

- Thermal-shutdown and current-limit protection

- Output voltage as low as 1V

- 26-pin 4mm × 4mm QFN

- -40°C to +125°C junction temperature range

### Applications

- Solid state drives (SSD)

- μC/μP, FPGA, and DSP power

- Test and measurement systems

- Set-top boxes and DTV

- High-performance servers

- Security/surveillance cameras

- 5V POL applications

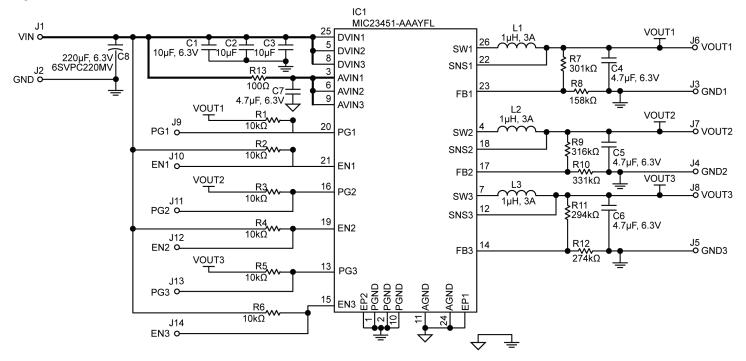

### **Typical Application**

HyperLight Load is a registered trademark of Micrel, Inc.

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 • http://www.micrel.com

### **Ordering Information**

| Part Number     | Marking | Nominal Output<br>Voltage | Junction Temperature<br>Range <sup>(1)</sup> | Package <sup>(2,3)</sup>    | Lead Finish |

|-----------------|---------|---------------------------|----------------------------------------------|-----------------------------|-------------|

| MIC23451-AAAYFL | AAA     | Adj./Adj./Adj.            | –40°C to +125°C                              | 26-Pin 4mm $\times$ 4mm QFN | Pb-Free     |

Notes:

1. Other options are available. Contact Micrel for details.

2. QFN is a Green, RoHS-compliant package. Lead finish is NiPdAu. Mold compound is Halogen Free.

3. QFN • = Pin 1 identifier

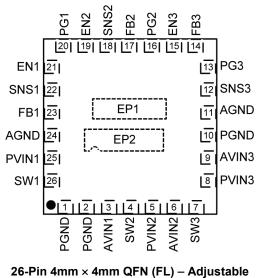

## **Pin Configuration**

(Top View)

### **Pin Description**

| Pin Number    | Pin Name    | Pin Function                                                                                                                                                          |

|---------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 26, 4, 7      | SW1, 2, 3   | Switch (Output). Internal power MOSFET output switches for output 1/2/3.                                                                                              |

| 21, 19, 15    | EN1, 2, 3   | Enable (Input). Logic high enables operation of regulator 1/2/3. Logic low will shut down the device. Do not leave floating.                                          |

| 22, 18, 12    | SNS1, 2, 3  | Sense. Connect to $V_{OUT1,2,3}$ as close to output capacitor as possible to sense output voltage.                                                                    |

| 23, 17, 14    | FB1, 2, 3   | Feedback. Connect a resistor divider from output 1/2/3 to ground to set the output voltage.                                                                           |

| 20, 16, 13    | PG1, 2, 3   | Power Good. Open-drain output for the power good indicator for output 1/2/3. Place a resistor between this pin and a voltage source to detect a power good condition. |

| EP1, 24, 11   | AGND        | Analog Ground. Connect to quiet ground point away from high-current paths, for example, $C_{OUT}$ , for best operation. Must be connected externally to PGND.         |

| 25, 5, 8      | PVIN1, 2, 3 | Power Input Voltage. Connect a capacitor to PGND to localize loop currents and decouple switching noise.                                                              |

| 3, 6, 9       | AVIN1, 2, 3 | Analog Input Voltage. Connect a capacitor to AGND to decouple noise.                                                                                                  |

| EP2, 10, 2, 1 | PGND        | Power Ground.                                                                                                                                                         |

# Absolute Maximum Ratings<sup>(1)</sup>

| Supply Voltage (PV <sub>IN,</sub> AV <sub>IN</sub> )                            | –0.3 to 6V        |

|---------------------------------------------------------------------------------|-------------------|

| Sense (V <sub>SNS1</sub> , V <sub>SNS2</sub> , V <sub>SNS3</sub> )              | –0.3 to 6V        |

| Power Good (PG1, PG2, PG3)                                                      | –0.3 to 6V        |

| Output Switch Voltage (V <sub>SW1</sub> , V <sub>SW2</sub> , V <sub>SW3</sub> ) | –0.3V to 6V       |

| Enable Input Voltage (V <sub>EN1</sub> , V <sub>EN2</sub> , V <sub>EN3</sub> )  | –0.3V to $V_{IN}$ |

| Storage Temperature Range                                                       |                   |

| ESD Rating <sup>(3)</sup>                                                       | . ESD Sensitive   |

|                                                                                 |                   |

# **Operating Ratings**<sup>(2)</sup>

| Supply Voltage (V <sub>IN</sub> )                                               | +2.7V to +5.5V                             |

|---------------------------------------------------------------------------------|--------------------------------------------|

| Enable Input Voltage (V <sub>EN1</sub> , V <sub>EN2</sub> , V <sub>EN3</sub> )  |                                            |

| Output Voltage Range (V <sub>SNS1</sub> , V <sub>SNS2</sub> , V <sub>SNS2</sub> | <sub>S3</sub> ) +1V to +3.3V               |

| Junction Voltage Range (T <sub>J</sub> )4                                       | $0^{\circ}C \leq T_{J} \leq +125^{\circ}C$ |

| Thermal Resistance                                                              |                                            |

| 26-Pin 4mm $\times$ 4mm QFN ( $\theta_{JA}$ )                                   | +20°C/W                                    |

| 26-Pin 4mm $\times$ 4mm QFN ( $\theta_{JC})$                                    | +10°C/W                                    |

|                                                                                 |                                            |

# Electrical Characteristics<sup>(4)</sup>

$T_A = +25^{\circ}C; V_{IN} = V_{EN1}, V_{EN2}, V_{EN3} = 3.6V; L1 = L2 = L3 = 1\mu H; C_{OUT1}, C_{OUT2}, C_{OUT3} = 4.7\mu F, unless otherwise specified.$ Bold values indicate -40°C  $\leq T_J \leq$  +125°C, unless noted.

| Parameter                                                                     | Condition                                                                                           | Min.  | Тур.  | Max.  | Units |  |

|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-------|-------|-------|-------|--|

| Supply Voltage Range                                                          |                                                                                                     | 2.7   |       | 5.5   | V     |  |

| Undervoltage Lockout Threshold                                                | Turn-On                                                                                             | 2.45  | 2.55  | 2.65  | V     |  |

| Undervoltage Lockout Hysteresis                                               |                                                                                                     |       | 75    |       | mV    |  |

| Quiescent Current                                                             | $I_{OUT}$ = 0mA, SNS > 1.2 × V <sub>OUTNOM</sub>                                                    |       | 65    | 120   | μA    |  |

| Per Channel Shutdown Current                                                  | V <sub>EN1</sub> , V <sub>EN2</sub> , V <sub>EN3</sub> = 0V; V <sub>IN</sub> = 5.5V                 |       | 0.1   | 5     | μA    |  |

|                                                                               | V <sub>IN</sub> = 3.6V if V <sub>OUT(NOM)</sub> < 2.5V, I <sub>LOAD</sub> = 20mA                    |       |       |       |       |  |

| Output Voltage Accuracy                                                       | $V_{IN}$ = 4.5V if $V_{OUT(NOM)} \ge 2.5V$ , $I_{LOAD}$ = 20mA                                      | -2.5  |       | +2.5  | %     |  |

| Feedback Voltage<br>(V <sub>FB1</sub> , V <sub>FB2</sub> , V <sub>FB3</sub> ) |                                                                                                     | 0.604 | 0.62  | 0.635 | V     |  |

| Peak Current Limit                                                            | $I_{OUT1}$ , $I_{OUT2}$ , $I_{OUT3}$<br>SNS1, SNS2, SNS3 = 0.9 × $V_{OUTNOM}$                       | 2.2   | 4.1   |       | А     |  |

| Foldback Current Limit                                                        |                                                                                                     |       | 2.3   |       | Α     |  |

| Output Voltage Line Regulation                                                | $V_{\text{IN}}$ = 3.6V to 5.5V if $V_{\text{OUTNOM1, 2, 3}}\!<\!2.5\text{V},I_{\text{LOAD}}$ = 20mA | 0.3   |       |       | %/V   |  |

| (V <sub>OUT1</sub> , V <sub>OUT2</sub> , V <sub>OUT3</sub> )                  | $V_{\text{IN}}$ = 4.5V to 5.5V if $V_{\text{OUTNOM1, 2, 3}} \!\geq\! 2.5V,  I_{\text{LOAD}}$ = 20mA |       | 0.5   |       | 707 V |  |

| Output Voltage Load Regulation                                                | DCM: 20mA < $I_{\text{LOAD}}$ < 130mA, $V_{\text{IN}}$ = 3.6V if $V_{\text{OUTNOM}}$ < 2.5V         |       | 0.2   |       | ~ %   |  |

|                                                                               | DCM: 20mA < $I_{\text{LOAD}}$ < 130mA, $V_{\text{IN}}$ = 5.0V if $V_{\text{OUTNOM}}$ > 2.5V         |       | 0.4   |       |       |  |

| (Vout1, Vout2, Vout3)                                                         | CCM: 200mA < $I_{\text{LOAD}}$ < 500mA, $V_{\text{IN}}$ = 3.6V if $V_{\text{OUTNOM}}$ < 2.5V        |       | 0.6   |       |       |  |

|                                                                               | CCM: 200mA < I <sub>LOAD</sub> < 1A, V <sub>IN</sub> = 5.0V if V <sub>OUTNOM</sub> > 2.5V           |       | 0.3   |       |       |  |

| PWM Switch ON-Resistance<br>(Rsw1, Rsw2, Rsw3)                                | I <sub>SW1</sub> , I <sub>SW2</sub> , I <sub>SW3</sub> = +100mA (PMOS)                              |       | 0.217 |       | Ω     |  |

| Maximum Frequency                                                             | Iout1, Iout2, Iout3 = 120mA                                                                         |       | 3     |       | MHz   |  |

| Soft-Start Time                                                               | V <sub>OUT1</sub> , V <sub>OUT2</sub> , V <sub>OUT3</sub> = 90%                                     |       | 150   |       | μs    |  |

| Power Good Threshold                                                          | % of V <sub>NOM</sub>                                                                               | 83    | 90    | 96    | %     |  |

| Power Good Hysteresis                                                         |                                                                                                     |       | 10    |       | %     |  |

| Power Good Pull Down                                                          | V <sub>SNS</sub> = 90% V <sub>NOM</sub> , I <sub>PG</sub> = 1mA                                     |       |       | 200   | mV    |  |

#### Notes:

1. Exceeding the absolute maximum ratings may damage the device.

2. The device is not guaranteed to function outside its operating ratings.

3. Devices are ESD sensitive. Handling precautions are recommended. Human body model,  $1.5k\Omega$  in series with 100pF.

4. Specification for packaged product only.

# Electrical Characteristics<sup>(4)</sup> (Continued)

$T_{A} = +25^{\circ}C; V_{IN} = V_{EN1}, V_{EN2}, V_{EN3} = 3.6V; L1 = L2 = L3 = 1\mu H; C_{OUT1}, C_{OUT2}, C_{OUT3} = 4.7\mu F, unless otherwise specified.$ Bold values indicate  $-40^{\circ}C \le T_{J} \le +125^{\circ}C$ , unless noted.

| Parameter                              | Condition | Min. | Тур. | Max. | Units |

|----------------------------------------|-----------|------|------|------|-------|

| Enable Threshold                       | Turn-On   | 0.5  | 0.9  | 1.2  | V     |

| Enable Input Current                   |           |      | 0.1  | 1    | μA    |

| Overtemperature Shutdown               |           |      | 160  |      | °C    |

| Overtemperature Shutdown<br>Hysteresis |           |      | 20   |      | °C    |

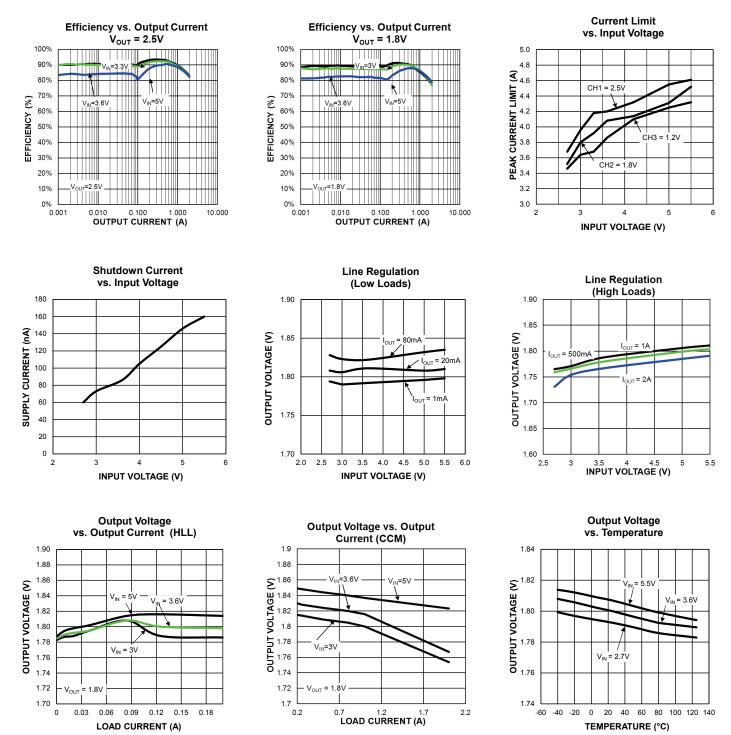

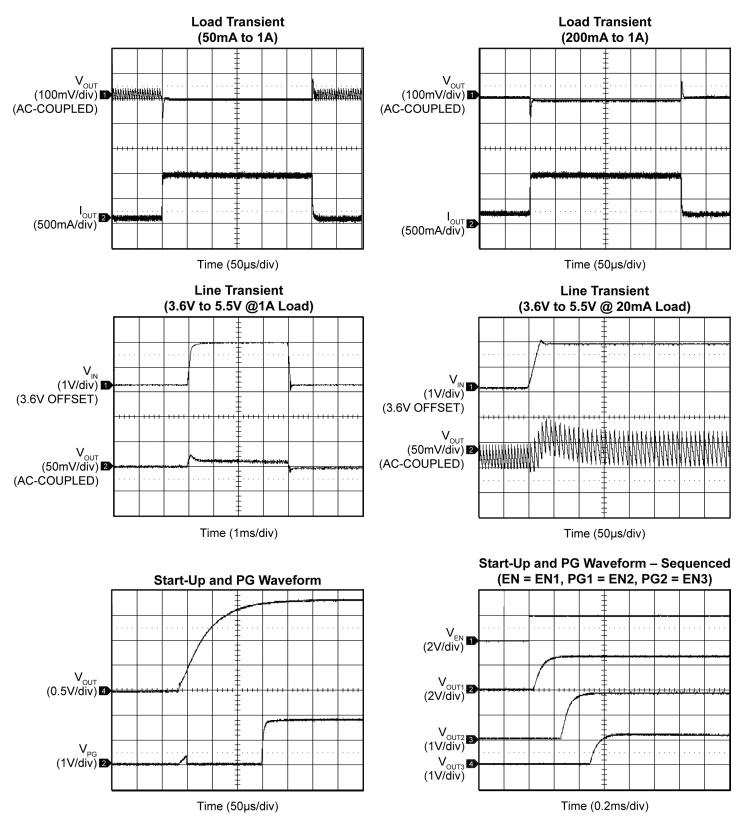

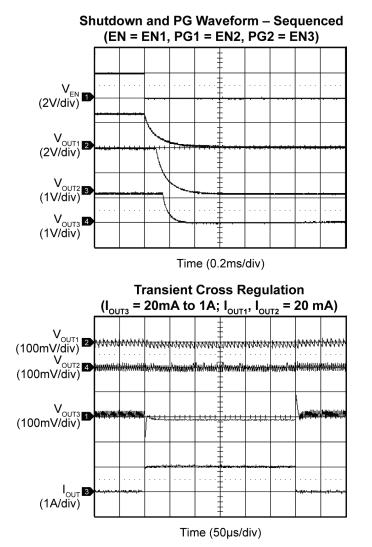

# **Typical Characteristics**

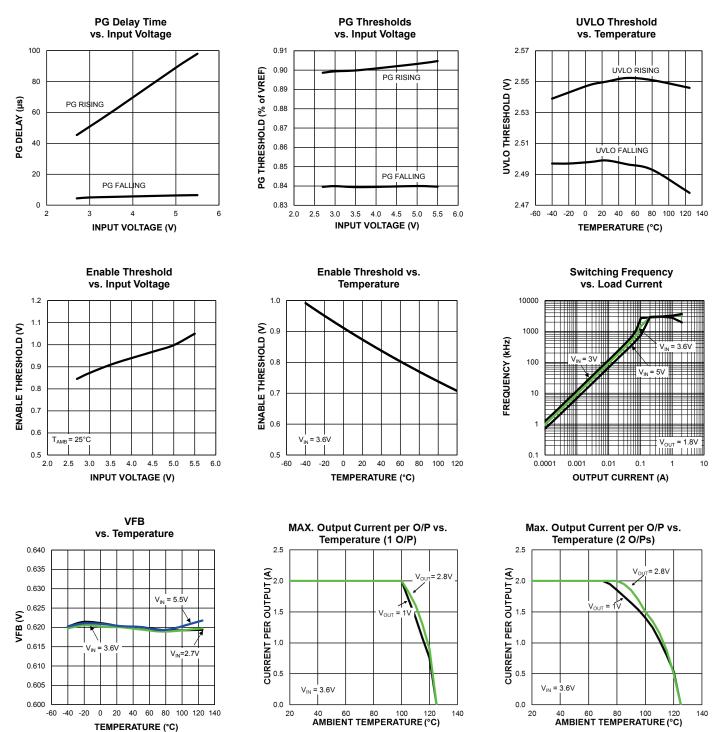

# **Typical Characteristics (Continued)**

## **Typical Characteristics (Continued)**

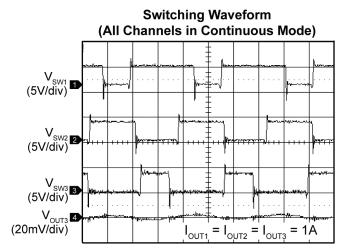

### **Functional Characteristics**

**Functional Characteristics (Continued)**

### **Functional Characteristics (Continued)**

Time (0.1µs/div)

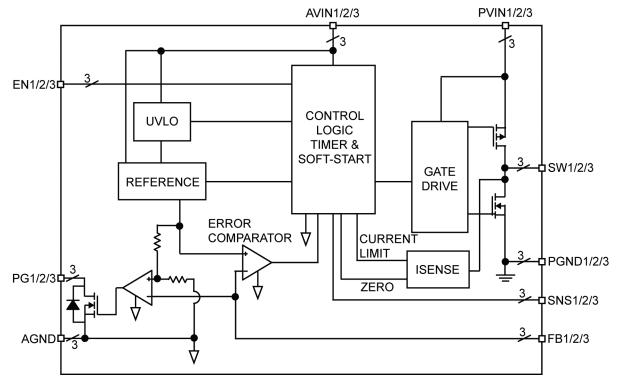

### **Functional Diagram**

Figure 1. Simplified MIC23451 Adjustable Functional Block Diagram

### **Functional Description**

#### PVIN

The input supply (PVIN) provides power to the internal MOSFETs for the switch mode regulator. The V<sub>IN</sub> operating range is 2.7V to 5.5V, so an input capacitor, with a minimum voltage rating of 6.3V is recommended. Because of the high di/dt switching speeds, a minimum 2.2 $\mu$ F or 4.7 $\mu$ F recommended bypass capacitor, placed close to PVIN and the power ground (PGND) pin, is required. Refer to the "PCB Layout Recommendations" section for details.

#### AVIN

The input supply (AVIN) provides power to the internal control circuitry. Because the high di/dt switching speeds on PVIN cause small voltage spikes, a  $50\Omega$  RC filter and a minimum 100nF decoupling capacitor, placed close to the AVIN and signal ground (AGND) pin, is required.

#### EN

A logic high signal on the enable pin (EN) activates the output voltage of the device. A logic low signal on the enable pin deactivates the output and reduces supply current to  $0.01\mu$ A. The MIC23451 features internal softstart circuitry that reduces inrush current and prevents the output voltage from overshooting at start-up. Do not leave the EN pin floating.

#### SW

The switch (SW) connects directly to one end of the inductor and provides the current path during switching cycles. The other end of the inductor is connected to the load, SNS pin, and output capacitor. Because of the high-speed switching on this pin, the switch node should be routed away from sensitive nodes.

#### SNS

The sense (SNS) pin is connected to the output of the device to provide feedback to the control circuitry. The SNS connection should be placed close to the output capacitor. Refer to the "PCB Layout Recommendations" section for more details.

### AGND

The analog ground (AGND) is the ground path for the biasing and control circuitry. The current loop for the signal ground should be separate from the power ground (PGND) loop. Refer to the "PCB Layout Recommendations" section for more details.

### PGND

The power ground pin is the ground path for the high current in PWM mode. The current loop for the power ground should be as short and wide as possible and separate from the analog ground (AGND) loop as applicable. Refer to the "PCB Layout Recommendations" section for more details.

#### PG

The power good (PG) pin is an open-drain output that indicates logic high when the output voltage is typically above 90% of its steady state voltage. A pull-up resistor of more than  $5k\Omega$  should be connected from PG to V<sub>OUT</sub>.

#### FΒ

The feedback (FB) pin is the control input for programming the output voltage. A resistor divider network is connected to this pin from the output and is compared to the internal 0.62V reference within the regulation loop.

The output voltage can be programmed between 1V and 3.3V using Equation 1:

$$V_{OUT} = V_{REF} \times \left(1 + \frac{R1}{R2}\right)$$

Eq. 1

where:

R1 is the top,  $V_{OUT}$  connected resistor R2 is the bottom, AGND connected resistor

Table 1 shows example feedback resistor values.

#### Table 1. Feedback Resistor Values

| Vout | R1   | R2    |

|------|------|-------|

| 1.2V | 274k | 294k  |

| 1.5V | 316k | 221k  |

| 1.8V | 301k | 158k  |

| 2.5V | 324k | 107k  |

| 3.3V | 309k | 71.5k |

### **Application Information**

The MIC23451 is a triple high performance DC-to-DC step down regulator offering a small solution size. Supporting three outputs with currents up to 2A inside a 4mm × 4mm QFN package, the IC requires only five external components per channel while meeting today's miniature portable electronic device needs. Using the HyperLight Load switching scheme, the MIC23451 can maintain high efficiency throughout the entire load range while providing ultra-fast load transient response. The following sections provide additional device application information.

#### Input Capacitor

A 2.2 $\mu$ F or greater ceramic capacitor should be placed close to the PVIN pin for each channel and its corresponding PGND pin for bypassing. For example, the Murata GRM188R60J475ME19D, size 0603, 4.7 $\mu$ F ceramic capacitor is ideal, based on performance, size, and cost. An X5R or X7R temperature rating is recommended for the input capacitor. Y5V temperature rating capacitors, in addition to losing most of their capacitance over temperature, can also become resistive at high frequencies. This reduces their ability to filter out high-frequency noise.

### **Output Capacitor**

The MIC23451 is designed for use with a 2.2µF or greater ceramic output capacitor. Increasing the output capacitance lowers output ripple and improves load transient response, but could also increase solution size or cost. A low equivalent series resistance (ESR) ceramic output capacitor. such as the Murata GRM188R60J475ME84D, size 0603, 4.7µF ceramic capacitor, is recommended based on performance, size, and cost. Both the X7R or X5R temperature rating capacitors are recommended. The Y5V and Z5U temperature rating capacitors are not recommended due to their wide variation in capacitance over temperature and increased resistance at high frequencies.

### Inductor Selection

When selecting an inductor, it is important to consider the following factors (not necessarily in order of importance):

- Inductance

- Rated current value

- Size requirements

- DC resistance (DCR)

The MIC23451 is designed for use with a  $0.47\mu$ H to 2.2 $\mu$ H inductor. For faster transient response, a  $0.47\mu$ H inductor yields the best result. On the other hand, a 2.2 $\mu$ H inductor yields lower output voltage ripple. For the best compromise of these, a  $1\mu$ H is generally recommended.

Maximum current ratings of the inductor are generally given in two forms: permissible DC current and saturation current. Permissible DC current can be rated either for a 40°C temperature rise or a 10% to 20% loss in inductance. Make sure the inductor selected can handle the maximum operating current. When saturation current is specified, make sure that there is enough margin, so that the peak current does not cause the inductor to saturate. Peak current can be calculated as shown in Equation 2:

$$I_{PEAK} = \left[ I_{OUT} + V_{OUT} \left( \frac{1 - V_{OUT} / V_{IN}}{2 \times f \times L} \right) \right]$$

Eq. 2

As Equation 2 shows, the peak inductor current is inversely proportional to the switching frequency and the inductance; the lower the switching frequency or the inductance the higher the peak current. As input voltage increases, the peak current also increases.

The size of the inductor depends on the requirements of the application. Refer to the "Typical Application Schematic" and "Bill of Materials" sections for details.

DC resistance (DCR) is also important. While DCR is inversely proportional to size, DCR can represent a significant efficiency loss. Refer to the "Efficiency Considerations" section.

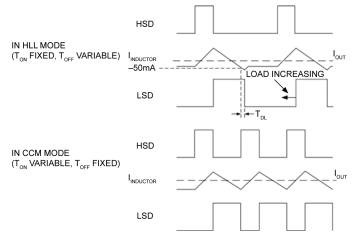

The transition between high loads (CCM) to HyperLight Load (HLL) mode is determined by the inductor ripple current and the load current, as shown in Figure 2.

Figure 2. Transition between CCM Mode and HLL Mode

The diagram shows the signals for high-side switch drive (HSD) for  $T_{ON}$  control, the inductor current, and the low-side switch drive (LSD) for  $T_{OFF}$  control.

In HLL mode, the inductor is charged with a fixed  $T_{ON}$  pulse on the high-side switch (HSD). After this, the LSD is switched on and current falls at a rate of  $V_{OUT}/L$ . The controller remains in HLL mode while the inductor falling

current is detected to cross approximately -50mA. When the LSD (or T<sub>OFF</sub>) time reaches its minimum and the inductor falling current is no longer able to reach this -50mA threshold, the part is in CCM mode and switching at a virtually constant frequency.

Once in CCM mode, the  $T_{OFF}$  time does not vary. Therefore, it is important to note that if L is large enough, the HLL transition level will not be triggered.

That inductor is:

$$L_{MAX} = \frac{V_{OUT} \times 135ns}{2 \times 50mA}$$

Eq. 3

#### Compensation

The MIC23451 is designed to be stable with a 0.47  $\mu H$  to 2.2  $\mu H$  inductor with a 4.7  $\mu F$  ceramic (X5R) output capacitor.

#### **Duty Cycle**

The typical maximum duty cycle of the MIC23451 is 80%.

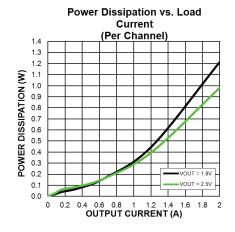

#### **Efficiency Considerations**

Efficiency is defined as the amount of useful output power, divided by the amount of power supplied.

Efficiency % =

$$\left(\frac{V_{OUT} \times I_{OUT}}{V_{IN} \times I_{IN}}\right) \times 100$$

Eq. 4

Maintaining high efficiency serves two purposes. It reduces power dissipation in the power supply, reducing the need for heat sinks and thermal design considerations, and it reduces current consumption for battery-powered applications. Reduced current draw from a battery increases the device's operating time and is critical in hand-held devices.

There are two types of losses in switching converters: DC losses and switching losses. DC losses are the power dissipation of  $I^2R$ . Power is dissipated in the high-side switch during the on cycle. Power loss is equal to the high-side MOSFET R<sub>DSON</sub> multiplied by the switch current squared. During the off cycle, the low-side N-channel MOSFET conducts, also dissipating power. Device operating current also reduces efficiency. The product of the quiescent (operating) current and the supply voltage represents another DC loss. The current required to drive the gates on and off at a constant 4MHz frequency, and the switching transitions, make up the switching losses.

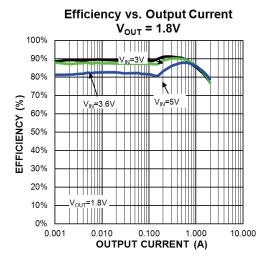

Figure 3. Efficiency under Load

Figure 3 shows an efficiency curve. From no load to 100mA, efficiency losses are dominated by quiescent current losses, gate drive, and transition losses. By using the HyperLight Load mode, the MIC23451 can maintain high efficiency at low output currents.

Over 100mA, efficiency loss is dominated by MOSFET  $R_{DSON}$  and inductor losses. Higher input supply voltages will increase the gate-to-source voltage on the internal MOSFETs, thereby reducing the internal  $R_{DSON}$ . This improves efficiency by reducing DC losses in the device. All but the inductor losses are inherent to the device. Because of this, inductor selection becomes increasingly critical in efficiency calculations. As the inductors are reduced in size, the DC resistance (DCR) can become very significant. The DCR losses can be calculated as shown in Equation 5.

$$P_{DCR} = I_{OUT}^2 \times DCR$$

Eq. 5

From that, the loss in efficiency caused by inductor resistance can be calculated as shown in Equation 6.

Efficiency Loss =

$$\left[1 - \left(\frac{V_{OUT} \times I_{OUT}}{V_{OUT} \times I_{OUT} + P_{DCR}}\right)\right] \times 100$$

Eq. 6

Efficiency loss caused by DCR is minimal at light loads and gains significance as the load is increased. Inductor selection becomes a trade-off between efficiency and size in this case.

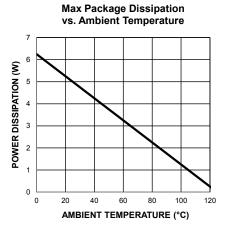

#### **Thermal Considerations**

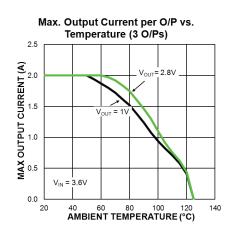

Most applications will not require 2A continuous current from all outputs at all times, so it is useful to know what the thermal limits are for various loading profiles.

The allowable overall package dissipation is limited by the intrinsic thermal resistance of the package ( $R\theta_{(J-C)}$ ) and the area of copper used to spread heat from the package case to the ambient surrounding temperature ( $R\theta_{(C-A)}$ ). The composite of these two thermal resistances is  $R\theta_{(J-A)}$ , which represents the package thermal resistance with at least 1 square inch of copper ground plane. From this figure, which for the MIC23451 is 20°C/W, we can calculate maximum internal power dissipation, as shown in Equation 7:

$$PD_{MAX} = \frac{T_{JMAX} - T_{AMB}}{R\theta} Eq. 7$$

where:

$T_{JMAX}$  = Maximum junction temp (125°C)

T<sub>AMB</sub> = Ambient temperature

$R\theta_{(J-A)} = 20^{\circ}C/W$

The allowable dissipation tends towards zero as the ambient temperature increases towards the maximum operating junction temperature.

The graph of  $PD_{MAX}$  vs. ambient temperature could be drawn quite simply using this equation. However, a more useful measure is the maximum output current per regulator vs. ambient temperature. This requires creating an 'exchange rate' between power dissipation per regulator ( $P_{DISS}$ ) and its output current ( $I_{OUT}$ ).

An accurate measure of this function can use the efficiency curve, as illustrated in Equation 8:

$$\eta = \frac{P_{out}}{P_{out} + P_{LOSS}}$$

Eq. 8

$$P_{LOSS} = \frac{P_{out}(1 - \eta)}{\eta}$$

where:

$\eta$  = Efficiency

$$P_{OUT} = I_{OUT} V_{OUT}$$

To arrive at the internal package dissipation  $P_{\text{DISS}}$ , remove the inductor loss  $P_{\text{DCR}}$ , which is not dissipated within the package. This does not give a worst case figure because efficiency is typically measured on a nominal part at nominal temperatures. The  $I_{\text{OUT}}$  to  $P_{\text{DISS}}$  function used in this case is a synthesized  $P_{\text{DISS}}$ , which accounts for worst case values at maximum operating temperature, as shown in Equation 9.

$$P_{\text{DISS}} = I_{\text{OUT}}^{2} \left( R_{\text{DSON}\_P} \times \frac{V_{\text{OUT}}}{V_{\text{IN}}} + R_{\text{DSON}\_N} \times \left( 1 - \frac{V_{\text{OUT}}}{V_{\text{IN}}} \right) \right)$$

Eq. 9

where:

$R_{DSON\_P}$  = Maximum  $R_{DSON}$  of the high-side, P-Channel switch at  $T_{JMAX}$

$R_{DSON_N}$  = Maximum  $R_{DSON}$  of the low-side, N-Channel switch at  $T_{JMAX}$

V<sub>OUT</sub> = Output voltage

V<sub>IN</sub> = Input voltage

Because ripple current and switching losses are small with respect to resistive losses at maximum output current, they can be considered negligible for the purpose of this method, but could be included if required.

Using the function describing  $P_{DISS}$  in terms of  $I_{OUT}$ , substitute  $P_{DISS}$  with Equation 7 to form the function of maximum output current  $I_{OUTMAX}$  vs. ambient temperature  $T_{AMB}$  (Equation 10):

$$I_{OUTMAX} = \sqrt{\frac{\frac{T_{JMAX} - T_{AMB}}{R\theta_{(J-A)}}}{R_{DSON_P} \times \frac{V_{OUT}}{V_{IN}} + R_{DSON_N} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right)}}$$

Eq. 10

The curves shown in the "Typical Characteristics" section are plots of this function adjusted to account for 1, 2, or 3 regulators running simultaneously.

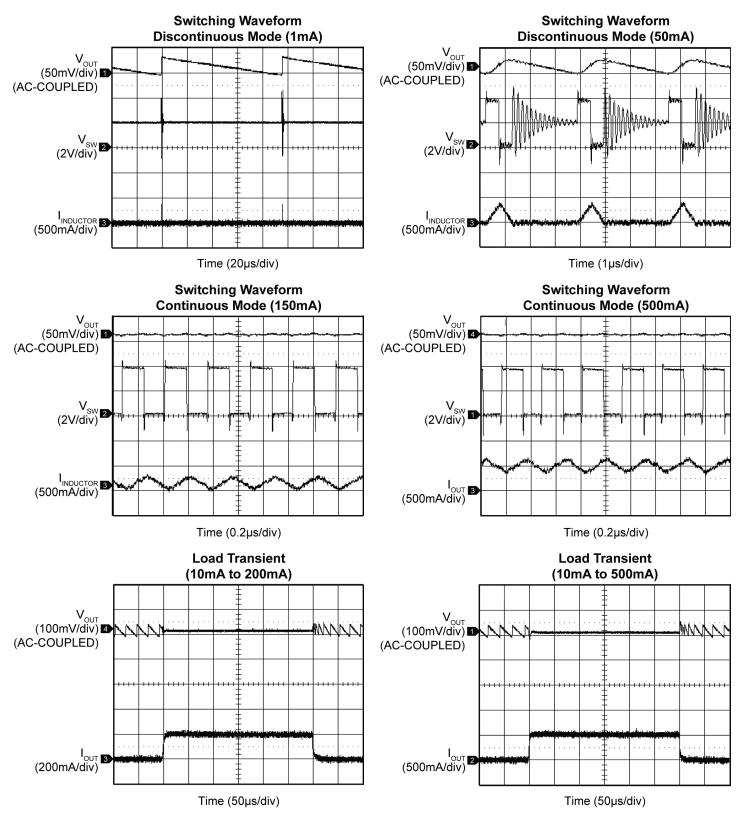

#### HyperLight Load Mode

Each regulator in the MIC23451 uses a minimum on and off time proprietary control loop (patented by Micrel). When the output voltage falls below the regulation threshold, the error comparator begins a switching cycle that turns the PMOS on and keeps it on for the duration of the minimum-on-time. This increases the output voltage. If the output voltage is over the regulation threshold, then the error comparator turns the PMOS off for a minimum-off-time until the output drops below the threshold. The NMOS acts as an ideal rectifier that conducts when the PMOS is off. Using an NMOS switch instead of a diode allows for lower voltage drop across the switching device when it is on. The asynchronous switching combination between the PMOS and the NMOS allows the control loop to work in discontinuous mode for light load operations. In discontinuous mode, the MIC23451 works in pulse-frequency modulation (PFM) to regulate the output. As the output current increases, the off-time decreases, which provides more energy to the output. This switching scheme improves the efficiency of MIC23451 during light load currents by switching only when it is needed. As the load current

November 5, 2013

Downloaded from: http://www.datasheetcatalog.com/

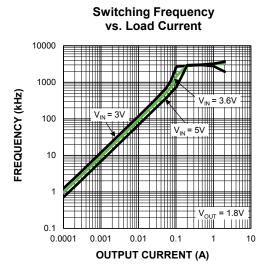

increases, the MIC23451 goes into continuous conduction mode (CCM) and switches at a frequency centered at 3MHz. The equation to calculate the load when the MIC23451 goes into continuous conduction mode is approximated in Equation 11.

$$I_{LOAD} > \left(\frac{(V_{IN} - V_{OUT}) \times D}{2L \times f}\right)$$

Eq. 11

As shown in Equation 11, the load at which the MIC23451 transitions from HyperLight Load mode to PWM mode is a function of the input voltage ( $V_{IN}$ ), output voltage ( $V_{OUT}$ ), duty cycle (D), inductance (L), and frequency (f). Figure 4 shows that as the output current increases, the switching frequency also increases until the MIC23451 goes from HyperLight Load mode to PWM mode at approximately 120mA. The MIC23451 will switch at a relatively constant frequency around 3MHz after the output current is over 120mA.

Figure 4. SW Frequency vs. Output Current

#### **Multiple Sources**

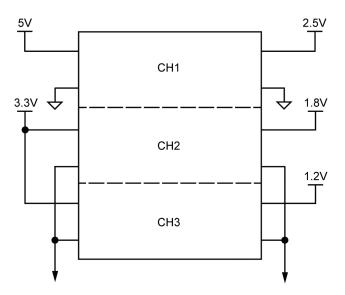

The MIC23451 provides all the pins necessary to operate the three regulators from independent sources. This can be useful in partitioning power within a multi-rail system. For example, two supplies may be available within a system: 3.3V and 5V. The MIC23451 can be connected to use the 3.3V supply to provide two, low-voltage outputs (for example, 1.2V and 1.8V) and use the 5V rail to provide a higher output (for example, 2.5V), resulting in the power blocks shown in Figure 5.

Figure 5. Multi-Source Power Block Diagram

# **Typical Application Schematic**

### **Bill of Materials**

| Item                      | Part Number        | Manufacturer                | Description                                                     | Qty. |  |

|---------------------------|--------------------|-----------------------------|-----------------------------------------------------------------|------|--|

| C1, C2, C3                | GRM188R60J106KE19D | Murata <sup>(1)</sup>       | Capacitor, 10µF, Size 0603                                      | 3    |  |

| 04.05.00.07               | C1608X5R0J475K     | TDK <sup>(2)</sup>          |                                                                 | 4    |  |

| C4, C5, C6, C7            | GRM188R60J475KE19D | Murata                      | Capacitor, 4.7µF, Size 0603                                     | 4    |  |

| C8                        | EEUFR1A221         | Panasonic <sup>(3)</sup>    | Electrolytic Capacitor, 220µF, 10V, Size 6.3mm                  |      |  |

| R1, R2, R3, R4,<br>R5, R6 | CRCW060310K0FKEA   | Vishay <sup>(4)</sup>       | Resistor, 10KΩ, Size 0603                                       | 6    |  |

| R7                        | CRCW0603301K0FKEA  | Vishay                      | Resistor, 301KΩ, Size 0603                                      | 1    |  |

| R8                        | CRCW0603158K0FKEA  | Vishay                      | Resistor, 158KΩ, Size 0603                                      | 1    |  |

| R9                        | CRCW0603316K0FKEA  | Vishay                      | Resistor, 316Ω, Size 0603                                       | 1    |  |

| R10                       | CRCW0603331K0FKEA  | Vishay                      | Resistor, 331KΩ, Size 0603                                      | 1    |  |

| R11                       | CRCW0603294K0FKEA  | Vishay                      | Resistor, 294KΩ, Size 0603                                      | 1    |  |

| R12                       | CRCW0603274K0FKEA  | Vishay                      | Resistor, 274KΩ, Size 0603                                      | 1    |  |

| VLS3012ST-1R0N1R9         |                    | TDK                         | 1μH, 2A, 60mΩ, L3.0mm x W3.0mm x H1.0mm                         |      |  |

| L1, L2, L3                | LQH44PN1R0NJ0      | Murata                      | 1μH, 2.8A, 50mΩ, L4.0mm x W4.0mm x H1.2mm                       | 3    |  |

| U1                        | MIC23451-AAAYFL    | Micrel, Inc. <sup>(5)</sup> | 3MHz PWM 2A Buck Regulator with HyperLight <sup>®</sup><br>Load | 1    |  |

Notes:

1. TDK: <u>www.tdk.com</u>.

2. Murata Tel: <u>www.murata.com</u>.

3. Panasonic: www.panasonic.com.

4. Vishay Tel: <u>www.vishay.com</u>.

5. Micrel, Inc.: <u>www.micrel.com</u>.

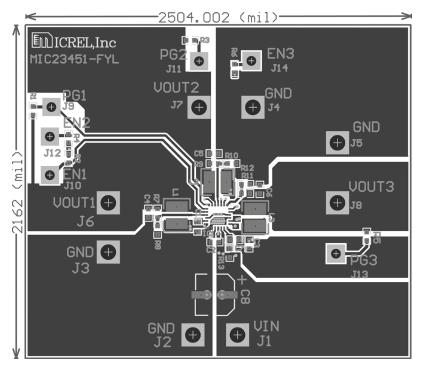

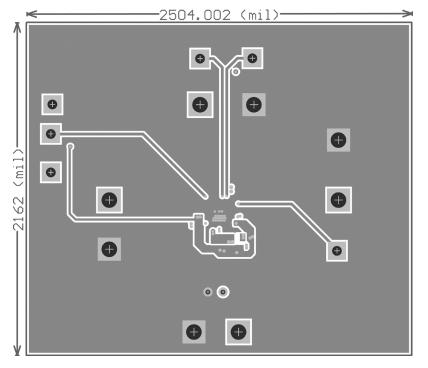

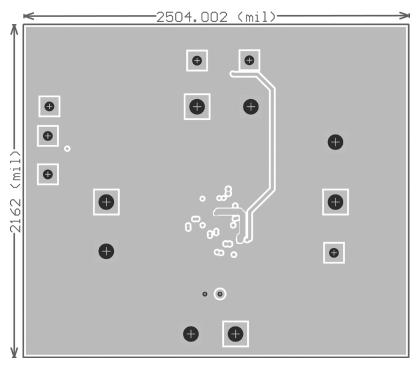

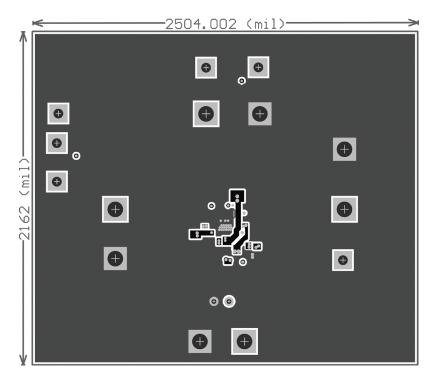

### **PCB Layout Recommendations**

**Top Layer**

Mid Layer 1

Mid Layer 2

**Bottom Layer**

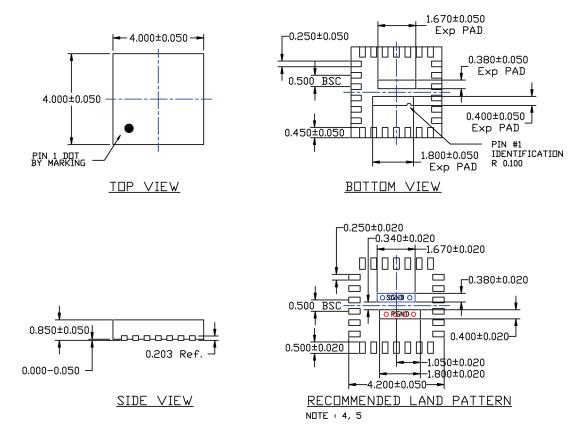

### Package Information<sup>(1)</sup>

<u>NDTE</u> :

- 1. Max package warpage is 0.05mm

- 2. Max allowable burr is 0.076mm in all directions

- 3. Pin #1 will be laser marked

- 4. Red circle in PGND indicate thermal via. Size should be 0.20mm in diameter, 0.40mm pitch and should be connected to GND for max thermal performance.

- 5. Blue colored pad & circle indicate SGND, do not connect to GND.

#### 26-Pin 4mm × 4mm QFN (FL)

#### Note:

1. Package information is correct as of the publication date. For updates and most current information, go to www.micrel.com.

### MICREL, INC. 2180 FORTUNE DRIVE SAN JOSE, CA 95131 USA

TEL +1 (408) 944-0800 FAX +1 (408) 474-1000 WEB http://www.micrel.com

Micrel makes no representations or warranties with respect to the accuracy or completeness of the information furnished in this data sheet. This information is not intended as a warranty and Micrel does not assume responsibility for its use. Micrel reserves the right to change circuitry, specifications and descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Micrel's terms and conditions of sale for such products, Micrel assumes no liability whatsoever, and Micrel disclaims any express or implied warranty relating to the sale and/or use of Micrel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is a Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2013 Micrel, Incorporated.