# EV20073DH-00A

2A, 1.30V - 6.0V

## **DDR Memory VTT Termination Regulator**

#### **DESCRIPTION**

The MP20073 integrates the DDR memory termination regulator with the output voltage (VTT) and a buffered VTTREF whose output is half of VREF.

The VTT-LDO is a 2A sink/source tracking termination regulator. It is specifically designed for low-cost/low-external component count systems, where space is a premium.

The MP20073 maintains a fast transient response only requiring 20uF (2x10uF) of ceramic output capacitance. The MP20073 supports Kelvin sensing functions.

The MP20073 is available in the 8-pin MSOP with Exposed PAD, package and is specified from -40°C to 85°C.

#### **ELECTRICAL SPECIFICATIONS**

| Parameter                  | Symbol          | Value                | Units |

|----------------------------|-----------------|----------------------|-------|

| Input Bias Voltage         | $V_{DRV}$       | 3.3                  | V     |

| Input Voltage              | $V_{DDQ}$       | 1.3-1.8              | V     |

| Reference Input<br>Voltage | $V_{REF}$       | $V_{DDR}$            | V     |

| Output Voltage             | V <sub>TT</sub> | 1/2 V <sub>DDR</sub> | V     |

| Output Current             | I <sub>TT</sub> | ±2                   | Α     |

#### **FEATURES**

- VDDQ Voltage Range: 1.3V to 6.0 V

- Up to 2A Integrated Sink/Source Linear Regulator with Accurate VDDQ/2 Divider Reference for DDR Termination

- Requires Only 20uF Ceramic Output Capacitance

- Drive Voltage Range: 3.3V

- 1.3V Input (VDDQ) Helps Reduce Total Power Dissipation

- Integrated Divider Tracks VREF for VTT and VTTREF

- Kelvin Sensing (VTTSEN)

- ±30mV Accuracy for VTT and VTTREF

- Built-In Soft-Start, UVLO and OCL

- Thermal Shutdown

#### **APPLICATIONS**

- Notebook DDR2/3 Memory Supply and Termination Voltage in ACPI Compliant

- Active Termination Busses

"MPS" and "The Future of Analog IC Technology", are Trademarks of Monolithic Power Systems, Inc.

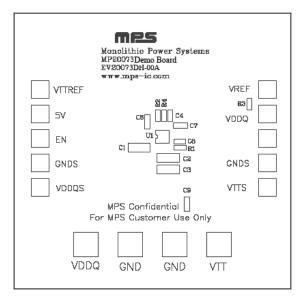

#### **EV20073DH-00A EVALUATION BOARD**

(L x W x H) 2.5" x 2.5" x 0.5" (6.5cm x 6.5cm x 1.2cm)

| Board Number  | MPS IC Number |  |  |

|---------------|---------------|--|--|

| EV20073DH-00A | MP20073DH     |  |  |

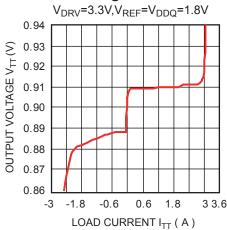

### **Load Regulation**

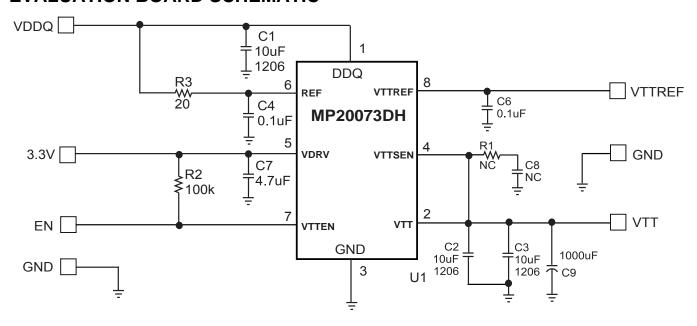

## **EVALUATION BOARD SCHEMATIC**

## **EV20073DH-00A BILL OF MATERIALS**

| Qty | Ref           | Value | Description            | Package | Manufacturer | Manufacturer P/N   |

|-----|---------------|-------|------------------------|---------|--------------|--------------------|

| 3   | C1, C2,<br>C3 | 10uF  | Ceramic Cap., 16V, X7R | 1206    | muRata       | GRM31CR71C106KAC7L |

| 2   | C4,C6         | 0.1uF | Ceramic Cap., 16V, X7R | 0603    | muRata       | GRM188R71C104KA01D |

| 1   | C7            | 4.7uF | Ceramic Cap., 16V, X7R | 0805    | muRata       | GRM21BR71C475KA73L |

| 1   | C8, C9        | NS    |                        | 0603    |              |                    |

| 1   | R1            | NS    |                        | 0603    |              |                    |

| 1   | R2            | 100ΚΩ | Film Res., 5%          | 0603    | Yageo        | RC0603JR-07100KL   |

| 1   | R3            | 0     | Film Res., 5%          | 0603    | Yageo        | 9C06031A0R00JL     |

| 1   | R4            | 20    | Film Res., 5%          | 0603    | Yageo        | 9C06031A20R0JLHFT  |

| 1   | U1            |       | Termination Regulator  | MSOP8   | MPS          | MP20073DH          |

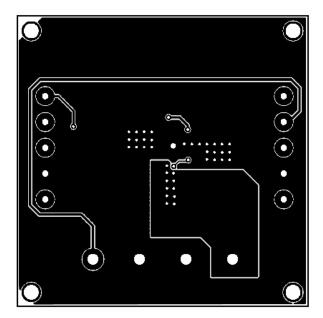

## PRINTED CIRCUIT BOARD LAYOUT

Figure 2—Top Layer

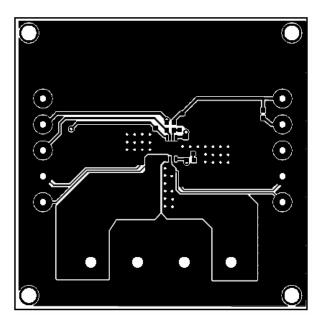

Figure 3—Bottom Layer

#### **QUICK START GUIDE**

The output voltage of this board is set by VREF voltage. The EN pin is connected to VDRV with a  $100K\Omega$  resistor for automatic startup. You can connect EN to GND to disable the MP20073.

- 1. Attach the positive and negative ends of the load to the VTT and GND pins, respectively.

- 2. Attach the input voltage (1.5V ≤ VDDQ ≤ 5V) and input ground to the VDDQ and GND pins, respectively. (the VREF and VDDQ is directly connected together by R3)

- 3. Attach the VDRV voltage 3.3V and ground to the VDRV and GND pins, respectively.

- 4. The VTT output voltage is 1/2 of VREF/VDDQ.

**NOTICE:** The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.