## **PCU9669**

# Parallel bus to 1 channel Fm+ and 2 channel UFm I<sup>2</sup>C-bus controller

Rev. 2 — 1 July 2011

Product data sheet

### 1. General description

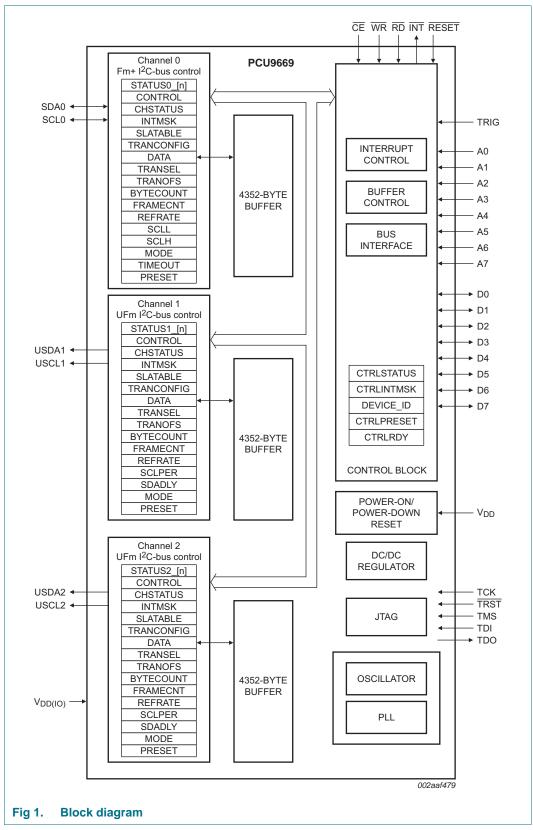

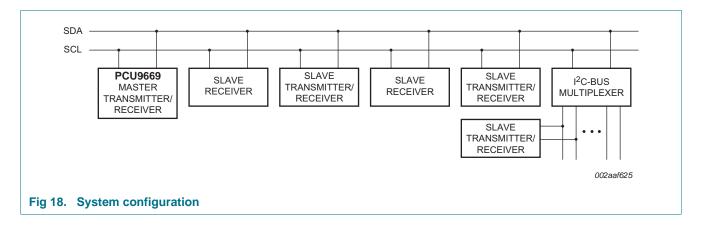

The PCU9669 is an advanced single master mode I<sup>2</sup>C-bus controller. It is a fourth generation bus controller designed for data intensive I<sup>2</sup>C-bus data transfers. It has three independent I<sup>2</sup>C-bus channels, one of them with data rates up to 1 Mbits/s using the Fast-mode Plus (Fm+) open-drain topology and two with a much larger transmit only transfer rate of up to 5 Mbits/s using the new Ultra Fast-mode (UFm) bus with push-pull topology. Each channel has a generous 4352 byte data buffer which makes the PCU9669 the ideal companion to any CPU that needs to transmit and receive large amounts of serial data with minimal interruptions.

The PCU9669 is a 8-bit parallel-bus to I<sup>2</sup>C-bus protocol converter. It can be configured to communicate with up to 64 slaves in one serial sequence with no intervention from the CPU. The controller also has a sequence loop control feature that allows it to automatically retransmit a stored sequence.

Its onboard oscillator and PLL allow the controller to generate the clocks for the I<sup>2</sup>C-bus and for the interval timer used in sequence looping. This feature greatly reduces CPU overhead when data refresh is required in fault tolerant applications.

An external trigger input allows data synchronization with external events. The trigger signal controls the rate at which a stored sequence is re-transmitted over the I<sup>2</sup>C-bus.

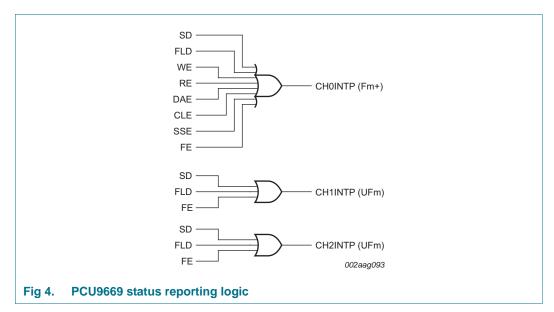

Error reporting is handled at the transaction level, channel level, and controller level. A simple interrupt tree and interrupt masks allow further customization of interrupt management.

The controller parallel bus interface runs at 3.3 V and the  $I^2C$ -bus I/Os logic levels are referenced to a dedicated  $V_{DD(IO)}$  input pin with a range of 3.0 V to 5.5 V.

### 2. Features and benefits

- Parallel-bus to I<sup>2</sup>C-bus protocol converter and interface

- 5 Mbit/s unidirectional data transfer on Ultra Fast-mode (UFm) channel (push-pull driver)

- 1 Mbit/s and up to 30 mA SCL/SDA I<sub>OL</sub> Fast-mode Plus (Fm+) capability

- Internal oscillator trimmed to 1 % accuracy reduces external components

- Individual 4352-byte buffers for the Fm+ and UFm channels for a total of 13056 bytes of buffer space

- Three levels of reset: individual software channel reset, global software reset, global hardware RESET pin

- Communicates with up to 64 slaves in one serial sequence

### Parallel bus to 1 channel Fm+ and 2 channel UFm I<sup>2</sup>C-bus controller

- Sequence looping with interval timer

- Supports SCL clock stretching (Fm+ only)

- JTAG port available for boundary scan testing during board manufacturing process

- Trigger input synchronizes serial communication exactly with external events

- Maskable interrupts

- Fast-mode Plus I<sup>2</sup>C-bus capable and compatible with SMBus

- Operating supply voltage: 3.0 V to 3.6 V (device and host interface)

- I<sup>2</sup>C-bus I/O supply voltage: 3.0 V to 5.5 V

- Latch-up testing is done to JEDEC Standard JESD78 which exceeds 100 mA

- ESD protection exceeds 8000 V HBM per JESD22-A114 and 1000 V CDM per JESD22-C101

- Packages offered: LQFP48

### 3. Applications

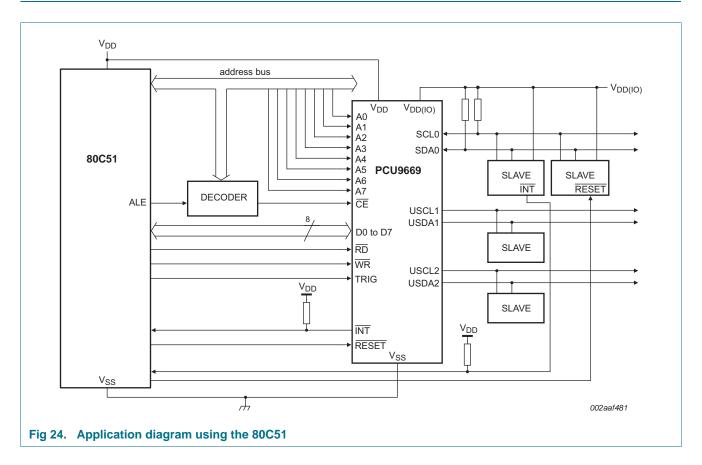

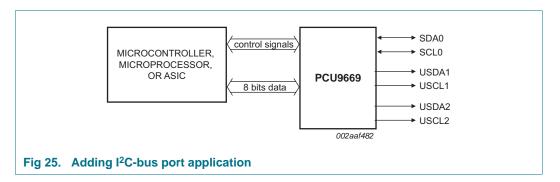

- Add I<sup>2</sup>C-bus port to controllers/processors that do not have one

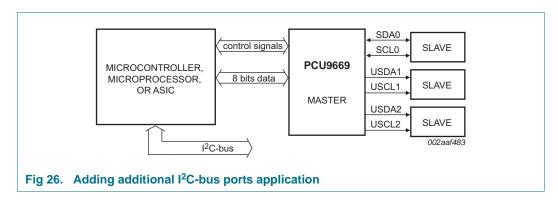

- Add additional I<sup>2</sup>C-bus ports to controllers/processors that need multiple I<sup>2</sup>C-bus ports

- Converts 8 bits of parallel data to serial data stream to prevent having to run a large number of traces across the entire printed-circuit board

- Entertainment systems

- LED matrix control

- Data intensive I<sup>2</sup>C-bus transfers

### 4. Ordering information

Table 1. Ordering information

| Type number | Topside | Package |                                                                         |          |  |  |  |  |  |

|-------------|---------|---------|-------------------------------------------------------------------------|----------|--|--|--|--|--|

|             | mark    | Name    | Description                                                             | Version  |  |  |  |  |  |

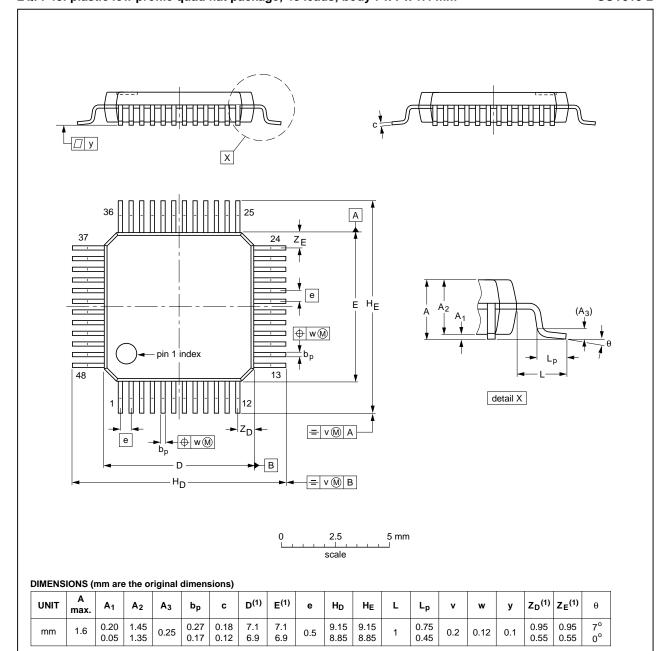

| PCU9669B    | PCU9669 | LQFP48  | plastic low profile quad flat package;<br>48 leads; body 7 × 7 × 1.4 mm | SOT313-2 |  |  |  |  |  |

### Parallel bus to 1 channel Fm+ and 2 channel UFm I<sup>2</sup>C-bus controller

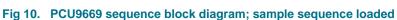

### 5. Block diagram

**PCU9669 NXP Semiconductors**

### Parallel bus to 1 channel Fm+ and 2 channel UFm I<sup>2</sup>C-bus controller

#### **Pinning information** 6.

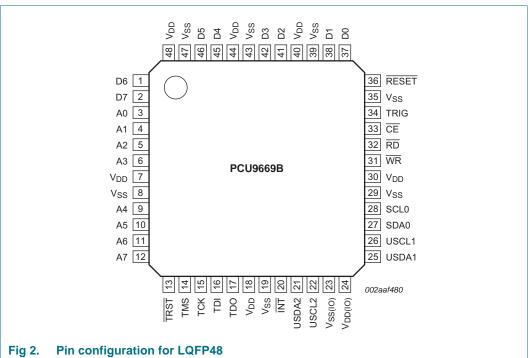

### 6.1 Pinning

### 6.2 Pin description

Table 2. Pin description

| Symbol | Pin | Туре | Description                                                                                                                          |  |  |  |  |  |  |  |

|--------|-----|------|--------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| A0     | 3   | I    | Address inputs: selects the bus controller's internal registers and                                                                  |  |  |  |  |  |  |  |

| A1     | 4   | I    | ports for read/write operations. Address is registered when CE is  LOW and whether WR or RD transitions LOW. A0 is the least         |  |  |  |  |  |  |  |

| A2     | 5   | I    | significant bit.                                                                                                                     |  |  |  |  |  |  |  |

| А3     | 6   | I    | _ <del>-</del>                                                                                                                       |  |  |  |  |  |  |  |

| A4     | 9   | I    |                                                                                                                                      |  |  |  |  |  |  |  |

| A5     | 10  | I    |                                                                                                                                      |  |  |  |  |  |  |  |

| A6     | 11  | I    |                                                                                                                                      |  |  |  |  |  |  |  |

| A7     | 12  | I    |                                                                                                                                      |  |  |  |  |  |  |  |

| D0     | 37  | I/O  | Data bus: bidirectional 3-state data bus used to transfer                                                                            |  |  |  |  |  |  |  |

| D1     | 38  | I/O  | commands, data and status between the bus controller and the host. D0 is the least significant bit. Data is registered on the rising |  |  |  |  |  |  |  |

| D2     | 41  | I/O  | edge of WR when CE is LOW.                                                                                                           |  |  |  |  |  |  |  |

| D3     | 42  | I/O  |                                                                                                                                      |  |  |  |  |  |  |  |

| D4     | 45  | I/O  |                                                                                                                                      |  |  |  |  |  |  |  |

| D5     | 46  | I/O  |                                                                                                                                      |  |  |  |  |  |  |  |

| D6     | 1   | I/O  |                                                                                                                                      |  |  |  |  |  |  |  |

| D7     | 2   | I/O  |                                                                                                                                      |  |  |  |  |  |  |  |

### Parallel bus to 1 channel Fm+ and 2 channel UFm I<sup>2</sup>C-bus controller

Table 2.

Pin description ...continued

| Symbol              | Pin                             | Туре            | Description                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------------|---------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TRST                | 13                              | I               | JTAG test reset input. For normal operation, hold LOW (V <sub>SS</sub> ).                                                                                                                                                                                                                                                                                                                    |

| TMS                 | 14                              | I               | <b>JTAG test mode select input.</b> For normal operation, hold HIGH $(V_{DD})$ .                                                                                                                                                                                                                                                                                                             |

| TCK                 | 15                              | I               | <b>JTAG test clock input.</b> For normal operation, hold HIGH ( $V_{DD}$ ).                                                                                                                                                                                                                                                                                                                  |

| TDI                 | 16                              | I               | <b>JTAG test data in input.</b> For normal operation, hold HIGH ( $V_{DD}$ ).                                                                                                                                                                                                                                                                                                                |

| TDO                 | 17                              | 0               | <b>JTAG test data out output.</b> For normal operation, do not connect (n.c.).                                                                                                                                                                                                                                                                                                               |

| ĪNT                 | 20                              | 0               | <b>Interrupt request:</b> Active LOW, open-drain, output. This pin requires a pull-up device.                                                                                                                                                                                                                                                                                                |

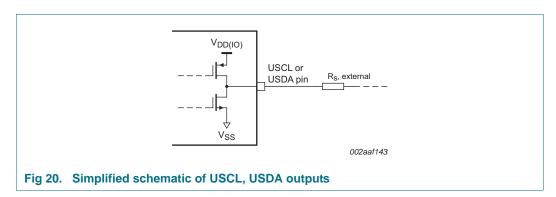

| USDA2               | 21                              | 0               | Channel 2 Ultra Fast-mode I <sup>2</sup> C-bus serial data output. Push-pull drive. No pull-up device is needed.                                                                                                                                                                                                                                                                             |

| USCL2               | 22                              | 0               | Channel 2 Ultra Fast-mode I <sup>2</sup> C-bus serial clock output. Push-pull drive. No pull-up device is needed.                                                                                                                                                                                                                                                                            |

| USDA1               | 25                              | 0               | Channel 1 Ultra Fast-mode I <sup>2</sup> C-bus serial data output. Push-pull drive. No pull-up device is needed.                                                                                                                                                                                                                                                                             |

| USCL1               | 26                              | 0               | Channel 1 Ultra Fast-mode I <sup>2</sup> C-bus serial clock output. Push-pull drive. No pull-up device is needed.                                                                                                                                                                                                                                                                            |

| SDA0                | 27                              | I/O             | Channel 0 l <sup>2</sup> C-bus serial data input/output (open-drain). This pin requires a pull-up device.                                                                                                                                                                                                                                                                                    |

| SCL0                | 28                              | I/O             | Channel 0 I <sup>2</sup> C-bus serial clock input/output (open-drain). This pin requires a pull-up device.                                                                                                                                                                                                                                                                                   |

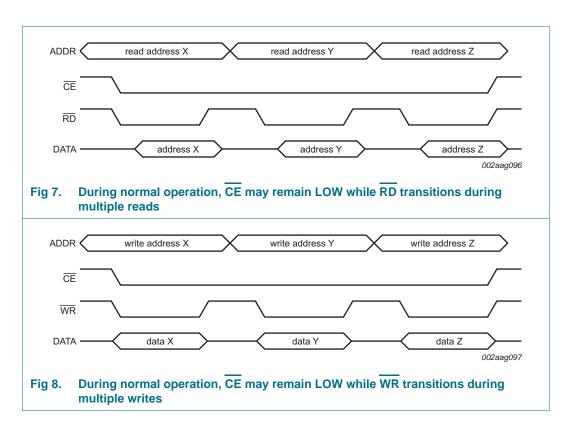

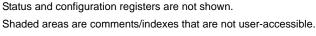

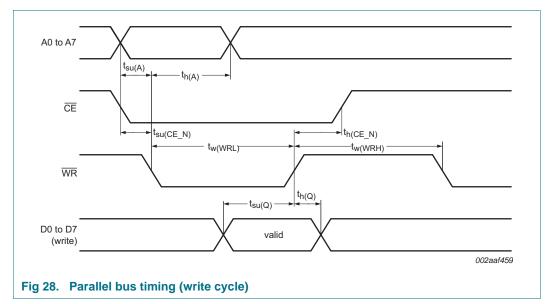

| WR                  | 31                              | I               | Write strobe: When LOW and $\overline{\text{CE}}$ is also LOW, the content of the data bus is loaded into the addressed register. Data are latched on the rising edge of $\overline{\text{WR}}$ . $\overline{\text{CE}}$ may remain LOW or transition with $\overline{\text{WR}}$ .                                                                                                          |

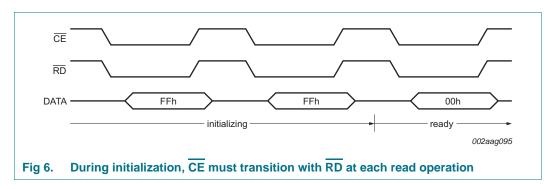

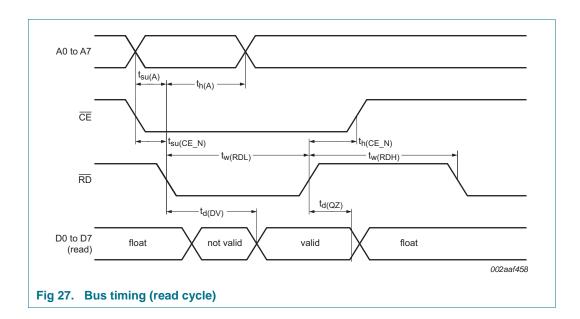

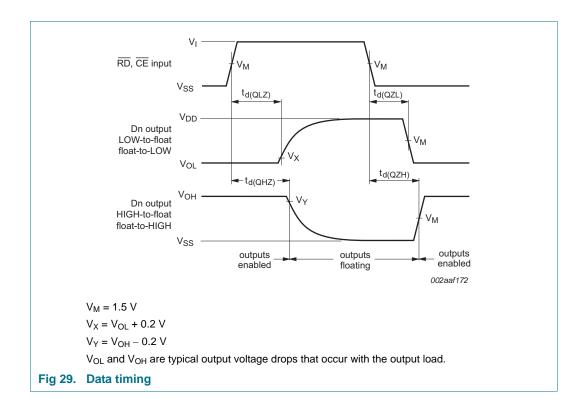

| RD                  | 32                              | I               | Read strobe: When LOW and $\overline{CE}$ is also LOW, causes the contents of the addressed register to be presented on the data bus. The read cycle begins on the falling edge of $\overline{RD}$ . Data lines are driven when $\overline{RD}$ and $\overline{CE}$ are LOW. $\overline{CE}$ may transition with $\overline{RD}$ .                                                           |

| CE                  | 33                              | I               | Chip Enable: Active LOW input signal. When LOW, data transfers between the host and the bus controller are enabled on D0 to D7 as controlled by the $\overline{WR}$ , $\overline{RD}$ and A0 to A7 inputs. When HIGH, places the D0 to D7 lines in the 3-state condition.  During the initialization period, $\overline{CE}$ must transition with $\overline{RD}$ until controller is ready. |

| TRIG                | 34                              | I               | Trigger input: provides the trigger to start a new frame.                                                                                                                                                                                                                                                                                                                                    |

| RESET               | 36                              | I               | <b>Reset:</b> Active LOW input. A LOW level resets the device to the power-on state. Internally pulled HIGH through weak pull-up current.                                                                                                                                                                                                                                                    |

| V <sub>DD(IO)</sub> | 24                              | power           | <b>I/O power supply:</b> 3.0 V to 5.5 V. Power supply reference for $I^2$ C-bus pins. Sets the voltage reference point for $V_{IL}/V_{IH}$ and the output drive rail for the UFm channel.                                                                                                                                                                                                    |

| $V_{SS(IO)}$        | 23                              | power           | <b>I/O supply ground.</b> Can be tied to V <sub>SS</sub> .                                                                                                                                                                                                                                                                                                                                   |

| $V_{DD}$            | 7, 18, 30,<br>40, 44, 48        | power           | Power supply: 3.0 V to 3.6 V. All $\ensuremath{V_{DD}}$ pins should be connected together externally.                                                                                                                                                                                                                                                                                        |

| $V_{SS}$            | 8, 19, 29,<br>35, 39,<br>43, 47 | power           | Supply ground. All $V_{\text{SS}}$ pins should be connected together externally.                                                                                                                                                                                                                                                                                                             |

|                     | All inform                      | nation provided | in this document is subject to legal disclaimers.  © NXP B.V. 2011. All rights reserved.                                                                                                                                                                                                                                                                                                     |

### Parallel bus to 1 channel Fm+ and 2 channel UFm I<sup>2</sup>C-bus controller

### 7. Functional description

#### 7.1 General

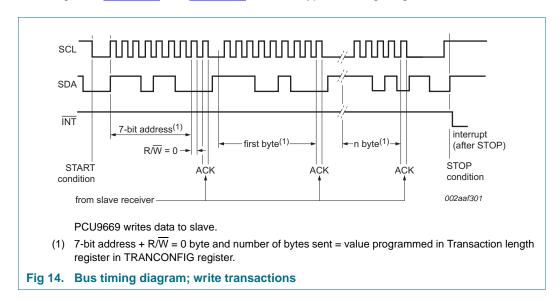

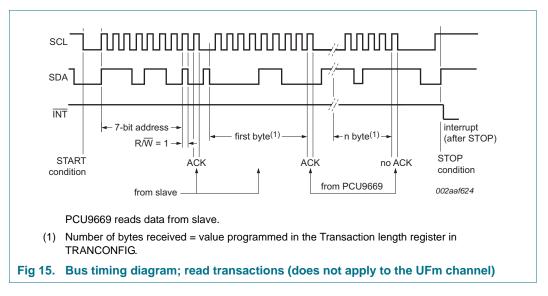

The PCU9669 acts as an interface device between standard high-speed parallel buses and the serial I<sup>2</sup>C-bus. On the I<sup>2</sup>C-bus, it acts as a master. Data transfer between the I<sup>2</sup>C-bus and the parallel-bus host is carried out on a buffered basis, using either an interrupt or polled handshake.

#### 7.2 Internal oscillator and PLL

The PCU9669 contains an internal 12.0 MHz oscillator and 156 MHz PLL which are used for all internal and I<sup>2</sup>C-bus timing. The oscillator and PLL require up to t<sub>init(po)</sub> to start up and lock after power-up. The oscillator is not shut down if the serial bus is disabled.

### 7.3 Buffer description

**Remark:** In the following section a 'transaction' is defined as a contiguous set of commands and/or data sent/received to/from a single slave. A 'sequence' is a set of transactions stored in the buffer.

The PCU9669 channels have individual 4352-byte data buffers (see Section 7.3.2 "Buffer sizes") that allow several transactions to be executed before an interrupt is generated. This allows the host to request several transactions (up to maximum buffer size on each channel) in a single sequence and lets the PCU9669 perform it without the intervention of the host each time a requested transaction is performed. The host can then perform other tasks while the PCU9669 executes the requested sequences.

By following a simple procedure, the I<sup>2</sup>C-bus controller can store several I<sup>2</sup>C-bus transactions directed to different slaves addresses on any of the channels. The transaction stored in the buffer can be of any type, thus reads and writes can be interlaced in a sequence. When multiple slave reads are requested in a sequence, the read data is stored in-line in the sequence and the buffer number must be specified in the TRANSEL to provide the read location and the TRANOFS byte offset value. By default, the TRANOFS is set to 00h. So let us consider the scenario where the host has done the initialization (mode, masks, and other configuration) and writes data into the buffer of one of the three channels.

The host starts by programming the buffer configuration registers TRANCONFIG (number of slaves and bytes per slave) and then the SLATABLE (slave addresses). Then the host programs the TRANSEL (Transaction Data Buffer Selection) and the TRANOFS (byte offset selection) to 00h to set the memory pointers to the beginning of the buffer (the default value is 00h after a power-on or RESET). Next, the host transfers the data into DATA until the entire sequence is loaded. If the transaction is a read transaction, the host must write a dummy byte (i.e., FFh) for each expected serial read byte to reserve the memory space in the buffer for the transaction.

Care should be taken so as to not overflow the buffer with excessive read/write commands. In the event of an overflow, represented by the BE bit in the CTRLSTATUS register, will be set to logic 1. The INT pin will be set LOW if the BEMSK bit in the CTRLINTMSK register is logic 0. To recover the channel, a channel reset is required. All configuration and data needs to be checked by the host and resent to the I<sup>2</sup>C-bus controller. (See Section 7.3.2 "Buffer sizes".)

#### Parallel bus to 1 channel Fm+ and 2 channel UFm I<sup>2</sup>C-bus controller

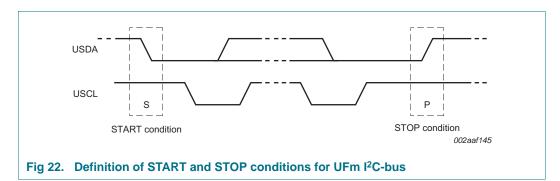

After sending all the commands and data it wanted to the I<sup>2</sup>C-bus controller, the host could either continue to program data for other channels or write to the CONTROL register to begin data transmission on the current channel. The transactions will be sent on the I<sup>2</sup>C-bus in the order in which the slave addresses are listed in the SLATABLE, separated by a RESTART condition. The last transaction in the sequence will end with a STOP condition.

If during a READ command a NACK on the slave address is received, the buffer space allocated for the read will remain untouched and will contain the last information written in that location. A buffer read on the parallel bus should only be done after a valid buffer state is reached to guarantee data valid (see <a href="Section 7.5.1.1"STATUS0\_[n]">SECTION TENTION TENTION

To program data for another channel, that channel is selected and data programmed as described above. One or more channels can be busy with serial transmission while additional parallel-bus data is sent to the buffer of an idle channel.

### 7.3.1 Buffer management assumptions

- Repeated STARTs will be sent between two consecutive transactions.

- After the last operation on a channel is completed, a STOP will be sent.

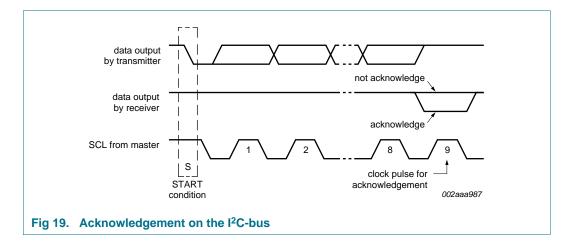

- In a READ transaction, after the last data byte has been received from a particular slave, a NACK is sent to the slave.

#### 7.3.2 Buffer sizes

The PCU9669 channels have individual buffers assigned to them. The contents of the buffers should only be modified during channel idle states.

The memory allocation is 4352 bytes per channel.

The buffer sizes represent the memory allocated for the data block only. The slave address table and configuration bytes are contained in other locations and do not need to be included in the required buffer size calculation.

For example, to calculate the size of the memory needed to write 26 bytes to 10 slaves and to read 2 bytes from 4 slaves (no command bytes required for the read):

10 slaves  $\times$  26 bytes/slave = 260 bytes for the write transactions

4 slaves  $\times$  2 bytes/slave = 8 bytes for the read transactions

A total of 268 bytes of buffer space is required to complete the sequence.

**Remark:** Note that the bytes required to store the 30 slave addresses are not included in the calculation since they are stored in the SLATABLE register.

#### Parallel bus to 1 channel Fm+ and 2 channel UFm I<sup>2</sup>C-bus controller

### 7.4 Error reporting and handling

In case of any transaction error conditions, the device will load the transaction error status in the STATUSx\_[n], generate an interrupt, if unmasked, by pulling down the INT pin and update the CHSTATUS and CTRLSTATUS registers. The status for the individual SLA addresses will be stored in the STATUSx\_[n] registers.

In the event of a NACK from a slave, there are two possible courses of action. The first is that an interrupt will be generated and the current transaction and sequence terminated. The second is that while the WEMSK and/or REMSK is a logic 1, a NACKed byte will be ignored, and the transmission will continue with the next transaction in the sequence until the end of the sequence. The controller will skip the slave address and/or data where the NACK occurred and move on to the next transaction in the sequence. Any error will be reported in the corresponding STATUSx\_[n] register (where 'n' is the buffer number of the slave) or the CHSTATUS or CTRLSTATUS registers.

### 7.5 Registers

The PCU9669 contains several registers that are used to configure the operation of the device, status reporting, and to send and receive data. The device also contains global registers for chip level control and status reporting.

The STATUSx\_[n] registers are channel-level direct access registers. The DATA, SLATABLE, TRANCONFIG, and BYTECOUNT registers are auto-increment registers.

The memory access pointer to the DATA registers can be programmed using the TRANSEL and TRANOFS registers. See <u>Section 7.5.1.2 "CONTROL — Control register"</u>, for information on the pointer reset bits BPTRRST and AIPTRRST.

Parallel bus to 1 channel Fm+ and 2 channel UFm I<sup>2</sup>C-bus controller

| Table | e 3.   | PCL    | J <b>9</b> 669                     | ) regi | ster a        | addre | ss m        | ap - direct regist | er access |                                                                   |                                                      |         |                 |

|-------|--------|--------|------------------------------------|--------|---------------|-------|-------------|--------------------|-----------|-------------------------------------------------------------------|------------------------------------------------------|---------|-----------------|

| 7     | 6      | 5      | 4                                  | 3      | 2             | 1     | 0           | Register name      | Access    | Write access while CH active                                      | Description                                          | Default | Size<br>(bytes) |

| Cha   | nnels  | status | regi                               | sters  |               | •     |             | '                  |           |                                                                   |                                                      |         | '               |

| 0     | 0      | char   | nnel (                             |        | sactio<br>ex) | n nun | nber        | STATUS0_[n]        | R         | no                                                                | individual transaction status (direct address)       | 00h     | 64              |

| 0     | 1      | char   | annel 1 transaction numbe<br>(hex) |        |               | nber  | STATUS1_[n] | R                  | no        | individual transaction status (direct address) ([7:2] = 0 in UFm) | 00h                                                  | 64      |                 |

| 1     | 0      | char   | channel 2 transaction number (hex) |        |               | nber  | STATUS2_[n] | R                  | no        | individual transaction status (direct address) ([7:2] = 0 in UFm) | 00h                                                  | 64      |                 |

| Cha   | nnel ( | ) (Fm  | +) re                              | gister | 'S            |       |             |                    |           |                                                                   |                                                      |         |                 |

| 1     | 1      | 0      | 0                                  | 0      | 0             | 0     | 0           | CONTROL            | R/W       | yes[1]                                                            | channel 0 control                                    | 00h     | 1               |

|       |        |        |                                    | 0      | 0             | 0     | 1           | CHSTATUS           | R         | no                                                                | channel 0 status                                     | 00h     | 1               |

| -     |        |        |                                    | 0      | 0             | 1     | 0           | INTMSK             | R/W       | yes                                                               | channel 0 interrupt mask                             | 00h     | 1               |

|       |        |        |                                    | 0      | 0             | 1     | 1           | SLATABLE           | R/W       | no                                                                | channel 0 slave address table (auto-increment)       | 00h     | 64              |

|       |        |        |                                    | 0      | 1             | 0     | 0           | TRANCONFIG         | R/W       | yes, for TRANCOUNT[2]                                             | channel 0 transaction configuration (auto-increment) | 00h     | 65              |

| -     |        |        |                                    | 0      | 1             | 0     | 1           | DATA               | R/W       | yes                                                               | channel 0 data (auto-increment)                      | 00h     | bufsize[3]      |

| -     |        |        |                                    | 0      | 1             | 1     | 0           | TRANSEL            | R/W       | yes                                                               | channel 0 transaction data buffer select             | 00h     | 1               |

|       |        |        |                                    | 0      | 1             | 1     | 1           | TRANOFS            | R/W       | yes                                                               | channel 0 transaction data buffer byte offset        | 00h     | 1               |

| -     |        |        |                                    | 1      | 0             | 0     | 0           | BYTECOUNT          | R         | no                                                                | channel 0 transmitted byte count (auto-increment)    | 00h     | 64              |

|       |        |        |                                    | 1      | 0             | 0     | 1           | FRAMECNT           | R/W       | no                                                                | channel 0 frame count                                | 01h     | 1               |

|       |        |        |                                    | 1      | 0             | 1     | 0           | REFRATE            | R/W       | no                                                                | channel 0 frame refresh rate                         | 00h     | 1               |

|       |        |        |                                    | 1      | 0             | 1     | 1           | SCLL               | R/W       | no                                                                | channel 0 clock LOW state                            | 5Eh     | 1               |

|       |        |        |                                    | 1      | 1             | 0     | 0           | SCLH               | R/W       | no                                                                | channel 0 clock HIGH state                           | 3Fh     | 1               |

|       |        |        |                                    | 1      | 1             | 0     | 1           | MODE               | R/W       | no                                                                | channel 0 mode                                       | 92h     | 1               |

|       |        |        |                                    | 1      | 1             | 1     | 0           | TIMEOUT            | R/W       | no                                                                | channel 0 time-out                                   | 00h     | 1               |

|       |        |        |                                    | 1      | 1             | 1     | 1           | PRESET             | R/W       | yes                                                               | channel 0 parallel reset                             | 00h     | 1               |

Product data sheet

|   | 7    | 6      | 5   | 4     | 3     | 2  | 1 | 0 | Register name | Access | Write access while CH active | Description                                          | Default | Size<br>(bytes) |

|---|------|--------|-----|-------|-------|----|---|---|---------------|--------|------------------------------|------------------------------------------------------|---------|-----------------|

|   | Char | nnel 1 | (UF | m) re | giste | rs |   |   |               |        |                              |                                                      |         |                 |

|   | 1    | 1      | 0   | 1     | 0     | 0  | 0 | 0 | CONTROL       | R/W    | yes[1]                       | channel 1 control ([7] = 1)                          | 00h     | 1               |

|   |      |        |     |       | 0     | 0  | 0 | 1 | CHSTATUS      | R      | no                           | channel 1 status ([5:1] = 0 in UFm)                  | 00h     | 1               |

|   |      |        |     |       | 0     | 0  | 1 | 0 | INTMSK        | R/W    | yes                          | channel 1 interrupt mask ([5:1] = don't care)        | 00h     | 1               |

|   |      |        |     |       | 0     | 0  | 1 | 1 | SLATABLE      | R/W    | no                           | channel 1 slave address table (auto-increment)       | 00h     | 64              |

|   |      |        |     |       | 0     | 1  | 0 | 0 | TRANCONFIG    | R/W    | yes, for TRANCOUNT[2]        | channel 1 transaction configuration (auto-increment) | 00h     | 65              |

|   |      |        |     |       | 0     | 1  | 0 | 1 | DATA          | R/W    | yes                          | channel 1 data (auto-increment)                      | 00h     | bufsize[3]      |

|   |      |        |     |       | 0     | 1  | 1 | 0 | TRANSEL       | R/W    | yes                          | channel 1 transaction data buffer select             | 00h     | 1               |

| • |      |        |     |       | 0     | 1  | 1 | 1 | TRANOFS       | R/W    | yes                          | channel 1 transaction data buffer byte offset        | 00h     | 1               |

|   |      |        |     |       | 1     | 0  | 0 | 0 | BYTECOUNT     | R      | no                           | channel 1 transmitted byte count (auto-increment)    | 00h     | 64              |

|   |      |        |     |       | 1     | 0  | 0 | 1 | FRAMECNT      | R/W    | no                           | channel 1 frame count                                | 01h     | 1               |

|   |      |        |     |       | 1     | 0  | 1 | 0 | REFRATE       | R/W    | no                           | channel 1 frame refresh rate                         | 00h     | 1               |

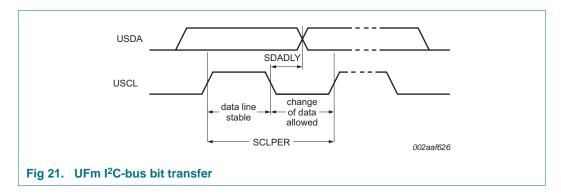

|   |      |        |     |       | 1     | 0  | 1 | 1 | SCLPER        | R/W    | no                           | channel 1 clock period                               | 20h     | 1               |

|   |      |        |     |       | 1     | 1  | 0 | 0 | SDADLY        | R/W    | no                           | channel 1 SDA delay                                  | 08h     | 1               |

|   |      |        |     |       | 1     | 1  | 0 | 1 | MODE[4]       | R/W    | no                           | channel 1 mode                                       | 83h     | 1               |

|   |      |        |     |       | 1     | 1  | 1 | 0 | -             | -      | -                            | reserved                                             | 00h     | 1               |

|   |      |        |     |       | 1     | 1  | 1 | 1 | PRESET        | R/W    | yes                          | channel 1 parallel reset                             | 00h     | 1               |

| 7  | ,   | 6     | 5    | 4     | 3     | 2  | 1 | 0 | Register name | Access | Write access while CH active | Description                                          | Default | Size<br>(bytes)       |

|----|-----|-------|------|-------|-------|----|---|---|---------------|--------|------------------------------|------------------------------------------------------|---------|-----------------------|

| Cł | nan | nel 2 | (UFı | n) re | giste | rs |   |   |               |        |                              |                                                      |         |                       |

| 1  |     | 1     | 1    | 0     | 0     | 0  | 0 | 0 | CONTROL       | R/W    | yes[1]                       | channel 2 control ([7] = 1)                          | 00h     | 1                     |

|    |     |       |      |       | 0     | 0  | 0 | 1 | CHSTATUS      | R      | no                           | channel 2 status ([5:1] = 0 in UFm)                  | 00h     | 1                     |

|    |     |       |      |       | 0     | 0  | 1 | 0 | INTMSK        | R/W    | yes                          | channel 2 interrupt mask ([5:1] = don't care)        | 00h     | 1                     |

|    |     |       |      |       | 0     | 0  | 1 | 1 | SLATABLE      | R/W    | no                           | channel 2 slave address table (auto-increment)       | 00h     | 64                    |

|    |     |       |      |       | 0     | 1  | 0 | 0 | TRANCONFIG    | R/W    | yes, for TRANCOUNT[2]        | channel 2 transaction configuration (auto-increment) | 00h     | 65                    |

|    |     |       |      |       | 0     | 1  | 0 | 1 | DATA          | R/W    | yes                          | channel 2 data (auto-increment)                      | 00h     | bufsize <sup>[3</sup> |

|    |     |       |      |       | 0     | 1  | 1 | 0 | TRANSEL       | R/W    | yes                          | channel 2 transaction data buffer select             | 00h     | 1                     |

|    |     |       |      |       | 0     | 1  | 1 | 1 | TRANOFS       | R/W    | yes                          | channel 2 transaction data buffer byte offset        | 00h     | 1                     |

|    |     |       |      |       | 1     | 0  | 0 | 0 | BYTECOUNT     | R      | no                           | channel 2 transmitted byte count (auto-increment)    | 00h     | 64                    |

|    |     |       |      |       | 1     | 0  | 0 | 1 | FRAMECNT      | R/W    | no                           | channel 2 frame count                                | 01h     | 1                     |

|    |     |       |      |       | 1     | 0  | 1 | 0 | REFRATE       | R/W    | no                           | channel 2 frame refresh rate                         | 00h     | 1                     |

|    |     |       |      |       | 1     | 0  | 1 | 1 | SCLPER        | R/W    | no                           | channel 2 clock period                               | 20h     | 1                     |

|    |     |       |      |       | 1     | 1  | 0 | 0 | SDADLY        | R/W    | no                           | channel 2 SDA delay                                  | 08h     | 1                     |

|    |     |       |      |       | 1     | 1  | 0 | 1 | MODE[4]       | R/W    | no                           | channel 2 mode                                       | 83h     | 1                     |

|    |     |       |      |       | 1     | 1  | 1 | 0 | -             | -      | no                           | reserved                                             | 00h     | 1                     |

|    |     |       |      |       | 1     | 1  | 1 | 1 | PRESET        | R/W    | yes                          | channel 2 parallel reset                             | 00h     | 1                     |

Parallel bus to 1 channel Fm+ and 2 channel UFm I<sup>2</sup>C-bus controller

NXP

Semiconductors

Table 3. PCU9669 register address map - direct register access ...continued

| 7    | 6     | 5     | 4  | 3 | 2 | 1 | 0 | Register name | Access | Write access while CH active | Description               | Default | Size<br>(bytes) |

|------|-------|-------|----|---|---|---|---|---------------|--------|------------------------------|---------------------------|---------|-----------------|

| Glob | al re | giste | rs | 1 | 1 |   |   |               |        |                              |                           |         | l               |

| 1    | 1     | 1     | 1  | 0 | 0 | 0 | 0 | CTRLSTATUS    | R      | yes                          | controller status         | 00h     | 1               |

|      |       |       |    | 0 | 0 | 0 | 1 | CTRLINTMSK    | R/W    | yes                          | master interrupt mask     | 00h     | 1               |

|      |       |       |    | 0 | 0 | 1 | 0 | -             | R      | no                           | reserved                  | 08h     |                 |

|      |       |       |    | 0 | 0 | 1 | 1 | -             | R      | no                           | reserved                  | 00h     |                 |

|      |       |       |    | 0 | 1 | 0 | 0 | -             | R      | no                           | reserved                  | 00h     |                 |

|      |       |       |    | 0 | 1 | 0 | 1 | -             | R      | no                           | reserved                  | 00h     |                 |

|      |       |       |    | 0 | 1 | 1 | 0 | DEVICE_ID     | R      | no                           | device ID                 | E9h     |                 |

|      |       |       |    | 0 | 1 | 1 | 1 | CTRLPRESET    | R/W    | yes                          | master parallel reset     | 00h     | 1               |

|      |       |       |    | 1 | 1 | 1 | 1 | CTRLRDY[5]    | R      | no                           | controller ready register | FFh     | 1               |

<sup>[1]</sup> Except TP and TE. Changing polarity of TP while TE is active will cause a false trigger.

<sup>[2]</sup> The transaction count (TRANCONFIG[0]) can be written to during the idle period between sequences.

<sup>[3]</sup> Refer to Section 7.3.2 "Buffer sizes" for channel memory allocation.

<sup>[4]</sup> Unused bits in the UFm register set will return 0b when read and writes will be ignored.

<sup>[5]</sup> Controller ready = FFh immediately after POR or after a hardware reset or global reset. It will clear (00h) once the initialization routine is done.

### Parallel bus to 1 channel Fm+ and 2 channel UFm I<sup>2</sup>C-bus controller

### 7.5.1 Channel registers

### 7.5.1.1 STATUS0\_[n], STATUS1\_[n], STATUS2\_[n] — Transaction status registers

STATUS0\_[n], STATUS1\_[n], and STATUS2\_[n] are 8-bit  $\times$  64 read-only registers that provide status information for a given transaction. Only the 5 lower bits are used; the top bits will always read 0. When bits [4:2] are set, a channel interrupt is requested (the  $\overline{\text{INT}}$  pin is asserted LOW). A read to STATUSx\_[n] register will clear its status. To clear all the STATUSx\_[n] registers, a byte-by-byte read of all STATUSx\_[n] registers is required. The controller will auto-clear the STATUSx\_[n] registers at each START of a sequence when FRAMECNT = 1 and only at the first START when FRAMECNT  $\neq$  1.

Each register byte can be accessed by direct addressing so that the host can choose to read the status on one or more individual transactions without having to read all 64 status bytes.

Table 4. STATUSx\_[n] - Transaction status code register bit description

| Bit | Symbol  | Description                                                                                                                                                      |

|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:5 | ST[7:5] | always reads 000                                                                                                                                                 |

| 4   | RSN[1]  | Read slave NACK. When HIGH, a NACK was received after a slave address was transmitted on the serial bus on a read transaction. An interrupt will be requested.   |

| 3   | WSN[1]  | Write slave NACK. When HIGH, a NACK was received after a slave address was transmitted on the serial bus on a write transaction. An interrupt will be requested. |

| 2   | WDN[1]  | Write data NACK. When HIGH, a NACK was received for a data byte during a write transaction on the serial bus. An interrupt will be requested.                    |

| 1   | TA      | Transaction active. When 1, the transaction is currently active on the serial bus. No interrupt is requested.                                                    |

| 0   | TR      | Transaction ready. When 1, a transaction is loaded in the buffer and waiting to be executed. No interrupt is requested.                                          |

<sup>[1]</sup> Does not apply to the UFm channel.

**Remark:** When STATUSx\_[n] = 00h, no interrupt is requested and the transaction is in the Done/Idle state.

During program execution, the TR and TA bits behave as follows:

Example, we are to transfer 3 transactions in a sequence. All initialization is completed (loading of SLA, TRANCONFIG, DATA) and device is ready for serial transfer.

Before the STA bit is set, the STATUSx\_[n] register will contain:

```

\begin{aligned} &\mathsf{STATUSx}[0] = 0 \\ &\mathsf{STATUSx}[1] = 0 \\ &\mathsf{STATUSx}[2] = 0 \\ &\mathsf{STATUSx}[3] = 0 \\ &\cdot \end{aligned}

```

### Parallel bus to 1 channel Fm+ and 2 channel UFm I<sup>2</sup>C-bus controller

After STA is set: STATUSx\_[0] = 2 STATUSx\_[1] = 1 STATUSx\_[2] = 1 STATUSx\_[3] = 0 :

Since there is no timing requirement in setting the STA bit after the initialization, the device will update the first status when the STA bit is set and will always go from 0 to 2 (Idle to Transaction active).

### 7.5.1.2 CONTROL — Control register

CONTROL is an 8-bit register. The STO bit is affected by the bus controller hardware: it is cleared when a STOP condition is present on the  $I^2C$ -bus.

Table 5. CONTROL - Control register bit description

Address: Channel 0 = C0h; Channel 1 = D0h; Channel 2 = E0h.

Legend: \* reset value

| Bit | Symbol | Access | Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|--------|--------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | STOSEQ | R/W    |       | Stop sequence bit.                                                                                                                                                                                                                                                                                                                                                                                                                                |

|     |        |        | 1     | When the STOSEQ bit is set while the channel is active, a STOP condition will be transmitted immediately following the end of the current sequence being transferred on the I <sup>2</sup> C-bus. No further buffered transactions will be carried out and the channel will return to the idle state. Normal error reporting will occur up until the last bit. When a STOP condition is detected on the bus, the hardware clears the STOSEQ flag. |

|     |        |        | 0*    | When STOSEQ is reset, no action will be taken.                                                                                                                                                                                                                                                                                                                                                                                                    |

| 6   | STA    | R/W    |       | The START flag.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|     |        |        | 1     | When the STA bit is set to begin a sequence, the bus controller hardware checks the status of the I <sup>2</sup> C-bus and generates a START condition if the bus is free (does not apply to the UFm channel). If the bus is not idle, then INT will go LOW and the CHSTATUS register will contain a bus error code (either DAE or CLE will be set).                                                                                              |

|     |        |        |       | The STA bit may be set only at a valid idle state. The controller will reset the bit under the following conditions:                                                                                                                                                                                                                                                                                                                              |

|     |        |        |       | <ul> <li>A sequence is done and FRAMECNT = 1.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                          |

|     |        |        |       | <ul> <li>A sequence loop is done and FRAMECNT &gt; 1.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                  |

|     |        |        |       | <ul> <li>The STOSEQ bit is set, FRAMECNT = 0, and the current sequence is done.</li> </ul>                                                                                                                                                                                                                                                                                                                                                        |

|     |        |        |       | <ul> <li>The STOSEQ bit is set, FRAMECNT &gt; 1, and the current sequence is done.</li> </ul>                                                                                                                                                                                                                                                                                                                                                     |

|     |        |        |       | <ul> <li>The STO bit is set and the current byte transaction is done. This bit cannot be<br/>set if the CHEN bit is 0.</li> </ul>                                                                                                                                                                                                                                                                                                                 |

|     |        |        | 0*    | When the STA bit is reset, no START condition will be generated.                                                                                                                                                                                                                                                                                                                                                                                  |

| 5   | STO    | R/W    |       | The STOP flag.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|     |        |        | 1     | When the STO bit is set while the channel is active, a STOP condition will be transmitted immediately following the current data or slave address byte being transferred on the I <sup>2</sup> C-bus. If a read is in progress, a NACK will be generated before the STOP. No further buffered transactions will be carried out and the channel will return to the idle state. Normal error reporting will occur up until the last bit.            |

|     |        |        |       | When a STOP condition is detected on the bus, the hardware clears the STO flag.                                                                                                                                                                                                                                                                                                                                                                   |

|     |        |        | 0*    | When the STO bit is reset, no action will be taken.                                                                                                                                                                                                                                                                                                                                                                                               |

### Parallel bus to 1 channel Fm+ and 2 channel UFm I<sup>2</sup>C-bus controller

Table 5.

CONTROL - Control register bit description ...continued

Address: Channel 0 = C0h; Channel 1 = D0h; Channel 2 = E0h.

Legend: \* reset value

| Bit | Symbol   | Access | Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----|----------|--------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4   | TP       | R/W    |       | Trigger polarity bit. Cannot be changed while channel is active.                                                                                                                                                                                                                                                                                                                                                                 |

|     |          |        | 1     | Trigger will be detected on a falling edge.                                                                                                                                                                                                                                                                                                                                                                                      |

|     |          |        | 0*    | Trigger will be detected on a rising edge.                                                                                                                                                                                                                                                                                                                                                                                       |

| 3   | TE       | R/W    |       | Trigger Enable (TE) bit controls the trigger input used for frame refresh. TE cannot be changed while channel is active. When the trigger input is enabled, the trigger will override the contents of the FRAMECNT register and will start triggering when STA bit is set. Thereafter, when a trigger tick is detected, the controller will issue a START command and the stored sequence will be transferred on the serial bus. |

|     |          |        | 1     | When TE = 1, the sequence is controlled by the Trigger input.                                                                                                                                                                                                                                                                                                                                                                    |

|     |          |        | 0*    | When TE = 0, the trigger inputs are ignored.                                                                                                                                                                                                                                                                                                                                                                                     |

| 2   | BPTRRST  | W      | 1     | Resets auto increment pointers for BYTECOUNT. Reads back as 0.                                                                                                                                                                                                                                                                                                                                                                   |

| 1   | AIPTRRST | W      | 1     | Resets auto increment pointers for SLATABLE and TRANCONFIG. The DATA register auto-increment pointer will be set to the value that corresponds to TRANSEL and TRANOFS registers. Reads back as 0.                                                                                                                                                                                                                                |

|     |          |        |       | Remark: To reset the data pointer, write 00h to TRANSEL.                                                                                                                                                                                                                                                                                                                                                                         |

| 0   | -        | W      | 0     | Reserved. User must write 0 to this bit.                                                                                                                                                                                                                                                                                                                                                                                         |

|     |          |        |       |                                                                                                                                                                                                                                                                                                                                                                                                                                  |

**Remark:** Due to a small latency between setting the STA bit and the ability to detect a trigger pulse, if the STA bit is set simultaneously to an incoming trigger pulse, the pulse will be ignored and the controller will wait for the next trigger to send the START.

If the STO or STOSEQ bit are set at anytime while the STA bit is 0, then no action will be taken and the write to these bits is ignored.

Remark: STO has priority over STOSEQ.

### Parallel bus to 1 channel Fm+ and 2 channel UFm I<sup>2</sup>C-bus controller

Table 6. CONTROL register bits STA, STO, STOSEQ operation/behavior

| Channel state                                        | Next write ac | ction | by hos | t   |        | Results                                                                                                                                                                                           |

|------------------------------------------------------|---------------|-------|--------|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (initialization steps)                               | FRAMECNT      | TE    | STA    | STO | STOSEQ |                                                                                                                                                                                                   |

| Idle (reset, TRANCONFIG,                             | 1             | 0     | 0      | X   | X      | No action.                                                                                                                                                                                        |

| SLATABLE, DATA, STA = 0)                             | 1             | 0     | 1      | X   | X      | START transmitted on serial bus followed by sequence stored in buffer.                                                                                                                            |

| Active (reset, load                                  | 1             | 0     | Χ      | 0   | Χ      | No change; cannot write STA while active.                                                                                                                                                         |

| TRANCONFIG, SLATABLE,<br>DATA, STA = 1               | 1             | 0     | X      | 1   | X      | When the STO bit is set, two actions are possible:                                                                                                                                                |

|                                                      |               |       |        |     |        | <ol> <li>If the transaction is a read, a STOP is<br/>sent after the first read byte (NACK sent)<br/>and the byte count is updated.</li> </ol>                                                     |

|                                                      |               |       |        |     |        | <ol><li>If the transaction is a write, a STOP is<br/>sent after the end of ACK cycle of the<br/>current byte and BYTECNT is updated.</li></ol>                                                    |

|                                                      |               |       |        |     |        | The SD bits will be set.                                                                                                                                                                          |

| REFRATE Loop idle (reset,                            | <b>≠</b> 1    | 0     | 0      | X   | X      | No action.                                                                                                                                                                                        |

| load TRANCONFIG,<br>SLATABLE, DATA STA = 1)[1]       | <b>≠</b> 1    | 0     | X      | 0   | 1      | Channel will go immediately to the inactive state and SD and FLD bits will be set. [2]                                                                                                            |

|                                                      | <b>≠</b> 1    | 0     | X      | 1   | X      | Channel will go immediately to the inactive state and SD and FLD bits will be set.[2]                                                                                                             |

| REFRATE Loop active (reset,                          | ≠ 1           | 0     | Χ      | 0   | 0      | No action.                                                                                                                                                                                        |

| load, TRANCONFIG,<br>SLATABLE, DATA, STA = 1)        | ≠ 1           | 0     | X      | 0   | 1      | STOP at end of current frame. The SD and FLD bits will be set.                                                                                                                                    |

|                                                      | <b>≠</b> 1    | 0     | X      | 1   | X      | <ul><li>When the STO bit is set, two actions are possible:</li><li>1. If the transaction is a read, a STOP is sent after the first read byte (NACK sent) and the byte count is updated.</li></ul> |

|                                                      |               |       |        |     |        | 2. If the transaction is a write, a STOP is sent after the end of ACK cycle of the current byte and BYTECNT is updated.                                                                           |

|                                                      | .,            |       |        | .,  |        | The SD and FLD bits will be set.                                                                                                                                                                  |

| Trigger Loop Idle (reset, load TRANCONFIG, SLATABLE, | X             | 1     | 0      | X   | X      | No action.                                                                                                                                                                                        |

| DATA, STA = 1)                                       | X             | 1     | X      | 0   | 1      | STOP at end of current frame. The SD and FLD bits will be set.                                                                                                                                    |

|                                                      | X             | 1     | X      | 1   | X      | When the STO bit is set, two actions are possible:                                                                                                                                                |

|                                                      |               |       |        |     |        | <ol> <li>If the transaction is a read, a STOP is<br/>sent after the first read byte (NACK sent)<br/>and the byte count is updated.</li> </ol>                                                     |

|                                                      |               |       |        |     |        | <ol><li>If the transaction is a write, a STOP is<br/>sent after the end of ACK cycle of the<br/>current byte and the BYTECNT is<br/>updated.</li></ol>                                            |

|                                                      |               |       |        |     |        | The SD and FLD bits will be set.                                                                                                                                                                  |

### Parallel bus to 1 channel Fm+ and 2 channel UFm I<sup>2</sup>C-bus controller

Table 6. CONTROL register bits STA, STO, STOSEQ operation/behavior ... continued

| Channel state                           | Next write ac | tion I | y hos | t   |        | Results                                                                                |

|-----------------------------------------|---------------|--------|-------|-----|--------|----------------------------------------------------------------------------------------|

| (initialization steps)                  | FRAMECNT      | TE     | STA   | STO | STOSEQ |                                                                                        |

| Trigger Loop active (reset, load        | X             | 1      | Χ     | 0   | 0      | No action.                                                                             |

| TRANCONFIG, SLATABLE,<br>DATA, STA = 1) | X             | 1      | X     | 0   | 1      | Channel will go immediately to the inactive state and SD and FLD bits will be set. [2] |

|                                         | X             | 1      | X     | 1   | X      | Channel will go immediately to the inactive state and SD and FLD bits will be set.[2]  |

<sup>[1]</sup> Loop Idle is defined as the time elapsed from a STOP to the START of the next sequence while STA = 1.

### 7.5.1.3 CHSTATUS — Channel status register

CHSTATUS is an 8-bit read-only register that provides status information for a given channel. Some of these status bits are error codes that cannot be masked (NMI) by the INTMSK register and need attention from the host. All these status drive the INT pin active LOW. To clear the individual channel interrupt request, you must read the CHSTATUS register. The BE interrupt is cleared by reading the CTRLSTATUS register.

After the CHSTATUS register is cleared, only new errors or status updates will cause the CHSTATUS bits to be set.

Table 7. CHSTATUS - Channel and buffer status codes register bit description Address: Channel 0 = C1h; Channel 1 = D1h; Channel 2 = E1h.

|     |        | - · ·                                                                                                                                                   |

|-----|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit | Symbol | Description                                                                                                                                             |

| 7   | SD     | Sequence Done. The sequence loaded in the buffer was sent and STOP issued on the serial bus.                                                            |

| 6   | FLD    | Frame Loop Done. The FRAMECNT value has been reached. A STOP has been issued on the bus.                                                                |

| 5   | WE[1]  | Write Error detected in transaction. An SLA NACK or data NACK was detected in a write transaction of the sequence.                                      |

| 4   | RE[1]  | Read Error detected in transaction. An SLA NACK was detected in a read transaction of the sequence.                                                     |

| 3   | DAE[1] | Bus error, SDA stuck LOW.                                                                                                                               |

| 2   | CLE[1] | Bus error, SCL stuck LOW.                                                                                                                               |

| 1   | SSE[1] | Bus error, illegal START or STOP detected.                                                                                                              |

| 0   | FE     | Frame Error detected. The time required to send the sequence exceeds refresh rate programmed to the REFRATE register or the time between trigger ticks. |

<sup>[1]</sup> Does not apply to UFm channel. Always read as logic 0.

The DAE, CLE and SSE bits correspond to bus error states, and the FE bit corresponds to host programming errors.

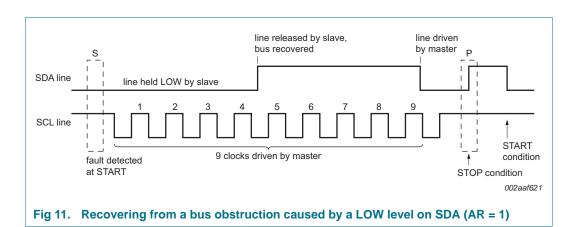

**DAE - SDA error bit:** This bit indicates that the SDA line is stuck LOW when the PCU9669 is trying to send a START condition.

CLE - SCL error bit: This bit indicates that the SCL line is stuck LOW.

<sup>[2]</sup> Channel Active is defined by the CTRLSTATUS[5:3] bits.

### Parallel bus to 1 channel Fm+ and 2 channel UFm I<sup>2</sup>C-bus controller

**SSE - illegal START/STOP detected bit:** This bit indicates that a bus error has occurred during a serial transfer. A bus error is caused when a START or STOP condition occurs at an illegal position in the format frame. Examples of such illegal positions are during the serial transfer of an address byte, a data byte, or an acknowledge bit. A bus error may also be caused when external interference disturbs the internal PCU9669 signals.

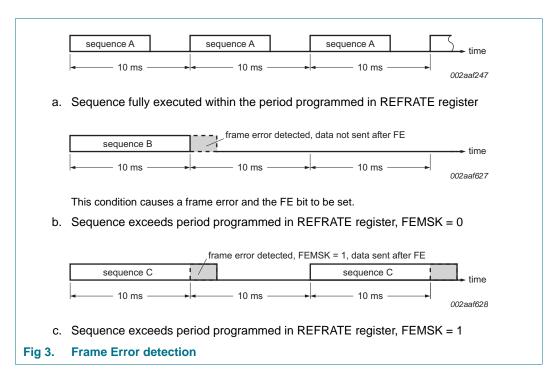

**FE - Frame Error bit:** This bit indicates that the time required to send the sequence exceeds the refresh rate programmed in the REFRATE register or the time between trigger ticks. Solving frame errors include programming longer refresh rates, speeding up the bus frequency, shortening the amount of bytes sent/received in the sequence, or increasing the time between trigger ticks. If the frame error is masked by the FEMSK, the device will continue to transmit transactions until the end of the sequence without re-starting the sequence even if new triggers are detected. The total number of sequences transmitted will be the number stored in the FRAMECNT register. Once a complete sequence is transmitted, a new sequence will initiate when a subsequent trigger appears. The FE flag will be held HIGH and sequences will still be transmitted unless CHSTATUS is read. If the frame error is unmasked, the sequence will be aborted at the next logical stopping point (i.e., for a read transaction a NACK will be sent), a STOP transmitted and an interrupt will be generated. Since the controller terminates the sequence in a controlled mechanism, there may be a 2-byte delay if a frame error (FE) is detected during a read transaction. The FE bit is set after the STOP is detected on the bus.

### Parallel bus to 1 channel Fm+ and 2 channel UFm I<sup>2</sup>C-bus controller

Table 8. Error detection operation/behavior

| Channel state                                           | AR (MODE register) | •   |     | d   | Next Action                                                                                                                                                                                                                                                                                             |

|---------------------------------------------------------|--------------------|-----|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                         |                    | DAE | CLE | SSE |                                                                                                                                                                                                                                                                                                         |