# GreenFET<sup>TM</sup> Low Voltage Gate Driver

#### **Features**

- Drain Voltage Range 0.7V to 1.5V

- · Controlled Load Discharge Rate

- · Controlled Turn on Slew Rate

- · Pb-Free / RoHS compliant

- Halogen-Free

- 2mm x 2mm TDFN-8 Package

## **Applications**

- · Low Transient Load Switching

- · Personal computers and Servers

- · Hot Plugging Applications

- · Power Rail Switches

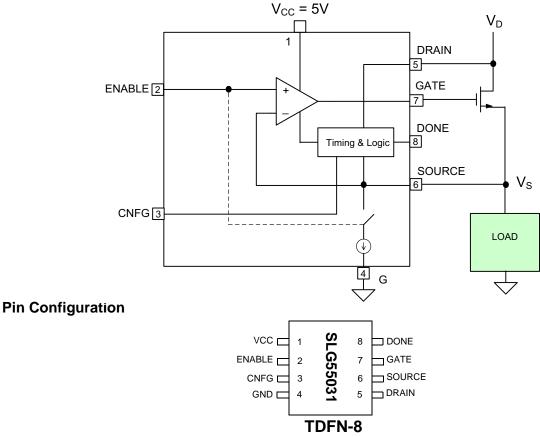

## **Block Diagram**

#### Overview

The SLG55031 N-Channel FET Gate Driver is used for controlling the ramping slew rate of the source voltage on N-Channel FET switches from a CMOS logic level input. Intended as supporting control elements for switched voltage rails in energy efficient advanced power management systems, these devices also include circuits to discharge opened switched voltage rails. SLG55031 uses an external resistor connected between the CNFG pin and GND to establish the slew rate. F

SLG55031 ramps  $V_S$  from 10% to 90% of 1.50V in 33 $\mu s$  with External Resistor =  $560k\Omega$

# **Pin Description**

| Pin Name | Pin Number | Туре   | Pin Description                                                       |

|----------|------------|--------|-----------------------------------------------------------------------|

| VCC      | 1          | Power  | Supply Voltage 5V                                                     |

| ENABLE   | 2          | Input  | CMOS Logic Level. High True for SLG55031                              |

| CNFG     | 3          | Input  | Resistor or Capacitor Connection for timing configuration             |

| GND      | 4          | GND    | Ground.                                                               |

| DRAIN    | 5          | Input  | FET Drain Connection                                                  |

| SOURCE   | 6          | Input  | Source Connection                                                     |

| GATE     | 7          | Output | FET Gate Drive                                                        |

| DONE     | 8          | Output | Output CMOS Open Drain - Power Good, indicates external FET fully on. |

# **Ordering Information**

| Part Number | External Timing<br>Component | Enable Polarity  | External FET<br>Threshold Voltage<br>Range | Package Type                      |

|-------------|------------------------------|------------------|--------------------------------------------|-----------------------------------|

| SLG55031VTR | External Resistor            | HIGH True Active | 1.5V < VT < 2.5V                           | TDFN-8 - Tape and Reel (3k units) |

000-0055031-100 Page 2 of 12

## **Absolute Maximum Conditions**

| Parameter                   | Min. | Max. | Unit |

|-----------------------------|------|------|------|

| V <sub>CC</sub> to GND      | -0.3 | 6.0  | V    |

| Voltage at Logic Input pins | -0.3 | 6.0  | V    |

| Current at input pin        | -1.0 | 1.0  | mA   |

| Storage temperature range   | -65  | 150  | °C   |

| Operating temperature range | 0    | 70   | °C   |

| Junction temperature        |      | 150  | °C   |

| Moisture Sensitivity Level  |      | 1    |      |

## Electrical Characteristics (-10°C to 75°C)

| Symbol                 | Parameter                                  | Condition/Note                                  | Min. | Тур. | Max. | Unit |

|------------------------|--------------------------------------------|-------------------------------------------------|------|------|------|------|

| V <sub>CC</sub>        | Supply Voltage                             |                                                 | 4.75 | 5.0  | 5.25 | V    |

| Iq                     | Quiescent Current                          | ENABLE = 1, V <sub>G</sub> not ramping          |      | 1.5  | 5    | μΑ   |

| I <sub>STBY</sub>      | Standby Current                            | ENABLE = 0                                      |      | 2    | 3    | μΑ   |

| Т                      | Operating Temperature                      |                                                 | 0    | 25   | 70   | °C   |

| V <sub>D</sub>         | Driven FET Drain Voltage                   | May dynamically vary                            | 0.7  |      | 1.5  | V    |

| V <sub>G</sub>         | Gate Voltage                               | Tracks Supply V <sub>CC</sub>                   | 4.75 | 5.0  | 5.25 | V    |

| T <sub>VT</sub>        | FET Turn on Delay                          | FET VT <2.0V<br>FET GATE CIN < 4nF              | 3    | 8    |      | μs   |

| I <sub>DISCHARGE</sub> | Internal Discharge Equiva-<br>lent Current | Discharges MOSFET Source                        |      |      | 10   | mA   |

| V <sub>IH</sub>        | HIGH-level input voltage                   | ENABLE pin                                      | 2.0  |      |      | V    |

| V <sub>IL</sub>        | LOW-level Input voltage                    | ENABLE pin                                      |      |      | 1.0  | V    |

| I <sub>IH</sub>        | HIGH-level Input Current                   | Digital pins, V <sub>IN</sub> = V <sub>CC</sub> | -1.0 |      | 1.0  | μΑ   |

| I <sub>IL</sub>        | LOW-level input Current                    | Digital pins, V <sub>IN</sub> = 0V              | -1.0 |      | 1.0  | μΑ   |

| V <sub>OH_LOGIC</sub>  | DONE Pull-up Voltage                       | Open Drain Output Buffer                        |      |      | 5.5  | V    |

000-0055031-100 Page 3 of 12

### **Description**

In a typical application, de-asserting ENABLE turns off the external power N-FET. The voltage at the load is discharged through the discharge control path internal to the SLG55031. The rate of discharge is current limited to 10ma.

When ENABLE is asserted, gate voltage is applied to the gate of the external power N-FET within  $10\mu$ s (typical) then the gate voltage is ramped up to  $V_{CC}$  -  $V_D$  (3.5V typical) at a slew rate determined by the value of the external resistor or capacitor connected to the CNFG pin of the SLG55031. Monotonic rise of the external FET's source voltage  $V_S$  is maintained even as Source current increases after the load device turn on threshold voltage is reached. After the Source voltage has ramped up to the Drain Voltage – the voltage drop contribution by  $R_{DS-ON}$  of the FET, the external FET is fully on and the open drain DONE signal is asserted.

If a voltage is not present on the Drain Sense Pin prior to assertion of ENABLE, the FET's gate will be immediately driven high turning the FET fully on.

DONE may be used as the ENABLE control of a second SLG55031 connected in series thereby providing power on sequence control of a number of switched power rails, or used in a 'wired and' with other DONE signals to indicate all switched power rails are in a power good condition.

## **Configuration Options**

The SLG55031 is configured with external passive devices to select between two widely separate ramp slew rates. See the following Table for details

## **Configuration Pin Usage Table**

| Resistor to Ground (SLG55031) to 1.5V Rail |      |      |      |  |  |  |

|--------------------------------------------|------|------|------|--|--|--|

| Value (Ω)                                  | 400K | 560K | 750K |  |  |  |

| Typical Slew Time (μs)                     | 23   | 33   | 45   |  |  |  |

000-0055031-100 Page 4 of 12

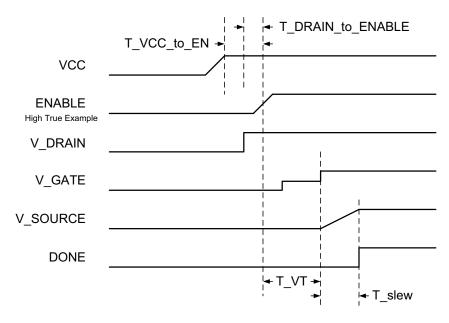

## **Timing Diagram - Initial P-ON**

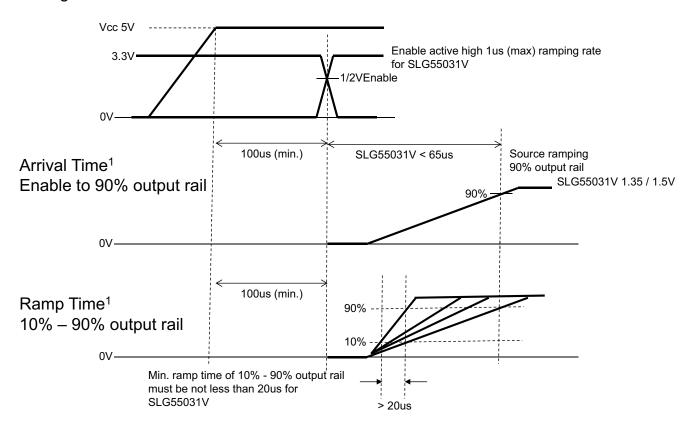

$V_{CC}$  to the SLG55031 must reach  $V_{CC}$  min (4.75V) before the device will begin to be operational. ENABLE<sup>1</sup> must be asserted 100 $\mu$ s after 100 $\mu$ s of  $V_{CC}$  has been attained. If  $V_{CC}$  has been attained. If  $V_{CC}$  has been attained of the ENABLE, the Source will begin to ramp towards  $V_{CC}$  has been attained. If  $V_{CC}$  has typically), the time required for the gate of the FET to be past turn on threshold (typically 2.0V). Carefully examine specific FET turn-on threshold as well as FET C-IN and if the values fall outside of the range of values covered in the electrical specifications section of this document, consult Silego for applications assistance in determining the value of  $T_{CC}$ .

Diagram 1 Enable after VCC

000-0055031-100 Page 5 of 12

# **SLG55031**

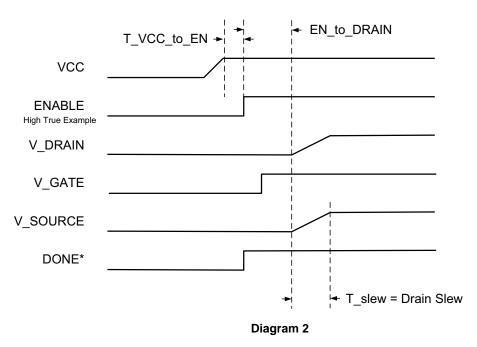

If V\_DRAIN is not present prior to the assertion ENABLE, the driven FET will be turned on immediately following assertion of ENABLE and subsequent application of a voltage on the Drain of the FET will be directly applied to the Source (Diagram 2). Again,  $V_{CC}$  must have reached  $V_{CC-MIN}$  before ENABLE will operate the device.  $V_{CC}$  after which the  $V_{CC}$  after  $V_{CC}$  after

<sup>1</sup>  $T_{VCC}$  to ENABLE = 100 $\mu$ s assertion delay (when  $V_{CC}$  initially ramping up to 100% of  $V_{CC}$ ).

000-0055031-100 Page 6 of 12

<sup>2</sup> Enable assertion transition time must be less than  $1\mu$ s.

<sup>\*</sup> If V\_Drain = 0V prior to assertion of ENABLE, DONE becomes true co-incident with assertion of ENABLE.

<sup>\*</sup> In the case of V\_DRAIN after ENABLE, the definition of Arrival and Ramp Time are not valid

## **Timing Diagram - Rail Switching**

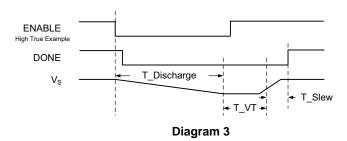

The two components of the FET turn-on time consist of the time it takes to drive the FET's gate up to turn-on threshold ( $T_VT$ ) added to the time it takes for the FET's source voltage to ramp ( $T_Slew$ ) up fully on into the driven load. The timing diagram and table below show the min/max values for these two components vs. different rail source voltage. The  $T_VT$  delay is  $8\mu s - 10\mu s$  typically (with FET VT = 2.0V) depending on the threshold voltage of the FET being driven (Diagram 3).

The Table below and Diagram 3 illustrate source voltage ramp times for various slew rates and resulting total turn on time (ENABLE to DONE) when using the SLG55031 for several selected ranges of drain voltages..

|                                     | Min<br>(μSec)                           | Typ<br>(μSec) |       | Max<br>(μSec) |  |  |  |

|-------------------------------------|-----------------------------------------|---------------|-------|---------------|--|--|--|

| SLG55031                            |                                         |               |       |               |  |  |  |

| R ext = 560KΩ                       | V_Drain Voltage (FET VT = 1.5V to 2.5V) |               |       |               |  |  |  |

| K_ext = 500K22                      |                                         | 1.35V         | 1.50V |               |  |  |  |

| T_Slew*                             | 20                                      | 30            | 33    |               |  |  |  |

| T_DONE**                            |                                         | 42            | 46    | 65            |  |  |  |

| Recommended FET: ON Semi NTMFS4834N |                                         |               |       |               |  |  |  |

|                                     |                                         |               |       |               |  |  |  |

(See Diagram 4 below for more details)

000-0055031-100 Page 7 of 12

<sup>\*</sup> T\_Slew: As V\_Source increases from 10% to 90% of V\_Drainl; e.g. ramp time

<sup>\*\*</sup> T\_Done: From assertion of Enable to V\_Source = 90% of V\_Drain; e.g. arrival time

## **Timing Definition of Arrival Time and Ramp Time**

## Timing for Vcc and Enable

Diagram 4

000-0055031-100 Page 8 of 12

<sup>1</sup> The definition of Arrival Time and Ramp Time is only valid for ENABLE (asserted with a  $100\mu$ s delay) after  $V_{CC}$  has reached 100% and  $V_{DRAIN}$  is present prior to assertion of ENABLE

## **Package Top Marking System Definition**

|          | 8 7 6 5 |               |

|----------|---------|---------------|

| Part ID  | XXA     | Assembly Code |

| Datecode | DD L    | Lot           |

|          | R       | Revision      |

|          | 1 2 3 4 |               |

XX - Part ID Field: identifies the specific device configuration

A – Assembly Code Field: Assembly Location of the device.

DD – Date Code Field: Coded date of manufacture

L – Lot Code: Designates Lot #

R – Revision Code: Device Revision

Page 9 of 12 000-0055031-100

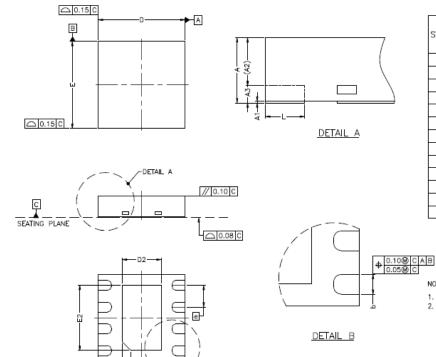

## **Package Drawing and Dimensions** 8 Lead TDFN Package

|        |      | DIMENSION | 1    | DIMENSION |        |      |  |

|--------|------|-----------|------|-----------|--------|------|--|

| SYMBOL |      | (MM)      |      | (MIL)     |        |      |  |

|        | MIN. | NOM.      | MAX. | MIN.      | NOM.   | MAX. |  |

| Α      | 0.70 | 0.75      | 0.80 | 28        | 30     | 31   |  |

| A1     | 0.00 | 0.02      | 0.05 | 0         | 1      | 2    |  |

| A2     | 0    | 0.55      | 0.80 | 0         | 22     | 31   |  |

| A3     | _    | 0.20      | _    | _         | 8      | _    |  |

| b      | 0.18 | 0.25      | 0.30 | 7         | 10     | 12   |  |

| D      | 1.90 | 2.00      | 2.10 | 74        | 79     | 83   |  |

| D1     |      | _         |      | _         |        |      |  |

| D2     | 0.75 | 0.90      | 1.05 | 30        | 35     | 41   |  |

| E      | 1.90 | 2.00      | 2.10 | 75        | 79     | 83   |  |

| E1     |      | _         |      |           | _      |      |  |

| E2     | 1.35 | 1.50      | 1.65 | 53        | 59     | 65   |  |

| е      | (    | 0.50 BSC  | ;    |           | 20 BSC |      |  |

| L      | 0.25 | 0.30      | 0.35 | 10        | 12     | 14   |  |

1. REFER TO JEDEC STD: MO-229.

2. DIMENSION "5" APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.15MM AND 0.30MM FROM THE TERMINAL TIP. IF THE TERMINAL HAS OPTIONAL RADIUS ON THE OTHER END OF THE TERMINAL, THE DIMENSION B SHOULD NOT BE MEASURED IN THAT RADIUS AREA.

Note: Bottom side metal plate is at ground potential

000-0055031-100 Page 10 of 12

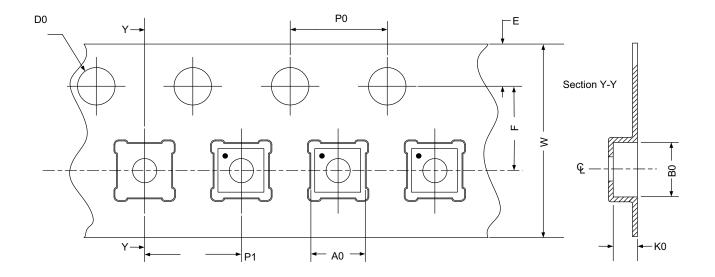

## **Tape and Reel Specifications**

| Bookaga          | # of         | Nominal           | Max      | Jnits Reel & |                   | Leader (min) |                | Trailer (min) |                | Tape          | Part          |

|------------------|--------------|-------------------|----------|--------------|-------------------|--------------|----------------|---------------|----------------|---------------|---------------|

|                  | # or<br>Pins | Package Size [mm] | per Reel | per Box      | Box Hub Size [mm] | Pockets      | Length<br>[mm] | Pockets       | Length<br>[mm] | Width<br>[mm] | Pitch<br>[mm] |

| TDFN 8L<br>Green | 8            | 2 x 2 x 0.75      | 3,000    | 3,000        | 178 / 60          | 100          | 400            | 100           | 400            | 8             | 4             |

## **Carrier Tape Drawing and Dimensions**

| Package<br>Type  | PocketBTM<br>Length | PocketBTM<br>Width | Pocket<br>Depth | Index Hole<br>Pitch | Pocket<br>Pitch | Index Hole<br>Diameter | Index Hole<br>to Tape<br>Edge |     | Tape Width |

|------------------|---------------------|--------------------|-----------------|---------------------|-----------------|------------------------|-------------------------------|-----|------------|

|                  | A0                  | В0                 | K0              | P0                  | P1              | D0                     | E                             | F   | w          |

| TDFN 8L<br>Green | 2.3                 | 2.3                | 1.05            | 4                   | 4               | 1.55                   | 1.75                          | 3.5 | 8          |

## **Recommended Reflow Soldering Profile**

Please see IPC/JEDEC J-STD-020: latest revision for reflow profile based on package volume of 3.00 mm<sup>3</sup> (nominal). More information can be found at www.jedec.org.

000-0055031-100 Page 11 of 12

### Silego Website & Support

#### Silego Technology Website

Silego Technology provides online support via our website at <a href="http://www.silego.com/">http://www.silego.com/</a>. This website is used as a means to make files and information easily available to customers.

For more information regarding Silego Green products, please visit:

http://greenpak.silego.com/ http://greensak.silego.com/ http://greenlib.silego.com/ http://greenfet.silego.com/ http://greenclk.silego.com/

http://greenddr3.silego.com/

Products are also available for purchase directly from Silego at the Silego Online Store at http://store.silego.com/.

#### Silego Technical Support

Datasheets and errata, application notes and example designs, user guides, and hardware support documents and the latest software releases are available at the Silego website or can be requested directly at info@silego.com.

For specific GreenPAK design or applications questions and support please send email requests to GreenPAK@silego.com

Users of Silego products can receive assistance through several channels:

#### Online Live Support

Silego Technology has live video technical assistance and sales support available at <a href="http://www.silego.com/">http://www.silego.com/</a>. Please ask our live web receptionist to schedule a 1 on 1 training session with one of our application engineers.

#### **Contact Your Local Sales Representative**

Customers can contact their local sales representative or field application engineer (FAE) for support. Local sales offices are also available to help customers. More information regarding your local representative is available at the Silego website or send a request to info@silego.com

#### **Contact Silego Directly**

Silego can be contacted directly via e-mail at info@silego.com or user submission form, located at the following URL:

http://support.silego.com/

#### Other Information

The latest Silego Technology press releases, listing of seminars and events, listings of world wide Silego Technology offices and representatives are all available at <a href="http://www.silego.com/">http://www.silego.com/</a>

THIS PRODUCT HAS BEEN DESIGNED AND QUALIFIED FOR THE CONSUMER MARKET. APPLICATIONS OR USES AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS ARE NOT AUTHORIZED. SILEGO TECHNOLOGY DOES NOT ASSUME ANY LIABILITY ARISING OUT OF SUCH APPLICATIONS OR USES OF ITS PRODUCTS. SILEGO TECHNOLOGY RESERVES THE RIGHT TO IMPROVE PRODUCT DESIGN, FUNCTIONS AND RELIABILITY WITHOUT NOTICE.

000-0055031-100 Page 12 of 12