# Keysight Technologies

InfiniiVision MSO Dynamic Probe for Xilinx FPGAs (N5406A and DSOX4FPGAX, and DSOX6FPGAX)

Data Sheet

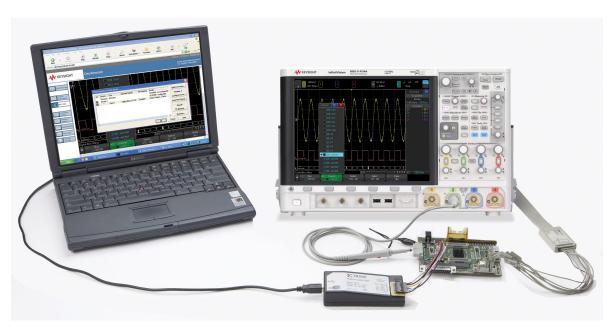

Figure 1. FPGA dynamic probe for Xilinx used in conjunction with a Keysight InfiniiVision 6000, 7000, or 4000 or 6000 X-Series MSO provides an effective solution for simple through complex debugging of systems incorporating Xilinx FPGAs.

### The challenge

You rely on the insight a MSO (mixed-signal oscilloscope) provides to understand the behavior of your FPGA in the context of the surrounding system. Design engineers typically take advantage of the programmability of the FPGA to route internal nodes to a small number of physical pins for debugging. While this approach is very useful, it has significant limitations.

- Since pins on the FPGA are typically an expensive resource, there are a relatively small number available for debug. This limits internal visibility (i.e. one pin is required for each internal signal to be probed).

- When you need to access different internal signals, you must change your design to route these signals to the available pins. This can be time consuming and can affect the timing of your FPGA design.

- Finally, the process required to map the signal names from your FPGA design to the MSO digital channel labels is manual and tedious.

- When new signals are routed out, you need to manually update these signal names on the MSO, which takes additional time and is a potential source of confusing errors.

# Debug Your FPGAs Faster and More Effectively With a MSO

### A better way

Collaborative development between Keysight Technologies, Inc. and Xilinx have produced a faster and more effective way to use your MSO to debug FPGAs and the surrounding system. The Keysight FPGA dynamic probe, used in conjunction with a Keysight MSO, provides the most effective solution for simple through complex debugging.

### View internal activity

With the digital channels on your MSO, you are normally limited to measuring signals at the periphery of the FPGA. With the FPGA dynamic probe, you can now access signals internal to the FPGA. You can measure up to 64 internal signals for each external pin dedicated to debug, unlocking visibility into your design that you never had before.

# Make multiple measurements in seconds

Moving probe points internal to an FPGA used to be time consuming. Now, in less than a second, you can easily measure different sets of internal signals without design changes. FPGA timing stays constant when you select new sets of internal signals for probing.

# Leverage the work you did in your design environment

The FPGA dynamic probe maps internal signal names from your FPGA design tool to your Keysight MSO. Eliminate unintentional mistakes and save hours of time with this automatic setup of signal and bus names on your MSO.

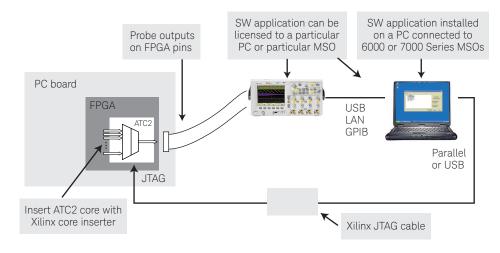

Figure 2. Create a timesaving FPGA measurement system. Insert an ATC2 (Keysight Trace Core) core into your FPGA design. With the application running on your PC you control which group of internal signals to measure via JTAG.

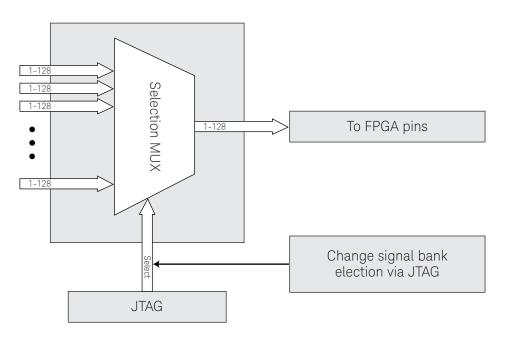

Figure 3. Access up to 64 internal signals for each debug pin. Signal banks all have identical width (1 to 128 signals wide) determined by the number of device pins you devote for debug. Each pin provides sequential access to one signal from every input bank.

# A Quick Tour of the Application

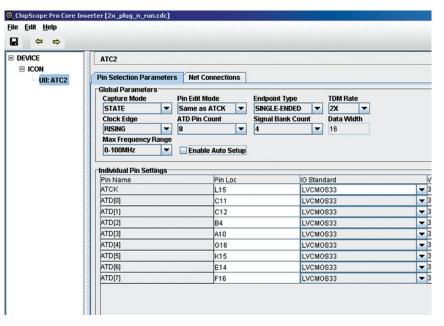

# Design step 1: Create the ATC2 core

Use Xilinx Core Inserter or EDK to select your ATC2 parameters and to create a debug core that best matches your development needs. Parameters include number of pins, number of signal banks, the type of measurement (state or timing), and other ATC2 attributes.

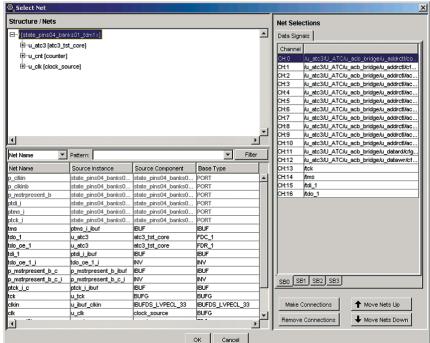

# Design step 2: Select groups of signals to probe

Specify banks of internal signals that are potential candidates for MSO measurements (using Xilinx Core Inserter or EDK).

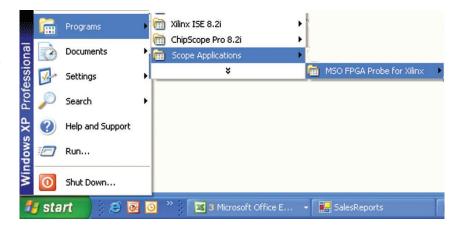

# Activate FPGA dynamic probe for Xilinx

The FPGA dynamic probe application allows you to control the ATC2 core and set up the MSO for the desired measurements. This application runs on a PC.

## A Quick Tour of the Application (Continued)

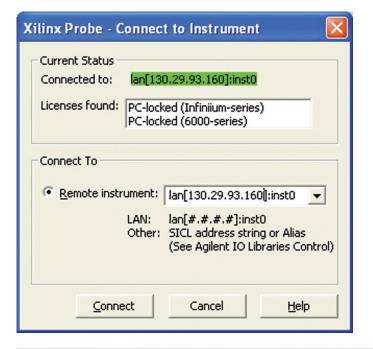

## Connect your MSO to your PC

From FPGA dynamic probe application software, specify the communication link between your PC and MSO.

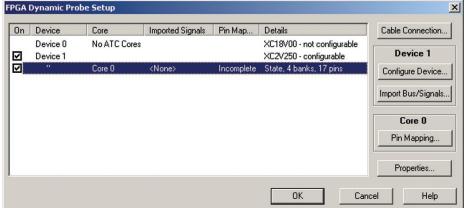

## Measurement setup step 1: Establish a connection between the PC and the ATC2 core

The FPGA dynamic probe application establishes a connection between the PC and a Xilinx cable. It also determines what devices are on the JTAG scan chain and lets you pick which one you wish to communicate with. Core and device names are user definable.

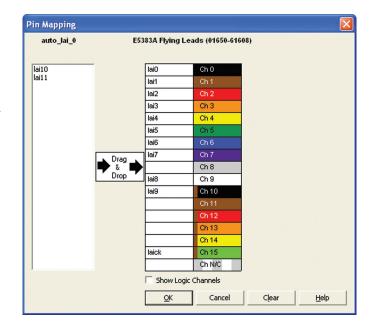

# Measurement setup step 2: Map FPGA pins

Quickly specify how the FPGA pins (the signal outputs of ATC2) are connected to your MSO. Select your probe type and rapidly provide the information needed for the MSO to automatically track names of signals routed through the ATC2 core.

## A Quick Tour of the Application (Continued)

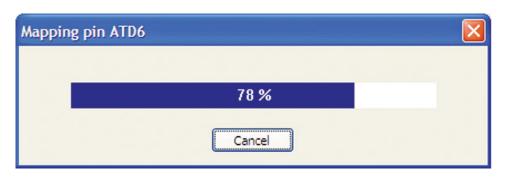

For ATC2 cores with auto setup enabled, each pin of the ATC2 core, one at a time, produces a unique stimulus pattern. The instrument looks for this unique pattern on any of its acquisition channels. When the instrument finds the pattern, it associates that instrument channel with the ATC2 output pin producing it. It then repeats the process for each of the remaining output pins eliminating the need to manually enter probe layout information.

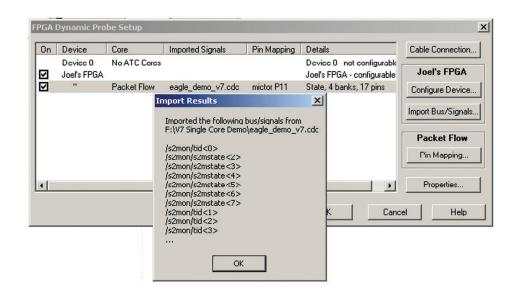

# Measurement setup step 3: Import signal names

Tired of manually entering bus and signal names on your MSO? The FPGA dynamic probe application reads a .cdc file produced by Xilinx Core Inserter. The names of signals you measure will now automatically show on your MSO digital channel labels.

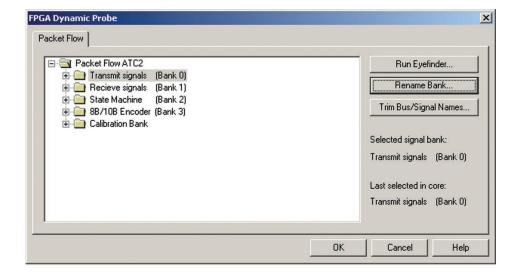

# Setup complete: Make measurements

Quickly change which signal bank is routed to the MSO. A single mouse click tells the ATC2 core to switch to the newly specified signal bank without any impact to the timing of your design. To make measurements throughout your FPGA, change signal banks as often as needed. User-definable signal bank names make it straight forward to select a part of your design to measure.

## A Quick Tour of the Application (Continued)

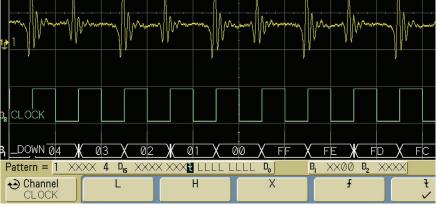

## Triggering on valid states

MSOs incorporate logic state triggering for triggering on specific states. Set up a valid state trigger by specifying the clock edge and the desired bus/signal pattern. Because the ATC2 core outputs both the clock signal and bus values, triggering on the combination ensures your state trigger is valid—even though the digital channels are sampling asynchronously. Track valid states by measuring the bus value on each falling clock edge for image shown.

# \_DOWN 04 ◆ Channel **CLOCK**

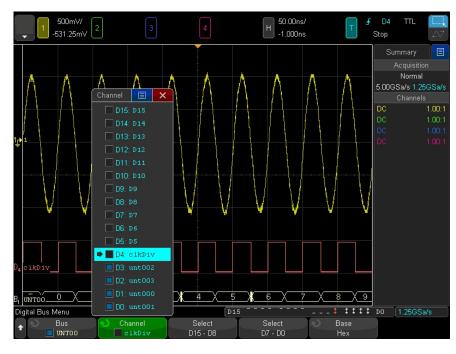

## Automatic bus groupings

InfiniiVision MSOs include up to 2 bus groupings. Contiguous signal names are automatically grouped and displayed as buses. Bus values can be displayed as HEX or binary values. Additional signals are shown using independent waveforms.

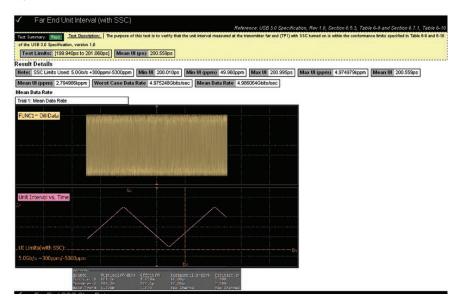

#### Report Detail

## Correlate internal FPGA activity with external measurements

View internal FPGA activity and timecorrelate internal FPGA measurements with external analog and digital events in the surrounding system. FPGA Dynamic Probe unlocks the power of the MSO for system-level debug with FPGAs.

# Specifications and Characteristics

| Supported oscilloscopes             |                                                                                                                                                                                                                                                     |  |

|-------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Standalone oscilloscopes            | InfiniiVision 6000 and 7000 Series, and 4000 and 6000 X-Series MSOs                                                                                                                                                                                 |  |

| MSO digital channels                | 16                                                                                                                                                                                                                                                  |  |

| Bus groupings                       | Up to 2, each with 6 character labels                                                                                                                                                                                                               |  |

| Triggering capabilities             | Determined by MSO, all have state triggering                                                                                                                                                                                                        |  |

| Supported Xilinx FPGA families      | Zynq-7000/7000Q, Artix-7/7Q, Kintex-7/7Q, Virtex-7/7Q, Virtex-6/6Q, Virtex-5/5Q/5QV, Virtex-4/4Q/4QV, Spartan-6/6Q, Spartan-3A, 3AN, and 3E                                                                                                         |  |

| Supported Xilinx cables (required)  | Platform Cable USB, Platform cable II                                                                                                                                                                                                               |  |

| Supported probing mechanisms        | Soft touch (34-channel and 17-channel), Mictor, Samtec, Flying lead, 6000 and 7000 Series MSOs come standard with a 40 pin probe cable and flying leads. Cables and probing for Mictor, soft touch, or Samtec probing must be purchased separately. |  |

| Keysight trace core characteristics |                                                                                                                                                                                                                                                     |  |

| Number of output signals            | User definable: Clock line plus 4 to 128 signals in 1 signal increments                                                                                                                                                                             |  |

| Signal banks                        | User definable: 1, 2, 4, 8, 16, 32, or 64                                                                                                                                                                                                           |  |

| Modes                               | State (synchronous) or timing (asynchronous) mode                                                                                                                                                                                                   |  |

| FPGA resource consumption           | Approximately 1 slice required per input signal to ATC2 Core Consumes no BUFGs, DCM or Block RAM                                                                                                                                                    |  |

|                                     | resources. See resource calculator at www.keysight.com/find/fpga                                                                                                                                                                                    |  |

| Features with application           | Mouse-click bank select, graphical pin mapping, cdc signal name import, auto-pin mapping, and ATC2 "always on" option                                                                                                                               |  |

| Compatible design tools             |                                                                                                                                                                                                                                                     |  |

| ISE 1 ChipScope Pro version         | Keysight MSO FPGA dynamic probe SW version                                                                                                                                                                                                          |  |

| 14.3 or greater                     | 2.60 or greater                                                                                                                                                                                                                                     |  |

| Vivado                              | Designs using Vivado not currently supported                                                                                                                                                                                                        |  |

| Synthesis                           | Core Inserter produces ATC2 cores post-synthesis (pre-place and route) making the cores synthesis                                                                                                                                                   |  |

|                                     | independent. ATC2 cores produced by Core Generator are compatible with:                                                                                                                                                                             |  |

|                                     | <ul> <li>Exemplar Leonardo Spectrum</li> </ul>                                                                                                                                                                                                      |  |

|                                     | <ul> <li>Synopsys Design Compiler</li> </ul>                                                                                                                                                                                                        |  |

|                                     | - Synopsys Design Compiler II                                                                                                                                                                                                                       |  |

|                                     | <ul> <li>Synopsys FPGA Express</li> </ul>                                                                                                                                                                                                           |  |

|                                     | <ul> <li>Synplicity Synplify</li> </ul>                                                                                                                                                                                                             |  |

|                                     | - Xilinx XST                                                                                                                                                                                                                                        |  |

Additional information available via the Internet:

www.keysight.com/find/FPGA and www.keysight.com/find/7000-xilinx.

# Ordering Information

| Ordering information |                                                                                  |

|----------------------|----------------------------------------------------------------------------------|

| N5405A               | FPGA dynamic probe for 6000 or 7000 MSOs                                         |

| - Option 001         | Entitlement certificate for perpetual node-locked license locked to oscilloscope |

| DSOX4FPGAX           | Dynamic probe for 4000 X-Series MSOs                                             |

| DSOX6FPGAX           | Dynamic probe for 6000 X-Series MSOs                                             |

### Product web site

For the most up-to-date and complete application and product information, please visit our product Web site at: www.keysight.com/find/oscilloscope.

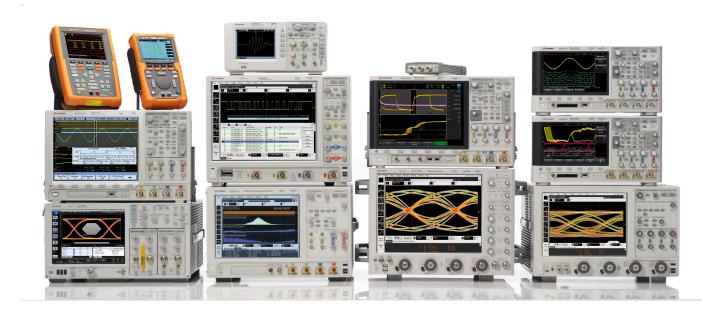

Keysight Technologies Oscilloscopes

Multiple form factors from 20 MHz to > 90 GHz | Industry leading specs | Powerful applications

### www.axiestandard.org

AdvancedTCA® Extensions for Instrumentation and Test (AXIe) is an open standard that extends the AdvancedTCA for general purpose and semiconductor test. Keysight is a founding member of the AXIe consortium. ATCA®, AdvancedTCA®, and the ATCA logo are registered US trademarks of the PCI Industrial Computer Manufacturers Group.

# I WI

### www.lxistandard.org

LAN eXtensions for Instruments puts the power of Ethernet and the Web inside your test systems. Keysight is a founding member of the LXI consortium.

PCI eXtensions for Instrumentation (PXI) modular instrumentation delivers a rugged, PC-based high-performance measurement and automation system.

# From Hewlett-Packard through Agilent to Keysight

For more than 75 years, we've been helping you unlock measurement insights. Our unique combination of hardware, software and people can help you reach your next breakthrough. Unlocking measurement insights since 1939.

1939 THE FUTURE

### myKeysight

### myKeysight

### www.keysight.com/find/mykeysight

A personalized view into the information most relevant to you.

### Three-Year Warranty

### www.keysight.com/find/ThreeYearWarranty

Keysight's committed to superior product quality and lower total cost of ownership. Keysight is the only test and measurement company with three-year warranty standard on all instruments, worldwide. And, we provide a full one-year warranty on all accessories, calibration devices, systems and custom products.

### Keysight Assurance Plans

Keysight Infoline

### www.keysight.com/find/AssurancePlans

Up to ten years of protection and no budgetary surprises to ensure your instruments are operating to specification, so you can rely on accurate measurements.

### Keysight Infoline

### www.keysight.com/find/service

Keysight's insight to best in class information management. Free access to your Keysight equipment company reports and e-library.

### Keysight Channel Partners

### www.keysight.com/find/channelpartners

Get the best of both worlds: Keysight's measurement expertise and product breadth, combined with channel partner convenience.

www.keysight.com

For more information on Keysight Technologies' products, applications or services, please contact your local Keysight office. The complete list is available at: www.keysight.com/find/contactus

#### **Americas**

| Canada        | (877) 894 4414   |

|---------------|------------------|

| Brazil        | 55 11 3351 7010  |

| Mexico        | 001 800 254 2440 |

| United States | (800) 829 4444   |

### Asia Pacific

| 1 800 629 485  |

|----------------|

| 800 810 0189   |

| 800 938 693    |

| 1 800 11 2626  |

| 0120 (421) 345 |

| 080 769 0800   |

| 1 800 888 848  |

| 1 800 375 8100 |

| 0800 047 866   |

| (65) 6375 8100 |

|                |

#### Europe & Middle East

| Austria        | 0800 001122   |

|----------------|---------------|

| Belgium        | 0800 58580    |

| Finland        | 0800 523252   |

| France         | 0805 980333   |

| Germany        | 0800 6270999  |

| Ireland        | 1800 832700   |

| Israel         | 1 809 343051  |

| Italy          | 800 599100    |

| Luxembourg     | +32 800 58580 |

| Netherlands    | 0800 0233200  |

| Russia         | 8800 5009286  |

| Spain          | 800 000154    |

| Sweden         | 0200 882255   |

| Switzerland    | 0800 805353   |

|                | Opt. 1 (DE)   |

|                | Opt. 2 (FR)   |

|                | Opt. 3 (IT)   |

| United Kingdom | 0800 0260637  |

For other unlisted countries: www.keysight.com/find/contactus (BP-10-30-15)

### www.keysight.com/go/quality

Keysight Technologies, Inc. DEKRA Certified ISO 9001:2008 Quality Management System