TOSHIBA Intelligent Power Device Silicon Monolithic Power MOS Integrated Circuit

# **TPD7210F**

### Power MOSFET Gate Driver for 3-Phase DC Motor

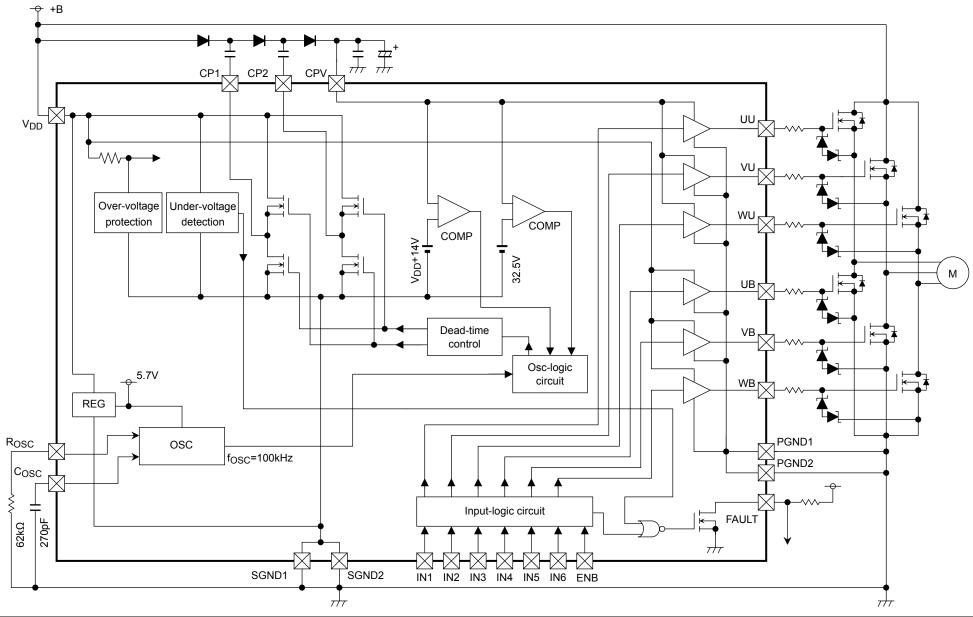

The TPD7210F is a power MOSFET gate driver for 3-phase full-bridge circuits that use a charge pump system. The inclusion of a charge pump circuit for high-side drive inside the IC makes it easy to configure a 3-phase full-bridge circuit.

### **Features**

- Power MOSFET gate driver for 3-phase DC motor

- Built-in diagnosis function: under-voltage detection

- Built-in charge pump circuit

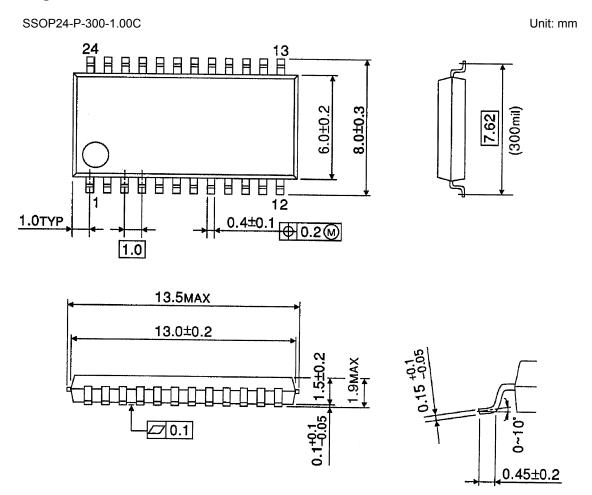

- Package: SSOP-24 (300 mil) with embossed-tape packing

Weight: 0.29 g (typ.)

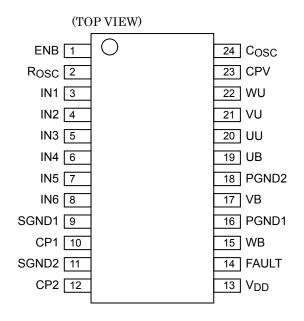

### **Pin Assignment**

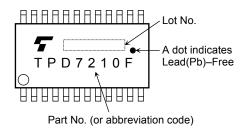

### Marking

This product has a MOS structure and is sensitive to electrostatic discharge.

# **Block Diagram / Application Circuit**

# **Pin Description**

| Pin No. | Symbol           | Pin Description                                                                                                                                                                                                                  |

|---------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | ENB              | Inhibit pin (high active ): By driving this pin low, all outputs can be turned off regardless of input signals. Built-in pull-down resistor (100 k $\Omega$ typ.).                                                               |

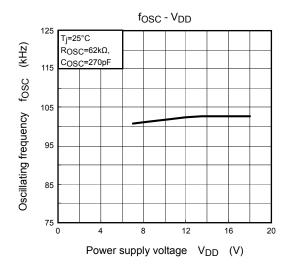

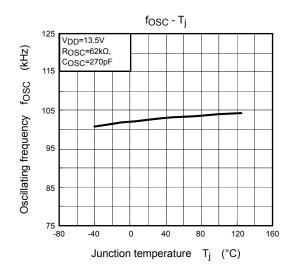

| 2       | Rosc             | This pin sets the oscillation frequency for the charge pump drive. Connect a 62 k $\Omega$ (typ.) resistor.                                                                                                                      |

| 3       | IN1              | Input pin: it controls the power MOSFET connected to UU. Built-in pull-down resistor (100 k $\Omega$ typ.).                                                                                                                      |

| 4       | IN2              | Input pin: it controls the power MOSFET connected to VU. Built-in pull-down resistor (100 k $\Omega$ typ.).                                                                                                                      |

| 5       | IN3              | Input pin: it controls the power MOSFET connected to WU. Built-in pull-down resistor (100 k $\Omega$ typ.).                                                                                                                      |

| 6       | IN4              | Input pin: it controls the power MOSFET connected to UB. Built-in pull-down resistor (100 k $\Omega$ typ.).                                                                                                                      |

| 7       | IN5              | Input pin: it controls the power MOSFET connected to VB. Built-in pull-down resistor (100 k $\Omega$ typ.).                                                                                                                      |

| 8       | IN6              | Input pin: it controls the power MOSFET connected to WB. Built-in pull-down resistor (100 k $\Omega$ typ.).                                                                                                                      |

| 9       | SGND1            | Signal block GND pin: shared internally with pin 11.                                                                                                                                                                             |

| 10      | CP1              | Capacitor pin for charge pump.                                                                                                                                                                                                   |

| 11      | SGND2            | Signal block GND pin: shared internally with pin 9.                                                                                                                                                                              |

| 12      | CP2              | Capacitor pin for charge pump.                                                                                                                                                                                                   |

| 13      | V <sub>DD</sub>  | Power supply pin: when under-voltage (5.5 V typ.) is detected, FAULT output goes high. On this occasion, all outputs are switching normally, and charge pump circuit does not come to a stop.                                    |

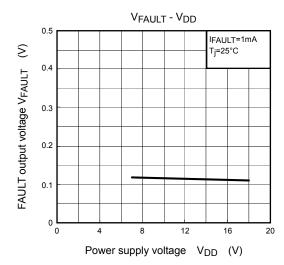

| 14      | FAULT            | Diagnosis output pin: when under-voltage (5.5 V typ.) is detected, FAULT output goes high. High-side/low-side arm shorting mode, FAULT output goes high and all outputs are shut down. Circuit configuration is N-ch open drain. |

| 15      | WB               | Drives the power MOSFET connected to the low side of the W phase.                                                                                                                                                                |

| 16      | PGND1            | Power block GND pin: shared internally with pin 18.                                                                                                                                                                              |

| 17      | VB               | Drives the power MOSFET connected to the low side of the V phase.                                                                                                                                                                |

| 18      | PGND2            | Power block GND pin: shared internally with pin 16.                                                                                                                                                                              |

| 19      | UB               | Drives the power MOSFET connected to the low side of the U phase.                                                                                                                                                                |

| 20      | UU               | Drives the power MOSFET connected to the high side of the U phase.                                                                                                                                                               |

| 21      | VU               | Drives the power MOSFET connected to the high side of the V phase.                                                                                                                                                               |

| 22      | WU               | Drives the power MOSFET connected to the high side of the W phase.                                                                                                                                                               |

| 23      | CPV              | Final stage capacitor pin for the charge pump.                                                                                                                                                                                   |

| 24      | C <sub>OSC</sub> | This pin sets the oscillation frequency for the charge pump drive. Connect a 270pF (typ.) capacitor.                                                                                                                             |

Truth Table (All outputs go to low for input in high-side/low-side arm shorting mode)

| Mode |             |             |             | Output      |             |             |     |           |           |           |           |           |                                         |

|------|-------------|-------------|-------------|-------------|-------------|-------------|-----|-----------|-----------|-----------|-----------|-----------|-----------------------------------------|

| No.  | IN1<br>(UU) | IN2<br>(VU) | IN3<br>(WU) | IN4<br>(UB) | IN5<br>(VB) | IN6<br>(WB) | OUT | OUT<br>VU | OUT<br>WU | OUT<br>UB | OUT<br>VB | OUT<br>WB | Remarks                                 |

| 01   | L           | L           | L           | L           | L           | L           | L   | L         | L         | L         | L         | L         |                                         |

| 02   | Н           | L           | L           | L           | L           | L           | Н   | L         | L         | L         | L         | L         |                                         |

| 03   | L           | Η           | L           | Ш           | L           | L           | L   | Ι         | L         | L         | L         | L         |                                         |

| 04   | L           | L           | Н           | Ш           | L           | L           | L   | Ш         | Н         | L         | L         | L         |                                         |

| 05   | L           | L           | L           | Ι           | L           | L           | L   | Ш         | L         | Н         | L         | L         |                                         |

| 06   | L           | L           | L           | Ш           | Н           | L           | L   | Ш         | L         | L         | Η         | L         |                                         |

| 07   | L           | L           | L           | L           | L           | Н           | L   | L         | L         | L         | L         | Н         |                                         |

| 08   | Н           | L           | L           | Н           | L           | L           | L   | L         | L         | L         | L         | L         | High-side/low-side arm shorting mode *  |

| 09   | Н           | L           | L           | L           | Н           | L           | Н   | L         | L         | L         | Н         | L         | 120° square wave conducting normal mode |

| 10   | Н           | L           | L           | L           | L           | Н           | Н   | L         | L         | L         | L         | Н         | 120° square wave conducting normal mode |

| 11   | L           | Н           | L           | Н           | L           | L           | L   | Н         | L         | Н         | L         | L         | 120° square wave conducting normal mode |

| 12   | L           | Н           | L           | L           | Н           | L           | L   | L         | L         | L         | L         | L         | High-side/low-side arm shorting mode *  |

| 13   | L           | Н           | L           | L           | L           | Н           | L   | Н         | L         | L         | L         | Н         | 120° square wave conducting normal mode |

| 14   | L           | L           | Н           | Н           | L           | L           | L   | L         | Н         | Н         | L         | L         | 120° square wave conducting normal mode |

| 15   | L           | L           | Н           | L           | Н           | L           | L   | L         | Н         | L         | Н         | L         | 120° square wave conducting normal mode |

| 16   | L           | L           | Н           | L           | L           | Н           | L   | L         | L         | L         | L         | L         | High-side/low-side arm shorting mode *  |

| 17   | Н           | Н           | L           | L           | L           | L           | Н   | Н         | L         | L         | L         | L         |                                         |

| 18   | L           | Н           | Н           | L           | L           | L           | L   | Н         | Н         | L         | L         | L         |                                         |

| 19   | Н           | L           | Н           | L           | L           | L           | Н   | L         | Н         | L         | L         | L         |                                         |

| 20   | L           | L           | L           | Н           | Н           | L           | L   | L         | L         | Н         | Н         | L         |                                         |

| 21   | L           | L           | L           | L           | Н           | Н           | L   | L         | L         | L         | Н         | Н         |                                         |

| 22   | L           | L           | L           | Н           | L           | Н           | L   | L         | L         | Н         | L         | Н         |                                         |

| 23   | Н           | Н           | L           | Н           | L           | L           | L   | L         | L         | L         | L         | L         | High-side/low-side arm shorting mode *  |

| 24   | Н           | Н           | L           | L           | Н           | L           | L   | L         | L         | L         | L         | L         | High-side/low-side arm shorting mode *  |

| 25   | Н           | Н           | L           | L           | L           | Н           | Η   | Н         | L         | L         | L         | Н         |                                         |

| 26   | L           | Н           | Н           | Н           | L           | L           | L   | Н         | Н         | Н         | L         | L         |                                         |

| 27   | L           | Н           | Н           | L           | Н           | L           | L   | L         | L         | L         | L         | L         | High-side/low-side arm shorting mode *  |

| 28   | L           | Н           | Н           | L           | L           | Н           | L   | L         | L         | L         | L         | L         | High-side/low-side arm shorting mode *  |

| 29   | Н           | L           | Н           | Н           | L           | L           | L   | L         | L         | L         | L         | L         | High-side/low-side arm shorting mode *  |

| 30   | Н           | L           | Н           | L           | Н           | L           | Н   | L         | Н         | L         | Н         | L         |                                         |

<sup>\*:</sup> High-side/low-side arm shorting mode is disabled by the internal logic. FAULT output goes high (open-drain, high-impedance)

<sup>\*:</sup> By driving ENB pin low, all outputs can be turned off regardless of input signals. By driving ENB pin high, all outputs are switching normally.

| Mode |             |             | Inp         | out         |             |             | Output |           |           |           |           |           |                                        |  |

|------|-------------|-------------|-------------|-------------|-------------|-------------|--------|-----------|-----------|-----------|-----------|-----------|----------------------------------------|--|

| No.  | IN1<br>(UU) | IN2<br>(VU) | IN3<br>(WU) | IN4<br>(UB) | IN5<br>(VB) | IN6<br>(WB) | OUT    | OUT<br>VU | OUT<br>WU | OUT<br>UB | OUT<br>VB | OUT<br>WB | Remarks                                |  |

| 31   | Н           | L           | Н           | L           | L           | Н           | L      | L         | L         | L         | L         | L         | High-side/low-side arm shorting mode * |  |

| 32   | Н           | L           | L           | Н           | Η           | L           | L      | L         | L         | L         | L         | L         | High-side/low-side arm shorting mode * |  |

| 33   | Н           | L           | L           | L           | Н           | Н           | Н      | L         | L         | L         | Н         | Н         |                                        |  |

| 34   | Н           | L           | L           | Н           | L           | Н           | L      | L         | L         | L         | L         | L         | High-side/low-side arm shorting mode * |  |

| 35   | L           | Н           | L           | Н           | Н           | L           | L      | L         | L         | L         | L         | L         | High-side/low-side arm shorting mode * |  |

| 36   | L           | Н           | L           | L           | Н           | Н           | L      | L         | L         | L         | L         | L         | High-side/low-side arm shorting mode * |  |

| 37   | L           | Н           | ٦           | Н           | L           | Н           | L      | Н         | L         | Н         | L         | Н         |                                        |  |

| 38   | L           | L           | Η           | Н           | Н           | L           | L      | L         | Н         | Н         | Н         | L         |                                        |  |

| 39   | L           | L           | Н           | L           | Ι           | Η           | Ш      | L         | L         | L         | L         | L         | High-side/low-side arm shorting mode * |  |

| 40   | L           | L           | Н           | Η           | L           | Η           | Ш      | L         | L         | L         | L         | L         | High-side/low-side arm shorting mode * |  |

| 41   | Н           | Н           | Н           | L           | L           | L           | Ι      | Н         | Н         | L         | L         | L         |                                        |  |

| 42   | L           | L           | L           | Η           | Ι           | Η           | Ш      | L         | L         | Н         | Н         | Н         |                                        |  |

| 43   | Н           | Н           | L           | Η           | Ι           | L           | Ш      | L         | L         | L         | L         | L         | High-side/low-side arm shorting mode * |  |

| 44   | Н           | Н           | L           | L           | Ι           | Η           | Ш      | L         | L         | L         | L         | L         | High-side/low-side arm shorting mode * |  |

| 45   | Н           | Н           | L           | Η           | L           | Н           | L      | L         | L         | L         | L         | L         | High-side/low-side arm shorting mode * |  |

| 46   | L           | Н           | Н           | Η           | Η           | L           | L      | L         | L         | L         | L         | L         | High-side/low-side arm shorting mode * |  |

| 47   | L           | Н           | Н           | L           | Η           | Н           | L      | L         | L         | L         | L         | L         | High-side/low-side arm shorting mode * |  |

| 48   | L           | Н           | Н           | Η           | L           | Н           | L      | L         | L         | L         | L         | L         | High-side/low-side arm shorting mode * |  |

| 49   | Н           | L           | Н           | Η           | Η           | L           | L      | L         | L         | L         | L         | L         | High-side/low-side arm shorting mode * |  |

| 50   | Н           | L           | Н           | L           | Η           | Н           | L      | L         | L         | L         | L         | L         | High-side/low-side arm shorting mode * |  |

| 51   | Н           | L           | Н           | Η           | L           | Н           | L      | L         | L         | L         | L         | L         | High-side/low-side arm shorting mode * |  |

| 52   | Н           | Н           | Н           | Н           | L           | L           | L      | L         | L         | L         | L         | L         | High-side/low-side arm shorting mode * |  |

| 53   | Н           | Н           | Н           | L           | Η           | L           | L      | L         | L         | L         | L         | L         | High-side/low-side arm shorting mode * |  |

| 54   | Н           | Н           | Н           | L           | L           | Η           | L      | L         | L         | L         | L         | L         | High-side/low-side arm shorting mode * |  |

| 55   | Н           | L           | L           | Η           | Η           | Η           | L      | L         | L         | L         | L         | L         | High-side/low-side arm shorting mode * |  |

| 56   | L           | Н           | L           | Η           | Η           | Н           | L      | L         | L         | L         | L         | L         | High-side/low-side arm shorting mode * |  |

| 57   | L           | L           | Н           | Η           | Η           | Η           | L      | L         | L         | L         | L         | L         | High-side/low-side arm shorting mode * |  |

| 58   | Н           | Н           | Н           | Н           | Н           | L           | L      | L         | L         | L         | L         | L         | High-side/low-side arm shorting mode * |  |

| 59   | Н           | Н           | Н           | L           | Н           | Н           | L      | L         | L         | L         | L         | L         | High-side/low-side arm shorting mode * |  |

| 60   | Н           | Н           | Н           | Н           | L           | Н           | L      | L         | L         | L         | L         | L         | High-side/low-side arm shorting mode * |  |

| 61   | Н           | Н           | L           | Н           | Н           | Н           | L      | L         | L         | L         | L         | L         | High-side/low-side arm shorting mode * |  |

| 62   | L           | Н           | Н           | Н           | Н           | Н           | L      | L         | L         | L         | L         | L         | High-side/low-side arm shorting mode * |  |

| 63   | Н           | L           | Н           | Н           | Н           | Н           | L      | L         | L         | L         | L         | L         | High-side/low-side arm shorting mode * |  |

| 64   | Н           | Н           | Н           | Н           | Н           | Н           | L      | L         | L         | L         | L         | L         | High-side/low-side arm shorting mode * |  |

<sup>\*:</sup> High-side/low-side arm shorting mode is disabled by the internal logic. FAULT output goes high (open-drain, high-impedance)

<sup>\*:</sup> By driving ENB pin low, all outputs can be turned off regardless of input signals. By driving ENB pin high, all outputs are switching normally.

# Absolute Maximum Ratings $(T_a = 25^{\circ}C)$

| Characteristic              | Symbol                             | Rating      | Unit | Remarks                                                                                     |  |  |

|-----------------------------|------------------------------------|-------------|------|---------------------------------------------------------------------------------------------|--|--|

| Power supply voltage        | V <sub>DD(1)</sub>                 | -0.5 to 30  | V    |                                                                                             |  |  |

| Power supply voltage        | V <sub>DD(2)</sub>                 | 45          | V    | Pulse width ≤ 200ms                                                                         |  |  |

| Output current              | ISOURCE                            | 1           | Α    | Pulso width < 10 us                                                                         |  |  |

| Output current              | ISINK                              | 1           | ^    | Pulse width ≤ 10μs                                                                          |  |  |

| Input voltage               | V <sub>IN</sub> , V <sub>ENB</sub> | -0.5 to 7.0 | V    |                                                                                             |  |  |

| FAULT pin voltage           | VFAULT                             | 30          | V    |                                                                                             |  |  |

| PGND pin negative voltage   | P <sub>GND</sub> (-)               | -0.5        | V    | Negative voltage that can be applied to PGND pin (reference to SGND pin)                    |  |  |

| Output pin negative voltage | V <sub>OUT(-)</sub>                | -0.5        | ٧    | Negative voltage that can be applied to UU, VU,WU,UB,VB and WB pins (Reference to SGND pin) |  |  |

| FAULT pin current           | IFAULT                             | 5           | mA   |                                                                                             |  |  |

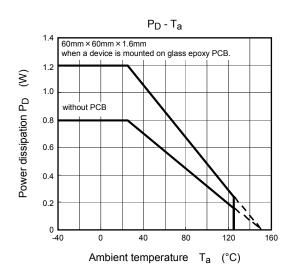

| Dowar dissination           | D-                                 | 0.8         | w    |                                                                                             |  |  |

| Power dissipation           | P <sub>D</sub>                     | 1.2 (Note2) | VV   |                                                                                             |  |  |

| Operating temperature       | T <sub>opr</sub>                   | -40 to 125  | °C   |                                                                                             |  |  |

| Junction temperature        | Tj                                 | 150         | °C   |                                                                                             |  |  |

| Storage temperature         | T <sub>stg</sub>                   | -40 to 150  | °C   |                                                                                             |  |  |

Note1: Using continuously under heavy loads (e.g. the application of high temperature/current/voltage and the significant change in temperature, etc.) may cause this product to decrease in the reliability significantly even if the operating conditions (i.e. operating temperature/current/voltage, etc.) are within the absolute maximum ratings and the operating ranges.

Please design the appropriate reliability upon reviewing the Toshiba Semiconductor Reliability Handbook ("Handling Precautions"/"Derating Concept and Methods") and individual reliability data (i.e. reliability test report and estimated failure rate, etc).

### **Thermal Resistance**

| Characteristic                         | Symbol                | Rating        | Unit   |

|----------------------------------------|-----------------------|---------------|--------|

| Junction to ambient thermal resistance | Du (1)                | 156.3         | °C/W   |

| Junction to ambient thermal resistance | R <sub>th (j-a)</sub> | 104.2 (Note2) | C / VV |

Note2: When the device is mounted on a 60 mm  $\times$  60 mm  $\times$  1.6 mm glass epoxy PCB

Electrical Characteristics (Unless otherwise specified,  $T_a$  = -40 to 125°C, CP1, 2 = 0.1 $\mu$ F,  $R_{OSC}$  = 62 $k\Omega$ ,  $C_{OSC}$  = 270pF)

| Characteristic                              | Symbol                                              | Test<br>Circuit | Condition                                                                                                                | Min                      | Тур.                                      | Max                    | Unit | Remarks                                                                                                       |  |

|---------------------------------------------|-----------------------------------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------|--------------------------|-------------------------------------------|------------------------|------|---------------------------------------------------------------------------------------------------------------|--|

| Operating supply voltage (Note3)            | V <sub>DD(opr)</sub>                                | -               | -                                                                                                                        | 4.5                      | 13.5                                      | 18                     | V    |                                                                                                               |  |

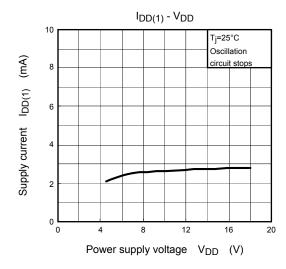

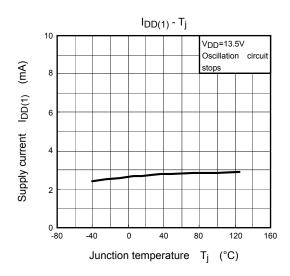

|                                             | I <sub>DD(1)</sub>                                  | -               | V <sub>DD</sub> = 13.5 V                                                                                                 | -                        | -                                         | 7                      |      | Oscillation circuit stops                                                                                     |  |

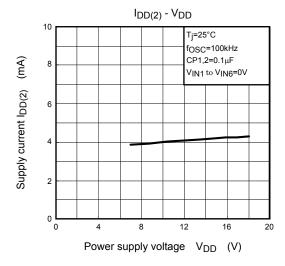

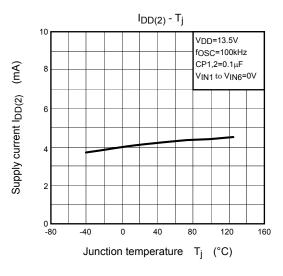

| Supply current                              |                                                     |                 | V <sub>DD</sub> = 13.5 V,<br>V <sub>IN1</sub> to V <sub>IN6</sub> = 0 V,<br>CP1,2 = 0.1μF                                | -                        | ı                                         | 9                      | mA   | When oscillation circuit is operating f = 100 kHz, mean current                                               |  |

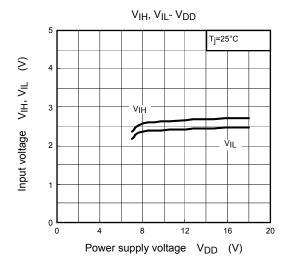

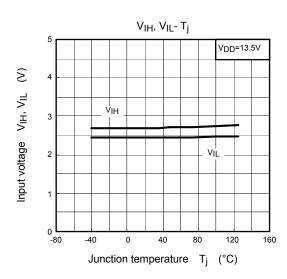

| Input voltage                               | V <sub>IH</sub>                                     |                 | V <sub>DD</sub> = 7 to 18 V,                                                                                             | 3.5                      | ı                                         | _                      | V    | IN1 to IN6 and ENB<br>High-level input voltage                                                                |  |

| input voltage                               | V <sub>IL</sub>                                     |                 | I <sub>O</sub> = 0 A                                                                                                     | -                        | ı                                         | 1.5                    | V    | IIN1 to IN6 and ENB<br>low-level input voltage                                                                |  |

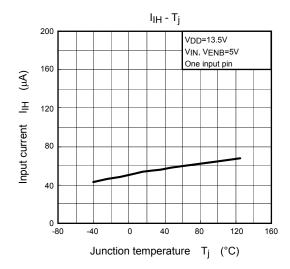

| Input current                               | I <sub>IH</sub>                                     | _               | V <sub>DD</sub> = 7 to 18V,<br>V <sub>IN</sub> = 5 V                                                                     | -                        | -                                         | 200                    | μА   | IN1 to IN6, ENB input                                                                                         |  |

| input current                               | I <sub>IL</sub>                                     |                 | V <sub>DD</sub> = 7 to 18 V,<br>V <sub>IN</sub> = 0 V                                                                    | - 10                     | ı                                         | 10                     | μА   | (per one input)                                                                                               |  |

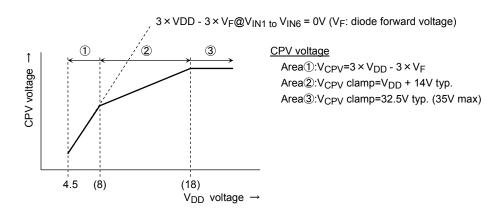

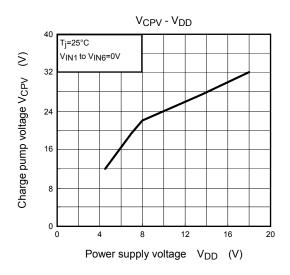

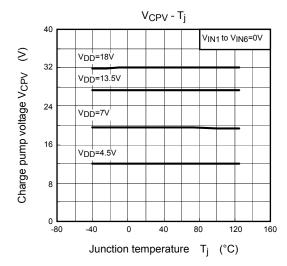

| Charge pump voltage                         |                                                     |                 | V <sub>DD</sub> = 7 V,<br>V <sub>IN1</sub> to V <sub>IN6</sub> = 0 V                                                     | V <sub>DD</sub><br>+10.9 | V <sub>DD</sub><br>+11.9                  | -                      | V    | $V_{CPV} \approx 3 \times (V_{DD} - V_F)$<br>$V_{CPV}$ denotes CPV pin<br>voltage.<br>(reference to SGND pin) |  |

| (Note4)(Note5)                              | V <sub>CPV</sub>                                    | -               | - V <sub>DD</sub> = 13.5 V, V <sub>DD</sub> V <sub>DD</sub> V <sub>DD</sub> V <sub>DD</sub> V <sub>CPV</sub> de voltage. |                          | V <sub>CPV</sub> denotes CPV pin voltage. |                        |      |                                                                                                               |  |

|                                             |                                                     |                 | V <sub>DD</sub> = 18 V,<br>V <sub>IN1</sub> to V <sub>IN6</sub> = 0 V                                                    | V <sub>DD</sub><br>+12   | V <sub>DD</sub><br>+14                    | V <sub>DD</sub><br>+16 | V    | (reference to SGND pin)                                                                                       |  |

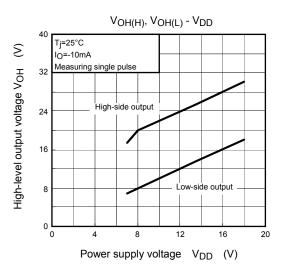

|                                             | V <sub>OH(H1)</sub>                                 |                 | V <sub>DD</sub> = 7V,<br>V <sub>IN</sub> = 5V,<br>I <sub>O</sub> = -10mA                                                 | -                        | V <sub>DD</sub><br>+ 9.9                  | -                      |      |                                                                                                               |  |

| High-side high-level<br>output voltage      | V <sub>OH(H2)</sub>                                 | _               | V <sub>DD</sub> = 13.5 V,<br>V <sub>IN</sub> = 5 V,<br>I <sub>O</sub> = -10 mA                                           | -                        | V <sub>DD</sub><br>+ 12                   | -                      |      | UU, VU and WU pin<br>voltage<br>(reference to SGND pin)<br>*Measuring single pulse                            |  |

|                                             | V <sub>OH(H3)</sub>                                 |                 | V <sub>DD</sub> = 18 V,<br>V <sub>IN</sub> = 5 V,<br>I <sub>O</sub> = -10 mA                                             | 1                        | V <sub>DD</sub><br>+ 12                   | -                      |      |                                                                                                               |  |

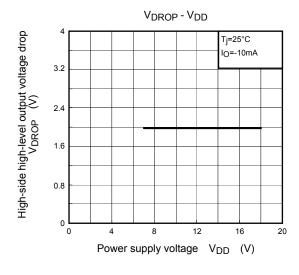

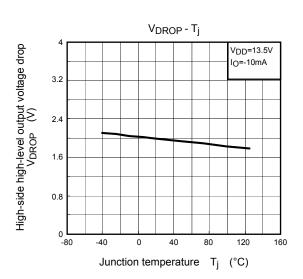

| High-side high-level<br>output voltage drop | V <sub>DROP</sub>                                   |                 | V <sub>IN</sub> = 5 V,<br>I <sub>O</sub> = -10 mA,<br>V <sub>DROP</sub> = V <sub>CPV</sub> - V <sub>OH</sub>             | -                        | 2                                         | 3                      | V    |                                                                                                               |  |

| High-side low-level<br>output voltage       | V <sub>OL(H)</sub>                                  | -               | V <sub>DD</sub> = 7 to 18 V,<br>V <sub>IN</sub> = 0 V,<br>I <sub>O</sub> = 0 A                                           | -                        | -                                         | 0.1                    |      |                                                                                                               |  |

| Low-side high-level output voltage          | V <sub>OH(L)</sub>                                  | -               | $V_{DD} = 7 \text{ to } 18V,$<br>$V_{IN} = 5V,$<br>$I_{O} = -10\text{mA}$                                                | V <sub>DD</sub> - 0.1    | V <sub>DD</sub>                           | -                      |      | UB, VB and WB pin voltage                                                                                     |  |

| Low-side low-level output voltage           | side low-level V <sub>OL(L)</sub> - V <sub>IN</sub> |                 | V <sub>DD</sub> = 7 to 18 V,<br>V <sub>IN</sub> = 0 V,<br>I <sub>O</sub> = 0 A                                           | -                        | -                                         | 0.1                    |      | (reference to SGND pin)                                                                                       |  |

| Output ON registance                        | R <sub>SOURCE</sub>                                 |                 | $V_{DD} = 13.5 \text{ V},$<br>$V_{IN} = 5 \text{ V},$<br>$I_{O} = -0.5 \text{ A}$                                        |                          | 7                                         | 10                     | Ω    | UU, VU, WU, UB, VB and                                                                                        |  |

| Output ON resistance                        | R <sub>SINK</sub>                                   | _               | V <sub>DD</sub> = 13.5 V,<br>V <sub>IN</sub> = 0 V,<br>I <sub>O</sub> = 0.5 A                                            | -                        | 4.5                                       | 10                     | 72   | WB output resistance pulse width $\leq$ 10 $\mu$ s                                                            |  |

2008-05-12 7

| Characteristic               |                           | Symbol                | Test<br>Circuit | Condition                                                                          | Min | Тур. | Max | Unit | Remarks                                                   |  |

|------------------------------|---------------------------|-----------------------|-----------------|------------------------------------------------------------------------------------|-----|------|-----|------|-----------------------------------------------------------|--|

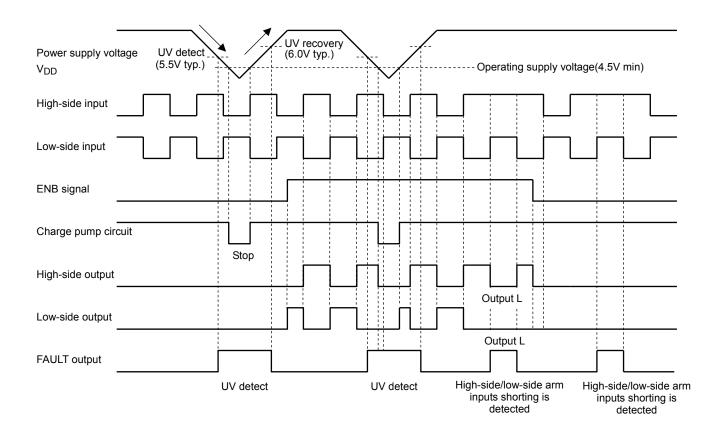

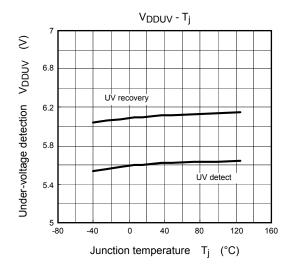

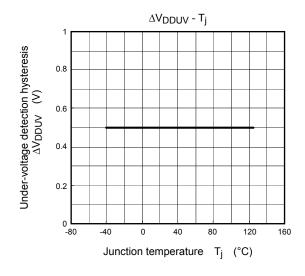

| Under-                       | Detection                 | $V_{DDUV}$            |                 |                                                                                    | 5.0 | 5.5  | 6.0 | V    | Under voltage detection                                   |  |

| voltage<br>detection         | Hysteresis                | $\Delta V_{DDUV}$     | _               | _                                                                                  | -   | 0.5  | -   | V    | voltage and hysteresis (V <sub>DD</sub> voltage detected) |  |

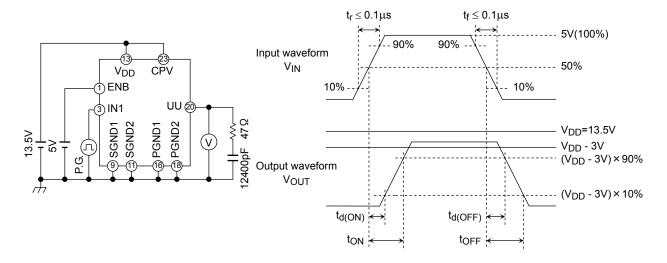

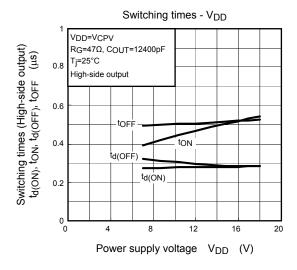

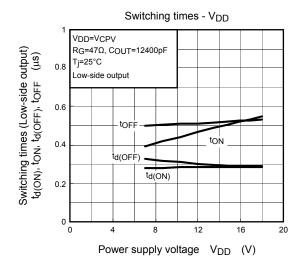

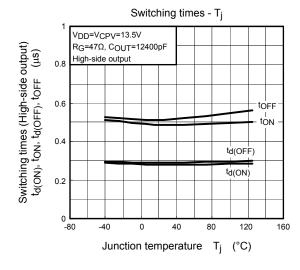

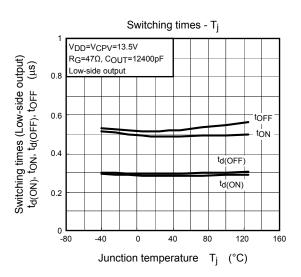

|                              | Turn-on<br>delay<br>time  | t <sub>d</sub> (ON)   |                 | $V_{DD}$ = 13.5 V, $V_{CPV}$ = 13.5 V, $C_{OUT}$ = 12400 pF, $R_{G}$ = 47 $\Omega$ | ı   | 0.25 | 1   |      |                                                           |  |

| Switching                    | Turn-on time              | t <sub>ON</sub>       | 1               |                                                                                    | ı   | 0.5  | 2   | μS   | UU, VU, WU, UB, VB<br>and WB switching<br>times           |  |

| times                        | Turn-off<br>delay<br>time | <sup>t</sup> d (OFF)  | 1               |                                                                                    | -   | 0.25 | 1   | μδ   |                                                           |  |

|                              | Turn-off<br>time          | tOFF                  |                 |                                                                                    | ı   | 0.5  | 2   |      |                                                           |  |

| Dead time (Note 6)           |                           | <sup>t</sup> dead     | -               | $V_{DD}$ = 13.5 V,<br>$t_{dead}$ = $t_{OFF}$ - $t_{d(ON)}$                         | I   | 0.25 | 1   | μ\$  |                                                           |  |

| Oscillating frequency        |                           | fosc -                |                 | $V_{DD}$ = 7 to 18V,<br>$R_{OSC}$ = 62 k $\Omega$ ,<br>$C_{OSC}$ = 270 pF          | 80  | 100  | 120 | kHz  |                                                           |  |

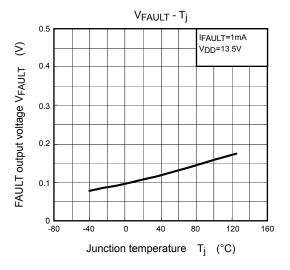

| FAULT output voltage         |                           | VFAULT                | -               | V <sub>DD</sub> = 7 to 18 V,<br>I <sub>FAULT</sub> = 1 mA                          | I   | -    | 0.8 | >    | FAULT pin low-level voltage (open-drain)                  |  |

| FAULT output leakage current |                           | I <sub>FAULT</sub>    | _               | V <sub>DD</sub> = 7 to 18 V,<br>V <sub>FAULT</sub> = 18 V                          | _   | _    | 10  | μΑ   |                                                           |  |

| FAULT out delay time         | put                       | t <sub>d(FAULT)</sub> | -               | -                                                                                  | -   | -    | 1   | μS   |                                                           |  |

Note3 : On-off output control, FAULT output and charge pump circuit operate from  $V_{DD} \ge 4.5V$ . However, charge pump voltage (CPV voltage) decreases by there are a lot of output currents in the condition with a low power supply voltage ( $V_{DD}$ ). It may be not enough voltage ( $V_{GS}$ ) to drive external power MOSFET. Be careful enough when using it .

Note4 : When converting foward voltage of the charge pump circuit diode by 0.7V. Please use the diode of high-speed type ( $trr \le 100ns$ ).

### Note5: About the charge pump voltage

So as not to apply over-voltage to the gate-source voltage ( $V_{GS}$ ) of external power MOSFET, and so as to become the best driving voltage, the clamping circuit is built into. When the CPV voltage reaches the value, so as not to apply over-voltage, the oscillation logic circuit of the charge pump is stopped.

Note6: About the dead time

High-side/low-side arm shorting mode is disabled by the internal logic. All outputs can be turned off. The deadtime of this product is  $1\mu s$ . That doesn't contain deadtime of external power MOSFET. Please set the deadtime of the input signal after considering the switching time of external power MOSFET.

Note7 : About the direct input method of the charge pump oscillation frequency By the oscillation signal from the outside to  $C_{OSC}$  it is possible to set up the charge pump oscillation. As this method, please input the signal to  $C_{OSC}$  after  $V_{DD}$  becomes over 9V. ( $V_{COSC} \le 5.5V$ ) Moreover, please use the terminal  $R_{OSC}$  by the resistance unconnection (open). When the CPV voltage reaches up to the clamping voltage, though the signal is input to  $C_{OSC}$ , the movement of the charge pump (oscillation) stops.

### **Test Circuit 1**

### **Switching times**

Example of measuring UU output

### **Truth Table**

| IN          | ENB | VOUT | FAULT | STATE                                         |

|-------------|-----|------|-------|-----------------------------------------------|

| L           | L   | L    | L     |                                               |

| Н           | ┙   | ┙    | ┙     | Normal                                        |

| L           | Н   | L    | L     | Normal                                        |

| Н           | Н   | Н    | L     |                                               |

| L           | ┙   | ┙    | Η     |                                               |

| Н           | ┙   | ┙    | Н     | V under veltage detection                     |

| L           | Н   | L    | Н     | V <sub>DD</sub> under-voltage detection       |

| Н           | Н   | Н    | Н     |                                               |

| High-side H | ┙   | ┙    | Н     | Upper and lower short sirewit input detection |

| Low-side H  | Н   | L    | Н     | Upper and lower short-circuit input detection |

9

- When under-voltage (5.5V typ.) is detected, only FAULT outputs "H". Neither the output nor the operation of the charge pump circuit stops(off).

- When a in-phase high side and the low side input are the "H" levels, all the outputs be made "L" level, and the "H" level is output to FAULT.

# **Timing chart**

11

12

# **Usage Precautions**

Precautions on dry packing

After unpacking dry or moisture-proof packing, make sure the device is mounted in place within 48 hours at a temperature and humidity of 30°C and 60% RH or less. Because the device is emboss-taped and cannot be processed by baking, always be sure to use it within the said allowable time after unpacking. Standard tape packing quantity: 2000 devices / reel (EL1).

# **Package Dimensions**

Weight: 0.29 g (typ.)

### RESTRICTIONS ON PRODUCT USE

20070701-EN GENERAL

- The information contained herein is subject to change without notice.

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc.

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in his document shall be made at the customer's own risk.

- The products described in this document shall not be used or embedded to any downstream products of which manufacture, use and/or sale are prohibited under any applicable laws and regulations.

- Please contact your sales representative for product-by-product details in this document regarding RoHS

compatibility. Please use these products in this document in compliance with all applicable laws and regulations

that regulate the inclusion or use of controlled substances. Toshiba assumes no liability for damage or losses

occurring as a result of noncompliance with applicable laws and regulations.