#### Rev C2, Page 1/67

#### FEATURES

- Input frequency of up to 125 kHz

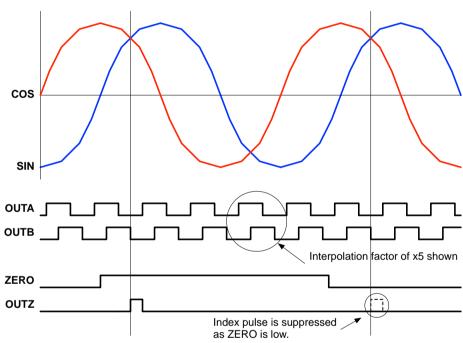

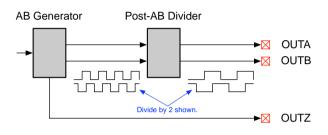

- Binary/decimal interpolation factors from x0.25 to x16384

- Post-AB divider [1/1 to 1/32] allows fractional resolution

Differential sine/cosine input signal range of

- 20 mV to 1.4 V peak-peak ♦ Automatic offset, gain match and phase correction

- Simple automatic one-pin calibration

- Easy configuration: by static pins (for generic ABZ output)

- Advanced configuration: 1-wire interface, 3 and 4-wire SPI (32 MHz), serial I<sup>2</sup>C EEPROM

- PWM or ABZ quadrature encoder output signals

- Incremental ABZ output to 8 MHz (32 MHz edge separation)

- Position and velocity read-out (32 bit SPI)

- Sophisticated error handling and signal monitoring

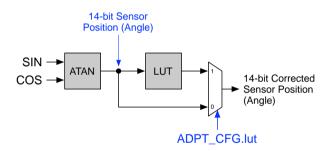

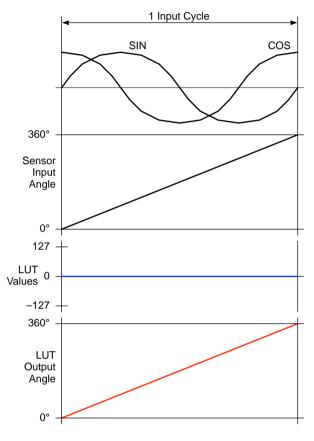

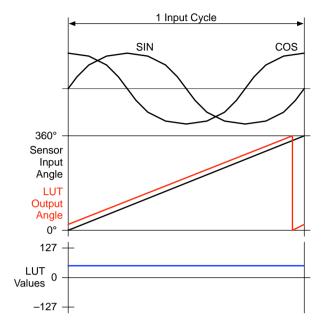

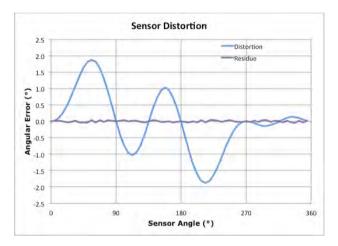

- Static 64 position LUT to compensate for arbitrary sensor distortions

- ♦ Supply voltage range of 3.1 V to 5.5 V

- Extended temperature range of -40 to +125 °C

**APPLICATIONS**

calibration

systems

٠

٠

۵

Sine/cosine interpolation

Signal conditioning with auto

Linear and rotary encoders

Flexible incremental encoder

Rev C2, Page 2/67

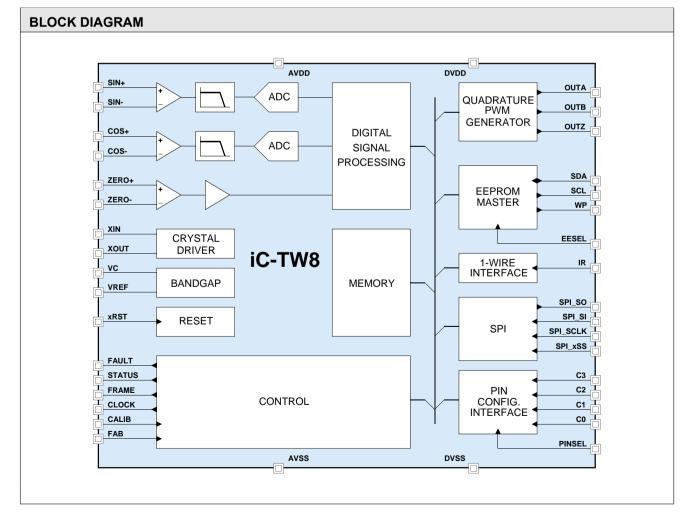

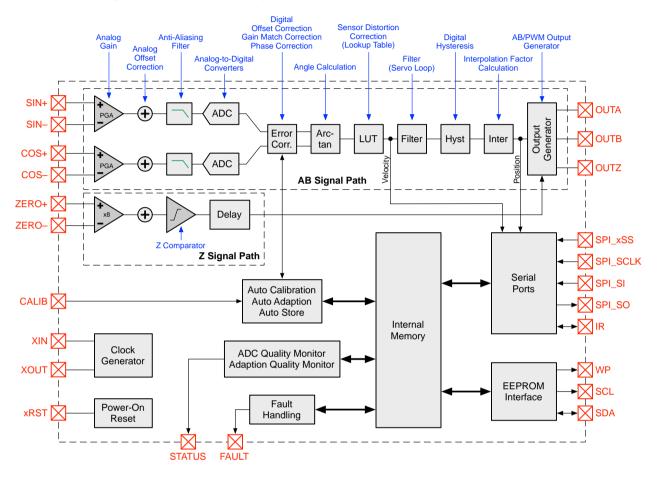

#### DESCRIPTION

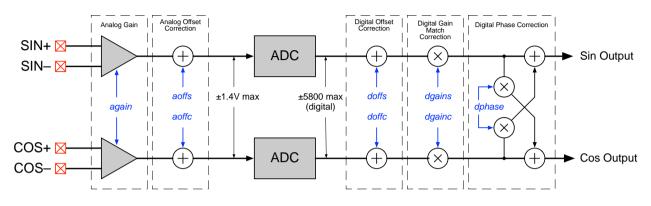

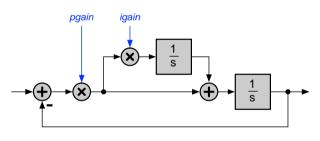

The iC-TW8 is a 16-bit application-specific DSP interpolator for sine/cosine signals with automatic calibration and adaption of signal path parameters during operation to maintain minimum angular error and jitter. Angular position is calculated at a programmable resolution of up to 65,536 increments per input cycle. Automatic calibration and adaption (correction during operation) of sensor offset, Sin/Cos amplitude match, and phase quadrature is provided. Additionally, a 64-byte lookup table (LUT) is available to correct for residual harmonic distortion in the sensor signals.

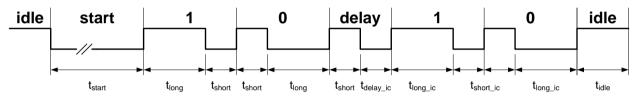

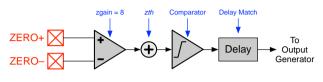

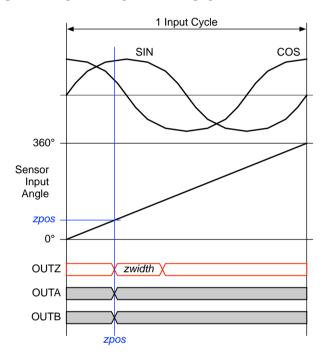

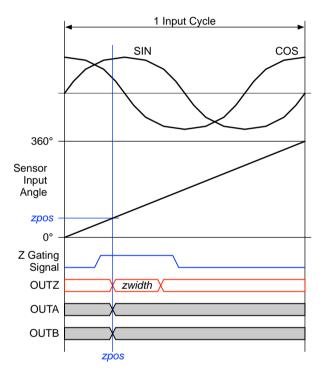

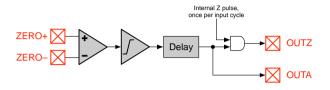

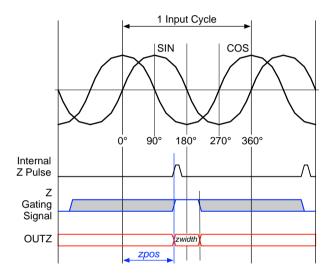

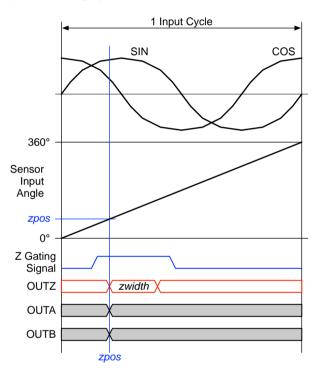

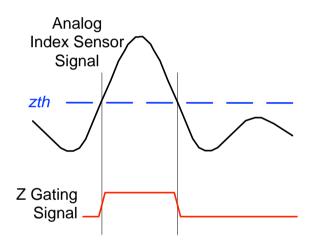

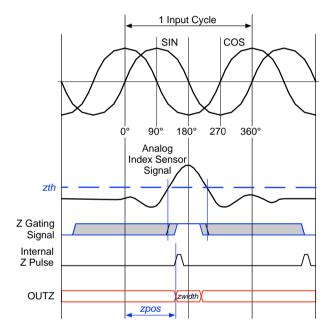

The iC-TW8 accepts 10 mV to 700 mV differential Sin/-Cos input signals directly from magnetic or optical sensors – no external signal conditioning is required in most applications. The differential zero (reference) input accepts a wide range of digital and analog index gating sources such as Hall or MR sensor bridges. The Z output width, position relative to the Sin/Cos inputs, and synchronization to the AB quadrature outputs is fully programmable.

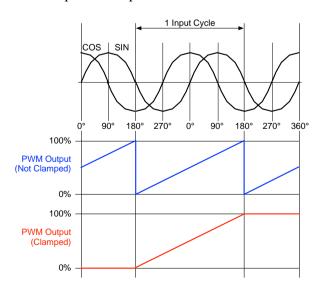

In addition to industry-standard incremental ABZ quadrature output, the iC-TW8 provides optional PWM (potentiometer) and serial-only (SPI or 1-wire) output modes for special or imbedded applications. The incremental ABZ quadrature output can be generated at a frequency of up to 8 MHz (31 ns edge spacing); the maximum output frequency can also be limited so as not to overwhelm connected counters.

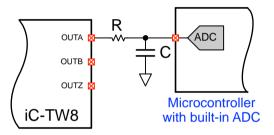

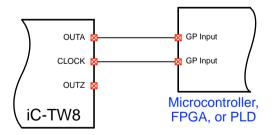

In PWM output mode, the iC-TW8 provides a differential pulse-width modulated signal proportional to the calculated angle (position) of the Sin/Cos inputs. An RC filter may be used to provide an analog voltage output for potentiometer applications, or to drive an external ADC for simple single-turn absolute applications. Synchronous digital filters may be implemented using an external microcontroller or FPGA for more sophisticated or imbedded applications. In serial-only output mode, the iC-TW8's internal 32-bit position counter and instantaneous angular velocity register can be read via the built-in SPI or 1-wire serial ports at clock rates of up to 32 MHz. Higher input signal frequencies are allowed in serial-only output mode since the ABZ output frequency limitation is not applicable.

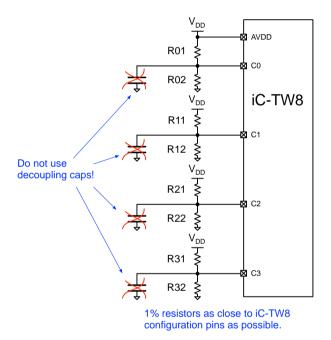

The iC-TW8 offers two configuration modes. Pin configuration mode provides simple, static configuration that does not require any programming or complicated calibration. Pin configuration mode uses a subset of the iC-TW8's complete capabilities including ABZ quadrature output, a limited choice of the most commonly used interpolation (resolution) and hysteresis values, and one-button calibration. Eight resistors set voltage levels at four configuration input pins to select all operating parameters, simplifying product assembly. One-button auto calibration sets input gain and compensates sensor offset and Sin/Cos channel gain match and phase with just a few input cycles and then stores the compensation values to EEPROM.

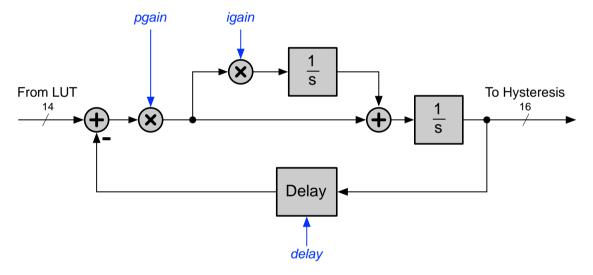

In more sophisticated applications, serial configuration mode allows access to all iC-TW8 features. Complete device configuration using the bi-directional SPI or 1-wire serial ports provides access to all resolutions (including fractional interpolation), the sensor distortion LUT, fully programmable hysteresis, and advanced noise/jitter filtering, quality monitoring, and fault detection capabilities.

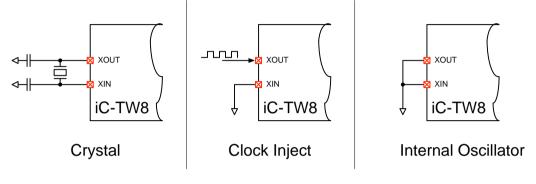

The iC-TW8 requires only two external components for operation, a serial EEPROM for storage of configuration and calibration data, and a clock oscillator or crystal. An internal RC oscillator is provided for cost-sensitive applications. Split analog and digital power supply inputs allow optimal filtering for noisy industrial environments. An integrated power-on reset circuit can be overridden by an external hardware reset signal if necessary.

#### Rev C2, Page 3/67

### CONTENTS

| PACKAGING INFORMATION                    | 4           |  |  |

|------------------------------------------|-------------|--|--|

| PIN CONFIGURATION QFN48-7x7<br>(topview) | 4<br>5<br>6 |  |  |

| ABSOLUTE MAXIMUM RATINGS                 |             |  |  |

| THERMAL DATA                             | 8           |  |  |

| ELECTRICAL CHARACTERISTICS               | 9           |  |  |

| OPERATING REQUIREMENTS                   | 12          |  |  |

| SPI Interface                                | 12<br>12 |

|----------------------------------------------|----------|

| ADDITIONAL INFORMATION                       | 14       |

| DESIGN REVIEW: Function Notes                | 14       |

| REVISION HISTORY                             | 15       |

| ATTACHMENTS                                  | 17       |

| PC: Description of Pin Configuration Mode .  | 17       |

| SC: Description of Serial Configuration Mode | 32       |

Rev C2, Page 4/67

#### PACKAGING INFORMATION

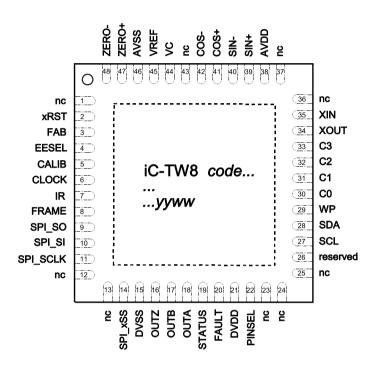

# PIN CONFIGURATION QFN48-7x7 (topview)

#### PIN FUNCTIONS No. Name Function

- 38 AVDD +3.1 V to 5.5 V Analog Supply Voltage AVDD and DVDD can be powered either mutually or separately but must be the same voltage.

- 46 AVSS Analog Ground AVSS must be connected to DVSS externally.

- 21 DVDD +3.1 V to 5.5 V Digital Supply Voltage

- 15 DVSS Digital Ground

- TP Connect the backside paddle to a ground plane which must have AVSS potential.

- ... other Refer to the Pin Function table for a detailed description.

Rev C2, Page 5/67

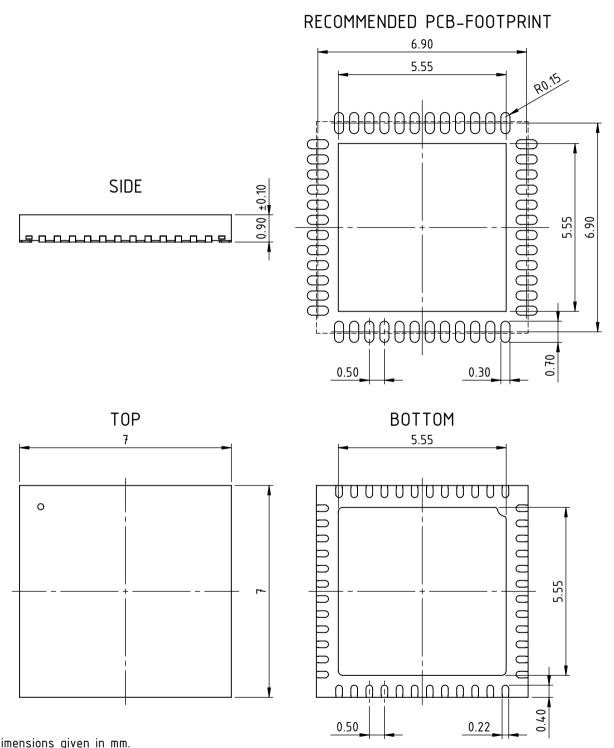

#### PACKAGE DIMENSIONS

All dimensions given in mm. Tolerances of form and position according to JEDEC MO-220.

| PI       | N FUNCTIO | ONS                                         |                                     |                                                                                                                                                                                                                                                                                                                                                                                        |

|----------|-----------|---------------------------------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No.      | Name      | I/O                                         | Function                            | Description                                                                                                                                                                                                                                                                                                                                                                            |

| 1        | nc        |                                             |                                     | Pin has no connection to die. Connect to DVSS on PCB.                                                                                                                                                                                                                                                                                                                                  |

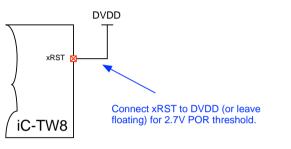

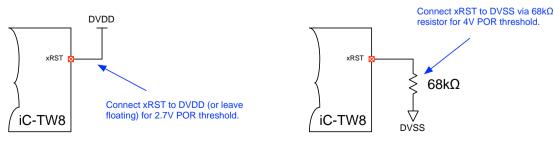

| 2        | xRST      | Digital in,<br>low active,<br>40 kΩ pull-up | Reset Input                         | The device is held in reset as long as xRST is low.<br>For operation at 5 V, connect 68 k $\Omega$ to DVSS (changes the pow-<br>er-on-reset threshold to approx. 4 V). Refer to section Power-on-Reset<br>and Startup for more information on reset.                                                                                                                                   |

| 3        | FAB       | Digital in,<br>5 kΩ pull-down               | Test Enable Input                   | Fabrication test is enabled when pin is high during reset. This pin must<br>be connected to DVSS for normal operation.                                                                                                                                                                                                                                                                 |

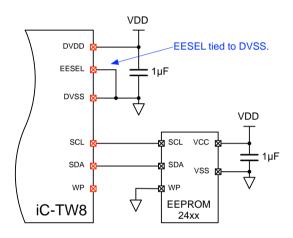

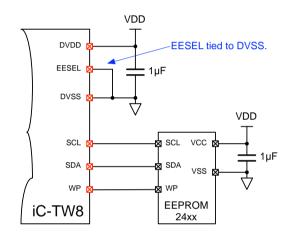

| 4        | EESEL     | Digital in,<br>150 kΩ pull-down             | Selection Input                     | Pin must be tied low.                                                                                                                                                                                                                                                                                                                                                                  |

| 5        | CALIB     | Digital in,<br>10 kΩ pull-up,<br>hysteresis | Calibration Control                 | Device enters calibration mode on falling edge of CALIB. Adaptation<br>parameters are written to the external eeprom on rising edge of CALIB.<br>This pin should be left floating or connected to DVDD if not used.                                                                                                                                                                    |

| 6        | CLOCK     | Digital in/out,<br>150 kΩ pull-down         | Clock Output                        | The pin is a programmable clock output that can be used for PWM synchronization.<br>A connection to DVSS is advisable when not in use.                                                                                                                                                                                                                                                 |

| 7        | IR        | Digital in/out,<br>150 kΩ pull-up           | 1-Wire Interface I/O                | Pin is bi-directional. Refer to Programmer's Reference for more details.                                                                                                                                                                                                                                                                                                               |

| 8        | FRAME     | Digital in/out,<br>150 kΩ pull-down         | Sync Output                         | This pin outputs the internal ADC sampling clock, which can be used to<br>synchronize downstream circuits.<br>A connection to DVSS is advisable when not in use.                                                                                                                                                                                                                       |

| 9        | SPI_SO    | Digital out                                 | SPI Slave Output                    | Pin directly connects to an SPI master MI pin.                                                                                                                                                                                                                                                                                                                                         |

| 10       | SPI_SI    | Digital in                                  | SPI Slave Input                     | Pin directly connects to SPI master MO pin.<br>This pin should be tied to DVSS if the SPI is not used.                                                                                                                                                                                                                                                                                 |

| 11       | SPI_SCLK  | Digital in, with hysteresis                 | SPI Slave Clock Input               | Pin connects to SPI master clock output. The input implements hys-<br>teresis to avoid double triggering.<br>This pin must be tied to DVSS if the SPI is not used.                                                                                                                                                                                                                     |

| 12<br>13 | nc<br>nc  |                                             |                                     | These pins have no connection to die. Connect to DVSS on PCB.                                                                                                                                                                                                                                                                                                                          |

| 14       | SPI_xSS   | Digital in,<br>low active                   | SPI Slave Select Input              | In 4-pin SPI mode this pin directly connects to the SPI master slave<br>select output. In case the SPI is operated in 3-pin mode, SPI_xSS<br>must be tied low to DVSS.<br>This pin is not debounced or filtered. A noise-free ground connection is<br>essential to avoid SPI_SO tri-stating during communication.<br>If the SPI is not used, this pin should be tight to DVDD or DVSS. |

| 15       | DVSS      | Ground                                      | Digital Ground                      | Pin must tie to high quality ground, usually a solid PCB plane.                                                                                                                                                                                                                                                                                                                        |

| 16       | OUTZ      | Digital out                                 | Z Output                            | Quadrature interface reference output.                                                                                                                                                                                                                                                                                                                                                 |

| 17       | OUTB      | Digital out                                 | B Output<br>PWM- Output<br>Z Window | In quadrature mode this is output B.<br>In PWM mode this is PWM-, the inverted output of OUTA.<br>In Z calibration mode (bit RB_TEST1.z_test = 1) this is the Z window<br>seen just after the input comparator.                                                                                                                                                                        |

| 18       | OUTA      | Digital out                                 | A Output<br>PWM+ Output<br>Z Window | In quadrature mode this is output A.<br>In PWM mode this is PWM+.<br>In Z calibration mode (bit RB_TEST1.z_test = 1) this is the Z window<br>used to gate the Z output.                                                                                                                                                                                                                |

| 19       | STATUS    | Digital out                                 | PWM Status Output                   | This pin provides proportional status information. Pin can drive a 10 mA LED and is widely configurable. Refer to section Monitoring Interpolation Quality for details.                                                                                                                                                                                                                |

| 20       | FAULT     | Digital out                                 | Error Status Output                 | Pin is low on error and is capable of driving a 10 mA LED. The error response can be configured as detailed in section Fault Handling for details.                                                                                                                                                                                                                                     |

| 21       | DVDD      | Supply                                      | Digital Power Supply                | +3.1 V to +5.5 V supply voltage terminal.<br>DVDD and AVDD must be the same voltage level (5 V or 3.3 V).                                                                                                                                                                                                                                                                              |

| 22       | PINSEL    | Digital in,<br>150 kΩ pull-down             | Configuration Mode Selection        | Tie pin to DVSS to enable serial configuration mode.<br>Tie pin to DVDD to select pin configuration mode.                                                                                                                                                                                                                                                                              |

| 23       | nc        |                                             |                                     |                                                                                                                                                                                                                                                                                                                                                                                        |

| 24       | nc        |                                             |                                     | These pins have no connection to die. Connect to DVSS on PCB.                                                                                                                                                                                                                                                                                                                          |

| 25       | nc        |                                             |                                     |                                                                                                                                                                                                                                                                                                                                                                                        |

| 26       | reserved  |                                             |                                     | Connect this pin to DVSS on PCB.                                                                                                                                                                                                                                                                                                                                                       |

| No. | Name  | I/O                              | Function                | Description                                                                                                                                                                   |

|-----|-------|----------------------------------|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27  | SCL   | Digital in/out,<br>10 kΩ pull-up | EEPROM Clock Line       | This pin connects to the EEPROM SCL pin. No external I2C pull-up resistor is required as $10 \text{ k}\Omega$ is integrated.                                                  |

| 28  | SDA   | Digital in/out,<br>10 kΩ pull-up | EEPROM Data Line        | This pin connects to the EEPROM SDA pin. No external I2C pull-up resistor is required as $10 \text{ k}\Omega$ is integrated.                                                  |

| 29  | WP    | Digital out                      | EEPROM Write Protection | This pin acts as the write protect signal and connects to the EEPROM WP pin. No external pull-up is required as this pin is a push-pull output actively driving low and high. |

| 30  | C0    |                                  |                         | If the pin configuration mode is used (pin PINSEL tied high), each pin                                                                                                        |

| 31  | C1    | Analog in                        | Configuration           | functions as 12-level configuration input.                                                                                                                                    |

| 32  | C2    | Analog In                        | Inputs                  | If serial configuration mode is used (pin PINSEL tied low), connect                                                                                                           |

| 33  | C3    |                                  |                         | these pins to DVSS on PCB.                                                                                                                                                    |

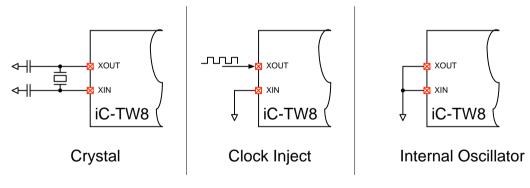

| 34  | XOUT  | Analog in/out                    | Crystal Terminal        | Pin should be tied to AVSS if no crystal is used.<br>An external oscillator or other square wave clock source can be used<br>to drive this pin. Refer to Providing a Clock.   |

| 35  | XIN   | Analog in                        | Crystal Terminal        | Pin must be tied to AVSS if no crystal is used.                                                                                                                               |

| 36  | nc    |                                  |                         | These pins have no connection to die. Connect to DVSS on PCB.                                                                                                                 |

| 37  | nc    |                                  |                         |                                                                                                                                                                               |

| 38  | AVDD  | Supply                           | Analog Power Supply     | +3.1 V to +5.5 V supply voltage terminal. Keep it clean!<br>DVDD and AVDD must be the same voltage level (5 V or 3.3 V).                                                      |

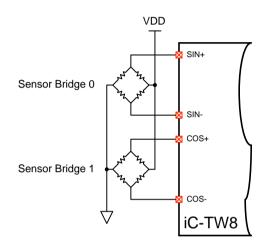

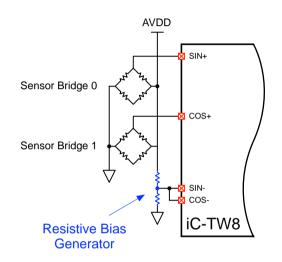

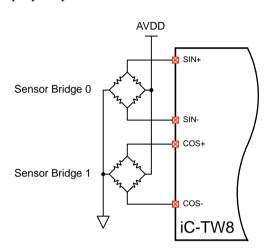

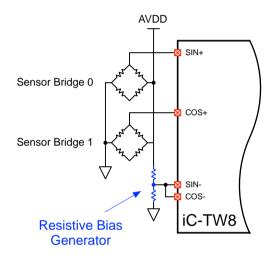

| 39  | SIN+  | Analog in                        | Sine Input +            | Differential sine signal input. For single ended sensors SIN- must be                                                                                                         |

| 40  | SIN-  | Analog in                        | Sine Input -            | biased to an appropriate DC level.                                                                                                                                            |

| 41  | COS+  | Analog in                        | Cosine Input +          | Differential cosine signal input. For single ended sensors COS- must                                                                                                          |

| 42  | COS-  | Analog in                        | Cosine Input -          | be biased to an appropriate DC level.                                                                                                                                         |

| 43  | nc    |                                  |                         | Pin has no connection to die. Connect to DVSS on PCB.                                                                                                                         |

| 44  | VC    | Analog out                       | Bias Output             | Decouple with $1 \mu F$ capacitor to AVSS. Do not inject noise into this pins as it directly impacts ADC conversion noise.                                                    |

| 45  | VREF  | Analog out                       | Bias Output             | Decouple with $1\mu F$ capacitor to AVSS. Do not inject noise into this pin as it directly impacts ADC conversion noise.                                                      |

| 46  | AVSS  | Ground                           | Analog Ground           | Pin must be tied to high quality ground, usually a solid PCB plane.                                                                                                           |

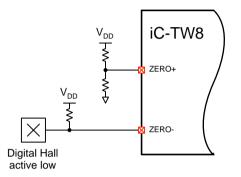

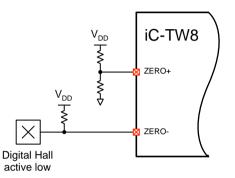

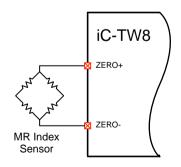

| 47  | ZERO+ | Analog in                        | Zero Input +            | Differential Zero Gating Input.                                                                                                                                               |

| 48  | ZERO- | Analog in                        | Zero Input -            | If single ended signal sources are used, the unused terminal (either ZERO+ or ZERO-) must be tied to an appropriate DC bias.                                                  |

Rev C2, Page 8/67

#### **ABSOLUTE MAXIMUM RATINGS**

These ratings do not imply operating conditions; functional operation is not guaranteed. Beyond these values damage may occur.

| Item | Symbol        | Parameter                                                  | Conditions                                                                                |      |               | Unit |

|------|---------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------|------|---------------|------|

| No.  |               |                                                            |                                                                                           | Min. | Max.          |      |

| G001 | DVDD,<br>AVDD | Voltage at DVDD, AVDD                                      | referenced to AVSS                                                                        | -0.3 | 6             | V    |

| G002 | dVDD          | Difference Voltage between<br>DVDD and AVDD                |                                                                                           | -0.3 | +0.3          | V    |

| G003 | dVSS          | Difference Voltage between<br>DVSS and AVSS                |                                                                                           | -0.3 | +0.3          | V    |

| G004 | Vpin          | Pin Voltage at any pin versus AVSS                         | referenced to AVSS                                                                        | -0.3 | AVDD +<br>0.5 | V    |

| G005 | Ipin          | Input Current at any pin, except<br>AVDD, AVSS, DVDD, DVSS |                                                                                           | -10  | 10            | mA   |

| G006 | Vesd1         | ESD Susceptibility Of Signal Input Pins                    | HBM, 100 pF discharged through 1.5 k $\Omega$ ; pins SIN+, SIN-, COS+, COS-, ZERO+, ZERO- | 2    |               | kV   |

| G007 | Vesd2         | ESD Susceptibility Of Remaining Pins                       | HBM, 100 pF discharged through $1.5 \text{ k}\Omega$                                      | 2    |               | kV   |

| G008 | Tj            | Junction Temperature                                       |                                                                                           | -40  | 150           | °C   |

| G009 | Ts            | Storage Temperature                                        |                                                                                           | -40  | 150           | °C   |

#### THERMAL DATA

| ltem | Symbol | Parameter                           | Conditions                                            |      |      | Unit |     |

|------|--------|-------------------------------------|-------------------------------------------------------|------|------|------|-----|

| No.  |        |                                     |                                                       | Min. | Тур. | Max. |     |

| T01  | Та     | Operating Ambient Temperature Range |                                                       | -40  |      | 125  | °C  |

| T02  | Rthja  | Thermal Resistance Chip to Ambient  | QFN48 surface mounted to PCB according to<br>JEDEC 51 |      | 30   |      | K/W |

All currents flowing into the device pins are positive; all currents flowing out of the device pins are negative.

Rev C2, Page 9/67

### **ELECTRICAL CHARACTERISTICS**

| tem   | Symbol                 | Parameter                                       | Conditions                                                                                                                                      |        |                |               | Unit       |

|-------|------------------------|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------------|---------------|------------|

| No.   | -                      |                                                 |                                                                                                                                                 | Min.   | Тур.           | Max.          |            |

| Total | Device                 |                                                 |                                                                                                                                                 |        |                |               |            |

| 001   | AVDD,<br>DVDD          | Permissible Supply Voltage<br>AVDD, DVDD        |                                                                                                                                                 | 3.1    |                | 5.5           | V          |

| 002   | IDD                    | Total Supply Current in AVDD and DVDD           | fin = 1 kHz, Increments 4096, Post-AB Divider 1,<br>error-free boot-up from EEPROM;<br>VDD = 5 V, 32 MHz crystal<br>VDD = 3.3 V, 20 MHz crystal |        | 25<br>12       | 35<br>20      | mA<br>mA   |

| Signa | I Inputs an            | d Amplifiers: SIN+, SIN-, COS+, C               | OS-                                                                                                                                             |        |                |               |            |

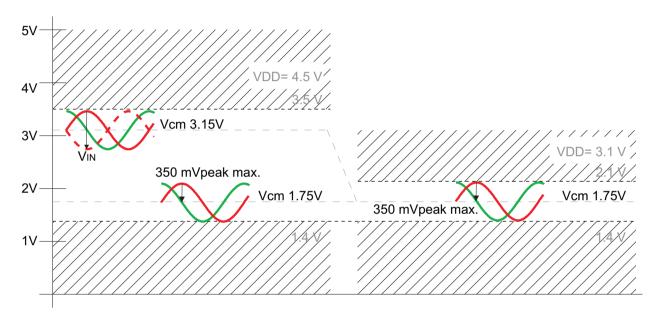

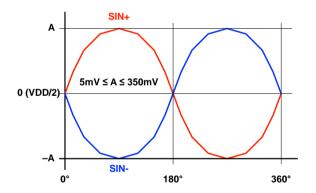

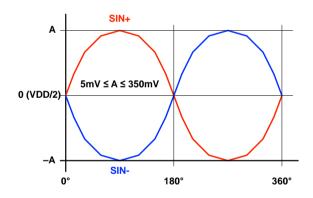

| 101   | Vin()                  | Permissible Input Voltage Range                 | refer to Figure 1                                                                                                                               | 1.4    |                | AVDD -<br>1.0 | V          |

| 102   | V <sub>IN</sub> ()     | Permissible Input Amplitude                     | refer to Figure 1                                                                                                                               |        |                | 700           | mVpp       |

| 103   | V <sub>IN</sub> ()diff | Permissible Input Amplitude,<br>differential    |                                                                                                                                                 |        |                | 1.4           | Vpp        |

| 104   | Vos()                  | Amplifier Input Offset Voltage                  |                                                                                                                                                 |        |                | ±15           | mV         |

| 105   | lin()                  | Input Leakage Current                           |                                                                                                                                                 |        |                | ±50           | nA         |

| 107   | OFFcorr                | Correctable Input Offset Voltage                | as percentage of input signal amplitude; input<br>offset voltage is the sum of sensor offset plus<br>amplifier offset (item 104);               | ±100   |                |               | %          |

| 108   | Acorr                  | Correctable SIN/COS Amplitude<br>Mismatch       | max(Asin, Acos) / min(Asin, Acos), whereas<br>Asin and Acos are the SIN/COS input ampli-<br>tudes respectively.                                 | 1.24   |                |               |            |

| 109   | PHIcorr                | Correctable SIN/COS Phase<br>Error              | (step size 0.052 degree)                                                                                                                        |        | ±53            |               | deg        |

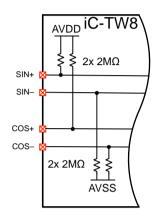

| 110   | Rpu()                  | Pull-Up Resistor at SIN+, COS+                  | MAIN_CFG.pull = 1                                                                                                                               |        | 3              |               | MΩ         |

| 111   | Rpd()                  | Pull-Down Resistor at SIN-, COS-                | MAIN_CFG.pull = 1                                                                                                                               |        | 3              |               | MΩ         |

| Index | Signal Inp             | uts and Amplifier: ZERO+, ZERO-                 | · · ·                                                                                                                                           |        |                |               |            |

| 201   | Vin()                  | Permissible Input Voltage                       |                                                                                                                                                 | 0      |                | AVDD          | V          |

| 202   | Vos()                  | Input Referred Offset Voltage                   |                                                                                                                                                 |        |                | ±15           | mV         |

| 203   | lin()                  | Input Leakage Current                           |                                                                                                                                                 |        |                | ±50           | nA         |

| Conv  | erter Perfor           | rmance                                          | ц                                                                                                                                               |        |                | 1             |            |

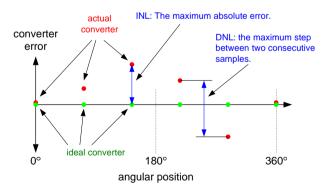

| 301   | INL                    | Integral Nonlinearity                           | refer to Figure 3, 1 Vpp-diff SIN/COS input with compensated offset, gain and phase                                                             |        |                | 0.08          | deg        |

| 302   | DNL                    | Differential Nonlinearity                       | refer to Figure 3, 1 Vpp-diff SIN/COS input with compensated offset, gain and phase                                                             |        |                | 0.02          | deg        |

| 303   | N                      | Output Angle Noise                              | 1 Vpp-diff SIN/COS input, fin = 0 Hz                                                                                                            |        |                | 0.08          | deg        |

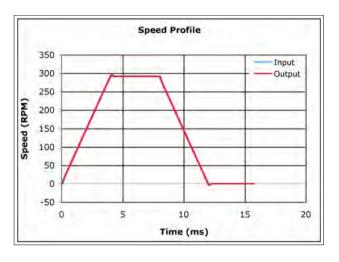

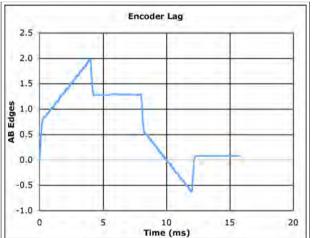

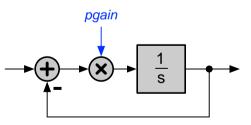

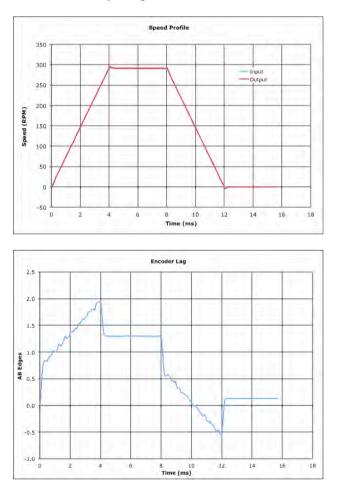

| 305   | tp()io                 | Input-to-Output Latency                         | fosc = 32 MHz;<br>MAIN_FLTR.fb = 0 (lag recovery disabled)<br>MAIN_FLTR.fb = 1 (lag recovery enabled)                                           |        | 24<br>4        |               | μs<br>µs   |

|       |                        |                                                 | fosc = 24 MHz;<br>MAIN_FLTR.fb = 0 (lag recovery disabled)<br>MAIN_FLTR.fb = 1 (lag recovery enabled)                                           |        | 32<br>5.3      |               | μs<br>μs   |

| Clock | : XIN, XOU             | T                                               |                                                                                                                                                 |        |                | 1             | . <u> </u> |

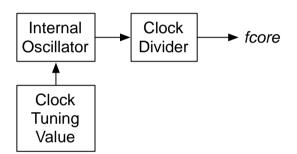

| 401   | fxtl                   | Permissible External Frequency driven into XOUT | AVDD, DVDD = 5 V<br>AVDD, DVDD = 3.3 V                                                                                                          | 6<br>6 |                | 32<br>24      | MHz<br>MHz |

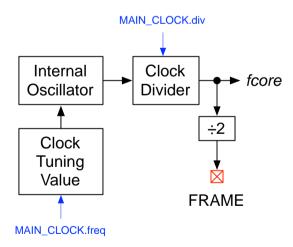

| 402   | fosc                   | Internal Oscillator Frequency                   | AVDD, DVDD = 5 V, permissible maximum<br>Tj = 27 °C, MAIN_CLOCK.freq = 0                                                                        |        | 20             | 32            | MHz<br>MHz |

|       |                        |                                                 | AVDD, DVDD = 3.3 V, permissible maximum<br>Tj = 27 °C, MAIN_CLOCK.freq = 0                                                                      |        | 18             | 24            | MHz<br>MHz |

| 403   | TCosc                  | Internal Oscillator Temperature<br>Dependancy   | AVDD, DVDD = 5 V<br>AVDD, DVDD = 3.3 V                                                                                                          |        | -0.07<br>-0.09 |               | %/K<br>%/K |

| 404   | VCosc                  | Internal Oscillator Power Supply<br>Dependancy  |                                                                                                                                                 |        | 1.18           |               | MHz/\      |

Rev C2, Page 10/67

#### **ELECTRICAL CHARACTERISTICS**

| tem | Symbol       | Parameter                                                   | Conditions                                                                                                                                 |              | 1          |              | Unit       |

|-----|--------------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------|--------------|------------|

| No. |              |                                                             |                                                                                                                                            | Min.         | Тур.       | Max.         |            |

|     | and Start-L  |                                                             |                                                                                                                                            | m            | , ,        |              | 0          |

| 601 | DVDDon       | DVDD Reset Threshold                                        | increasing voltage at DVDD;<br>xRST tied to DVDD                                                                                           |              | 2.7        |              | v          |

|     |              |                                                             | xRST lied to $DVDD$<br>xRST connected through 68 k $\Omega$ to DVSS                                                                        |              | 4.0        |              | v          |

| 602 | Vt()hi       | Input Logic Threshold High                                  | increasing voltage at xRST                                                                                                                 | -            |            | 2.7          | V          |

| 603 | Vt()lo       | Input Logic Threshold Low                                   |                                                                                                                                            | 0.8          |            |              | V          |

| 604 | Rpu()        | Pull-Up Resistor                                            | V() = 0 DVDD - 1 V                                                                                                                         | _            | 40         |              | kΩ         |

| 605 | tstart       | Startup Time                                                | AVDD, DVDD = 5 V, fxtl = 24 MHz by crystal;<br>pin configuration (EEPROM connected)<br>ready for serial configuration:<br>EEPROM connected |              | 100<br>100 |              | ms<br>ms   |

|     |              |                                                             | no EEPROM, SDA = AVSS<br>no EEPROM, SDA = AVDD                                                                                             |              | 10<br>100  |              | ms<br>ms   |

| 606 | td()lo       | Low-Level Duration for Reset<br>Triggering                  | V(xRST) < Vt(xRST)lo                                                                                                                       | 10           |            |              | ns         |

|     | I Input Pins |                                                             | CLK, SPI_xSS, PINSEL, SCL, SDA, FAB                                                                                                        |              |            |              |            |

| 701 | Vt()hi       | Input Logic Threshold High                                  | DVDD = 5 V                                                                                                                                 |              |            | 2.2          | V          |

|     |              |                                                             | DVDD = 3.3 V                                                                                                                               |              |            | 2.2          | V          |

| 702 | Vt()lo       | Input Logic Threshold Low                                   | DVDD = 5 V<br>DVDD = 3.3 V                                                                                                                 | 0.8<br>0.8   |            |              | V<br>V     |

| 703 | Vt()hi       | Input Logic Threshold High<br>CALIB, SPI_SCLK               | DVDD = 5 V<br>DVDD = 3.3 V                                                                                                                 |              |            | 3.75<br>2.47 | V<br>V     |

| 704 | Vt()lo       | Input Logic Threshold Low<br>CALIB, SPI_SCLK                | DVDD = 5 V<br>DVDD = 3.3 V                                                                                                                 | 0.75<br>0.49 |            |              | V<br>V     |

| 706 | llk()        | Input Leakage Current at SPI_SI, SPI_SCLK, SPI_XSS          |                                                                                                                                            |              |            | ±50          | nA         |

| 707 | Rpu()        | Pull-Up Resistor at IR                                      |                                                                                                                                            |              | 150        |              | kΩ         |

| 708 | Rpu()        | Pull-Up Resistor at<br>CALIB, SCL, SDA                      |                                                                                                                                            |              | 10         |              | kΩ         |

| 709 | Rpd()        | Pull-Down Resistor at EESEL,<br>CLOCK, FRAME, PINSEL        |                                                                                                                                            |              | 150        |              | kΩ         |

| 710 | Rpd()        | Pull-Down Resistor at FAB                                   |                                                                                                                                            |              | 4          |              | kΩ         |

| 711 | tstore       | Required CALIB Wait Time for<br>Parameter Storage to EEPROM | writing of 150 bytes after CALIB lo $\rightarrow$ hi;<br>for EEPROM with write time of 5 ms<br>for EEPROM with write time of 2 ms          |              |            | 770<br>320   | ms<br>ms   |

|     |              | n <b>s:</b><br>//E, SPI_SO, OUTA, OUTB, OUTZ,               | STATUS FAULT SCL SDA WP                                                                                                                    | 11           |            |              |            |

| 801 | Vs()hi       | Output Voltage High                                         | pins SCL, SDA excluded;                                                                                                                    |              |            |              |            |

|     |              | o alpar i olago i ligit                                     | DVDD = 5 V, $IOUT = 4 mADVDD = 3.3 V$ , $IOUT = 4 mA$                                                                                      | 4.4<br>2.7   |            |              | V<br>V     |

| 802 | Vs()lo       | Output Voltage Low                                          | DVDD = 5 V, IOUT = -4 mA<br>DVDD = 3.3 V, IOUT = -4 mA                                                                                     |              |            | 0.45<br>0.45 | V<br>V     |

| 803 | ldc()max     | Permissible Output DC Load                                  | per pin                                                                                                                                    |              |            | ±10          | mA         |

| 804 | Idcmax       | Permissible Total Output DC Load                            | for all output pins in aggregate                                                                                                           |              |            | ±60          | mA         |

| 805 | tr()         | Rise Time                                                   | DVDD = 5 V, CL = 50 pF<br>DVDD = 3.3 V, CL = 50 pF                                                                                         | 50<br>30     |            |              | ns<br>ns   |

| 806 | tf()         | Fall Time                                                   | DVDD = 5 V, CL = 50 pF<br>DVDD = 3.3 V, CL = 50 pF                                                                                         | 50<br>30     |            |              | ns<br>ns   |

| 807 | fclk(SCL)    | SCL Clock Frequency                                         | I2C access to EEPROM on power up after configuration, max. at fosc = 32 MHz                                                                |              | fosc/128   | 100<br>250   | kHz<br>kHz |

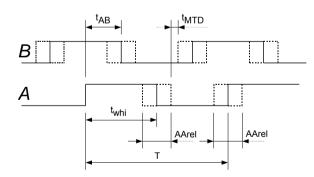

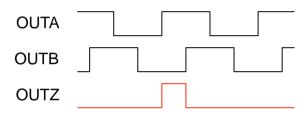

| 808 | twhi         | Duty Cycle at OUTA, OUTB                                    | referred to period T, see Fig. 2                                                                                                           |              | 50         |              | %          |

| 809 | tAB          | Output Phase OUTA vs. OUTB                                  | referred to period T, see Fig. 2                                                                                                           |              | 25         |              | %          |

| 810 | tMTD         | Minimum Edge Distance at OUTA vs. OUTB                      | fcore = fxtl or fosc, AB_CFG1.div = 0,<br>AB_VTOP = 0, see Fig. 2                                                                          |              | 1/fcore    |              |            |

Rev C2, Page 11/67

#### **ELECTRICAL CHARACTERISTICS**

| Operating conditions: AVDD = DVDD = 3.15.5 V, Tj = -40+125 °C, reference point AVSS unless oth | erwise stated |

|------------------------------------------------------------------------------------------------|---------------|

|------------------------------------------------------------------------------------------------|---------------|

| ltem   | em Symbol Parameter Conditions       |                                |                                      |      |      | Unit |      |  |  |  |

|--------|--------------------------------------|--------------------------------|--------------------------------------|------|------|------|------|--|--|--|

| No.    | _                                    |                                |                                      | Min. | Тур. | Max. |      |  |  |  |

| Bias C | Bias Outputs: VC, VREF               |                                |                                      |      |      |      |      |  |  |  |

| 901    | VC                                   | Bias Voltage at VC             | I(VC) = 0                            |      | 50   |      | %VDD |  |  |  |

| 902    | dVREF                                | Bias Voltage at VREF versus VC | dVREF = V(VREF) - V(VC); I(VREF) = 0 |      | -1   |      | V    |  |  |  |

| Config | Configuration Inputs: C0, C1, C2, C3 |                                |                                      |      |      |      |      |  |  |  |

| A01    | llk()                                | Input Leakage Current          |                                      |      |      | ±1   | μA   |  |  |  |

Figure 1: Permissible input voltage range (@5 V -10%, and @3.3 V -5%)

Figure 2: Description of AB output signals.

Figure 3: Definition of integral and differential nonlinearity.

Rev C2, Page 12/67

#### **OPERATING REQUIREMENTS: SPI Interface**

Operating Conditions: AVDD = DVDD = +3.1 ... +5.5 V, AVSS = DVSS = 0 V, Tj = -40...125 °C

| Item   | Symbol       | Parameter                                                                        | Conditions                                                                           |      |          | Unit       |

|--------|--------------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|------|----------|------------|

| No.    |              |                                                                                  |                                                                                      | Min. | Max.     |            |

| SPI In | terface Timi | ng                                                                               |                                                                                      |      |          |            |

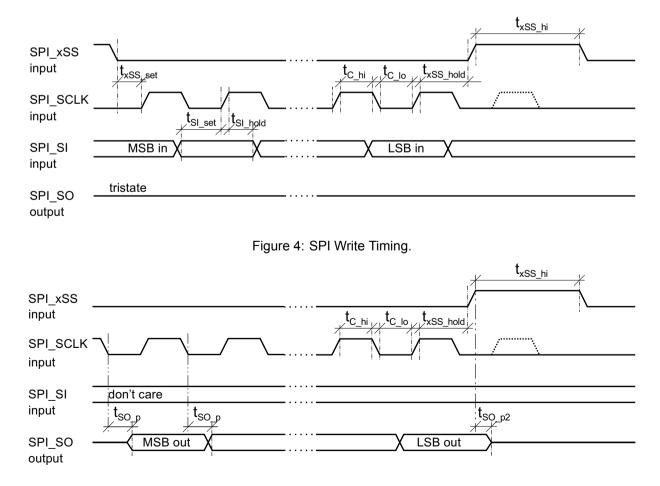

| 1001   | txSS_set     | Setup Time: SPI_xSS hi $\rightarrow$ lo before SPI_SCLK lo $\rightarrow$ hi      |                                                                                      | 15   |          | ns         |

| 1002   | txSS_hold    | Hold Time: SPI_xSS Io after SPI_SCLK Io $\rightarrow$ hi                         |                                                                                      | 25   |          | ns         |

| 1003   | txSS_hi      | SPI_xSS Signal Duration hi                                                       |                                                                                      | 15   |          | ns         |

| 1004   | tSI_set      | Setup Time: SPI_SI stable before SPI_SCLK lo $\rightarrow$ hi                    |                                                                                      | 5    |          | ns         |

| 1005   | tSI_hold     | Hold Time: SPI_SI stable after SPI_SCLK lo $\rightarrow$ hi                      |                                                                                      | 10   |          | ns         |

| 1006   | f(SCLK)      | SPI_SCLK Clock Frequency                                                         | AVDD = DVDD = +4.5 +5.5 V, fosc = 32 MHz<br>AVDD = DVDD = +3.1 +5.5 V, fosc = 24 MHz |      | 24<br>20 | MHz<br>MHz |

| 1007   | tC_hi        | SPI_SCLK Signal Duration hi                                                      |                                                                                      | 10   |          | ns         |

| 1008   | tC_lo        | SPI_SCLK Signal Duration lo                                                      |                                                                                      | 10   |          | ns         |

| 1009   | tSO_p        | Propagation Delay: SPI_SO stable after SPI_SCK hi $\rightarrow$ lo               |                                                                                      |      | 20       | ns         |

| 1010   | tSO_p2       | Propagation Delay:<br>SPI_SO high impedance after<br>SPI_xSS lo $\rightarrow$ hi |                                                                                      |      | 20       | ns         |

Rev C2, Page 13/67

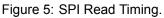

#### **OPERATING REQUIREMENTS: 1-Wire Interface**

#### Operating Conditions: AVDD = DVDD = +3.1 ... +5.5 V, AVSS = DVSS = 0 V, Tj = -40...125 $^\circ\text{C}$

| Item   | Symbol                | Parameter                        | Conditions            |                        |                        | Unit     |

|--------|-----------------------|----------------------------------|-----------------------|------------------------|------------------------|----------|

| No.    |                       |                                  |                       | Min.                   | Max.                   |          |

| 1W-Int | erface Tim            | ing                              |                       |                        |                        |          |

| 1101   | t <sub>start</sub>    | Low Time Start Condition         |                       | 2                      |                        | ms       |

| 1102   | t <sub>long</sub>     | Unit Time Long                   | unprogrammed EEPROM   | 50<br>100              | 500                    | μs<br>μs |

| 1103   | t <sub>short</sub>    | Unit Time Short                  | unprogrammed EEPROM   | 25<br>50               | t <sub>long</sub> - 25 | · ·      |

| I104   | t <sub>idle</sub>     | Interface Idle Before New Access |                       | 100                    |                        | μs       |

| 1105   | t <sub>delay_ic</sub> | Memory Read Delay by IC          | iC-TW8 returning data | t <sub>short</sub> / 2 | t <sub>short</sub>     |          |

| I106   | t <sub>long_ic</sub>  | Unit Time Long by IC             | iC-TW8 returning data | t <sub>long</sub> / 2  | t <sub>long</sub>      |          |

| I107   | t <sub>short_ic</sub> | Unit Time Short by IC            | iC-TW8 returning data | t <sub>short</sub> / 2 | t <sub>short</sub>     |          |

Figure 6: 1-Wire interface timing (PWM bit stream).

#### ADDITIONAL INFORMATION

#### **Documentation**

- · Pin Configuration Manual: refer to attachment PC

- · Serial Configuration Manual: refer to attachment SC

- Programmer's Reference: available on request, please contact iC-Haus applications engineering.

- Evaluation Board Description iC-TW8 EVAL TW8\_1D: refer to iC-Haus website for download.

- GUI Software: refer to iC-Haus website for download.

#### **Design Tools**

• Rotary Encoder Design Tool (Excel spreadsheet): available on request, please contact iC-Haus applications engineering.

### **Application Notes**

• (under preparation)

#### **DESIGN REVIEW: Function Notes**

| iC-TW8 C1 |                                |                                                                                                             |  |

|-----------|--------------------------------|-------------------------------------------------------------------------------------------------------------|--|

| No.       | Function, Parameter/Code       | Description and Application Notes                                                                           |  |

| 1         | Look-up Table:<br>ADPT_CFG.lut | The distortion look-up table is not featured by chip release C1;<br>mandatory programming: ADPT_CFG.lut = 0 |  |

#### Table 7: Notes on chip functions regarding iC-TW8 chip release C1.

| iC-TW8 D | 1, D2, D3                                      |                                                                                                                                                                                                                                                                                                                      |

|----------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No.      | Function, Parameter/Code                       | Description and Application Notes                                                                                                                                                                                                                                                                                    |

| 1        | Adaption Quality Monitoring:<br>MON_CFG.adapt  | If enabling adaption quality monitoring, note that this reduces the permissible adaption limits and quality thresholds for MON_OFF, MON_GAIN, and MON_PHASE (allowed maximum value is 7 instead of 12). Refer to the Programmer's Reference for further details.                                                     |

| 2        | ADC Underflow:<br>STAT_SP.adcuf                | This status error is initially raised on startup because the signal amplitude (first ADC_AMP value) has not been calculated yet.                                                                                                                                                                                     |

| 3        | ADC Fault Enable:<br>FLT_EN.adc                | Do not enable latching (freezes ADC underflow status raised on startup).<br>If latching ADC overflow and underflow conditions is essential to the system, use<br>an external MCU to set the FLT_EN.adc after startup has been completed.                                                                             |

| 4        | 32-bit Position Counter Reset:<br>MAIN_Z.reset | To reset the 32-bit position counter by an index signal, use MAIN_Z.reset = 1 to reset whenever the Z output is active.<br>Do not use MAIN_Z.reset = 2 to reset by the ZERO input signal (as described in previous datasheet releases), as this may cause invalid data for SPI output and spurious AB output bursts. |

#### Table 8: Notes on chip functions regarding iC-TW8 chip releases D1, D2, D3

| iC-TW8 D4 |                                                               |                                   |

|-----------|---------------------------------------------------------------|-----------------------------------|

| No.       | Function, Parameter/Code                                      | Description and Application Notes |

|           | None at time of printing (related to this datasheet release). |                                   |

#### Table 9: Notes on chip functions regarding iC-TW8 chip release D4.

Rev C2, Page 15/67

#### **REVISION HISTORY**

| Rel. | Rel. Date* | Chapter                      | Modification    | Page |

|------|------------|------------------------------|-----------------|------|

| A1   | 2012-11-22 | All chapters and attachments | Initial release | all  |

| Rel. | Rel. Date* | Chapter     | Modification                  | Page |

|------|------------|-------------|-------------------------------|------|

| A2   | 2013-01-29 | ATTACHMENTS | Attachments PC and SC updated | all  |

| Rel. | Rel. Date* | Chapter                                     | Modification                                                                                                                                                                                                                                                                                                                            | Page |

|------|------------|---------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| B1   | 2014-03-17 | PACKAGING INFORMATION                       | Drawing added for package dimensions and recommended footprint                                                                                                                                                                                                                                                                          | 5    |

|      |            | ELECTRICAL<br>CHARACTERISTICS               | Item 002: max. values supplemented;<br>Item 101: Fig. 1 added;<br>Item 402: typ. value;<br>Item 602: max. value, 605: typ. value supplemented;<br>Item 801: pins SDA and SCL excluded; 802: max. value and unit;<br>Items 800ff: with IR and SCL as outputs;<br>Items 102, 703, 704, 807 introduced as new items (former 703 excluded); | 9-10 |

|      |            | OPERATING REQUIREMENTS:<br>1-Wire Interface | Interface timing supplemented                                                                                                                                                                                                                                                                                                           | 13   |

|      |            | ADDITIONAL INFORMATION                      | List supplemented                                                                                                                                                                                                                                                                                                                       | 14   |

|      |            | ORDERING INFORMATION                        | Board size corrected, REDT download link removed;                                                                                                                                                                                                                                                                                       | 16   |

|      |            | ATTACHMENTS                                 | Attachments PC and SC updated                                                                                                                                                                                                                                                                                                           | 17ff |

| Rel. | Rel. Date* | Chapter                                       | Modification                                                                                                                                                                                                                                                                                                                        | Page |

|------|------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| C2   | 2016-08-18 | PACKAGES                                      | Package drawing updated<br>Pin 14, SPI_xSS: Note added.                                                                                                                                                                                                                                                                             | 5, 6 |

|      |            | ABSOLUTE MAXIMUM RATINGS                      | Items G006, G007: ESD ratings supplemented                                                                                                                                                                                                                                                                                          | 8    |

|      |            | ELECTRICAL<br>CHARACTERISTICS                 | Items 103, 305, 403, 404, 606, 808, 809, 810: added as new items<br>Item 104: max value, item 110, 111: typ. value, item 202: max value<br>Item 402: max value supplemented<br>Item 710: typ. value, new item 711 added<br>Item 901, 902: conditions corrected<br>Group A introduced for pins C0, C1, C3, C4 (removed from Group 7) | 9ff  |

|      |            | OPERATING REQUIRE-<br>MENTS: SPI Interface    | Item I006: supplemented specification<br>Items I009, I010: max. value                                                                                                                                                                                                                                                               | 12   |

|      |            | OPERATING REQUIRE-<br>MENTS: 1-Wire Interface | Items I102, I103: conditions and values supplemented                                                                                                                                                                                                                                                                                | 13   |

|      |            | DESIGN REVIEW: Function Notes                 | New entries for chip releases D1 to D3<br>Chip release D4 supplemented                                                                                                                                                                                                                                                              | 14   |

|      |            | ATTACHMENTS                                   | Attachment PC and SC updated                                                                                                                                                                                                                                                                                                        | 17ff |

iC-Haus expressly reserves the right to change its products and/or specifications. An info letter gives details as to any amendments and additions made to the relevant current specifications on our internet website www.ichaus.com/infoletter; this letter is generated automatically and shall be sent to registered users by email.

Copying - even as an excerpt - is only permitted with iC-Haus' approval in writing and precise reference to source.

iC-Haus does not warrant the accuracy, completeness or timeliness of the specification and does not assume liability for any errors or omissions in these materials.

The data specified is intended solely for the purpose of product description. No representations or warranties, either express or implied, of merchantability, fitness for a particular purpose or of any other nature are made hereunder with respect to information/specification or the products to which information refers and no guarantee with respect to compliance to the intended use is given. In particular, this also applies to the stated possible applications or areas of applications of the product.

ic-Haus products are not designed for and must not be used in connection with any applications where the failure of such products would reasonably be expected to result in significant personal injury or death (Safety-Critical Applications) without iC-Haus' specific written consent. Safety-Critical Applications include, without limitation, life support devices and systems. iC-Haus products are not designed nor intended for use in military or aerospace applications or environments or in automotive applications unless specifically designated for such use by iC-Haus.

iC-Haus conveys no patent, copyright, mask work right or other trade mark right to this product. iC-Haus assumes no liability for any patent and/or other trade mark rights of a third party resulting from processing or handling of the product and/or any other use of the product.

\* Release Date format: YYYY-MM-DD

Rev C2, Page 16/67

#### **ORDERING INFORMATION**

| Туре                | Package                                                         | Options                                                                                                  | Order Designation                                                                                |

|---------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|

| iC-TW8              | 48-pin QFN, 7 mm x 7 mm,<br>thickness 0.9 mm,<br>RoHS compliant |                                                                                                          | iC-TW8 QFN48-7x7                                                                                 |

| Evaluation Board    | PCB, 120 mm x 100 mm                                            |                                                                                                          | iC-TW8 EVAL TW8_1D                                                                               |

| PC-USB Adapter      |                                                                 | Only required if the evaluation board needs to be operated by the GUI.                                   | iC-MB3 iCSY MB3U-I2C                                                                             |

| iC-TW8 GUI          |                                                                 | Evalutation software for<br>Windows PC (entry of IC<br>parameters, file storage, and<br>transfer to DUT) | For download link refer to<br>www.ichaus.com/tw8                                                 |

| Encoder Design Tool |                                                                 | Excel-based rotary encoder design tool for parameter definition.                                         | Check www.ichaus.com/tw8<br>for download link or contact<br>iC-Haus applications<br>engineering. |

Please send your purchase orders to our order handling team:

#### Fax: +49 (0) 61 35 - 92 92 - 692 E-Mail: dispo@ichaus.com

For technical support, information about prices and terms of delivery please contact:

iC-Haus GmbH Am Kuemmerling 18 D-55294 Bodenheim GERMANY Tel.: +49 (0) 61 35 - 92 92 - 0 Fax: +49 (0) 61 35 - 92 92 - 192 Web: http://www.ichaus.com E-Mail: sales@ichaus.com

Appointed local distributors: http://www.ichaus.com/sales\_partners

# **iC-TW8** 16-BIT SIN/COS INTERPOLATOR **Pin Configuration Mode**

## **Table of Contents**

| About This Document                               | 2  |

|---------------------------------------------------|----|

| Functional Overview                               | 2  |

| Electrical Connections                            | 3  |

| Connecting the Incremental Sensor                 |    |

| Connecting an Index Sensor (If Used)              | 5  |

| Connecting the EEPROM                             |    |

| Power-on-Reset                                    | 6  |

| Providing a Clock                                 | 6  |

| Connecting the ABZ Outputs                        | 7  |

| Power-Up Sequence                                 | 7  |

| Pin Configuration                                 | 8  |

| Setting the Interpolation Factor                  | 9  |

| Setting the Auto-Adaption Mode                    |    |

| Setting the Filter Mode and Hysteresis            |    |

| Setting the Maximum AB Frequency and Lag Recovery | 11 |

| Serial Interfaces                                 | 11 |

| Auto Calibration                                  | 12 |

| iC-TW8 Rotary Encoder Design Tool                 | 12 |

| Pin Configuration Reference                       | 14 |

| Revision History                                  | 15 |

# **iC-TW8** 16-BIT SIN/COS INTERPOLATOR **Pin Configuration Mode**

Aug 3, 2016 Page PC2/15

#### About This Document

This document describes the pin configuration mode of the iC-TW8 Interpolator. Pin-configuration mode provides simple, static configuration of the device without any programming or complicated calibration.

Pin configuration allows selection of only the most commonly used features of the device. Access to all features of the iC-TW8 is available in serial configuration mode, described in a separate document. Design tools for both rotary and linear encoders using the iC-TW8 are available. These tools are in the form of Excel spreadsheets that allow entering application parameters in engineering units and then provide performance limits and graphs, configuration resistor values, and jumper settings for use with the iC-TW8 TW8\_1D demonstration board. This greatly simplifies and speeds up the design process of encoders using the iC-TW8.

#### **Functional Overview**

The iC-TW8 is a general-purpose 16-bit Sin/Cos interpolator with sophisticated auto-calibration functions. It accepts 20mV to 1.4V peak-to-peak differential analog input signals from magnetic or optical sensors and calculates (interpolates) the angular position. Output is industry-standard incremental AB quadrature at programmable resolution. Simple pin configuration and one-step automatic calibration requires no complicated signal analysis or calibration procedure during product design or production.

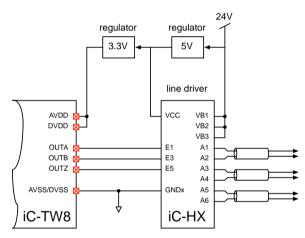

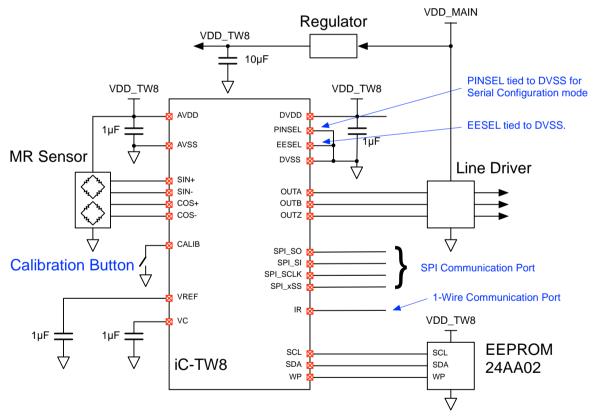

In addition to the chosen sensor, the iC-TW8 requires an external EEPROM to store its configuration and calibration data. An external crystal can be used instead of the internal oscillator of the iC-TW8 for superior frequency stability. A differential line driver can be connected directly to the iC-TW8 quadrature outputs to make a complete encoder.

Figure 1: iC-TW8 Functional Overview

#### **Electrical Connections**

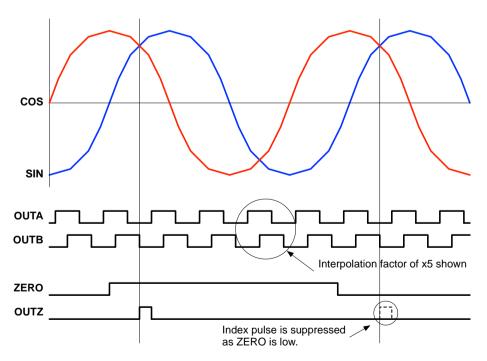

The basic electrical connections for an encoder using the iC-TW8 are shown in Figure 2. Other than the analog sensor, only an EEPROM for parameter storage, eight configuration resistors, and a few bypass capacitors are required for operation. PINSEL (pin 22) must be connected to DVDD to select pin configuration mode. A voltage regulator to supply clean power to the device and a line driver are recommended. An crystal or oscillator (clock driver) is also recommended.

The iC-TW8 requires a high quality ground and clean power supplies. Analog ground (AVSS = pin 46) and digital ground (DVSS = pin 15) must both be connected on the PCB to a solid ground plane.

Analog power (AVDD = pin 38) and digital power (DVDD = pin 21) inputs must be connected to a low impedance 5V or 3.3V power source, preferably an on-board voltage regulator. In addition, AVDD and DVDD should each have a dedicated  $1\mu$ F decoupling capacitor placed as close to the power pins on the device as possible.

If the iC-TW8 is used with a line driver (such as the iC-HD7 or iC-HX) or a high frequency FPGA, it is especially important to isolate the iC-TW8 power inputs (AVDD and DVDD) against external noise. In such applications, a dual voltage regulator such as the iC-DC is highly recommended. Note that both AVDD and DVDD must be the same voltage level (5V or 3.3V).

Figure 2: iC-TW8 Electrical Connections (Pin Configuration Mode)