NAND Flash Drive

--- THNIDxxxxBx Series ---

### <u>Outline</u>

The THNIDxxxxBx NAND Flash Drive series from Toshiba features an IDE interface, a flash disk controller chip, and NAND-type flash memory devices. There are two form factors, 2.5 inch-type and 3.5 inch-type, available in the series. The THNIDxxxxBx is available in 16 MB, 32 MB, 64 MB, 128 MB, 192 MB, 256 MB, 320 MB, 384 MB, 512 MB, 640 MB, 1024 MB, 1536 MB and 2048 MB capacities in each type. The drives operate with a 5-volts power supply and support Mode 4 PIO data transfer.

The NAND Flash Drive is geared specifically to the industrial market for use in ATM, factory automation machine, POS terminal, measuring product, ticket-vending machine, parking system and other industrial products that require high tolerance to environmental condition.

#### **Features**

- Capacity

- $16\mathrm{MB}$  up to  $2\mathrm{GB}$

- Form factor

- 2.5 inch-type, 3.5 inch-type, (HDD compatible)

- IDE interface Mode4 PIO

- ATA command set compatible

- Power supply

- $V_{CC} = 5.0 \text{ V} \pm 10\%$

- Operating temperature

- -40°C~85°C (Industrial grade : THNIDxxxxBxI)

- 0°C~70°C (Commercial grade : THNIDxxxxBx)

- Performance

- Burst data transfer rate (Drive-Host) Sustained write speed Sustained read speed

16.6 MB/sec. (max) 3.2 MB/sec. (max) 6.5 MB/sec. (max)

Shock Vibration 9800 m/s<sup>2</sup> (max) [Non-operating] 147 m/s<sup>2</sup> peak (25~2000 Hz) [Operating]

000707EBA1

• TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property.

In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

• The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

• The products described in this document are subject to the foreign exchange and foreign trade laws.

The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

• The information contained herein is subject to change without notice.

## Product Models

## 2.5 inch-type

| Unformatted | Cylinder | Head | Sector | Model No.       |

|-------------|----------|------|--------|-----------------|

| 16 MB       | 248      | 4    | 32     | THNID016MBA/BAI |

| 32 MB       | 496      | 4    | 32     | THNID032MBA/BAI |

| 64 MB       | 978      | 4    | 32     | THNID064MBA/BAI |

| 128 MB      | 978      | 8    | 32     | THNID128MBA/BAI |

| 192 MB      | 733      | 16   | 32     | THNID192MBA/BAI |

| 256 MB      | 978      | 16   | 32     | THNID256MBA/BAI |

| 320 MB      | 814      | 16   | 48     | THNID320MBA/BAI |

| 384 MB      | 977      | 16   | 48     | THNID384MBA/BAI |

| 512 MB      | 993      | 16   | 63     | THNID512MBA/BAI |

| 640 MB      | 1241     | 16   | 63     | THNID640MBA/BAI |

| 1024 MB     | 1985     | 16   | 63     | THNID1G02BA/BAI |

| 1536 MB     | 2966     | 16   | 63     | THNID1G53BA/BAI |

| 2048 MB     | 3954     | 16   | 63     | THNID2G04BA/BAI |

## 3.5 inch-type

| Unformatted | Cylinder | Head | Sector | Model No.       |

|-------------|----------|------|--------|-----------------|

| 16 MB       | 248      | 4    | 32     | THNID016MBB/BBI |

| 32 MB       | 496      | 4    | 32     | THNID032MBB/BBI |

| 64 MB       | 978      | 4    | 32     | THNID064MBB/BBI |

| 128 MB      | 978      | 8    | 32     | THNID128MBB/BBI |

| 192 MB      | 733      | 16   | 32     | THNID192MBB/BBI |

| 256 MB      | 978      | 16   | 32     | THNID256MBB/BBI |

| 320 MB      | 814      | 16   | 48     | THNID320MBB/BBI |

| 384 MB      | 977      | 16   | 48     | THNID384MBB/BBI |

| 512 MB      | 993      | 16   | 63     | THNID512MBB/BBI |

| 640 MB      | 1241     | 16   | 63     | THNID640MBB/BBI |

| 1024 MB     | 1985     | 16   | 63     | THNID1G02BB/BBI |

| 1536 MB     | 2966     | 16   | 63     | THNID1G53BB/BBI |

| 2048 MB     | 3954     | 16   | 63     | THNID2G04BB/BBI |

## Product Specification

| • | Storage Capacities:          |                                                     |

|---|------------------------------|-----------------------------------------------------|

|   |                              | 2, 640, 1024, 1536, 2048 Mbytes (unformatted)       |

| • | Performance:                 |                                                     |

|   | To/from host                 | 16.6 Mbytes/sec. (max theoretical)                  |

|   | Sustained write              | 3.2 Mbyte/sec. (max) [ATA PIO mode 4] (≥64 MB)      |

|   |                              | 1.5 Mbyte/sec. (max) [ATA PIO mode 4] (16 MB~32 MB) |

|   | Sustained read               | 6.5 Mbyte/sec. (max) [ATA PIO mode 4]               |

| • | Operating Voltage:           |                                                     |

|   | 5V +/- 10%                   |                                                     |

| ٠ | Power Consumption:           |                                                     |

|   | Read mode                    | 51 mA (typ)                                         |

|   | Write mode                   | 43 mA (typ)                                         |

|   | Idle mode                    | 16 mA (typ)                                         |

|   | Sleep mode                   | 1 mA (typ) (≤64 MB)                                 |

|   |                              | 3 mA (typ) (2 GB)                                   |

| ٠ | Environmental Specification: |                                                     |

|   | Operating temperature        | –40°C to 85°C (Industrial grade : THNIDxxxxBxI)     |

|   |                              | 0°C to 70°C (Commercial grade : THNIDxxxxBx)        |

|   | Storage temperature          | –40°C to 85°C (Industrial grade : THNIDxxxxBxI)     |

|   |                              | –20°C to 85°C (Commercial grade : THNIDxxxxBx)      |

|   | Humidity                     | 95% (max) [No condensation]                         |

|   | Shock                        | 9800 m/s <sup>2</sup> (max) (3 axis) [No-operating] |

|   | Vibration                    | 147 m/s <sup>2</sup> peak (25Hz~2000Hz) [Operating] |

| • | Reliability:                 |                                                     |

|   | Error rate                   | $<1$ bit/ $10^{15}$ bit read                        |

|   | ECC                          | 1 bit error connection                              |

|   |                              |                                                     |

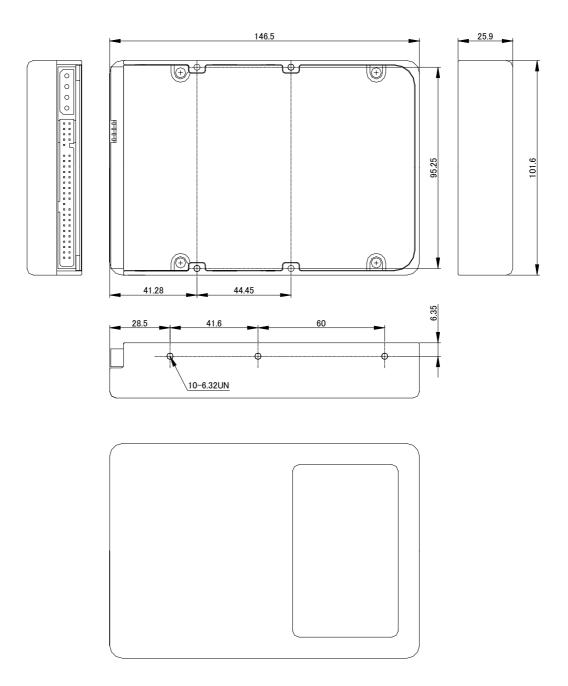

## **Mechanical Specification**

#### Absolute Maximum Ratings

| Symbol           | Parameter             | Value                         | Unit |

|------------------|-----------------------|-------------------------------|------|

| V <sub>CC</sub>  | Power Supply Voltage  | -0.6 to 6.0                   | V    |

| V <sub>IN</sub>  | Input Voltage         | –0.3 to V <sub>CC</sub> + 0.3 | V    |

| т                | Storogo Tomporaturo   | -40 to 85 (Industrial grade)  | °C   |

| T <sub>STG</sub> | Storage Temperature   | 0 to 70 (Commercial grade)    |      |

| Τ                | Operating Temperature | -40 to 85 (Industrial grade)  | °C   |

| T <sub>OPR</sub> | Operating Temperature | -20 to 85 (Commercial grade)  |      |

#### Recommended DC Operating Conditions

| Symbol          | Parameter                | Min | Тур | Max | Unit |

|-----------------|--------------------------|-----|-----|-----|------|

| V <sub>CC</sub> | Power Supply Voltage     | 4.5 | 5.0 | 5.5 | V    |

| VIH             | High Level Input Voltage | 2.0 | _   |     | V    |

| V <sub>IL</sub> | Low Level Input Voltage  |     |     | 0.8 | V    |

## <u>DC Characteristics</u> (Ta = $-40^{\circ}$ C to 85°C, V<sub>CC</sub> = 5.0 V ± 10%)

| Symbol           | Parameter                          | Min                  | Тур | Max | Unit |

|------------------|------------------------------------|----------------------|-----|-----|------|

| I <sub>CCR</sub> | Operating Current (Read)           |                      | 51  |     | mA   |

| ICCW             | Operating Current (Write)          |                      | 43  |     | mA   |

| 1                | Sleep Mode Current ( $\leq$ 64 MB) |                      | 1   |     | mA   |

| Iccs             | Sleep Mode Current (2 GB)          |                      | 3   |     | mA   |

| V <sub>OH</sub>  | High Level Output Voltage          | V <sub>CC</sub> –0.8 | —   | —   | V    |

| V <sub>OL</sub>  | Low Level Output Voltage           |                      |     | 0.4 | V    |

## Package Dimensions

<u>3.5 inch</u>

3.5 inch Flash Drive Dimensions

## <u>2.5 inch</u>

2.5 Flash Drive Dimensions

## Jumper Settings

### <u>3.5 inch</u>

| 0000  | 00         |

|-------|------------|

| 0000  | 00         |

|       | 1          |

|       |            |

|       | 00         |

|       | 0 0<br>0 0 |

| ·     | 1          |

| 0 000 | 0 0        |

|       | 00         |

|       | 1          |

#### 2.5 inch

|   |   |   | 1 |     |

|---|---|---|---|-----|

| 0 | 0 | 0 | 0 |     |

| 0 | 0 | 0 | 0 | 이이  |

|   |   |   |   |     |

|   |   |   | 1 |     |

| 0 | 0 | 0 | 0 |     |

| 0 | 0 | 0 | 0 | 00  |

|   |   |   |   |     |

|   |   |   | 1 |     |

| 0 | 0 | 0 | 0 | 0 0 |

| 0 | 0 | 0 | 0 | 00  |

|   |   |   |   |     |

Master

Master

Slave

Cable Select

Slave

Cable Select

## Pin Assignments and Pin Type

| Pin Number | Signal Name | Pin Type | Pin Number | Signal Name | Pin Type |

|------------|-------------|----------|------------|-------------|----------|

| 1          | RESET       | I        | 2          | GND         | _        |

| 3          | DD7         | I/O      | 4          | DD8         | I/O      |

| 5          | DD6         | I/O      | 6          | DD9         | I/O      |

| 7          | DD5         | I/O      | 8          | DD10        | I/O      |

| 9          | DD4         | I/O      | 10         | DD11        | I/O      |

| 11         | DD3         | I/O      | 12         | DD12        | I/O      |

| 13         | DD2         | I/O      | 14         | DD13        | I/O      |

| 15         | DD1         | I/O      | 16         | DD14        | I/O      |

| 17         | DD0         | I/O      | 18         | DD15        | I/O      |

| 19         | GND         | —        | 20         | KEY(NC)     | —        |

| 21         | DMARQ(NC)   | —        | 22         | GND         | —        |

| 23         | DIOW        | I        | 24         | GND         | —        |

| 25         | DIOR        | I        | 26         | GND         | —        |

| 27         | Reserved    | 0        | 28         | CSEL        | I        |

| 29         | DMACK (NC)  | —        | 30         | GND         | —        |

| 31         | INTRQ       | 0        | 32         | Reserved    | —        |

| 33         | DA1         | I        | 34         | PDIAG       | I/O      |

| 35         | DA0         | I        | 36         | DA2         | I        |

| 37         | CS0         | I        | 38         | CS1         | I        |

| 39         | DASP        | I/O      | 40         | GND         | _        |

| 41         | VCC         | —        | 42         | VCC         | _        |

| 43         | GND         | _        | 44         | —           | _        |

Note 1: Pins #41 to 44 are for the IDE 44-pin standard (2.5 inch-type).

Note 2: To avoid damage to the drive or its pins, be sure to connect the drive to the IDE connecter properly

Note 3: "I" is defined as a direction from the host to the drive.

"O" is defined as a direction from the drive to the host.

| Power supply                         |         | Jum  | per F | Pin |                 | 2 | 4 | 6    | 8 | 10 <sup>-</sup> | 12 14 | 4 16 | 6 18 | 3 20 | 22 | 24 | 26           | 28 3 | 30 | 32 | 34 | 36 | 38 4 |

|--------------------------------------|---------|------|-------|-----|-----------------|---|---|------|---|-----------------|-------|------|------|------|----|----|--------------|------|----|----|----|----|------|

| 0000                                 | , Ĺ     | 0 0  | 0     | 0   | 1               | 0 | 0 | 0    | 0 | 0               | 0 0   | 0    | 0    |      | 0  | 0  | 0            | 0    | 0  | 0  | 0  | 0  | 0    |

|                                      |         | 0 0  | 0     | 0   | 0               | 0 | 0 | 0    | 0 | 0               | 0 0   | 0    | 0    | 0    | 0  | 0  | 0            | 0    | 0  | 0  | 0  | 0  | 0    |

|                                      |         |      |       |     |                 |   |   |      |   |                 |       |      |      |      |    |    |              |      |    |    |    |    |      |

|                                      |         |      |       |     |                 | 1 | 3 | 5    | 7 | 9 ′             | 11 1  | 3 15 | 5 17 | ' 19 | 21 | 23 | 25 :         | 27 : | 29 | 31 | 33 | 35 | 37 : |

| 5 inch (44 pins)<br>43 41 39 37 35 3 | 33 31 2 | 29 2 | 7 25  | 23  | 21 <sup>-</sup> |   | - | -    |   | -               |       |      |      | -    |    | -  | 25 :<br>er P |      | 29 | 31 | 33 | 35 | 37 : |

| 5 inch (44 pins)<br>43 41 39 37 35 3 | 33 31 2 | 29 2 |       |     |                 |   | - | 15 1 |   | 1 9             | 7     |      | 3    | -    | Ju | -  | er P         |      | 29 | 31 | 33 | 35 | 37 : |

## Signal Description

| Signal Name                         | Dir. | Pin                           | Description                                                                                                                                                                                                                                                                                                                               |

|-------------------------------------|------|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET                               | I    | 1                             | This pin is shall be used by host to reset the device. Reset signal is from the host and it is active low.                                                                                                                                                                                                                                |

| DD[0:15]                            | I/O  | 3 to 18                       | These lines carry Data, Commands and Status information between the host and controller. DD[0] is the LSB and DD[15] is the MSB.                                                                                                                                                                                                          |

| DIOW                                | I    | 23                            | DIOW is the strobe signal asserted by the host to write the device register.                                                                                                                                                                                                                                                              |

| DIOR                                | I    | 25                            | DIOR is the strobe signal asserted by the host to read the device register                                                                                                                                                                                                                                                                |

| INTRQ                               | 0    | 31                            | This signal is used by the selected device to interrupt the host<br>system when interrupt pending is set. When the nIEN bit is cleared to<br>zero and the device is selected, INTRQ shall be enabled through a<br>tri-state buffer. When the nIEN bit is set to one or the device is not<br>selected, the INTRQ signal shall be released. |

| DA[0: 2]                            | I    | 33, 35, 36                    | DA[2:0] are used to select one of eight registers                                                                                                                                                                                                                                                                                         |

| $\overline{CS}0$ , $\overline{CS}1$ | I    | 37, 38                        | $\overline{CS0}$ is used to select the Command Block registers while $\overline{CS1}$ is used to select the Control Block Register.                                                                                                                                                                                                       |

| CSEL                                | I    | 28                            | CSEL is used to select Master/Slave mode, Low for Master, High for Slave mode.                                                                                                                                                                                                                                                            |

| PDIAG                               | I/O  | 34                            | This bi-directional open drain signal is asserted by the slave after an Execute Diagnostic command to indicate to the master it has passed its diagnostics.                                                                                                                                                                               |

| DASP                                | I/O  | 39                            | This open drain output is asserted low any time the drive is active. In<br>a Master/Slave configuration, this signal is used for the slave to<br>inform the master that a slave drive is present.                                                                                                                                         |

| GND                                 |      | 2, 19, 22, 24, 26, 30, 40, 43 | Ground                                                                                                                                                                                                                                                                                                                                    |

| VCC                                 |      | 41, 42                        | Power                                                                                                                                                                                                                                                                                                                                     |

## I/O Register Specifications

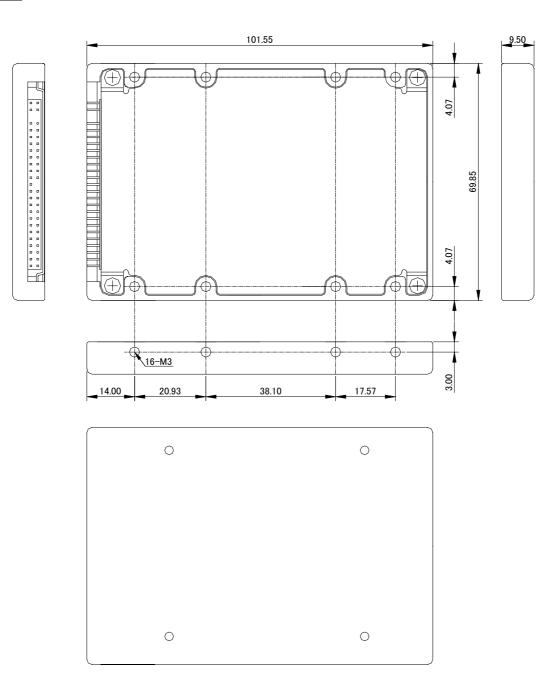

The data is transferred between the host system and the device via I/O registers in the device. Reads and writes to the registers are performed using the following logics.

#### Read I/O Register Function

| Mode                                | CS1 | $\overline{CS}0$ | DA0~DA2 | DIOR | DIOW | DD8~DD15 | DD0~DD7    |

|-------------------------------------|-----|------------------|---------|------|------|----------|------------|

| Invalid mode                        | L   | L                | ×       | ×    | ×    | High-Z   | High-Z     |

| Standby mode                        | Н   | Н                | ×       | ×    | ×    | High-Z   | High-Z     |

| Data register access                | Н   | L                | 0       | L    | Н    | odd byte | even byte  |

| Alternate status access             | L   | Н                | 6H      | L    | Н    | High-Z   | status out |

| Other command block register access | Н   | L                | 1~7H    | L    | Н    | High-Z   | data       |

Note:  $\times:$  L or H

#### Write I/O Register Function

| Mode                                | CS1 | $\overline{CS}0$ | DA0~DA2 | DIOR | DIOW | DD8~DD15   | DD0~DD7    |

|-------------------------------------|-----|------------------|---------|------|------|------------|------------|

| Invalid mode                        | L   | L                | ×       | ×    | ×    | don't care | don't care |

| Standby mode                        | Н   | Н                | ×       | ×    | ×    | don't care | don't care |

| Data register access                | Н   | L                | 0       | Н    | L    | odd byte   | even byte  |

| Control register access             | L   | Н                | 6H      | Н    | L    | don't care | control in |

| Other command block register access | Н   | L                | 1~7H    | Н    | L    | don't care | data       |

Note: x: L or H

#### I/O Register Address

This table summarizes the register selected by DA0~DA2.

| CS1 | $\overline{CS}0$ | DA2 | DA1 | DA0 | $\overline{DIOR} = L$  | $\overline{DIOW} = L$   |

|-----|------------------|-----|-----|-----|------------------------|-------------------------|

| 1   | 0                | 0   | 0   | 0   | Data register          | Data register           |

| 1   | 0                | 0   | 0   | 1   | Error register         | Feature register        |

| 1   | 0                | 0   | 1   | 0   | Sector count register  | Sector count register   |

| 1   | 0                | 0   | 1   | 1   | Sector number register | Sector number register  |

| 1   | 0                | 1   | 0   | 0   | Cylinder low register  | Cylinder low register   |

| 1   | 0                | 1   | 0   | 1   | Cylinder high register | Cylinder high register  |

| 1   | 0                | 1   | 1   | 0   | Device/Head register   | Drive head register     |

| 1   | 0                | 1   | 1   | 1   | Status register        | Command register        |

| 0   | 1                | 1   | 1   | 0   | Alt. status register   | Device control register |

| 0   | 1                | 1   | 1   | 1   | Drive address register | Reserved                |

#### Register Access Timing Example

| Rit 1                      | 5 Rit 14  | Rit 13 F  | Bit 12 Bit 11 | Bit 10              | Rit 9                                                                                                                                  | Bit 8   | Bit 7             | Bit 6   | Bit 5    | Bit 4     | Bit 3   | Bit 2    | Bit 1                       | Bit 0                        |

|----------------------------|-----------|-----------|---------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------|-------------------|---------|----------|-----------|---------|----------|-----------------------------|------------------------------|

| DR                         |           |           |               | Bit To              | Bit 0                                                                                                                                  |         | -DD15             | Bit 0   | Bito     | DR 4      | Bit 0   | DRZ      | Dit 1                       | BRO                          |

|                            |           |           |               |                     |                                                                                                                                        |         | DD15              |         |          |           |         |          |                             |                              |

| acc                        |           | acces     | -             | is regi             | ster is                                                                                                                                | valid v |                   |         |          |           |         |          | the drive is<br>nd Alternat |                              |

| Bit 7                      |           | Bit 6     | Bit 5         |                     | Bit 4                                                                                                                                  |         | Bit 3             |         | Bit 2    |           | Bit 1   |          | Bit 0                       |                              |

| BBK                        |           | UNC       | "0"           |                     | IDNF                                                                                                                                   |         | "0"               |         | ABRT     |           | "0"     |          | AMNF                        | :                            |

| Bit Name                   |           |           |               |                     |                                                                                                                                        |         |                   |         | Fund     | ction     |         |          |                             |                              |

| 7 BBK (Bad Block detected) |           |           |               |                     | This bit is set when a Bad Block is detected.                                                                                          |         |                   |         |          |           |         |          |                             |                              |

| 6 UNC (Data ECC error)     |           |           |               |                     | This b<br>readin                                                                                                                       |         | et whei<br>drive. | n an u  | ncorre   | ctable    | error   | has oc   | curred                      | when                         |

| 4 IDNF (ID Not Found)      |           |           |               |                     | it is se                                                                                                                               | et whei | n the 1           | request | ed see   | ctor is i | in erro | or or ca | innot                       |                              |

| 2                          | ABRT (A   | ABoRTed   | command)      |                     | This bit is set if the command has been aborted because of the<br>drive status condition. (Not ready, Write fault, Invalid<br>command) |         |                   |         |          |           |         | of the   |                             |                              |

| 0                          | AMNF (    | Address I | /lark Not Fou | und)                | This bit is set in case of a general error.                                                                                            |         |                   |         |          |           |         |          |                             |                              |

| Featu                      | are regis | ster:     |               | register<br>he host |                                                                                                                                        |         |                   | ovides  | s inforr | natior    | ı regar | ding fo  | eature                      | s of the driv                |

| Bit 7                      |           | Bit 6     | Bit 5         |                     | Bit 4                                                                                                                                  |         | Bit 3             |         | Bit 2    |           | Bit 1   |          | Bit 0                       |                              |

|                            |           |           |               |                     |                                                                                                                                        | Featu   | re byte           |         |          |           |         |          |                             |                              |

| Secto                      | r count   | register  | read          | -                   | e opera                                                                                                                                | tion b  | etweer            | n the h | ost an   |           | -       |          |                             | cransferred<br>of this regis |

|                            |           | Bit 6     | Bit 5         |                     | Bit 4                                                                                                                                  |         | Bit 3             |         | Bit 2    |           | Bit 1   |          | Bit 0                       |                              |

| Sect                    | or num   | ber register:  | This regist<br>transfer co |                                                                                                                                                                                                                                                   | s the starting s                   | sector number   | r, which is sta | arted by following |  |  |  |

|-------------------------|----------|----------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------|-----------------|--------------------|--|--|--|

| Bit                     | 7        | Bit 6          | Bit 5                      | Bit 4                                                                                                                                                                                                                                             | Bit 3                              | Bit 2           | Bit 1           | Bit 0              |  |  |  |

|                         |          |                |                            | Sec                                                                                                                                                                                                                                               | tor number byte                    |                 |                 |                    |  |  |  |

| Cylin                   | nder lo  | w register:    | -                          |                                                                                                                                                                                                                                                   | s the low 8-bits<br>ansfer comma   |                 | ng cylinder a   | ddress, which is s |  |  |  |

| Bit                     | 7        | Bit 6          | Bit 5                      | Bit 4                                                                                                                                                                                                                                             | Bit 3                              | Bit 2           | Bit 1           | Bit 0              |  |  |  |

|                         |          |                |                            | Су                                                                                                                                                                                                                                                | linder low byte                    |                 |                 |                    |  |  |  |

| Cylinder high register: |          |                |                            |                                                                                                                                                                                                                                                   | s the high 8-bi<br>sector transfer |                 | ing cylinder    | address, which is  |  |  |  |

| Bit                     | 7        | Bit 6          | Bit 5                      | Bit 4                                                                                                                                                                                                                                             | Bit 3                              | Bit 2           | Bit 1           | Bit 0              |  |  |  |

|                         |          |                |                            | Cyl                                                                                                                                                                                                                                               | inder high byte                    |                 |                 |                    |  |  |  |

| Devi                    | ice/head | l register:    | This regist<br>following o |                                                                                                                                                                                                                                                   | for selecting th                   | ne drive numb   | er and Head     | number for the     |  |  |  |

| Bit                     | 7        | Bit 6          | Bit 5                      | Bit 4                                                                                                                                                                                                                                             | Bit 3                              | Bit 2           | Bit 1           | Bit 0              |  |  |  |

| Obs                     | solete   | LBA            | Obsolete                   | DRV                                                                                                                                                                                                                                               | Head numb                          | er              |                 |                    |  |  |  |

| Bit                     | i        | Name           |                            |                                                                                                                                                                                                                                                   |                                    | Function        |                 |                    |  |  |  |

| 7                       | Obsol    | ete            |                            | This bit is                                                                                                                                                                                                                                       | set to "1".                        |                 |                 |                    |  |  |  |

| 6                       | LBA      |                |                            | LBA is a flag to select either Cylinder/Head/Sector (CHS) or Logical Block<br>Address (LBA) mode. When LBA = 0, CHS mode is selected. When<br>LBA = 1, LBA mode is selected. In LBA mode, the Logical Block Address is<br>interpreted as follows: |                                    |                 |                 |                    |  |  |  |

|                         |          |                |                            | LBA07-                                                                                                                                                                                                                                            | LBA00: Sector N                    | umber Register  | D7-D0.          |                    |  |  |  |

|                         |          |                |                            | LBA15-LBA08: Cylinder Low Register D7-D0.                                                                                                                                                                                                         |                                    |                 |                 |                    |  |  |  |

|                         |          |                |                            | LBA23-LBA16: Cylinder High Register D7-D0.                                                                                                                                                                                                        |                                    |                 |                 |                    |  |  |  |

| _                       | Obsol    | oto            |                            | LBA27-LBA24: Drive/Head Register bits HS3-HS0.                                                                                                                                                                                                    |                                    |                 |                 |                    |  |  |  |

| 5                       | 00500    |                |                            | This bit is set to "1".<br>This bit is used for selecting the Master (Drive 0) and Slave (Drive 1) in                                                                                                                                             |                                    |                 |                 |                    |  |  |  |

| 5<br>4                  | DEV (    | Device select) |                            |                                                                                                                                                                                                                                                   | ave organization.                  | Cloared to zero | colocte the M   | actor (Drive 0)    |  |  |  |

9. Status register:

TOSHIBA

This register is read-only. It indicates the status of the command execution. The contents of this register are updated to reflect the current state of the device and the progress of any command being executed by the device. Reading this register when an interrupt is pending causes the pending interrupt to be cleared. The host should not read the Status register when an interrupt is expected as this may clear the pending interrupt before the INTRQ can be recognized by the host.

| Bit 7 | Bit 6              | Bit 5       | Bit 4                                                                                                                                                                                | Bit 3                                                                                                                                 | Bit 2    | Bit 1    | Bit 0 |  |  |  |  |

|-------|--------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|----------|----------|-------|--|--|--|--|

| BSY   | Ø DRDY             | DWF         | DSC                                                                                                                                                                                  | DSC DRQ                                                                                                                               |          | Obsolete | ERR   |  |  |  |  |

| Bit   | Nam                | е           |                                                                                                                                                                                      |                                                                                                                                       | Function |          |       |  |  |  |  |

| 7     | BSY (BuSY)         |             |                                                                                                                                                                                      | This bit is set to "1" when an internal operation is executing. When this bit is set to "1", other bits in this register are invalid. |          |          |       |  |  |  |  |

| 6     | DRDY (Drive ReaD   | Y)          | This bit is set to "1" when an internal operation has been ended an<br>drive is capable of being accessed from the host.                                                             |                                                                                                                                       |          |          |       |  |  |  |  |

| 5     | DWF (Drive Write F | ault)       | This bit is                                                                                                                                                                          | This bit is set to "1" if this drive indicates a write fault status.                                                                  |          |          |       |  |  |  |  |

| 4     | DSC (Drive Seek Co | omplete)    | This bit is                                                                                                                                                                          | This bit is set to "1" when the drive seek is complete.                                                                               |          |          |       |  |  |  |  |

| 3     | DRQ (Data ReQues   | t)          |                                                                                                                                                                                      | This bit is set to "1" when the device is ready to transfer a word of data between the host and Data register.                        |          |          |       |  |  |  |  |

| 2     | CORR (CORRected    | l data)     |                                                                                                                                                                                      | This bit is set to "1" when a correctable data error has occurred and the data has been corrected.                                    |          |          |       |  |  |  |  |

| 1     | Obsolete           |             | This bit is                                                                                                                                                                          | This bit is always set to "0".                                                                                                        |          |          |       |  |  |  |  |

| 0     | ERR (ERRor)        | type of err | This bit is set to "1" when the previous command has ended in some<br>type of error. The error information is set in the Error register. This bit is<br>cleared by the next command. |                                                                                                                                       |          |          |       |  |  |  |  |

10. Alternate status register: This register is the same as the Status register in the command block. The bit assignment is same as the prior description of the Status register. But this register is different from the Status register in that -IREQ is not negated when data is read.

11. Device control register:

This register is write-only. This register allows a host to software reset attached devices and to enable or disable the assertion of the INTRQ signal by a selected device.

| Bit 7 | Bit 6             | Bit 5    | Bit 4                                                                                                                                     | Bit 3         | Bit 2 | Bit 1 | Bit 0 |  |  |  |

|-------|-------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------|---------------|-------|-------|-------|--|--|--|

|       |                   | Reserved |                                                                                                                                           |               | SRST  | nIEN  | 0     |  |  |  |

| Bit   | Name Function     |          |                                                                                                                                           |               |       |       |       |  |  |  |

| 7~3   | Х                 |          | Reserve                                                                                                                                   | Reserved bits |       |       |       |  |  |  |

| 2     | SRST (Software    | ReSeT)   | This bit is set to "1" in order to have the drive perform Software Re operation. The drive remains in Reset until this bit is set to "0". |               |       |       |       |  |  |  |

| 1     | nIEN (Interrupt E |          | This bit is used to enable INTRQ. When this bit is set to"0", INTRQ is active. When this bit is set to "1", INTRQ is high impedance.      |               |       |       |       |  |  |  |

| 0     | 0                 |          | This bit is set to "0".                                                                                                                   |               |       |       |       |  |  |  |

12. Drive Address register: This register is read-only. It is used for confirming the drive status.

| Bit 7 | Bit 6             | Bit 5  | Bit 4                                                                          | Bit 3 | Bit 2 | Bit 1 | Bit 0 |  |  |  |

|-------|-------------------|--------|--------------------------------------------------------------------------------|-------|-------|-------|-------|--|--|--|

| ×     | nWTG              | nHS3   | nHS2                                                                           | nHS1  | nHS0  | nDS1  | nDS0  |  |  |  |

| Bit   | Na                | ame    | Function                                                                       |       |       |       |       |  |  |  |

| 7     | Х                 |        | This bit is unknown. It remains in tri-state, when host read.                  |       |       |       |       |  |  |  |

| 6     | nWTG (WriTing C   | Sate)  | "0"                                                                            | "O"   |       |       |       |  |  |  |

| 5~2   | nHS3-0 (Head Se   |        | These 4 bits are the negative value of Head Number in the Drive/Head register. |       |       |       |       |  |  |  |

| 1     | nDS1 (Idrive Sele | ect 1) | ct 1) This bit is "0", when drive 1 is selected.                               |       |       |       |       |  |  |  |

| 0     | nDS0 (Idrive Sele | ect 0) | This bit is "0", when drive 0 is selected.                                     |       |       |       |       |  |  |  |

#### 13. Command register:

This register is write-only. Each command to be executed is written to this register, after setting the parameters as follows.

|                              |              | Used Parameter |    |    |    |    |    |     |  |  |

|------------------------------|--------------|----------------|----|----|----|----|----|-----|--|--|

| Command                      | Command code | FR             | SC | SN | CY | DR | HD | LBA |  |  |

| Check power mode             | E5H or 98H   | Ν              | Ν  | Ν  | Ν  | Y  | Ν  | Ν   |  |  |

| Execute drive diagnostic     | 90H          | Ν              | Ν  | Ν  | Ν  | Y  | Ν  | Ν   |  |  |

| CFA erase sector             | СОН          | Ν              | Y  | Y  | Y  | Y  | Y  | Y   |  |  |

| Format track                 | 50H          | Ν              | Y  | Ν  | Y  | Y  | Y  | Y   |  |  |

| Identify Drive               | ECH          | Ν              | Ν  | Ν  | Ν  | Y  | Ν  | Ν   |  |  |

| Idle                         | E3H or 97H   | Ν              | Y  | Ν  | Ν  | Y  | Ν  | Ν   |  |  |

| Idle immediate               | E1H or 95H   | Ν              | Ν  | Ν  | Ν  | Y  | Ν  | Ν   |  |  |

| Initialize drive parameters  | 91H          | Ν              | Y  | Ν  | Ν  | Y  | Y  | Ν   |  |  |

| Read buffer                  | E4H          | Ν              | Ν  | Ν  | Ν  | Y  | Ν  | Ν   |  |  |

| Read multiple                | C4H          | Ν              | Y  | Y  | Y  | Y  | Y  | Y   |  |  |

| Read long sector             | 22H or 23H   | Ν              | Ν  | Y  | Y  | Y  | Y  | Y   |  |  |

| Read sector                  | 20H or 21H   | Ν              | Y  | Y  | Y  | Y  | Y  | Y   |  |  |

| Read verify sector           | 40H or 41H   | Ν              | Y  | Y  | Y  | Y  | Y  | Y   |  |  |

| Recalibrate                  | 1XH          | Ν              | Ν  | Ν  | Ν  | Y  | Ν  | Ν   |  |  |

| CFA request extended error   | 03H          | Ν              | Ν  | Ν  | Ν  | Y  | Ν  | Ν   |  |  |

| Seek                         | 7XH          | Ν              | Ν  | Y  | Y  | Y  | Y  | Y   |  |  |

| Set features                 | EFH          | Y              | Ν  | Ν  | Ν  | Y  | Ν  | Ν   |  |  |

| Set multiple mode            | C6H          | Ν              | Y  | Ν  | Ν  | Y  | Ν  | Ν   |  |  |

| Sleep                        | E6H or 99H   | Ν              | Ν  | Ν  | Ν  | Y  | Ν  | Ν   |  |  |

| Stand by                     | E2H or 96H   | Ν              | Ν  | Ν  | Ν  | Y  | Ν  | Ν   |  |  |

| Stand by immediate           | E0H or 94H   | Ν              | Ν  | Ν  | Ν  | Y  | Ν  | Ν   |  |  |

| CFA translate sector         | 87H          | Ν              | Ν  | Y  | Y  | Y  | Y  | Y   |  |  |

| CFA wear level               | F5H          | Ν              | Ν  | Ν  | Ν  | Y  | Ν  | Ν   |  |  |

| Write buffer                 | E8H          | Ν              | Ν  | Ν  | Ν  | Y  | Ν  | Ν   |  |  |

| Write long sector            | 32H or 33H   | Ν              | Ν  | Y  | Y  | Y  | Y  | Y   |  |  |

| Write multiple               | C5H          | Ν              | Y  | Y  | Y  | Y  | Y  | Y   |  |  |

| CFA write multiple w/o erase | CDH          | Ν              | Y  | Y  | Y  | Y  | Y  | Y   |  |  |

| Write sector                 | 30H or 31H   | Ν              | Y  | Y  | Y  | Y  | Y  | Y   |  |  |

| CFA write sector w/o erase   | 38H          | Ν              | Y  | Y  | Y  | Y  | Y  | Y   |  |  |

| Write verify                 | 3CH          | Ν              | Y  | Y  | Y  | Y  | Y  | Y   |  |  |

Note: FR: Feature register

SC: Sector Count register

SN: Sector Number register

CY: Cylinder Low/High register

DR: DRV bit of Drive Head register

HD: Head Number of Drive/Head register

LBA: Logical Block Address Mode Supported

Y: The register contains a valid parameter for this command

N: The register does not contain a valid parameter for this command

## ATA Command Specification

- 1. Check Power Mode (code: E5H or 98H): This command checks the power mode.

- 2. Execute Drive Diagnostic (code: 90H): This command performs the internal diagnostic tests implemented by the drive.

- 3. CFA Erase Sector (s) (code: C0H): This command is used to erase data sectors.

- 4. Format Track (code: 50H): This command writes the desired head and cylinder of the selected drive. But selected sector data is not exchanged. This drive expects one sector (512 bytes) of data from the host to follow the command with the same protocol as the Write Sector Command

- 5. Identify Drive (code: ECH): This command enables the host to receive parameter information from the drive.

| Vord address | Default value | Total bytes | Data field type information                                  |

|--------------|---------------|-------------|--------------------------------------------------------------|

| 0            | 040AH         | 2           | General configuration bit-significant information            |

| 1            | XXXX          | 2           | Default number of cylinders                                  |

| 2            | 0000H         | 2           | Reserved                                                     |

| 3            | 00XXH         | 2           | Default number of heads                                      |

| 4            | XXXX          | 2           | Number of unformatted bytes per track                        |

| 5            | XXXX          | 2           | Number of unformatted bytes per sector                       |

| 6            | XXXX          | 2           | Default number of sectors per track                          |

| 7 to 8       | XXXX          | 4           | Reserved                                                     |

| 9            | 0000H         | 2           | Reserved                                                     |

| 10 to 19     | XXXX          | 20          | Serial number in ASCII                                       |

| 20           | 0001H         | 2           | Buffer type(single ported)                                   |

| 21           | 0004H         | 2           | Buffer size in 512 byte increments                           |

| 22           | 0004H         | 2           | # of ECC bytes passed on Read/Write Long Commands            |

| 23 to 46     | XXXX          | 48          | Firmware revision in ASCII etc.                              |

| 47           | 0001H         | 2           | Maximum number of sectors on Read/Write Multiple command     |

| 48           | 0000H         | 2           | Double Word not supported                                    |

| 49           | 0200H         | 2           | Capabilities: DMA NOT Supported (bit8), LBA supported (bit9) |

| 50           | 0000H         | 2           | Reserved                                                     |

| 51           | 0400H         | 2           | PIO data transfer cycle timing mode 4                        |

| 52           | 0000H         | 2           | DMA data transfer cycle timing mode not Supported            |

| 53 to 58     | XXXX          | 12          | Reserved                                                     |

| 59           | 0101H         | 2           | Multiple sector setting is valid                             |

| 60 to 61     | XXXX          | 4           | Total number of sectors addressable in LBA Mode              |

| 62 to 255    | 0000H         | 388         | Reserved                                                     |

Identify Drive Information

6. Idle (code: E3H or 97H): This command causes the drive to set BSY, enter the Idle mode, clear BSY and generate an interrupt. If the sector count is non-zero, the automatic power down mode is enabled. If the sector count is zero, the automatic power mode is disabled.

7. Idle Immediate (code: E1H or 95H): This command causes the drive to set BSY, enter the Idle(Read) mode, clear BSY and generate an interrupt.

- 8. Initialize Drive Parameters (code: 91H): This command enables the host to set the number of sectors per track and the number of heads per cycle.

- 9. Read Buffer (code: E4H): This command enables the host to read the current contents of the drive's sector buffer.

- 10. Read Multiple (code: C4H): This command performs similarly to the Read Sectors command. Interrupts are not generated on each sector, but on the transfer of a block which contains the number of sectors defined by a Set Multiple command.

- 11. Read Long Sector (code 22H or 23H): This command performs similarly to the Read Sector(s) command except that it returns 516 bytes of data instead of 512 bytes.

- 12. Read Sector(s) (code 20H, 21H): This command reads from 1 to 256 sectors as specified in the Sector Count register. A sector count of 0 requests 256 sectors. The transfer beings at the sector specified in the Sector Number register.

- 13. Read Verify Sector(s) (code: 40H or 41H): This command is identical to the Read Sectors command, except that DRQ is never set and no data is transferred to the host.

- 14. Recalibrate (code: 1XH): This command is effectively a NOP command to the drive and is provided for compatibility purposes.

- 15. CFA Request Extended Error (code: 03H): This command requests an extended error code after command ends with an error.

- 16. Seek (code: 7XH): This command is effectively a NOP command to the drive although it does perform a range check.

| Feature | Operation                                                             |

|---------|-----------------------------------------------------------------------|

| 01H     | Enable 8-bit data transfers.(CFA feature set only)                    |

| 55H     | Disable Read Look Ahead.                                              |

| 66H     | Disable Power on Reset (POR) establishment of defaults at Soft Reset. |

| 81H     | Disable 8-bit data transfers. (CFA feature set only)                  |

| BBH     | 4 bytes of data apply on Read/Write Long commands.                    |

| ССН     | Enable Power on Reset (POR) establishment of defaults at Soft Reset.  |

17. Set Features (code: EFH): This command is used by the host to establish or select certain features.

- 18. Set Multiple Mode (code: C6H): This command enables the drive to perform Read and Write Multiple operations and establishes the block count for these commands.

- 19. Sleep (code: E6H or 99H): This command causes the drive to set BSY, enter the Sleep mode, clear BSY and generate an interrupt.

- 20. Stand By (code: E2H or 96H): This command causes the drive to set BSY, enter the Standby mode, clear BSY and return the interrupt immediately.

- 21. Stand By Immediate (code: E0H or 94H): This command causes the drive to set BSY, enter the Standby mode, clear BSY and return the interrupt immediately

- 22. CFA Translate Sector (code: 87H): This command allows the host a method of determining the exact number of times a use sector has been erased and programmed

- 23. CFA Wear Level (code: F5H): This command is effectively a NOP command and only implemented for backward compatibility. The Sector Count Register will always be returned with a 00H indicating Wear Level is not needed.

- 24. Write Buffer (code: E8H): This command enables the host to overwrite contents of the drive's sector buffer with any data pattern desired.

- 25. Write Long Sector (code: 32H or 33H): This command is provided for compatibility purposes and is similar to the Write Sector(s) command except that it writes 516 bytes instead of 512 bytes.

- 26. Write Multiple (code: C5H): This command is similar to the Write Sector(s) command. Interrupts are not presented on each sector, but on the transfer of a block which contains the number of sectors defined by Set Multiple command.

- 27. CFA Write Multiple without Erase (code: CDH): This command is similar to the Write Multiple command with the exception that an implied erase before write operation is not performed.

- 28. Write Sector(s) (code: 30H or 31H): This command writes from 1 to 256 sectors as specified in the Sector Count register. A sector count of zero requests 256 sectors. The transfer begins at the sector specified in the Sector Number register.

- 29. CFA Write Sector(s) without Erase (code: 38H): This command is similar to the Write Sector(s) command with the exception that an implied erase before write operation is not performed.

- 30. Write Verify(s) (code: 3CH): This command is similar to the Write Sector(s) command, except each sector is verified immediately after being written.

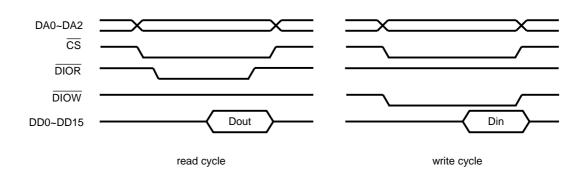

### Sector Transfer Protocol

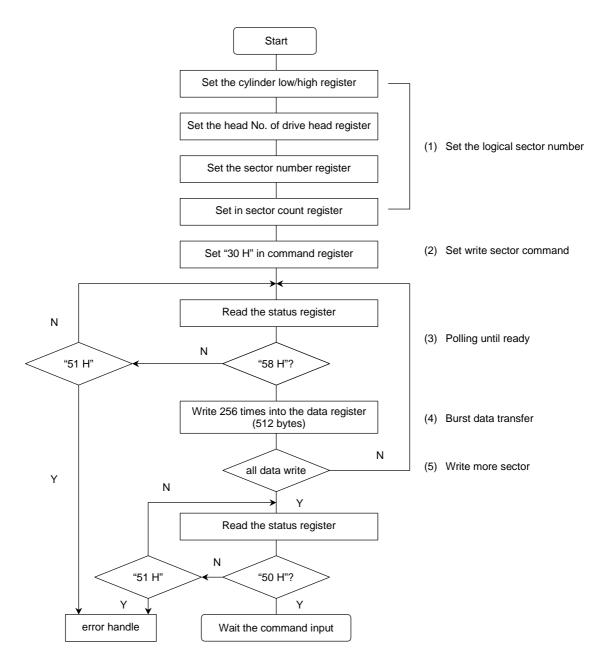

1. Sector read: The protocol of sector(s) read is as follows.

2. Sector write: The protocol of write sector(s) is as follows.

## <u>AC Characteristics</u> (Ta = $-40 \sim +85^{\circ}$ C, V<sub>CC</sub> = 5 V ± 10%)

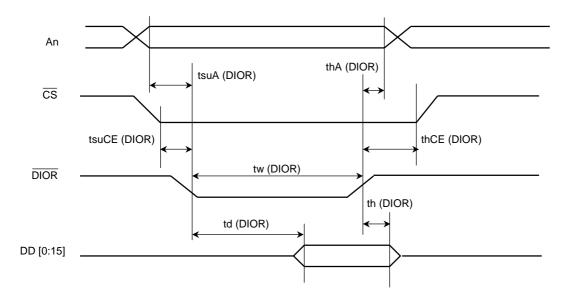

## Access Read AC Characteristics

| Parameter                   | Symbol       | Min | Тур. | Max | Unit |

|-----------------------------|--------------|-----|------|-----|------|

| Data delay after DIOR       | td (DIOR)    | _   | _    | 50  | ns   |

| Data hold following DIOR    | th (DIOR)    | 5   | —    | _   | ns   |

| DIOR width time             | tw (DIOR)    | 70  | —    | _   | ns   |

| Address setup before DIOR   | tsuA (DIOR)  | 15  | —    | _   | ns   |

| Address hold following DIOR | thA (DIOR)   | 10  | —    |     | ns   |

| CS setup before DIOR        | tsuCS (DIOR) | 5   | —    | _   | ns   |

| CS hold following DIOR      | thCS (DIOR)  | 10  | _    |     | ns   |

#### Access Read Timing

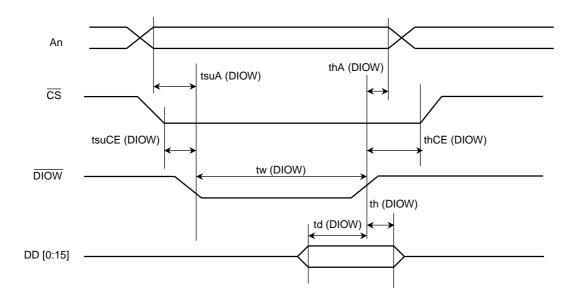

### Access Write AC Characteristics

| Parameter                   | Symbol       | Min | Тур. | Max | Unit |

|-----------------------------|--------------|-----|------|-----|------|

| Data setup before DIOW      | tsu (DIOW)   | 20  | _    | _   | ns   |

| Data hold following DIOW    | th (DIOW)    | 10  | _    | _   | ns   |

| DIOW width time             | tw (DIOW)    | 70  | _    | _   | ns   |

| Address setup before DIOW   | tsuA (DIOW)  | 15  | _    | _   | ns   |

| Address hold following DIOW | thA (DIOW)   | 10  | _    | _   | ns   |

| CS setup before DIOW        | tsuCS (DIOW) | 5   | _    | _   | ns   |

| CS hold following DIOW      | thCS (DIOW)  | 10  | _    | _   | ns   |

### Access Write Timing

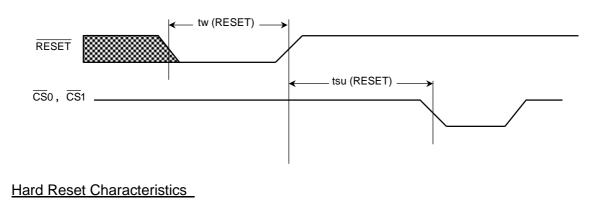

### **Power on Reset Characteristics**

This table summarizes the power on reset sequence.

#### Hard Reset Timing

| Parameter         | Symbol      | Min | Тур | Max | Unit | Test Conditions |

|-------------------|-------------|-----|-----|-----|------|-----------------|

| Reset setup time  | tsu (RESET) | 2   | _   | _   | ms   |                 |

| Reset pulse width | tw (RESET)  | 25  | _   | _   | μs   |                 |

### **Attention for Drive Use**

- After performing the reset or power off operation, the information of all registers is cleared.

- Please do not insert or remove the drive while the host is active.

- After performing a hard reset, soft reset, power on reset or command input, commands cannot be applied to the drive while the bit7 (BSY) in the Status register is "high" level. Flash drive will not respond in this case.

- It is recommended that the drive should be formatted using an operating system before using it.