PRODUCTION DATA - Mar 7, 2016

### **Features**

- · High efficiency 5V DC/DC buck converter

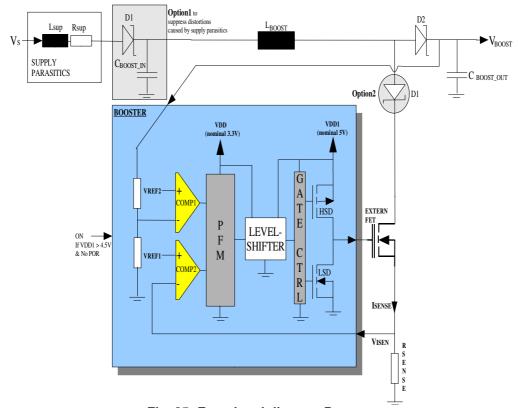

- Optional DC/DC boost converter

- Wakeable HS-CAN transceiver (ISO11898-2 and -5)

- Up to four LIN transceiver LIN 2.1, SAE-J2602 conformance

- Operating range 2.5V up to 28V

- Typ. 45μA sleep current consumption

- Typ. 85µA standby current consumption with active DC/DC buck converter

- Configurable μC watchdog (cycle time and type)

- BUS pins ESD-protected 8kV according to IEC-61000-4-2

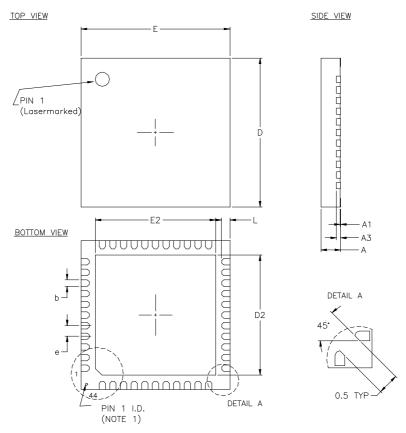

- Package QFN44L7

| with Booster | Without Booster | No. of LINs |

|--------------|-----------------|-------------|

| E521.12      | E521.02         | 2           |

| E521.13      | E521.03         | 3           |

| E521.14      | E521.04         | 4           |

## **Applications**

· Body control units, gateways

## **General Description**

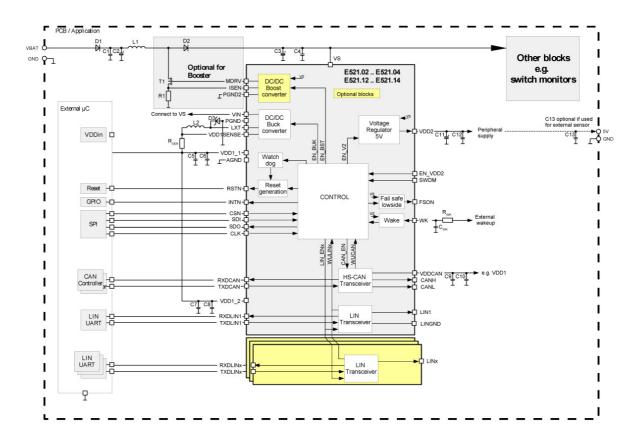

The CAN/LIN SBC family with DC/DC voltage regulator provides beside the CAN and LIN tranceivers the main  $\mu C$  power supply with a high efficiency DC/DC converter. An additional linear regulator can be used independently as peripheral supply. All supplies are monitored and can signalize a fail event by SPI interface. The main DC/DC supply monitor can generate a  $\mu C$  reset. System failure can activate a fail-safe output signal for limp home support.

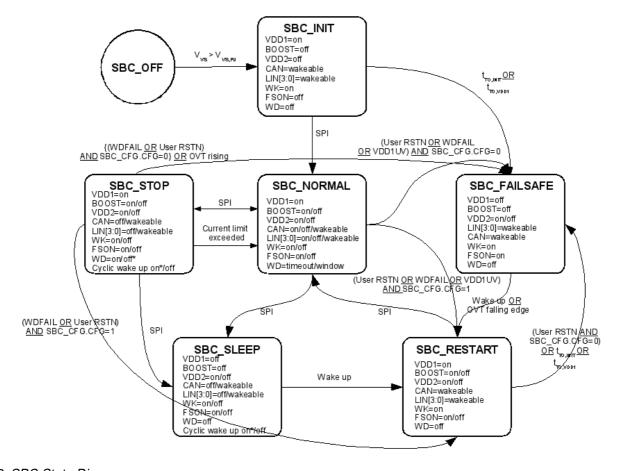

The CAN/LIN SBC family provides SLEEP, STOP, ACTIVE and FAILSAFE states.

The device is capable of detecting local and remote wake-up events which can be individually enabled via SPI.

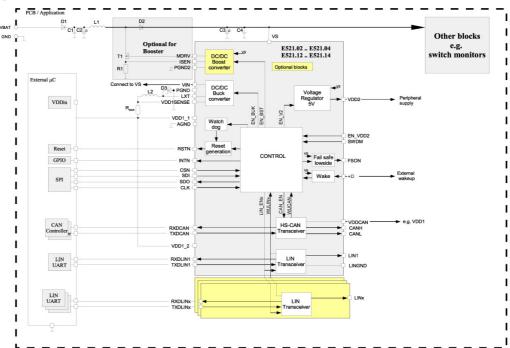

## **Typical Applications Circuit**

ELMOS Semiconductor AG reserves the right to change the detail specifications as may be required to permit improvements in the design of its products.

Elmos Semiconductor AG Data Sheet QM-No.: 25DS0093E.01

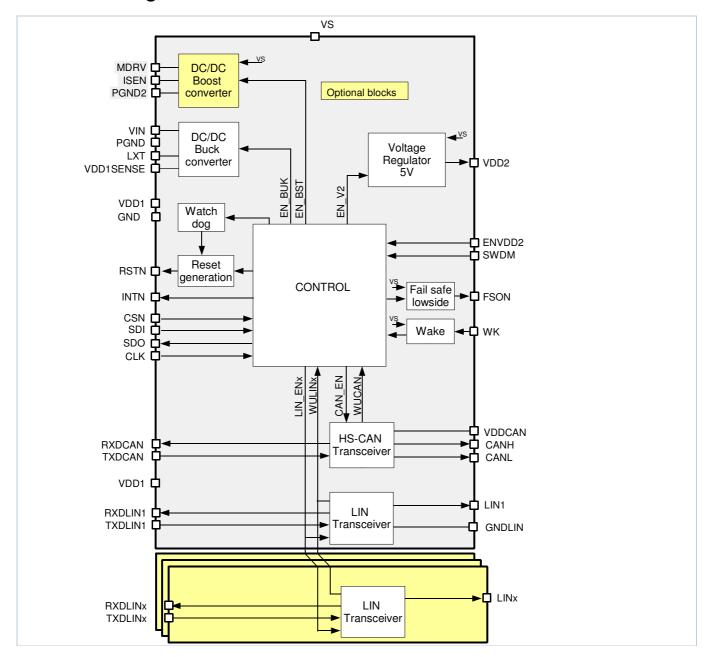

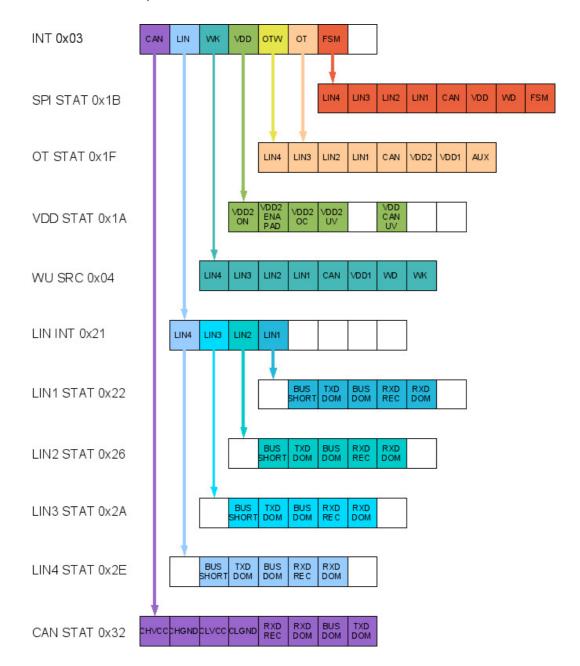

## **Functional Diagram**

PRODUCTION DATA - Mar 7, 2016

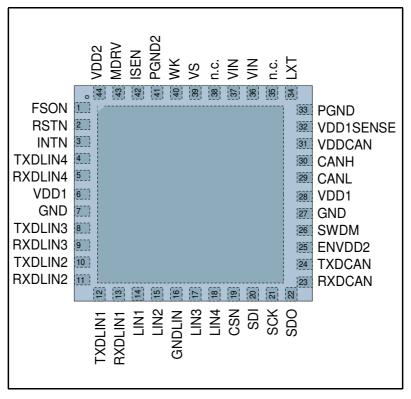

## **Pin Configuration**

Note: Top view, not to scale

# **Pin Description**

| Pin | Name    | Туре | Description                                                                                             |

|-----|---------|------|---------------------------------------------------------------------------------------------------------|

| 1   | FSON    | 0    | Fail safe output, open drain stage, low active                                                          |

| 2   | RSTN    | Ю    | Reset output, low active, pull up                                                                       |

| 3   | INTN    | Ю    | Interrupt output, low active, pull up Setup for bit SBC.CFG                                             |

| 4   | TXDLIN4 | I    | LIN4 transmit data, pull up, optional<br>E521.04/.14, only all other versions are not connected         |

| 5   | RXDLIN4 | 0    | LIN4 receive data E521.04/.14 only, all other versions are not connected                                |

| 6   | VDD1    | S    | Voltage Supply 1                                                                                        |

| 7   | GND     | S    | Ground                                                                                                  |

| 8   | TXDLIN3 | I    | LIN3 transmit data, pull up, optional<br>E521.03/.04/.13/.14 only, all other versions are not connected |

PRODUCTION DATA - Mar 7, 2016

| Pin | Name      | Туре  | Description                                                    |

|-----|-----------|-------|----------------------------------------------------------------|

| 9   | RXDLIN3   | 0     | LIN3 receive data                                              |

| 3   | TIADLING  |       | E521.03/.04/.13/.14 only, all other versions are not connected |

| 10  | TXDLIN2   | I     | LIN2 transmit data, pull up                                    |

| 11  | RXDLIN2   | 0     | LIN2 receive data                                              |

| 12  | TXDLIN1   | I     | LIN1 transmit data, pull up                                    |

| 13  | RXDLIN1   | 0     | LIN1 receive data                                              |

| 14  | LIN1      | Ю     | LIN1 bus line                                                  |

| 15  | LIN2      | Ю     | LIN2 bus line                                                  |

| 16  | GND       | S     | LIN ground                                                     |

| 17  | LIN3      | Ю     | LIN3 bus line,                                                 |

| 17  | LINO      | 10    | E521.03/.04/.13/.14 only, all other versions are not connected |

| 18  | LIN4      | Ю     | LIN4 bus line,                                                 |

| 10  | LIIVT     |       | E521.04/.14 only, all other versions are not connected         |

| 19  | CSN       | I     | SPI chip select, low active, pull up                           |

| 20  | SDI       | I     | SPI serial data input                                          |

| 21  | SCK       | I     | SPI clock, pull down                                           |

| 22  | SDO       | 0     | SPI serial data output                                         |

| 23  | RXDCAN    | 0     | CAN receive data                                               |

| 24  | TXDCAN    | I     | CAN transmit data, pull up                                     |

| 25  | ENVDD2    | I     | Enables VDD2                                                   |

| 26  | SWDM      |       | Must be connected to GND in application                        |

| 20  | 2 AN DINI | l<br> | Enables software development function, pull down               |

| 27  | GND       | S     | Ground                                                         |

| 28  | VDD1      | S     | Voltage Supply 1                                               |

| 29  | CANL      | Ю     | CANL bus Line                                                  |

| 30  | CANH      | Ю     | CANH bus Line                                                  |

| 31  | VDDCAN    | S     | HS-CAN supply                                                  |

| 32  | VDD1SENSE | Ю     | VDD1 Sense Back to DCDC Buck Converter                         |

| 33  | PGND      | S     | DCDC Buck Converter Power Ground                               |

| 0.4 | LVT       | 10    | DCDC Buck Converter                                            |

| 34  | LXT       | Ю     | Integrated Highside Switch Output                              |

PRODUCTION DATA - Mar 7, 2016

| Pin | Name  | Туре | Description                                                                                               |

|-----|-------|------|-----------------------------------------------------------------------------------------------------------|

| 35  | n.c.  |      | Not connected                                                                                             |

| 36  | VIN   | S    | DCDC Supply                                                                                               |

| 37  | VIN   | S    | DCDC Supply                                                                                               |

| 38  | n.c.  |      | Not connected, leave open                                                                                 |

| 39  | VS    | S    | Battery supply voltage                                                                                    |

| 40  | WK    | I    | Local wake up input, pull up or pull down                                                                 |

| 41  | PGND2 | S    | Power ground 2 (Boost Converter),<br>E521.12/.13/.14 only, all other versions are not connected           |

| 42  | ISEN  | I    | Sense Input (Boost Converter),<br>E521.12/.13/.14 only, all other versions are not connected              |

| 43  | MDRV  | 0    | Main Gate Driver Output (Boost Converter), E521.12/.13/.14 only, all other versions are not connected     |

| 44  | VDD2  | S    | Peripheral voltage supply                                                                                 |

| -   | EP    | S    | Exposed Pad. Connect to large copper ground plane for optimal heat dissipation. Connect to GNDA and GNDD. |

**Note:** S = Supply, I/O = Input/Output

PRODUCTION DATA - Mar 7, 2016

## 1 Absolute Maximum Ratings

Stresses beyond these absolute maximum ratings listed below may cause permanent damage to the device. These are stress ratings only; operation of the device at these or any other conditions beyond those listed in the operational sections of this document is not implied. Exposure to absolute maximum rated conditions for extended periods may affect device reliability. All voltages with respect to ground. Currents flowing into terminals are positive, those drawn out of a terminal are negative.

| Description                                                | Condition  | Symbol                   | Min  | Max                    | Unit     |

|------------------------------------------------------------|------------|--------------------------|------|------------------------|----------|

| Voltage at VS 1), 2)                                       | continuous | V <sub>vs</sub>          | -0.3 | 40                     | <b>V</b> |

| Voltage at VIN 1), 2)                                      | continuous | V <sub>vs</sub>          | -0.3 | 40                     | V        |

| Voltage at WK, FSON, ENVDD                                 | continuous | $V_{WK}$                 | -0.3 | 40                     | V        |

| Voltage at LIN14, CANL, CANL                               | continuous | V <sub>CANL</sub>        | -27  | 40                     | <b>V</b> |

| Voltage at LXT                                             | continuous | $V_{LXT}$                | -2   | V <sub>VIN</sub> + 0.3 | <b>V</b> |

| Voltage at VDDCAN                                          | continuous | V <sub>VDDCAN</sub>      | -0.3 | 5.5                    | V        |

| Voltage at SWDM                                            | continuous | V <sub>SWDM</sub>        | -0.3 | 5.5                    | V        |

| Voltage at digital pins TXDLIN14, RXDLIN14, TXDCAN, RXDCAN | continuous | V <sub>TXDLIN</sub>      | -0.3 | V <sub>VDD1</sub> +0.3 | V        |

| Voltage at VDD1                                            | continuous | $V_{\text{VDD1}}$        | -0.3 | 5.5                    | V        |

| Voltage at VDD2                                            | continuous | $V_{\text{VDD2}}$        | -5   | 40                     | V        |

| Current at WK                                              | continuous | I <sub>wk</sub>          | -15  | 1                      | mA       |

| Current of VDD1                                            | continuous | I <sub>VDD1</sub>        | -500 |                        | mA       |

| Current of VDD2, internally limited                        | continuous | I <sub>VDD2</sub>        | -200 | 1                      | mA       |

| Current at ENVDD2                                          | continuous | I <sub>ENVDD2</sub>      | -15  | 1                      | mA       |

| Maximum load at RXDCAN                                     |            | C <sub>RXDCAN,LOAD</sub> |      | 10                     | pF       |

| Junction temperature                                       | continuous | T <sub>JUNC</sub>        | -40  | 150                    | °C       |

| Storage temperature                                        | continuous | T <sub>STG</sub>         | -55  | 125                    | ∞        |

<sup>1)</sup> The device is implicitly protected against load dump

$<sup>^{\</sup>mbox{\tiny 2)}}$  The device is implicitly protected against jump start

PRODUCTION DATA - Mar 7, 2016

### **2 ESD Protection**

| Description                                                    | Condition | Symbol                 | Min  | Max  | Unit |

|----------------------------------------------------------------|-----------|------------------------|------|------|------|

| ESD HBM protection pins VDD2, LINx, WK, CANH and CANL          | 1)        | V <sub>ESD(HBM)</sub>  | -8   | +8   | kV   |

| ESD HBM protection all other pins                              | 1)        | V <sub>ESD(HBM)</sub>  | -2   | +2   | kV   |

| ESD system level protection pins VDD2, LINx, WK, CANH and CANL | to ground | $V_{\text{ESD(IEC)}}$  | -6   | +6   | kV   |

| ESD CDM Protection at all Pins                                 | 2)        | V <sub>ESD(CDM)</sub>  | -500 | +500 | V    |

| ESD CDM Protection at Edge Pins                                | 2)        | V <sub>ESD(CDM)C</sub> | -750 | +750 | V    |

$<sup>^{1)}</sup>$  According to AEC-Q100-002 (HBM) chip level test, C=100pF, R=1.5k $\Omega$   $^{2)}$  According to AEC-Q100-011 (CDM) chip level test, R=1 $\Omega$   $^{2)}$  Similar to IEC61000-4-2, C=150pF, R=330 $\Omega$

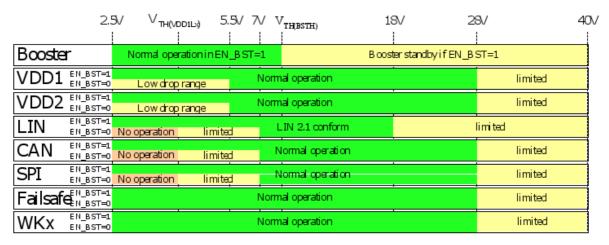

# **3 Recommended Operating Conditions**

| Description                                      | Condition | Symbol                | Min | Тур | Max | Unit |

|--------------------------------------------------|-----------|-----------------------|-----|-----|-----|------|

| Functional range E521.0204                       |           | $V_{VS,FUNC}$         | 5.5 | -   | 28  | V    |

| Functional range E521.1214                       |           | $V_{\text{VS,FUNC}}$  | 2.5 | -   | 28  | V    |

| Limited functional range E521.0204               |           | $V_{\text{VS,FL,LR}}$ | 2.5 | -   | 5.5 | ٧    |

| Limited functional range<br>E521.0204, E521.1214 |           | $V_{\text{VS,FL,HR}}$ | 28  | -   | 40  | V    |

| Ambient temperature                              |           | Т <sub>АМВ</sub>      | -40 | -   | 125 | S    |

PRODUCTION DATA - Mar 7, 2016

### **4 Electrical Characteristics**

$(V_{VS} = 5.5V \text{ to } 28V, T_{AMB} = -40 \,^{\circ}\text{C} \text{ to } +125 \,^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{VS} = 12.0V \text{ and } T_{AMB} = +25 \,^{\circ}\text{C}$ . Positive currents flow into the device pins.)

### 4.1 Power Supply and References; pins VS, GND

| No. | Description                                                | Condition                                                                                                                                            | Symbol                    | Min | Тур | Max | Unit |

|-----|------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----|-----|-----|------|

| 1   | Current consumption in SBC mode SLEEP 1)                   | SBC mode SLEEP, $V_S = V_{LIN} = V_{WK} = 13.5V$ , $I_{VDD1} = 0$ mA, $I_{VDD2} = 0$ mA, $T_{J} < 40$ °C, Booster is off All wake up sources enabled | Ivs,sleep                 |     | 45  | 110 | μА   |

| 1a  | Current consumption in SBC mode SLEEP 1)                   | SBC mode SLEEP, $V_S = V_{LIN} = V_{WK} = 13.5V$ , $I_{VDD1} = 0$ mA, $I_{VDD2} = 0$ mA, $T_J > 40$ °C, Booster is off All wake up sources enabled   | Ivs,sleep,40              |     | 65  | 150 | μА   |

| 2   | Current share for CAN wake up capability in SBC mode SLEEP | V <sub>S</sub> = 13.5V<br>Not production tested                                                                                                      | I <sub>VS,CAN,SLEEP</sub> |     | 5   | 10  | μΑ   |

| 3   | Current share for LIN wake up capability in SBC mode SLEEP | $V_S = 13.5V$<br>Not production tested                                                                                                               | I <sub>VS,LIN,SLEEP</sub> |     | 2   | 5   | μΑ   |

Table 1: DC Characteristics SLEEP

<sup>1)</sup> not production tested

PRODUCTION DATA - Mar 7, 2016

| No. | Description                                                                   | Condition                                                                                                                                           | Symbol                      | Min | Тур                   | Max | Unit |

|-----|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----|-----------------------|-----|------|

| 1   | Current consumption in SBC mode STOP without booster                          | SBC mode STOP, $V_{VS} = V_{LIN} = V_{WK} = 13.5V$ , $I_{VDD1} = 0$ mA, CAN off, LIN off, VDD2 off, All wake up sources enabled, $T_J > 40^\circ$   | lvs,stb,t<=125°C            |     | 100                   | 170 | μА   |

| 1a  | Current consumption in SBC mode STOP without booster                          | SBC mode STOP, $V_{VS} = V_{LIN} = V_{WK} = 13.5V$ , $I_{VDD1} = 0$ mA, CAN off, LIN off, VDD2 off, All wake up sources enabled, $T_J < 40^{\circ}$ | Ivs,stb,t<=40℃              |     | 85                    | 140 | μА   |

| 2   | Additional current if <b>VDD2</b> has load                                    | $V_{VS} = 13.5V, I_{VDD2} = -40mA$                                                                                                                  | I <sub>VS,VDD2</sub>        |     | 0.1*I <sub>VDD2</sub> |     | mA   |

| 3   | Current consumption of VDD2 voltage regulator in case of low load of 0.2mA 1) | $\begin{aligned} V_{VS} &= 13.5V, \\ I_{VDD2} &= -0.2mA \end{aligned}$                                                                              | I <sub>VS,VDD2,0.2m</sub> A |     | 1                     |     | mA   |

| 4   | Additional current in SBC mode STOP if cyclic wake up enabled 1)              | STOP Mode,<br>V <sub>VS</sub> = V <sub>LIN</sub> = V <sub>WK</sub> =<br>13.5V,<br>Cyclic wake up<br>enabled                                         | I <sub>VS,STB,CYCLIC</sub>  |     | 10                    |     | μА   |

Table 2: DC Characteristics STOP

| No. | Description                                     | Condition     | Symbol                          | Min | Тур  | Max | Unit |

|-----|-------------------------------------------------|---------------|---------------------------------|-----|------|-----|------|

| 1   | NORMAL mode current                             |               | I <sub>VS,NOM</sub>             |     | 150  | 400 | μΑ   |

|     | consumption                                     |               |                                 |     |      |     |      |

| 2   | Current consumption in active mode for all LINs | LIN dominant  | I <sub>VS,LIN,ACT,DOM</sub>     |     | 1.5  | 3   | mA   |

|     | not production tested                           |               |                                 |     |      |     |      |

| 3   | Current consumption in active mode for all LINs | LIN recessive | I <sub>VS,LIN,ACT,REC</sub>     |     | 0.25 | 0.5 | mA   |

| 4   | Current consumption in active mode for CAN      | CAN recessive | I <sub>VDDCAN,CAN,ACT,REC</sub> |     | 1    | 3   | mA   |

| 5   | Current consumption in active mode for CAN      | CAN dominant  | I <sub>VDDCAN,CAN,ACT,DOM</sub> |     | 40   | 105 | mA   |

|     | not production tested                           |               |                                 |     |      |     |      |

Table 3: DC Characteristics NORMAL

1) not production tested

PRODUCTION DATA - Mar 7, 2016

| No. | Description                                     | Condition | Symbol             | Min | Тур | Max | Unit |

|-----|-------------------------------------------------|-----------|--------------------|-----|-----|-----|------|

| 1   | Power on threshold according to pin <b>VS</b>   |           | $V_{\text{VS,PU}}$ | 4   |     | 5   | ٧    |

| 2   | Power down threshold according to pin <b>VS</b> |           | $V_{VS,PD}$        | 2.0 |     | 2.5 | V    |

Table 4: DC Characteristics POR

#### 4.1.1 Internal Time Base

| No. | Description                                                                                                                                         | Condition | Symbol           | Min   | Тур | Max   | Unit |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------------|-------|-----|-------|------|

|     | Internal time base, started automatically on demand. Most times specified are derived from this internal time base directly or by using prescalers. |           | t <sub>osc</sub> | 0.875 |     | 1.125 | μS   |

Table 5: AC Characteristics

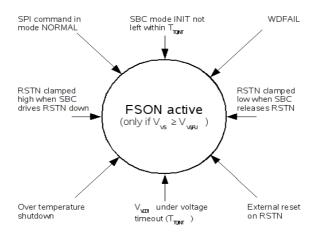

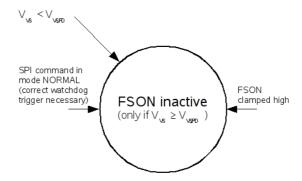

# **4.2 SBC Operating Modes**

| No. | Description                                                                                   | Condition                                                                                     | Symbol                    | Min  | Тур  | Max  | Unit |

|-----|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------|------|------|------|------|

| 1   | time out in SBC states INIT and RESTART                                                       |                                                                                               | $t_{TO,INIT}$             | 230  | 256  | 290  | ms   |

| 2   | time out in SBC states INIT and<br>RESTART for VDD1 start up                                  | VS rises above V <sub>ON-OFF,VS</sub> in before and not fallen below V <sub>ON-OFF_f,VS</sub> | t <sub>TO,VDD1</sub>      | 1.4  | 1.5  | 1.8  | S    |

| 3   | duration for changes between SBC states                                                       | detection of vaild<br>state change condi-<br>tion                                             | $t_{MODE\_CHANGE}$        |      | 8    |      | μs   |

| 4   | VS voltage threshold to be exceeded in order to start timeout $t_{TO,VDD1}$                   |                                                                                               | $V_{\text{ON-OFF,VS}}$    | 6.3  | 6.6  | 6.9  | V    |

| 5   | VS voltage threshold to be underflow in order to deactivate timeout $t_{\text{TO,VDD1}}^{1)}$ |                                                                                               | $V_{ON\text{-}OFF\_f,VS}$ | 5.75 | 6.05 | 6.35 | V    |

Table 6: AC Characteristics

1) Hysteresis is designed to 550mV, Not production tested

PRODUCTION DATA - Mar 7, 2016

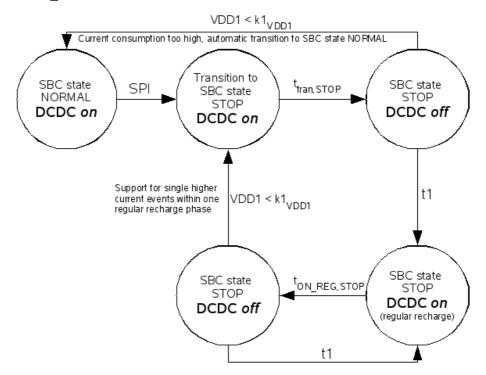

### VDD1 current observation in STOP mode

| No. | Description                                                                                                                                                 | Condition                         | Symbol                  | Min   | Тур | Max                      | Unit |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-------------------------|-------|-----|--------------------------|------|

| 1   | Timeout for whole system to enter STOP mode and therefore to decrease current consumption                                                                   | SPI command for<br>STOP mode sent | t <sub>tran_</sub> stop | 2.3   | 2.6 | 3.2                      | ms   |

| 2   | Threshold for VDD1 observation, 5V system. Upper limit ensures a safe voltage difference to VDD1 of 50mV using production test data for each particular IC. | SBC mode STOP                     | k1 <sub>VDD1,5</sub> v  | 4.625 |     | V <sub>VDD1</sub> - 50mV | V    |

| 3   | Minimum time VDD1 needs to stay above k1 <sub>VDD1</sub>                                                                                                    | VDD1_CFG[7:6]=<br>0h              | t1 <sub>0</sub>         | 4.7   |     | 6.4                      | ms   |

|     | After this time DCDC is switched on for ton_REG,STOP in order to recharge VDD1                                                                              |                                   |                         |       |     |                          |      |

| 4   | Minimum time VDD1 needs to stay above k1 <sub>VDD1</sub>                                                                                                    | VDD1_CFG[7:6]=<br>1h              | t1 <sub>1</sub>         | 9.7   |     | 12.4                     | ms   |

|     | After this time DCDC is switched on for t <sub>ON_REG,STOP P</sub> in order to recharge VDD1                                                                | (default)                         |                         |       |     |                          |      |

| 5   | Minimum time VDD1 needs to stay above k1 <sub>VDD1</sub>                                                                                                    | VDD1_CFG[7:6]=<br>2h              | t1 <sub>2</sub>         | 19.5  |     | 24.5                     | ms   |

|     | After this time DCDC is switched on for ton_REG,STOP in order to recharge VDD1                                                                              |                                   |                         |       |     |                          |      |

| 6   | Minimum time VDD1 needs to stay above k1 <sub>VDD1</sub>                                                                                                    | VDD1_CFG[7:6]=<br>3h              | t1 <sub>3</sub>         | 39.5  |     | 48.6                     | ms   |

|     | After this time DCDC is switched on for ton_REG,STOP in order to recharge VDD1                                                                              |                                   |                         |       |     |                          |      |

| 7   | On time of DCDC during regular recharge phase                                                                                                               | STOP mode                         | ton_reg,stop            | 110   |     | 160                      | μS   |

| 8   | Internal delay of DCDC after switching on request                                                                                                           |                                   | $t_{DEL,ON}$            | -     | 10  | 25                       | μS   |

Table 7: Characteristics

PRODUCTION DATA - Mar 7, 2016

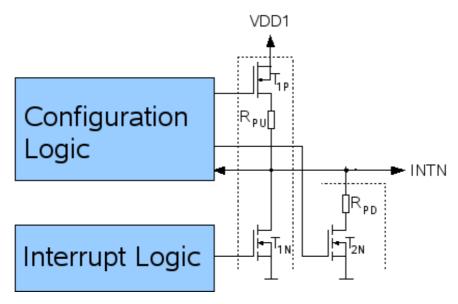

### 4.2.1 Configuration for transition behaviour to states FAILSAFE or RESTART

| No. | Description                                                            | Condition      | Symbol                           | Min | Тур | Max | Unit |

|-----|------------------------------------------------------------------------|----------------|----------------------------------|-----|-----|-----|------|

| 1   | Pull down resistance active during determination phase for SBC_CFG.CFG | SBC state INIT | R <sub>INTN,SBC_CFG,CFG,PD</sub> | 80  | 105 | 150 | kΩ   |

| 2   | Voltage level for detecting logic level low at <b>INTN</b>             | SBC state INIT | V <sub>INTN,SBC_CFG,L</sub>      |     |     | 0.7 | V    |

| 3   | Voltage level for detecting logic level high at INTN                   | SBC state INIT | $V_{INTN,SBC\_CFG,H}$            | 2.6 |     |     | V    |

Table 8: DC Characteristics

### Software Development function; pin SWDM

| No. | Description                                                                               | Condition | Symbol                   | Min | Тур | Max | Unit |

|-----|-------------------------------------------------------------------------------------------|-----------|--------------------------|-----|-----|-----|------|

| 1   | Voltage to be applied to pin <b>SWDM</b> in order to enable software development function |           | V <sub>ENABLE,SWDM</sub> | 0.7 |     |     | VDD1 |

| 2   | Pull down resistance                                                                      |           | R <sub>PD,SWDM</sub>     | 80  | 120 | 200 | kΩ   |

Table 9: DC Characteristics

### Over temperature behaviour

| No. | Description                                                                             | Condition                  | Symbol                            | Min | Тур | Max | Unit |

|-----|-----------------------------------------------------------------------------------------|----------------------------|-----------------------------------|-----|-----|-----|------|

| 1   | CAN over temperature detected                                                           | CAN enabled                | $T_{OT,CAN}$                      | 150 |     |     | လိ   |

| 2   | LIN over temperature detected.<br>Each LIN has its own sensor.                          | LIN enabled                | $T_{OT,LIN}$                      | 150 |     |     | °C   |

| 3   | VDD1 over temperature detected 1)                                                       | VDD1 enabled               | $T_{\text{OT,VDD1}}$              | 150 | 165 |     | .c   |

| 4   | VDD1 over temperature detection hysteresis 1)                                           | VDD1 enabled               | $T_{OT,VDD1,HYST}$                |     | 40  |     | °C   |

| 5   | VDD2 over temperature warning detected                                                  | VDD2 enabled               | T <sub>OT,VDD2,WARN</sub>         | 120 |     |     | ℃    |

| 6   | Temperature difference between failure and warning threshold                            | VDD2 enabled               | T <sub>OT,VDD2,FAIL</sub> to WARN | 10  |     |     | °C   |

| 7   | VDD2 over temperature detected                                                          | VDD2 enabled               | $T_{OT,VDD2,FAIL}$                | 140 |     | 180 | ∞    |

| 8   | Over temperature for aux. internal structures detected                                  | System in state<br>NORMAL  | $T_{OT,INT}$                      | 140 |     |     | ℃    |

| 9   | Over temperature detection hysteresis, valid for all sensors except otherwise stated 1) | Temperature sensor enabled | Т <sub>от,нувт</sub>              |     | 20  |     | ℃    |

Table 10: OT Characteristics

1) Not production tested

PRODUCTION DATA - Mar 7, 2016

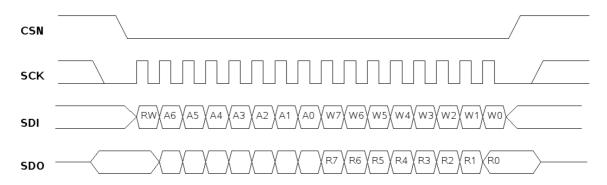

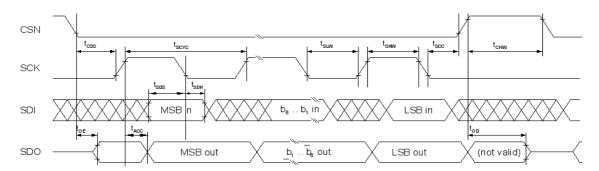

# SPI communication; pins SCK, SDI, SDO, CSN

| No. | Description               | Condition                          | Symbol                | Min                     | Тур | Max | Unit |

|-----|---------------------------|------------------------------------|-----------------------|-------------------------|-----|-----|------|

| 1   | High level input voltage  |                                    | $V_{\text{CSN,INH}}$  | 0.7                     |     |     | VDD1 |

| 2   | Low level input voltage   |                                    | $V_{\text{CSN,INL}}$  |                         |     | 0.3 | VDD1 |

| 3   | High level input current  | $V_{CSN} = V_{VDD1}$               | I <sub>CSN,LEAK</sub> | -1                      | 0   | 1   | μA   |

| 4   | Pull up resistor          | $V_{CSN} = 0V$                     | R <sub>CSN,PU</sub>   |                         | 120 |     | kΩ   |

| 5   | High level input voltage  |                                    | $V_{SCK,INH}$         | 0.7                     |     |     | VDD1 |

| 6   | Low level input voltage   |                                    | $V_{SCK,INL}$         |                         |     | 0.3 | VDD1 |

| 7   | Pull down resistor        | $V_{\text{SCK}} = V_{\text{VDD1}}$ | R <sub>SCK,PD</sub>   |                         | 120 |     | kΩ   |

| 8   | High level input voltage  |                                    | $V_{\text{SDI,INH}}$  | 0.7                     |     |     | VDD1 |

| 9   | Low level input voltage   |                                    | $V_{\text{SDI,INL}}$  |                         |     | 0.3 | VDD1 |

| 10  | Low level output voltage  | $I_{SDO} = 1 \text{mA}$            | $V_{\text{SDO,OUTL}}$ |                         |     | 0.4 | V    |

| 11  | High level output voltage | $I_{SDO} = -1 \text{mA}$           | $V_{SDO,OUTH}$        | V <sub>VDD1</sub> - 0.4 |     |     | V    |

Table 11: DC Characteristics

PRODUCTION DATA - Mar 7, 2016

| No. | Description                                       | Condition | Symbol           | Min | Тур | Max | Unit |

|-----|---------------------------------------------------|-----------|------------------|-----|-----|-----|------|

| 1   | Serial clock cycle (1)                            | SCK       | tscyc            | 125 |     |     | ns   |

| 2   | SCK "H" pulse width (1)                           | SCK       | t <sub>shw</sub> | 50  |     |     | ns   |

| 3   | SCK "L" pulse width (1)                           | SCK       | t <sub>SLW</sub> | 50  |     |     | ns   |

| 4   | data setup time (WR) (1)                          | SDI       | t <sub>sds</sub> | 50  |     |     | ns   |

| 5   | data hold time (1)                                | SDI       | t <sub>sDH</sub> | 50  |     |     | ns   |

| 6   | access time (1)                                   | SDO       | t <sub>ACC</sub> |     |     | 50  | ns   |

| 7   | output enable time (1)                            | SDO       | toE              |     |     | 50  | ns   |

| 8   | output disable time (1)                           | SDO       | t <sub>od</sub>  |     |     | 50  | ns   |

| 9   | SCK-CSN (1)                                       | CSN       | t <sub>scc</sub> | 50  |     |     | ns   |

| 10  | CSN "H" pulse (1)                                 | CSN       | t <sub>CHW</sub> | 5   |     |     | us   |

|     | Minimum time between two consecutive SPI accesses |           |                  |     |     |     |      |

| 11  | CSN-SCK time (1)                                  | CSN       | t <sub>css</sub> | 125 |     |     | ns   |

| 12  | output disable time (1)                           | CSN       | t <sub>CSH</sub> | 120 |     |     | ns   |

Table 12: AC Characteristics

(1) not production tested

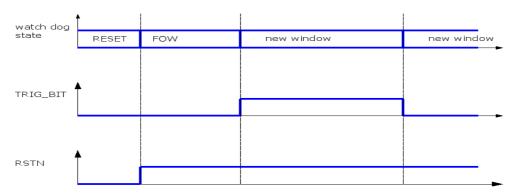

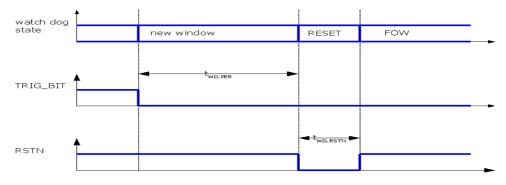

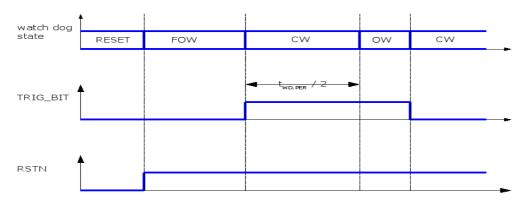

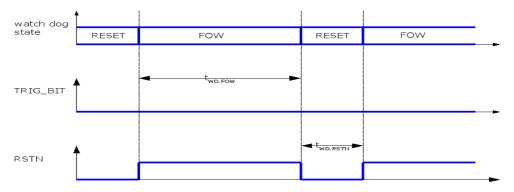

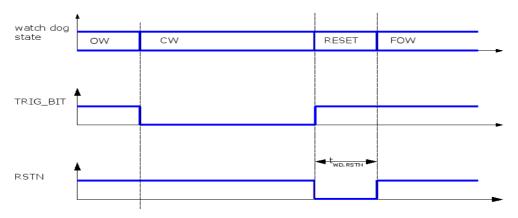

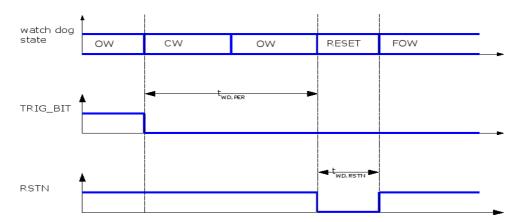

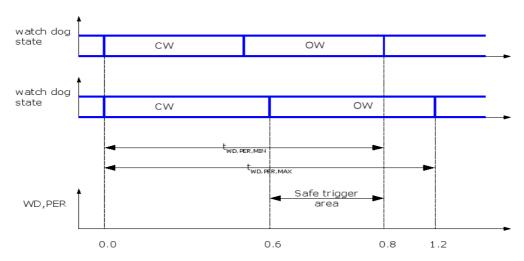

## 4.3 Watchdog; pin RSTN

| No. | Description                                                | Condition                                 | Symbol                                | Min  | Тур | Max  | Unit                |

|-----|------------------------------------------------------------|-------------------------------------------|---------------------------------------|------|-----|------|---------------------|

| 1   | Minimum watchdog time base important for safe trigger area |                                           | $t_{\text{WD,PER,MIN}}$               | 0.85 |     |      | t <sub>WD,PER</sub> |

| 2   | Maximum watchdog time base important for safe trigger area |                                           | $t_{\text{WD},\text{PER},\text{MAX}}$ |      |     | 1.15 | t <sub>WD,PER</sub> |

| 3   | First open window                                          | open window after <b>RSTN</b> is released | $t_{WD,FOW}$                          | 230  |     | 290  | ms                  |

| 4   | Watchdog reset time                                        |                                           | t <sub>wd,rstn</sub>                  | 450  |     | 650  | μS                  |

Table 13: AC Characteristics

PRODUCTION DATA - Mar 7, 2016

### 4.3.1 External Reset / Reset clamping

| No. | Description                              | Condition               | Symbol               | Min | Тур | Max | Unit |

|-----|------------------------------------------|-------------------------|----------------------|-----|-----|-----|------|

| 1   | output low level                         | I <sub>RSTN</sub> = 1mA | $V_{RSTN,OUTL}$      |     |     | 0.4 | V    |

|     |                                          | $V_{VDD1} > 3V$         |                      |     |     |     |      |

| 2   | internal pull up resistor                | $V_{RSTN} = 0V$         | R <sub>RSTN,PU</sub> | 22  | 32  | 42  | kΩ   |

| 3   | Voltage level for detecting low at RSTN  |                         | $V_{RSTN,INL}$       |     |     | 0.7 | V    |

| 4   | Voltage level for detecting high at RSTN |                         | $V_{RSTN,INH}$       | 2.6 |     |     | V    |

Table 14: DC Characteristics

| No. | Description                                                                                    | Condition | Symbol                   | Min | Тур | Max | Unit |

|-----|------------------------------------------------------------------------------------------------|-----------|--------------------------|-----|-----|-----|------|

| 1   | debounce time for external applied reset                                                       |           | t <sub>rstn,deb</sub>    |     | 4   |     | ms   |

| 2   | time out for short detection to <b>VDD1</b>                                                    |           | t <sub>RSTN,TO,VDD</sub> |     | 16  |     | ms   |

| 3   | time out for short detection to <b>GND</b> , can only be detected after twd.rstn or tvdd1,rstn |           | twdrstn,to,gnd           |     | 16  |     | ms   |

Table 15: AC Characteristics

## 4.4 Local wake up; pin WK

| No. | Description                                         | Condition                                          | Symbol             | Min  | Тур | Max | Unit |

|-----|-----------------------------------------------------|----------------------------------------------------|--------------------|------|-----|-----|------|

| 1   | Threshold of local wake up, $V_{\text{WK}}$ rising  | V <sub>wk</sub> rising                             | $V_{WK,TH,LH}$     | 0.6  |     | 0.8 | VS   |

| 2   | Threshold of local wake up, $V_{\text{WK}}$ falling | $V_{w\kappa}$ falling                              | $V_{WK,TH,HL}$     | 0.5  |     | 0.7 | VS   |

| 3   | Pull up current                                     | $V_{WK} > V_{WK,TH,LH\_max} $ $VS - V_{WK} > 1V$   | $I_{WK,PU}$        | -100 |     | -10 | μΑ   |

| 4   | Pull down current                                   |                                                    | I <sub>WK_PD</sub> | 10   |     | 100 | μΑ   |

| 5   | Leakage current                                     | VS = 12V,<br>$V_{WK} = 0V$ or<br>$V_{WK} = V_{VS}$ | lwk_leak           | -2   |     | +2  | μΑ   |

### Table 16: DC Characteristics

| No. | Description                 | Condition                              | Symbol           | Min | Тур | Max | Unit |

|-----|-----------------------------|----------------------------------------|------------------|-----|-----|-----|------|

| 1   | Local wake up debounce time | Threshold crossing transition detected | $t_{\sf WK,DEB}$ | 20  |     | 30  | μs   |

Table 17: AC Characteristics

PRODUCTION DATA - Mar 7, 2016

# 4.5 LIN Transceiver; pins LIN1 to LIN4, TXDLIN1 to TXDLIN4, RXDLIN1 to RXDLIN4, GND-LIN

#### 4.5.1 Characteristics

| No. | Description                                                            | Condition                                                                                                       | Symbol                 | Min                 | Тур | Max      | Unit |

|-----|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|------------------------|---------------------|-----|----------|------|

| 1   | functional range LIN transceiver                                       |                                                                                                                 | $V_{\text{LIN,VS}}$    | 7                   | -   | 18       | V    |

| 2   | recessive output voltage                                               | TXDLINx = 1                                                                                                     | $V_{LIN,REC}$          | V <sub>vs</sub> -1V | -   | $V_{VS}$ | -    |

| 3   | dominant output voltage                                                | $ \begin{aligned}                                   $                                                           | $V_{LIN,DOM}$          | -                   | -   | 1.2      | V    |

| 4   | dominant output voltage                                                | $ \begin{array}{l} \textbf{TXDLINx} = 0, \ V_{VS} = \\ 18V, \ R_{LIN} = 0.5k\Omega \ to \\ V_{VS} \end{array} $ | $V_{\text{LIN,DOM1}}$  | -                   | -   | 2.0      | V    |

| 5   | receiver dominant level                                                |                                                                                                                 | $V_{\text{LIN,THDOM}}$ | -                   | -   | 0.4      | VS   |

| 6   | receiver recessive level                                               |                                                                                                                 | $V_{LIN,THREC}$        | 0.6                 | -   | -        | VS   |

| 7   | LIN bus center voltage                                                 | V <sub>LINx,BUSCNT</sub> = (V <sub>LINx,THDOM</sub> + V <sub>LINx,THREC</sub> ) / 2                             | $V_{LIN,BUSCNT}$       | 0.475               | -   | 0.525    | VS   |

| 8   | receiver hysteresis                                                    | $V_{\text{LINx,THREC}}$ - $V_{\text{LIN,THDOM}}$                                                                | $V_{LIN,HYS}$          | 0.02                | -   | 0.175    | VS   |

| 9   | output current limitation                                              | $V_{\text{LINx}} = V_{\text{VS,MAX}} = 18V$                                                                     | $I_{LIN,LIM}$          | 40                  | -   | 200      | mA   |

| 10  | pull up resistance                                                     |                                                                                                                 | $R_{\text{LIN,SLAVE}}$ | 20                  | 33  | 60       | kΩ   |

| 11  | leakage current flowing into pin LIN                                   | transmitter passive, $7V < V_{VS} < 18V, 7V < V_{LINx} < 18V, V_{LINx} > V_{VS}$                                | ILIN,BUSREC            | -                   | -   | 20       | μΑ   |

| 12  | pull up current flowing out of pin LIN                                 | transmitter passive, $7V < V_{VS} < 18V$ , $V_{LINx} = 0V$                                                      | $I_{LIN,BUSDOM}$       | -1                  | -   | -        | mA   |

| 13  | leakage current, ground disconnected ( <b>GND</b> device = <b>VS</b> ) | $V_{VS} = 13.5V, \ 0V < V_{LINx} < 18V$                                                                         | I <sub>LIN,NOGND</sub> | -1                  | -   | 0.1      | mA   |

| 14  | leakage current, supply disconnected                                   | $\begin{aligned} V_{VS} &= 0V, \\ 0V &< V_{LINx} < 18V \end{aligned}$                                           | I <sub>LIN</sub>       | -                   | -   | 20       | μΑ   |

| 15  | leakage current, supply disconnected, $T_J = 85^{\circ}\text{C}$ ,     | $\begin{aligned} V_{VS} &= 0V, \\ 0V &< V_{LINx} < 18V \end{aligned}$                                           | I <sub>LIN,85</sub>    | -                   | -   | 15       | μА   |

|     | not production tested                                                  |                                                                                                                 |                        |                     |     |          |      |

| 16  | clamping voltage, not production tested                                | $V_{VS} = 0V, I_{LINx} = 1mA$                                                                                   | $V_{LIN,CLAMP}$        | 40                  |     | -        | V    |

Table 18: DC Characteristics

PRODUCTION DATA - Mar 7, 2016

| No. | Description                                           | Condition                                                                                                                                                                                                                                                                                                      | Symbol                                                            | Min   | Тур | Max   | Unit  |

|-----|-------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-------|-----|-------|-------|

| 1   | input capacitance, not production tested!             | 7V < V <sub>VS</sub> < 18V                                                                                                                                                                                                                                                                                     | $C_{LIN,PIN}$                                                     | -     | -   | 30    | pF    |

| 2a  | receive propagation delay                             |                                                                                                                                                                                                                                                                                                                | $t_{\text{RXD,PDR}}$ , $t_{\text{RXD,PDF}}$                       | -     | -   | 6     | μS    |

| 2b  | receive propagation delay in FLASH mode <sup>1)</sup> |                                                                                                                                                                                                                                                                                                                | ${\sf t_{{\sf RXD,PDR,FLASH}}}$ , ${\sf t_{{\sf RXD,PDF,FLASH}}}$ | -     | -   | 2.5   | μѕ    |

| 3   | receive propagation delay symmetry                    |                                                                                                                                                                                                                                                                                                                | $t_{\sf RXD,SYM}$                                                 | -2    | -   | 2     | μS    |

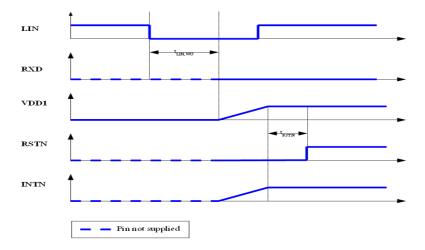

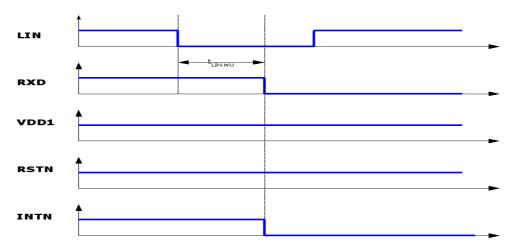

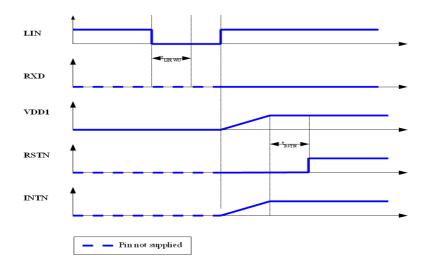

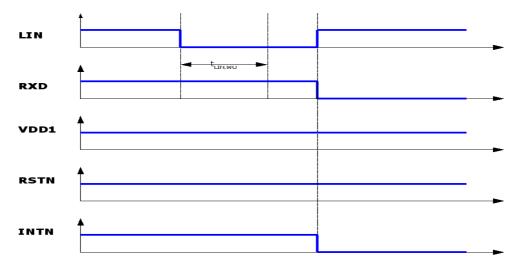

| 4   | wake up debounce time                                 |                                                                                                                                                                                                                                                                                                                | t <sub>LIN,WU</sub>                                               | 70    |     | 150   | μs    |

| 5   | Duty cycle 1 1)                                       | $\begin{split} &V_{\text{LIN,THREC}}(\text{max}) = \\ &0.744^*V_{\text{VS}}, \\ &V_{\text{LIN,THDOM}}(\text{max}) = \\ &0.581^*V_{\text{VS}}, V_{\text{VS}} = 7\text{-} \\ &18V, t_{\text{BIT}} = 50\text{us}, \\ &D_{\text{LIN,1}} = t_{\text{BUSREC}}(\text{min})/\\ &(2^*t_{\text{BIT}}) \end{split}$       | D <sub>LIN,1</sub>                                                | 0.396 | -   | -     | -     |

| 6   | Duty cycle 2 1)                                       | $\begin{array}{l} V_{\text{LIN,THREC}}(min) = \\ 0.422^*V_{VS}, \\ V_{\text{LIN,THDOM}}(min) = \\ 0.284^*V_{VS}, V_{VS} = 7 \\ 18V, t_{\text{BIT}} = 50\text{us}, \\ D_{\text{LIN,2}} = t_{\text{BUS}}, \\ \text{REC}(max)/(2^*t_{\text{BIT}}) \end{array}$                                                    | D <sub>LIN,2</sub>                                                | -     | -   | 0.581 | -     |

| 7   | Duty cycle 3 <sup>1)</sup>                            | $\begin{array}{l} V_{\text{LIN,THREC}}(\text{max}) = \\ 0.778^* V_{\text{VS}}, \\ V_{\text{LIN,THDOM}}(\text{max}) = \\ 0.616^* V_{\text{VS}}, V_{\text{VS}} = 7 \\ 18V, t_{\text{BIT}} = 96\text{us}, \\ D_{\text{LIN,3}} = t_{\text{BUSREC}}(\text{min}) / \\ (2^* t_{\text{BIT}}) \end{array}$              | D <sub>LIN,3</sub>                                                | 0.417 | -   | -     | 1     |

| 8   | Duty cycle 4 1)                                       | $\begin{array}{l} V_{\text{LIN,THREC}}(\text{min}) = \\ 0.389^* V_{\text{Vs}}, \\ V_{\text{LIN,THDOM}}(\text{min}) = \\ 0.251^* V_{\text{VS}}, V_{\text{VS}} = 7 - \\ 18V, t_{\text{BIT}} = 96 \text{us}, \\ D_{\text{LIN,4}} = t_{\text{BUS-}} \\ _{\text{REC}}(\text{max})/(2^* t_{\text{BIT}}) \end{array}$ | D <sub>LIN,4</sub>                                                | -     | -   | 0.590 | -     |

| 9   | receive data baud rate 2)                             | flash mode,<br>V <sub>VS</sub> = 13V                                                                                                                                                                                                                                                                           | $B_{LIN,RXD}$                                                     |       |     | 250   | kBd/s |

| 10  | transmit data baud rate 2)                            | $\begin{array}{l} flash\ mode, C_{LIN} = \\ 200PF,\ R_{LIN} = \\ 0.5k\Omega \\ V_{VS} = 13V \end{array}$                                                                                                                                                                                                       | $B_{\text{LIN},TXD}$                                              |       |     | 125   | kBd/s |

### Table 19: AC Characteristics

- 1) Bus load conditions (C<sub>LIN</sub>,R<sub>LIN</sub>): 1nF, 1k $\Omega$  or 6.8nF, 660 $\Omega$  or 10nF, 500 $\Omega$

- 2) Not production tested

PRODUCTION DATA - Mar 7, 2016

### 4.5.2 LIN TXD/RXD

| No. | Description                   | Condition             | Symbol              | Min                        | Тур | Max | Unit |

|-----|-------------------------------|-----------------------|---------------------|----------------------------|-----|-----|------|

| 1   | output low level range        | $I_{RXD,LINx} = 1mA$  | $V_{RXD,LINx,OUTL}$ | -                          | -   | 0.4 | V    |

| 2   | output high level range       | $I_{RXD,LINx} = -1mA$ | $V_{RXD,LINx,OUTH}$ | V <sub>VDD1</sub> -<br>0.4 | -   | -   | V    |

| 3   | input low voltage range       |                       | $V_{TXD,LINx,INL}$  | -                          | -   | 0.3 | VDD1 |

| 4   | input high voltage range      |                       | $V_{TXD,LINx,INH}$  | 0.7                        | -   | -   | VDD1 |

| 5   | Internal TXD pull up resistor | $V_{TXD,LINx} = 0V$   | $R_{TXD,LINx,PU}$   | 80                         | 110 | 150 | kΩ   |

Table 20: DC Characteristics

### 4.5.3 LIN Failure detection and recovery

| No. | Description                                | Condition | Symbol                   | Min | Тур | Max  | Unit |

|-----|--------------------------------------------|-----------|--------------------------|-----|-----|------|------|

| 1   | time out for txd dominant clamping failure |           | t <sub>LIN,TXD,DOM</sub> | 8.5 |     | 12.5 | ms   |

| 2   | time out for LIN dominant clamping failure |           | t <sub>LIN,BUS,DOM</sub> | 8.5 |     | 12.5 | ms   |

Table 21: AC Characteristics

PRODUCTION DATA - Mar 7, 2016

## HS-CAN Transceiver; pins CANH, CANL, RXDCAN, TXDCAN, VDDCAN

$(V_{VS} = 5.5V \text{ to } 28V, T_{AMB} = -40 ^{\circ}\text{C} \text{ to } +125 ^{\circ}\text{C}, V_{CAN} = -12V \text{ to } +12V \text{ unless otherwise noted.}$  Typical values are at  $V_{VS} = 12.0V$  and  $T_{AMB} = +25 ^{\circ}\text{C}$ . Positive currents flow into the device pins.)

| No. | Description                                                                                           | Condition                                                                              | Symbol                    | Min  | Тур                   | Max  | Unit |

|-----|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|---------------------------|------|-----------------------|------|------|

| 1   | CANH dominant output voltage                                                                          | $V_{TXDCAN} = 0V$<br>$R_L = 50\Omega$ to $65\Omega$                                    | $V_{DOM\_OUT\_H}$         | 3.0  |                       | 4.5  | V    |

| 2   | CANL dominant output voltage                                                                          | $V_{TXDCAN} = 0V$<br>$R_L = 50\Omega$ to $65\Omega$                                    | $V_{DOM\_OUT\_L}$         | 0.5  |                       | 2.0  | V    |

| 3   | Matching of dominant output voltages (V <sub>VDDCAN</sub> - (V <sub>CANH</sub> + V <sub>CANL</sub> )) | $V_{TXDCAN} = 0V$<br>$R_L = 50\Omega$ to $65\Omega$                                    | $V_{DOM\_OUT\_MATCH}$     | -400 |                       | 400  | mV   |

| 4   | Differential bus dominant output voltages (V <sub>CANH</sub> -V <sub>CANL</sub> )                     | $V_{TXDCAN} = 0V$<br>$R_L = 50\Omega$ to $65\Omega$                                    | $V_{DIFF\_OUT\_DOM}$      | 1.5  |                       | 3.0  | V    |

| 5   | Recessive output voltage on CANH and CANL                                                             | V <sub>TXDCAN</sub> = V <sub>VDD1</sub><br>CAN NORMAL and<br>LISTEN mode               | $V_{REC\_OUT}$            | 2.0  | V <sub>VDDCAN</sub> / | 3.0  | V    |

| 6   | Differential receiver threshold voltage                                                               | CAN NORMAL and<br>LISTEN mode                                                          | $V_{DIFF\_TH}$            | 500  | 700                   | 900  | mV   |

| 7   | Differential receiver threshold voltage, CAN off and wake up detection capability enabled             | CAN off, wakeable                                                                      | $V_{DIFF\_TH\_OFF}$       | 400  |                       | 1150 | mV   |

| 8   | Differential receiver hysteresis voltage                                                              | CAN NORMAL and<br>LISTEN mode                                                          | $V_{DIFF\_HYST}$          |      | 60                    |      | mV   |

| 9   | Differential bus recessive output voltages (VCANH - VCANL)                                            | CAN recessive, no load                                                                 | $V_{REC\_OUT\_OFF}$       | -100 |                       | 50   | mV   |

| 9a  | Recessive output voltage at CANH and CANL, low power mode                                             | CAN recessive, no load                                                                 | $V_{REC,LP}$              | -100 |                       | 100  | mV   |

| 10  | Short circuit output current on CANL                                                                  | $V_{TXDCAN} = 0V$<br>$V_{CANL} = 40V$                                                  | I <sub>SC_OUT_CANL</sub>  | 40   |                       | 100  | mA   |

| 11  | Short circuit output current on CANH                                                                  | $V_{TXDCAN} = 0V$<br>$V_{CANH} = -5V$                                                  | I <sub>SC_OUT_CANH</sub>  | -100 |                       | -40  | mA   |

| 12  | Recessive bus current                                                                                 | $V_{TXDCAN} = V_{VDD1}$<br>-27V < $V_{CANH/L}$ < 32V                                   | I <sub>REC_OUT</sub>      | -5   |                       | 5    | mA   |

| 13  | Input leakage current on <b>CANL</b><br>and <b>CANH</b>                                               | VDD connected to GND with $R = 0\Omega$ and $R = 47k\Omega$ $V_{CANH} = V_{CANL} = 5V$ | I <sub>LEAK_IN</sub>      | -10  |                       | 10   | μΑ   |

| 14  | Common mode input resistance                                                                          |                                                                                        | $R_{I\_COM}$              | 15   |                       | 35   | kΩ   |

| 15  | Differential input resistance                                                                         |                                                                                        | $R_{LDIF}$                | 30   |                       | 70   | kΩ   |

| 15a | Common mode input capacitance not production tested                                                   | $V_{TXDCAN} = VDD1$                                                                    | $C_l\_COM$                |      | 20                    |      | pF   |

| 15b | Differential input capacitance not production tested                                                  | $V_{TXDCAN} = VDD1$                                                                    | $C_{I\_DIF}$              |      | 10                    |      | pF   |

| 15c | Internal R <sub>in</sub> resistor matching of <b>CANH</b> and <b>CANL</b>                             |                                                                                        | $R_{\text{in\_matching}}$ | -3   |                       | 3    | %    |

PRODUCTION DATA - Mar 7, 2016

| No. | Description                                                                         | Condition           | Symbol                         | Min | Тур | Max | Unit |

|-----|-------------------------------------------------------------------------------------|---------------------|--------------------------------|-----|-----|-----|------|

| 16  | Differential bus recessive output voltages (V <sub>CANH</sub> - V <sub>CANL</sub> ) | $V_{TXDCAN} = VDD1$ | V <sub>DIFF_OUT_REC_LOAD</sub> | -5  |     | 5   | mV   |

| 17  | VDDCAN monitor threshold                                                            | HS-CAN enabled      | $V_{\text{VDDCAN}, \text{UV}}$ | 4.2 |     | 4.6 | V    |

| 18  | <b>VDDCAN</b> monitor threshold hysteresis                                          | HS-CAN enabled      | V <sub>VDDCAN,UV,HYST</sub>    |     | 100 |     | mV   |

|     | CANH / CANL common mode voltage range                                               |                     | $V_{\sf CAN}$                  | -12 |     | 12  | V    |

Table 22: DC Characteristics

| No. | Description                                                | Condition                                     | Symbol                           | Min  | Тур | Max  | Unit   |

|-----|------------------------------------------------------------|-----------------------------------------------|----------------------------------|------|-----|------|--------|

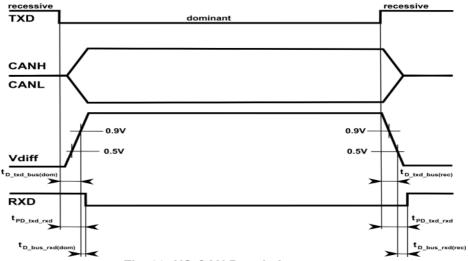

| 1   | Data rate range to be transmitted and received             | CAN NORMAL or<br>LISTEN mode                  | DR <sub>CAN</sub>                | 40   |     | 1000 | kBit/s |

| 2   | Delay <b>TXDCAN</b> to bus dominant not production tested  | CAN NORMAL<br>mode                            | t <sub>CAN,D_TXD_BUS</sub> (dom) | 25   |     | 110  | ns     |

| 3   | Delay <b>TXDCAN</b> to bus recessive not production tested | CAN NORMAL<br>mode                            | t <sub>CAN,D_TXD_BUS(rec)</sub>  | 10   |     | 95   | ns     |

| 4   | Delay bus to <b>RXDCAN</b> dominant not production tested  | CAN NORMAL or<br>LISTEN mode                  | t <sub>CAN,D_BUS_RXD(dom)</sub>  | 15   |     | 115  | ns     |

| 5   | Delay bus to <b>RXDCAN</b> recessive not production tested | CAN NORMAL or<br>LISTEN mode                  | tcan,d_bus_rxd(rec)              | 35   |     | 160  | ns     |

| 6   | Propagation delay <b>TXDCAN</b> to <b>RXDCAN</b>           | CAN NORMAL mode                               | tcan,pd_txd_rxd                  | 40   |     | 255  | ns     |

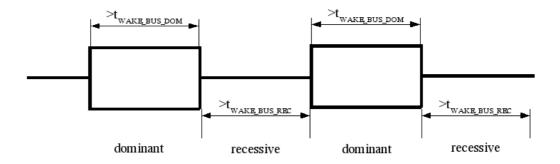

| 7   | Dominant time for wake up via bus                          | CAN off, wake up capability enabled, VS = 12V | t <sub>CAN,WAKE_BUS_DOM</sub>    | 0.75 |     | 5    | μS     |

| 8   | Recessive time for wake up via bus                         | CAN off, wake up capability enabled, VS = 12V | tcan,wake_bus_rec                | 0.75 |     | 5    | μS     |

| 9   | wake up time out                                           | CAN_CFG.RC = 0,<br>CAN_CFG.WU = 1             | t <sub>CAN,WAKE2</sub>           | 0.5  |     | 2    | ms     |

| 10  | CAN activation time                                        | CAN_CFG.RC = 1                                | t <sub>CAN,ACTIVE</sub>          |      |     | 50   | μs     |

Table 23: AC Characteristics

PRODUCTION DATA - Mar 7, 2016

#### 4.5.4 TXDCAN and RXDCAN

| No. | Description                             | Condition           | Symbol                  | Min                        | Тур | Max | Unit |

|-----|-----------------------------------------|---------------------|-------------------------|----------------------------|-----|-----|------|

| 1   | output low level range                  | $I_{RXDCAN} = 1mA$  | $V_{RXD,CAN,OUTL}$      | -                          | -   | 0.4 | V    |

| 2   | output high level range                 | $I_{RXDCAN} = -1mA$ | $V_{RXD,CAN,OUTH}$      | V <sub>VDD1</sub> -<br>0.4 | -   | -   | V    |

| 3   | input low voltage range                 |                     | $V_{TXD,CAN,INL}$       | -                          | ı   | 0.3 | VDD1 |

| 4   | input high voltage range                |                     | $V_{TXD,CAN,INH}$       | 0.7                        | -   | •   | VDD1 |

| 5   | Internal <b>TXDCAN</b> pull up resistor | $V_{TXDCAN} = 0V$   | R <sub>TXD,CAN,PU</sub> | 80                         | 110 | 150 | kΩ   |

Table 24: DC Characteristics

#### 4.5.5 CAN Failure detection and recovery

| No. | Description                                                              | Condition | Symbol                   | Min | Тур | Max | Unit |

|-----|--------------------------------------------------------------------------|-----------|--------------------------|-----|-----|-----|------|

| 1   | time out for TXD dominant clamping failure                               |           | t <sub>CAN,TXD,DOM</sub> | 1.4 |     | 1.9 | ms   |

| 2   | time out for BUS dominant clamping failure                               |           | t <sub>CAN,BUS,DOM</sub> | 1.4 |     | 1.9 | ms   |

| 3   | duration of bus dominant or recessive time for CAN bus failure detection |           | t <sub>BUS,FAIL</sub>    |     | 6   |     | μs   |

Table 25: AC Characteristics

## 4.6 Limp Home support; pin FSON

| No. | Description      | Condition            | Symbol          | Min | Тур | Max | Unit |

|-----|------------------|----------------------|-----------------|-----|-----|-----|------|

| 1   | output low level | $I_{FSON} = 1mA$     | $V_{FSON,OUTL}$ |     |     | 0.4 | V    |

|     |                  | $V_{VS} > V_{VS,PD}$ |                 |     |     |     |      |

Table 26: DC characteristics

## 4.7 Interrupt; pin INTN

| No. | Description      | Condition        | Symbol               | Min | Тур | Max | Unit |

|-----|------------------|------------------|----------------------|-----|-----|-----|------|

| 1   | output low level | $I_{INTN} = 1mA$ | $V_{INTN,OUTL}$      |     |     | 0.4 | ٧    |

|     |                  | $V_{VDD1} > 3V$  |                      |     |     |     |      |

| 2   | pull up resistor | $V_{INTN} = 0V$  | R <sub>INTN,PU</sub> | 80  | 105 | 150 | kΩ   |

Table 27: DC Characteristics

| ı | No. | Description | Condition                                 | Symbol                  | Min | Тур | Max | Unit |

|---|-----|-------------|-------------------------------------------|-------------------------|-----|-----|-----|------|

|   |     | ·           | Interrupt state change condition detected | t <sub>INTN,SETUP</sub> |     | 8   |     | tosc |

Table 28: AC Characteristics

PRODUCTION DATA - Mar 7, 2016

## 4.8 DCDC Buck converter; pins VIN, VDD1, VDD1SENSE, LXT, PGND

| No. | Description                                                                                          | Condition                                                                                                                                     | Symbol                        | Min | Тур | Max  | Unit |

|-----|------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-----|-----|------|------|

| 1   | <b>VDD1</b> output voltage if enabled, E521.0204, E521.1214                                          | $\begin{split} I_{VDD1} &= \text{-}500\text{mA}, \\ C_{VDD1} &> 22 \mu\text{F, ESR} \\ &< 120\text{m}\Omega,  V_{VIN} > \\ 5.5 V \end{split}$ | V <sub>VDD1,5</sub> v         | 4.9 |     | 5.1  | V    |

| 2   | Quiescent current consumption of DCDC buck converter in case of switched off, e.g. in SBC mode SLEEP | V <sub>VIN</sub> = 13.5V<br>DCDC off                                                                                                          | Ivin,dcdc_off                 |     | 9   | 20   | μΑ   |

| 3   | Quiescent current consumption of DCDC buck converter in case of switched on, e.g. in SBC mode NORMAL | $V_{VIN} = 13.5V$<br>DCDC on<br>Duty cycle = 0%                                                                                               | IVIN,DCDC_ON                  |     | 160 |      | μΑ   |

| 4   | reset threshold 1 for VDD1<br>E521.0204, E521.1214 1)                                                | VDD1_CFG.THR_<br>1:THR_0 = 0h,<br>VDD1 falling                                                                                                | V <sub>TH1,VDD1,RSTN</sub>    | 4.4 |     | 4.6  | V    |

| 5   | reset release threshold 1 for VDD1 E521.0204, E521.1214 1)                                           | VDD1_CFG.THR_<br>1:THR_0 = 0h,<br>VDD1 rising                                                                                                 | V <sub>TH1,VDD1_r,RSTN</sub>  | 4.6 |     | 4.9  | V    |

| 6   | reset threshold 2 for VDD1<br>E521.0204, E521.1214 1)                                                | VDD1_CFG.THR_<br>1:THR_0 = 1h,<br>VDD1 falling                                                                                                | V <sub>TH2,VDD1,RSTN</sub>    | 3.8 |     | 4    | V    |

| 7   | reset release threshold 2 for VDD1 E521.0204, E521.1214 1)                                           | VDD1_CFG.THR_<br>1:THR_0 = 1h,<br>VDD1 rising                                                                                                 | V <sub>TH2,VDD1_r,RSTN</sub>  | 4.0 |     | 4.25 | V    |

| 8   | reset threshold 3 for VDD1<br>E521.0204, E521.1214 1)                                                | VDD1_CFG.THR_<br>1:THR_0 = 2h,<br>VDD1 falling                                                                                                | V <sub>TH3,VDD1,RSTN</sub>    | 3.4 |     | 3.6  | V    |

| 9   | reset release threshold 3 for VDD1 E521.0204, E521.1214 1)                                           | VDD1_CFG.THR_<br>1:THR_0 = 2h,<br>VDD1 rising                                                                                                 | $V_{\text{TH3,VDD1\_r,RSTN}}$ | 3.6 |     | 3.85 | V    |

| 10  | reset threshold 4 for VDD1<br>E521.0204, E521.1214 1)                                                | VDD1_CFG.THR_<br>1:THR_0 = 3h,<br>VDD1 falling,<br>default selection                                                                          | V <sub>TH4,VDD1,RSTN</sub>    | 3   |     | 3.2  | V    |

| 11  | reset release threshold 4 for VDD1 E521.0204, E521.1214 1)                                           | VDD1_CFG.THR_<br>1:THR_0 = 3h,<br>VDD1 rising                                                                                                 | V <sub>TH4,VDD1_r,RSTN</sub>  | 3.2 |     | 3.45 | V    |

| 12  | LXT internal over current protection limit                                                           | $V_{VIN} > 5.5V$                                                                                                                              | I <sub>LXT</sub>              | 650 | 800 | 1100 | mA   |

<sup>&</sup>lt;sup>1)</sup> Hysteresis of reset thresholds is designed to > 150mV in 5V system

Table 29: DC Characteristics

PRODUCTION DATA - Mar 7, 2016

| No. | Description                                            | Condition | Symbol                    | Min | Тур | Max | Unit |

|-----|--------------------------------------------------------|-----------|---------------------------|-----|-----|-----|------|

| 1   | reset delay time after release of VDD1 reset           |           | t <sub>RSTN,VDD1</sub>    | 4.5 |     | 6.5 | ms   |

| 2   | VDD1 under voltage debounce time                       |           | t <sub>DEB,VDD1</sub>     |     | 10  | 50  | μS   |

| 3   | reset reaction time in case of under voltage condition |           | t <sub>RR,VDD1,RSTN</sub> |     | 14  | 20  | μS   |

Table 30: AC Characteristics

### 4.8.1 Pulse Frequency Modulated (PFM) Converter

**PFM Control Logic**

| No. | Description                                             | Condition                                                                 | Symbol              | Min | Тур  | Max | Unit |

|-----|---------------------------------------------------------|---------------------------------------------------------------------------|---------------------|-----|------|-----|------|

| 1   |                                                         | No over current detected                                                  | $T_{ON,MIN}$        |     | 260  |     | ns   |

| 2   | Minimum ON Time                                         | Over current detected                                                     | $T_{ON,OC}$         |     | 100  |     | ns   |

| 3   | Minimum OFF time without over current                   |                                                                           | $T_{OFF,MIN,NOM}$   |     | 520  |     | ns   |

| 4   | Nominal minimum OFF time after over current detection   |                                                                           | $T_{OFF,OC,NOM}$    |     | 1330 |     | ns   |

| 5   | Extended minimum OFF time after over currrent detection |                                                                           | $T_{OFF,OC,EXT}$    |     | 2450 |     | ns   |

| 6   |                                                         | depending on ratio V <sub>VIN</sub> /V <sub>DD1</sub> and load conditions | F <sub>OP</sub>     | 0   |      | 1.7 | MHz  |

| 7   | Peak Operation Frequency                                |                                                                           | F <sub>OP,MAX</sub> | 0.9 | 1.3  | 1.7 | MHz  |

Table 31: AC characteristics

PRODUCTION DATA - Mar 7, 2016

## Low drop regulator; pins VDD2, ENVDD2

| No. | Description                                                           | Condition                                                     | Symbol                      | Min  | Тур | Max  | Unit |

|-----|-----------------------------------------------------------------------|---------------------------------------------------------------|-----------------------------|------|-----|------|------|

| 1   | Parameter removed                                                     |                                                               |                             |      |     |      |      |

| 2   | output voltage range                                                  | VDD2 enabled,<br>$6V < V_{VS} < 28V$ ,<br>$I_{VDD2} > -100mA$ | V <sub>VDD2,100mA</sub>     | 4.9  | 5.0 | 5.1  | V    |

| 3   | output current limitation                                             | $V_{VDD2} = 0V, V_{VS} = 28V$                                 | I <sub>VDD2,LIM</sub>       | -220 |     | -110 | mA   |

| 4   | information only, RDS of regulator for $V_{VS} = 5.5V$                | VDD2 enabled,<br>Determined for                               | RDS <sub>VDD2,VS=5.5V</sub> |      |     | 12   | Ω    |

|     |                                                                       | $V_{VS} = 5.5V$                                               |                             |      |     |      |      |

|     |                                                                       | Not production tested                                         |                             |      |     |      |      |

| 5   | information only, RDS of regulator for $V_{VS} = 5.0V$                | VDD2 enabled,<br>Determined for                               | RDS <sub>VDD2,VS=5.0V</sub> |      |     | 13   | Ω    |

|     |                                                                       | $V_{VS} = 5.0V$                                               |                             |      |     |      |      |

|     |                                                                       | Not production tested                                         |                             |      |     |      |      |

| 6   | information only, RDS of regulator for $V_{VS} = 4.5V$                | VDD2 enabled,<br>Determined for                               | RDS <sub>VDD2,VS=4.5V</sub> |      |     | 15   | Ω    |

|     |                                                                       | $V_{VS} = 4.5V$                                               |                             |      |     |      |      |

|     |                                                                       | Not production tested                                         |                             |      |     |      |      |

| 7   | information only, RDS of regulator for $V_{VS} = 4.0V$                | VDD2 enabled,<br>Determined for                               | RDS <sub>VDD2,VS=4.0V</sub> |      |     | 17   | Ω    |

|     |                                                                       | $V_{VS} = 4.0V$                                               |                             |      |     |      |      |

|     |                                                                       | Not production tested                                         |                             |      |     |      |      |

| 8   | information only, RDS of regulator for $V_{\text{VS}} = 3.5 \text{V}$ | VDD2 enabled,<br>Determined for                               | RDS <sub>VDD2,VS=3.5V</sub> |      |     | 21   | Ω    |

|     |                                                                       | $V_{VS} = 3.5V$                                               |                             |      |     |      |      |

|     |                                                                       | Not production tested                                         |                             |      |     |      |      |

| 9   | under voltage threshold falling                                       | VDD2 enabled                                                  | $V_{\text{UV,THR}}$         | 4.5  |     | 4.8  | V    |

| 10  | under voltage hysteresis                                              | VDD2 enabled                                                  | $V_{\text{UV,HYS}}$         |      | 100 |      | mV   |

| 11  | threshold of <b>ENVDD2</b> rising                                     | V <sub>ENVDD2</sub> rising                                    | $V_{\text{ENVDD2,LH}}$      | 0.6  |     | 8.0  | VS   |

| 12  | threshold of <b>ENVDD2</b> falling                                    | V <sub>ENVDD2</sub> falling                                   | $V_{ENVDD2,HL}$             | 0.5  |     | 0.7  | VS   |

Table 32: DC Characteristics

PRODUCTION DATA - Mar 7, 2016

| No. | Description                 | Condition | Symbol              | Min | Тур | Max | Unit |

|-----|-----------------------------|-----------|---------------------|-----|-----|-----|------|

| 1   | under voltage debounce time |           | t <sub>DEB,UV</sub> | 150 |     | 280 | μS   |

Table 33: AC Characteristics

## 4.9 DCDC Boost converter; pins MDRV, ISEN, PGND2