# AS8202B TTP-C2NF Communication Controller

### 1 General Description

The AS8202B communication controller is an integrated device supporting serial communication according to the TTP specification version 1.1. It performs all communication tasks such as reception and transmission of messages in a TTP cluster without interaction of the host CPU. TTP provides mechanisms that allow the deployment in high-dependability distributed real-time systems. It provides the following services:

- Predictable transmission of messages with minimal jitter

- Fault-tolerant distributed clock synchronization

- Consistent membership service with small delay

- Masking of single faults

### 2 Key Features

- Dual-channel controller for redundant data transfers

- Dedicated controller supporting TTP (time-triggered protocol class C standardized in SAE 6003)

- Suited for dependable distributed real-time systems with guaranteed response time

- Asynchronous data rate up to 4 Mbit/s (MFM/Manchester)

- Synchronous data rate 20 to 25 Mbit/s

- Bus interface (speed, encoding) for each channel selectable independently

- 40 MHz oscillator clock support

- 16 MHz bus guardian clock with support for 16 MHz crystal or 16 MHz oscillator

- Single power supply 3.3V, 0.35µm CMOS process

- Full automotive temperature range (-40°C to 125°C)

- 16k x 16 SRAM for message, status, control area (communication network interface) and for scheduling information (MEDL)

- 4k x 16 (plus parity) instruction code RAM for protocol execution code

- Datasheet conforms to protocol revision 2.05

- 16k x 16 instruction code ROM containing startup execution code and deprecated protocol code revision 1.00

- 16-bit non-multiplexed asynchronous host CPU interface

- 16-bit RISC architecture

- Software tools, design support, development boards available Visit www.tttech.com

- Certification support package according to RTCA/DO-254 DAL A available – Visit www.tttech.com

- RoHS conform

### 3 Applications

The device is ideal for application fields such as, aerospace according to DO-254 level A (e.g. flight control, power distribution, engine control), industrial systems, and railway systems.

### Contents

| 1 | General Description                 | 1    |

|---|-------------------------------------|------|

| 2 | Key Features                        | 1    |

|   | Applications                        |      |

| 4 | Pin Assignments                     | 3    |

|   | 4.1 Pin Descriptions                | 3    |

| 5 | Absolute Maximum Ratings            | 6    |

| 6 | Electrical Characteristics          | 7    |

| 7 | Detailed Description                | 9    |

|   | 7.1 Host CPU Interface              | 9    |

|   | 7.1.1 Synchronous READYB Generation | 12   |

|   | 7.2 Reset and Oscillator            | 13   |

|   | 7.2.1 External Reset Signal         |      |

|   | 7.2.2 Integrated Power-On Reset     |      |

|   | 7.2.3 Oscillator Circuitry          |      |

|   | 7.2.4 Built-in Characteristics      |      |

|   | 7.3 TTP Bus Interface               | 14   |

|   | 7.4 TTP Asynchronous Bus Interface  | 15   |

|   | 7.5 TTP Synchronous Bus Interface   | 15   |

|   | 7.6 Test Interface                  | 16   |

|   | 7.7 LED Signals                     |      |

| 8 | Package Drawings and Markings       | . 17 |

| 9 | Ordering Information                | . 19 |

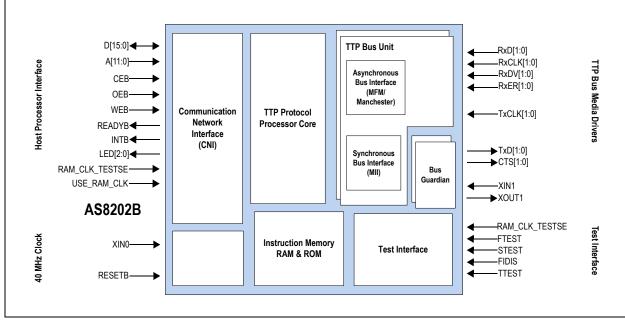

### 4 Pin Assignments

Figure 2. Pin Assignments (Top View)

### 4.1 Pin Descriptions

Table 1. Pin Descriptions

| Pin Name | Pin Number                    | Dir       | Description                                             |

|----------|-------------------------------|-----------|---------------------------------------------------------|

| VDD      | 4, 12, 29, 49, 59, 74         |           | Positive Power Supply                                   |

| VSS      | 13, 30, 41, 50, 60,<br>75, 80 | Power pin | Negative Power Supply                                   |

| VDDBG    | 70                            | ·         | Positive Power Supply for Bus Guardian (connect to VDD) |

| VSSBG    | 73                            |           | Negative Power Supply for Bus Guardian (connect to VSS) |

Table 1. Pin Descriptions

| Pin Name       | Pin Number | Dir                                                 | Description                                                                                  |

|----------------|------------|-----------------------------------------------------|----------------------------------------------------------------------------------------------|

| RAM_CLK_TESTSE | 21         |                                                     | RAM_CLK when STEST=0 and USE_RAM_CLK=1, else Test Input, connect to VSS if not used          |

| STEST          | 22         | TTL Input with internal weak                        | Test Input, connect to VSS                                                                   |

| FTEST          | 24         | - pull-down                                         | Test Input, connect to VSS                                                                   |

| FIDIS          | 25         |                                                     | Test Input, connect to VSS                                                                   |

| TTEST          | 61         | TTL Input with internal weak pull-up                | Test Input, connect to VDD                                                                   |

| USE_RAM_CLK    | 34         | TTL Input with internal weak pull-down              | RAM_CLK Pin Enable, connect to VSS if not used                                               |

| XIN0           | 2          | Analog CMOS nin                                     | Main Clock: 40MHz external clock input                                                       |

| CTEST          | 3          | - Analog CMOS pin                                   | Test input, to be unconnected                                                                |

| OSCMODE        | 23         | TTL Input with internal weak pull-down              | Connect to VDD <sup>1</sup>                                                                  |

| XIN1           | 72         | Analog CMOS nin                                     | Bus Guardian Clock: Analog CMOS Oscillator Input, use as input when providing external clock |

| XOUT1          | 71         | - Analog CMOS pin                                   | Bus Guardian Clock: Analog CMOS Oscillator Output, leave open when providing external clock  |

| RESETB         | 26         | TTL Input with internal weak pull-up                | Main Reset Input, active low                                                                 |

| TxD0           | 5          | TTL output with internal weak pull-up at tristate   | TTP Bus Channel 0: Transmit Data                                                             |

| CTS0           | 6          | TTL output with internal weak pull-down at tristate | TTP Bus Channel 0: Transmit Enable                                                           |

| RxD0           | 11         | TTL Input with internal weak pull-up                | TTP Bus Channel 0: Receive Data                                                              |

| TxCLK0         | 7          | TTL Input with internal weak pull-down              | TTP Bus Channel 0: Transmit Clock (MII mode)                                                 |

| RxER0          | 8          | TTL Input with internal weak pull-up                | TTP Bus Channel 0: Receive Error (MII mode)                                                  |

| RxCLK0         | 9          | TTL Input with internal weak pull-down              | TTP Bus Channel 0: Receive Clock (MII mode)                                                  |

| RxDV0          | 10         | TTL Input with internal weak pull-up                | TTP Bus Channel 0: Receive Data Valid (MII mode)                                             |

| TxD1           | 14         | TTL output with internal weak pull-up at tristate   | TTP Bus Channel 1: Transmit Data                                                             |

| CTS1           | 15         | TTL output with internal weak pull-down at tristate | TTP Bus Channel 1: Transmit Enable                                                           |

| RxD1           | 20         | TTL Input with internal weak pull-up                | TTP Bus Channel 1: Receive Data                                                              |

| TxCLK1         | 16         | TTL Input with internal weak pull-down              | TTP Bus Channel 1: Transmit Clock (MII mode)                                                 |

| RXER1          | 17         | TTL Input with internal weak pull-up                | TTP Bus Channel 1: Receive Error (MII mode)                                                  |

| RXCLK1         | 18         | TTL Input with internal weak pull-down              | TTP Bus Channel 1: Receive Clock (MII mode)                                                  |

| RxDV1          | 19         | TTL Input with internal weak pull-up                | TTP Bus Channel 1: Receive Data Valid (MII mode)                                             |

Table 1. Pin Descriptions

| Pin Name | Pin Number   | Dir                                                                                    | Description                                                                      |  |  |

|----------|--------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--|--|

| A[11:0]  | 48-42, 39-35 | TTL Input                                                                              | Host Interface (CNI) Address Bus <sup>2</sup>                                    |  |  |

| D[15:0]  | 69-62, 58-51 | TTL input/output with tristate                                                         | Host Interface (CNI) Data Bus, tristate                                          |  |  |

| CEB      | 76           |                                                                                        | Host Interface (CNI) chip enable, active low                                     |  |  |

| OEB      | 77           | 77 TTL Input with internal weak pull-up Host interface (CNI) output enable, active low |                                                                                  |  |  |

| WEB      | 78           | Fam ap                                                                                 | Host interface (CNI) write enable, active low                                    |  |  |

| READYB   | 79           | TTL output with internal weak                                                          | Host interface (CNI) transfer finish signal, active low, open drain <sup>3</sup> |  |  |

| INTB     | 28           | pull-up at tristate                                                                    | Host interface (CNI) time signal (interrupt), active low, open drain             |  |  |

| LED[2:0] | 33-31        | TTL output with internal weak pull-down at tristate                                    | Configurable generic output port                                                 |  |  |

| NC       | 1, 27, 40    |                                                                                        | Not connected, leave open                                                        |  |  |

- 1. This pin selects a clock multiplier of 1. This is the only supported operation mode.

- 2. The device is addressed at 16-bit data word boundaries. If the device is connected to a CPU with a byte-granular address bus, remember that A[11:0] of the AS8202B device has to be connected to A[12:1] of the CPU (considering a little endian CPU address bus)

- 3. At de-assertion READYB is driven to the inactive value (high) for a configurable time.

### 5 Absolute Maximum Ratings

Stresses beyond those listed in Table 2 may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated in Electrical Characteristics on page 7 is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Table 2. Absolute Maximum Ratings

| Symbol            | Parameter                     | Min      | Max     | Unit | Notes                                                                                                                                                                                                                                                                              |

|-------------------|-------------------------------|----------|---------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Electrical Para   | ameters                       | <u> </u> |         |      |                                                                                                                                                                                                                                                                                    |

| VDD               | DC Supply voltage             | -0.3     | 5.0     | V    |                                                                                                                                                                                                                                                                                    |

| Vin               | Input voltage                 | -0.3     | VDD+0.3 | V    | any pin                                                                                                                                                                                                                                                                            |

| lin               | Input current                 | -100     | 100     | mA   | any pin, T <sub>AMB</sub> =25°C                                                                                                                                                                                                                                                    |

| Electrostatic E   | Discharge                     |          | 1       |      |                                                                                                                                                                                                                                                                                    |

| ESD               | Electrostatic discharge       | 1000     |         | V    | HBM: 1KV Mil.std.883, Method 3015.7                                                                                                                                                                                                                                                |

| Temperature F     | Ranges and Storage Conditions | -        |         |      |                                                                                                                                                                                                                                                                                    |

| T <sub>STRG</sub> | Storage temperature           | -55      | +150    | °C   |                                                                                                                                                                                                                                                                                    |

| T <sub>BODY</sub> | Package body temperature      |          | 260     | °C   | The reflow peak soldering temperature (body temperature) specified is in accordance with IPC/JEDEC J-STD-020 "Moisture/Reflow Sensitivity Classification for Non-Hermetic Solid State Surface Mount Devices".  The lead finish for Pb-free leaded packages is matte tin (100% Sn). |

| Н                 | Humidity non-condensing       | 5        | 85      | %    |                                                                                                                                                                                                                                                                                    |

| MSL               | Moisture sensitivity level    |          | 3       |      | Represents a maximum floor life time of 168h                                                                                                                                                                                                                                       |

### **6 Electrical Characteristics**

TAMB = -40 to +125 °C, VDD = 3V to +3.6V,  $V_{SS}$  = 0V unless otherwise specified.

Table 3. Electrical Characteristics

| Symbol                                 | Parameter                                       | Conditions                                                                                             |                      | Min                   | Тур              | Max             | Unit |

|----------------------------------------|-------------------------------------------------|--------------------------------------------------------------------------------------------------------|----------------------|-----------------------|------------------|-----------------|------|

| Operating Condi                        | tions                                           |                                                                                                        |                      | •                     |                  | "               |      |

| I <sub>DDs</sub>                       | Static Supply Current                           | All inputs tied to VDD/V <sub>SS</sub> , clocks stopped, exclusive of I/O drive requirements, VDD=3.6V |                      | 5                     |                  | 900             | μΑ   |

| I <sub>DD</sub>                        | Operating Supply Current (see note 1)           | VDD=3.3V, exclusive of I/O drive requirements                                                          |                      |                       |                  | 100             | mA   |

| CLK1                                   | Clock Period of Bus Guardian Clock (see note 1) |                                                                                                        |                      |                       | 62.5             |                 | ns   |

| TTL Input Pins a                       | nd TTL Bidirectional Pins in Input/Tr           | state Model                                                                                            |                      | ,                     |                  | 1               |      |

| V <sub>IL</sub>                        | Input Low Voltage                               |                                                                                                        |                      |                       |                  | 0.8             | V    |

| V <sub>IH</sub>                        | Input High Voltage                              |                                                                                                        |                      | 2.0                   |                  |                 | V    |

| I <sub>INleak</sub>                    | Input Leakage Current                           | Pins without pad<br>VDD=3.6                                                                            | resistors,<br>V      | -1                    |                  | 1               | μΑ   |

|                                        |                                                 | Pins with pull-down                                                                                    | VIN=0.4V             | 4.9<br>(see note 2)   |                  |                 |      |

| $I_{\rm IL}$                           | Input Low Current                               | resistors, VDD=3.0V                                                                                    | VIN=0.8V             | 8.8<br>(see note 2)   |                  |                 | μΑ   |

|                                        |                                                 | Pins with pull-up resistors                                                                            | VDD=3.6V<br>VIN=0V   | -15                   |                  | -75             |      |

|                                        |                                                 | Pins with pull-down resistors                                                                          | VDD=3.6V<br>VIN=3.6V | 15                    |                  | 75              |      |

| I <sub>IH</sub>                        | Input High Current                              | Pins with pull-up                                                                                      | VIN=2.0V             | -10.7<br>(see note 2) |                  |                 | μΑ   |

|                                        |                                                 | resistors, VDD=3.0V                                                                                    | VIN=2.5V             | -6 (see note 2)       |                  |                 |      |

| C <sub>IN</sub>                        | Input Capacitance                               |                                                                                                        |                      |                       | 4.5 (see note 2) |                 | pF   |

| RxD Pin                                |                                                 |                                                                                                        | -                    |                       |                  |                 |      |

| t <sub>ASYM_Rx</sub><br>t(VIN=0.5*VDD) | Asymmetric Receiver Delay RxD                   | T=125°C, VDD=3.0V,<br>C <sub>LOAD</sub> =35pF                                                          | RxD[1,0]             | -2 (see note 3)       |                  | 2 (see note 3)  | ns   |

| CMOS Inputs (XI                        | N), drive from external clock generator         |                                                                                                        |                      |                       |                  |                 |      |

| Drive at XIN                           |                                                 |                                                                                                        |                      |                       |                  |                 |      |

| C <sub>XIN</sub>                       | Input Capacitance                               |                                                                                                        |                      |                       | 1.9              | 2.5             | pF   |

| I <sub>XIN</sub>                       | Input Current                                   |                                                                                                        |                      |                       |                  | ±1 (see note 3) | μΑ   |

| V <sub>IL_XIN</sub>                    | Input Low Voltage                               |                                                                                                        |                      | 0                     |                  | 0.3* VDD        | V    |

| $V_{IH\_XIN}$                          | Input High Voltage                              |                                                                                                        |                      | 0.7* VDD              |                  | VDD             | V    |

| Outputs and TTL                        | Bi-directional Pins in Output Mode              |                                                                                                        |                      |                       |                  |                 |      |

| I <sub>OL</sub>                        | Output Low Current                              | VDD=3.0V, Vo                                                                                           | = 0.4V               |                       |                  | -4              | mA   |

| I <sub>OH</sub>                        | Output High Current                             | VDD=3.0V, Vo                                                                                           | = 2.5V               |                       |                  | 4               | mA   |

Table 3. Electrical Characteristics

| Symbol                                                        | Parameter                   | Conditions                                          |                                | Min                | Тур | Max                 | Unit |

|---------------------------------------------------------------|-----------------------------|-----------------------------------------------------|--------------------------------|--------------------|-----|---------------------|------|

| loz                                                           | Output Tristate Current     | VDD=3.                                              | 6V                             |                    |     | ±10 (see note 3)    | μΑ   |

| t <sub>RISE</sub><br>t(Vout=0.1*VDD)                          | Transition Time – Rise      | T = 125 °C,<br>VDD=3.0V,                            | CTS[1,0],<br>LED[2:0],<br>INTB |                    |     | 8.1<br>(see note 2) | ns   |

| to<br>t(Vout=0.9*Vdd)                                         |                             | C <sub>LOAD</sub> =35pF                             | D[15:0],<br>READYB             |                    |     | 8.9<br>(see note 2) |      |

| t <sub>FALL</sub><br>t(Vout=0.9*Vdd)                          | Transition Time – Fall      | T = 125 °C,<br>VDD=3.0V,                            | CTS[1,0],<br>LED[2:0],<br>INTB |                    |     | 6 (see note 2)      | ns   |

| to<br>t(Vout=0.1*VDD)                                         |                             | C <sub>LOAD</sub> =35pF                             | D[15:0],<br>READYB             |                    |     | 7 (see note 2)      |      |

| TxD Pins                                                      |                             |                                                     |                                |                    |     |                     |      |

| t <sub>RISE</sub><br>t(Vout=0.3*Vdd)<br>to<br>t(Vout=0.7*Vdd) | Transition Time – Rise TxD  | T = 125 °C,<br>VDD=3.0V,<br>C <sub>LOAD</sub> =35pF | TxD[1,0]                       |                    |     | 4.5 (see note 3)    | ns   |

| t <sub>FALL</sub> t(Vout=0.7*Vdd) to t(Vout=0.3*Vdd)          | Transition Time – Fall TxD  | T = 125 °C,<br>VDD=3.0V,<br>C <sub>LOAD</sub> =35pF | TxD[1,0]                       |                    |     | 3 (see note 3)      | ns   |

| tasym_rx<br>t(Vout=0.5*Vdd)                                   | Asymmetric Driver Delay TxD | T = 125 °C,<br>VDD=3.0V,<br>C <sub>LOAD</sub> =35pF | TxD[1,0]                       | -3<br>(see note 3) |     | 3 (see note 3)      | ns   |

#### Notes:

- 1. Typical values: CLK0=40 MHz (duty cycle 45-55%), CLK1=16 MHz.

- 2. Implicitly tested.

- 3. Guaranteed by design; not tested during production.

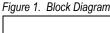

### 7 Detailed Description

The AS8202B is the first TTP controller to support both MFM and Manchester coding. Manchester coding is important for DC-free data transmission, which allows the use of transformers in the data stream. The AS8202B is pin-compatible with its predecessor, the AS8202. The AS8202B provides support for fault-tolerant, high-speed bus systems in a single device. The communication controller is qualified for the full temperature range required for automotive applications and is certifiable according to RTCA standards. It offers superior reliability and supports data transfer rates of 25 Mbit/s with MII and up to 4 Mbit/s with MFM/Manchester.

The CNI (communication network interface) forms a temporal firewall. It de-couples the controller network from the host subsystem by use of a dual ported RAM (CNI). This prevents the propagation of control errors. The interface to the host CPU is implemented as a 16-bit wide non-multiplexed asynchronous bus interface.

The TTP follows a conflict-free media access strategy called time division multiple access (TDMA). This means, TTP deploys a time slot technique based on a global time that is permanently synchronized. Each node is assigned a time slot in which it is allowed to perform transmit operation. The sequence of time slots is called TDMA round, a set of TDMA rounds forms a cluster cycle. The operation of the network is repeated after one cluster cycle. The sequence of interactions forming the cluster cycle is defined in a static time schedule, called message descriptor list (MEDL). The definition of the MEDL in conjunction with the global time determines the response time for a service request.

The membership of all nodes in the network is evaluated by the communications controller. This information is presented to all correct cluster members in a consistent fashion. During operation, the status of all other nodes is propagated within one TDMA round. Please read more about TTP and request the TTP specification at www.tttech.com.

#### 7.1 Host CPU Interface

The host CPU interface, also referred to as CNI (Communication Network Interface), connects the application circuitry to the AS8202B TTP controller. All related signal pins provide an asynchronous read/write access to a dual ported RAM located in the AS8202B. There are no setup/hold constraints referring to the microtick (main clock "CLK0").

All accesses have to be executed on a granularity of 16-bit (2 byte), the device does not support byte-wide accesses. The pin A0 (LSB) of the device differentiates even and odd 16-bit word addresses and is typically connected to A1 of a little-endian host CPU. The A0 of host CPU is not connected to the device, and the application/driver on the host CPU should force all accesses to be 16-bit. For efficiency reasons, the host CPU application/driver may access some memory locations of the AS8202B using wider accesses (e.g. 32-bit), and the bus interface of the host CPU will automatically split the access into two consecutive 16-bit wide accesses to the TTP controller. Note that particularly in such a setup all timing parameters of the host CPU interface must be met, especially the inactivity timeouts described as symbols 16–19.

The host interface features an interrupt or time signal INTB to notify the application circuitry of programmed and protocol-specific, synchronous and asynchronous events.

The host CPU interface allows access to the internal instruction code memory. This is required for proper loading of the protocol execution code into the internal instruction code RAM, for extensive testing of the instruction code RAM and for verifying the instruction code ROM contents.

**INTB** is an open-drain output, i.e. the output is only driven to '0' and is weak-pull-up at any other time, so external pull-up resistors or transistors may be necessary depending on the application.

**READYB** is also an open-drain output, but with a possibility to be driven to '1' for a defined time (selectable by register) before weak-pull-up at any other time.

The LED port is software-configurable to automatically show some protocol-related states and events, see below for the LED port configuration.

Table 4. Host Interface Ports

| Pin Name       | Mode             | Width | Comment                                |  |  |

|----------------|------------------|-------|----------------------------------------|--|--|

| A[11:0]        | in               | 12    | CNI address bus, 12-bit (A0 is LSB)    |  |  |

| D[15:0]        | inout (tri)      | 16    | CNI data bus, 16-bit (D0 is LSB)       |  |  |

| CEB            | in               | 1     | CNI chip enable, active low            |  |  |

| WEB            | in               | 1     | CNI write enable, active low           |  |  |

| OEB            | In               | 1     | CNI output enable, active low          |  |  |

| READYB         | out (open drain) | 1     | CNI ready, active low                  |  |  |

| INTB           | out (open drain) | 1     | CNI interrupt, time signal, active low |  |  |

| RAM_CLK_TESTSE | in               | 1     | HOST clock                             |  |  |

| USE_RAM_CLK    | in               | 1     | HOST clock pin enable                  |  |  |

**Asynchronous READYB** permits the shortest possible bus cycle but eventually requires signal synchronization in the application. Connect USE\_RAM\_CLK to VSS to enable this mode of operation.

**Synchronous READYB** uses an external clock (usually the host processor's bus clock) for synchronization of the signal, eliminating external synchronization logic. Connect USE\_RAM\_CLK to VDD and RAM\_CLK\_TESTSE to the host processor's bus clock to enable this mode of operation.

**Note:** Due to possible metastability occurrence, it is not recommended to be used in safety critical systems.

Table 5. Asynchronous DPRAM Interface

| Symbol | Parameter                                                          | Condition        | ns                | Min                  | Тур | Max  | Units |

|--------|--------------------------------------------------------------------|------------------|-------------------|----------------------|-----|------|-------|

| Tc     | Controller Cycle Time                                              |                  |                   |                      | 25  |      | ns    |

| 1a     | Input Valid to CED, WED (Catus Time)                               | A[11:0]          |                   | E                    |     |      |       |

| 2a     | Input Valid to CEB, WEB (Setup Time)                               | D[15:0]          |                   | 5                    |     |      | ns    |

| 1b     | CEB, WEB to Input Invalid (Hold Time)                              | A[11:0]          |                   | 3                    |     |      | no    |

| 2b     | - CEB, WEB to Imput Invalid (Floid Tillie)                         | D[15:0]          |                   | 4                    |     |      | ns    |

| 3      | Input Rising to CEB, WEB Falling                                   | CEB, WEB,        | OEB               | 5 (see note 1)       |     |      | ns    |

| 4      | CEB, WEB Rising to Input Falling                                   | CEB, WEB,        | OEB               | 5<br>(see note 1,2)  |     |      | ns    |

| 5      | Write Access Time (CEB, WEB to READYB)                             | Min = 1 Tc, Ma   | x = 4 Tc          | 25                   |     | 100  | ns    |

| 6      | CEB, WEB de-asserted to READYB de-asserted                         |                  |                   |                      |     | 9.4  | ns    |

| 7a     | Input Valid to CEB, OEB (Setup Time)                               | A[11:0]          |                   | 5                    |     |      | ns    |

| 7b     | CEB, OEB to Input Invalid (Hold Time)                              | A[11:0]          |                   | 2                    |     |      | ns    |

| 8      | Input Rising to CEB, OEB Falling                                   | CEB, WEB,        | OEB               | 5 (see note 1)       |     |      | ns    |

| 9      | CEB, OEB Rising to Input Falling                                   | CEB, WEB,        | OEB               | 5 (see note 1)       |     |      | ns    |

| 10     | Read Access Time (CEB, OEB to READYB)                              | Min = 1.5 Tc, Ma | ax = 8 Tc         | 37.5                 |     | 200  | ns    |

| 11a    | CEB, OEB asserted to signal asserted                               | D[15:0]          |                   | 4.0                  |     | 8.4  | ns    |

| 11b    | CEB, OEB de-asserted to signal de-                                 | D[15:0]          |                   | 3.8                  |     | 8    | 20    |

| 11c    | asserted                                                           | READYI           | 3                 |                      |     | 8.8  | ns    |

| 12     | READYB, D skew                                                     |                  |                   |                      |     | ±2   | ns    |

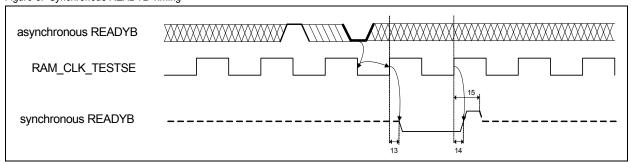

| 13     | RAM_CLK_TESTSE Rising to READYB Falling                            | USE_RAM_C        | CLK=1             | 3.7                  |     | 13.5 | ns    |

| 14     | RAM_CLK_TESTSE Rising to READYB Rising                             | USE_RAM_C        | CLK=1             | 3                    |     | 9.7  | ns    |

|        |                                                                    |                  | Ready<br>delay=00 | 3.6                  |     | 12.9 |       |

| 15     | RAM_CLK_TESTSE Rising to                                           | USE_RAM_CLK      | Ready<br>delay=01 | 4.5                  |     | 15.4 | 200   |

| 15     | READYB Deactivated 1->Z                                            | =1               | Ready<br>delay=10 | 5.4                  |     | 18.8 | ns    |

|        |                                                                    |                  | Ready<br>delay=11 | 6.4                  |     | 22.2 |       |

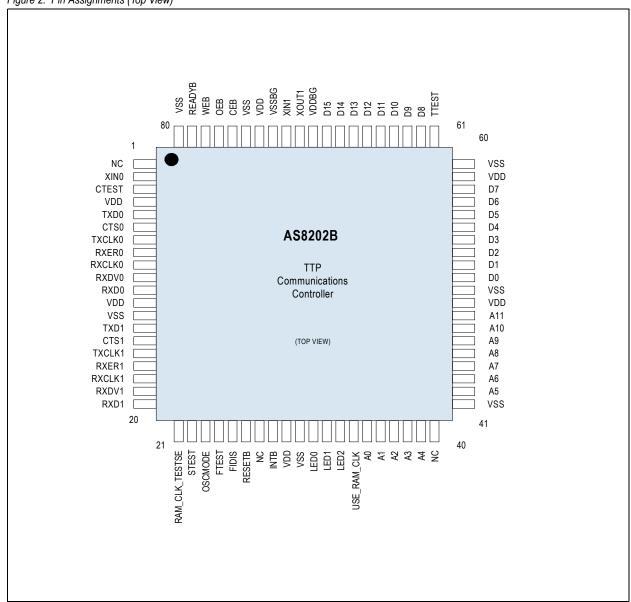

| 16     | Read to Read Access Inactivity Time (CEB, OEB low to CEB, OEB low) | Min = 1.5        | Tc                | 37.5<br>(see note 1) |     |      | ns    |

Table 5. Asynchronous DPRAM Interface

| Symbol | Parameter                                                            | Conditions | Min                 | Тур | Max | Units |

|--------|----------------------------------------------------------------------|------------|---------------------|-----|-----|-------|

| 17     | Read to Write Access Inactivity Time (CEB, OEB low to CEB, WEB low)  |            | 5 (see note 1)      |     |     | ns    |

| 18     | Write to Write Access Inactivity Time (CEB, WEB low to CEB, WEB low) |            | 5<br>(see note 1,2) |     |     | ns    |

| 19     | Write to Read Access Inactivity Time (CEB, WEB low to CEB, OEB low)  |            | 5<br>(see note 1,2) |     |     | ns    |

#### Notes:

- 1. Prior to starting a read or write access, CEB, WEB and OEB have to be stable for at least 5 ns (see symbol 3, 4, 8, 9). In addition the designer has to consider the minimum inactivity time according to symbols 16, 17, 18, 19. For more information on the inactivity times (see Figure 3).

- 2. To allow proper internal initialization, after finishing any write access (CEB or WEB is high) to the internal CONTROLLER\_ON register, CEB OEB and WEB have to be stable high within 200 ns (min = 8 Tc).

- 3. All values not tested during production, guaranteed by design.

Figure 3. Read/Write Access Inactivity Time

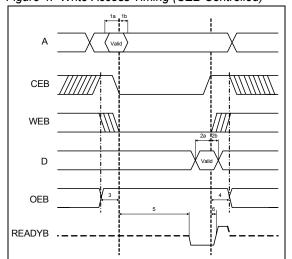

Figure 4. Write Access Timing (CEB Controlled)

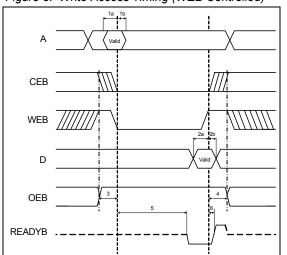

Figure 5. Write Access Timing (WEB Controlled)

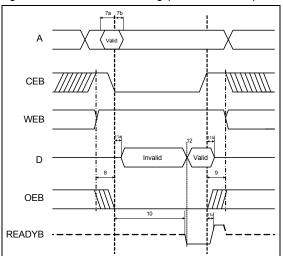

Figure 6. Read Access Timing (CEB Controlled)

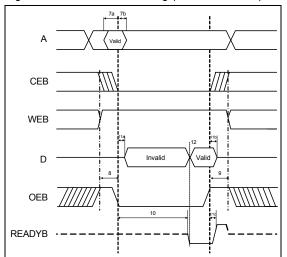

Figure 7. Read Access Timing (OEB Controlled)

#### 7.1.1 Synchronous READYB Generation

Figure 8. Synchronous READYB Timing

Synchronous READYB is aligned to host clock (with pulse duration of one host clock cycle) to fulfill the required host timing constraints for input setup and input hold time to/after host clock rising edge.

**Note:** Connect USE\_RAM\_CLK to VDD and RAM\_CLK\_TESTSE to the host processor's bus clock to enable this mode of operation. Due to possible metastability occurrence, it is not recommended to be used in safety critical systems.

#### 7.2 Reset and Oscillator

Table 6. Pin Mode

| Pin Name | Mode   | Comment                                              |

|----------|--------|------------------------------------------------------|

| XIN1     | analog | Bus guardian oscillator input (external clock input) |

| RESETB   | in     | External reset                                       |

#### 7.2.1 External Reset Signal

To issue a reset of the chip the RESETB port has to be driven low for at least 1µs. Pulses under 50ns duration are discarded. At power-up the reset must overlap the build-up time of the power supply. This reset may only be used if a proper power-on reset can be ensured (refer to Section 7.2.2 Integrated Power-On Reset).

#### 7.2.2 Integrated Power-On Reset

The device has an internal Power-On-Reset generator. When supply voltage ramps up, the internal reset signal is kept active (low) for 33µs typical.

Table 7. Parameters

| Symbol | Parameter                                   | Min | Тур | Max | Unit |

|--------|---------------------------------------------|-----|-----|-----|------|

| dV/dt  | supply voltage slope                        | 551 | -   | -   | V/ms |

| tpores | power on reset active time after VDD > 1,0V | 25  | 33  | 49  | μs   |

Note: In case of non-compliance keep the external reset (RESETB) active for min. 5 ms after supply voltage is valid and main clock is stable.

#### 7.2.3 Oscillator Circuitry

The main clock requires an external oscillator. The bus guardian requires an external oscillator or an external quartz.

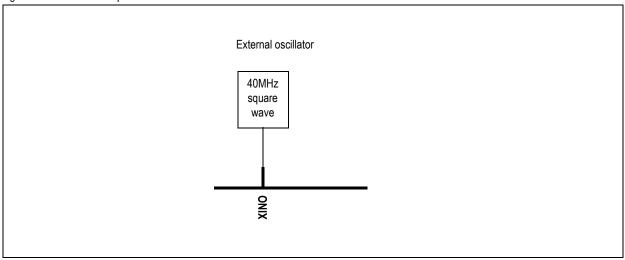

Figure 9. Main Clock Setup

XINO of the main clock shall be supplied by a 40MHz clock provided by an oscillator IC.

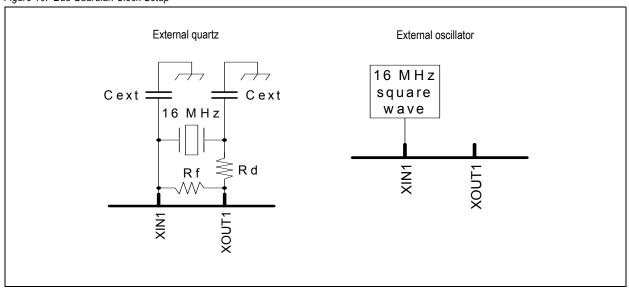

Figure 10. Bus Guardian Clock Setup

The bus guardian clock (XIN1/XOUT1) supports driving a quartz crystal oscillation, as well as a clock input by an external oscillator.

#### 7.2.4 Built-in Characteristics

Table 8. Characteristics

| Symbol        | Pin        | Parameter                                    | Min | Тур | Max | Unit | Note             |

|---------------|------------|----------------------------------------------|-----|-----|-----|------|------------------|

| Tosc_startup1 | XIN1/XOUT1 | Oscillator startup time (Bus Guardian clock) |     |     | 20  | ms   | Frequency: 16MHz |

#### 7.3 TTP Bus Interface

The AS8202B contains two TTP bus units, one for each TTP channel, building the TTP bus interface. Each TTP bus channel contains a transmitter and a receiver and can be configured to be either in the asynchronous or synchronous mode of operation. Note that the two channels (channel 0 and channel 1) can be configured independently for either of these modes.

The drivers of the TxD and CTS pins are actively driven only during a transmission window, all the other time the drivers are switched off and the weak pull resistors are active. External pull resistors must be used to define the signal levels during idle phases.

**Note:** The transmission window may be different for each channel.

Table 9. Bus Interface Connections

| Pin Name | Tx inactive    |  |

|----------|----------------|--|

| TxD[0]   | weak pull-up   |  |

| CTS[0]   | weak pull-down |  |

| TxD[1]   | weak pull-up   |  |

| CTS[1]   | weak pull-down |  |

#### 7.4 TTP Asynchronous Bus Interface

When in asynchronous mode of operation the channel's bus unit uses a self-clocking transmission encoding which can be either MFM or Manchester at a maximum data rate of 4 Mbit/s on a shared media (physical bus). The pins can either be connected to drivers using recessive/dominant states on the wire as well as drivers using active push/pull functionality.

The RxD signal uses '1' as the inactivity level. In the so-called RS485 compatible mode longer periods of '0' are treated as inactivity. If the RS485 compatible mode is not used, the application must care to drive RxD to '1' during inactivity on the bus.

Table 10. Asynchronous Bus Interface Connections

| Pin Name | Mode | Connect to PHY | Note                         |  |

|----------|------|----------------|------------------------------|--|

| TxD[0]   | out  | TxD            | Transmit data channel 0      |  |

| CTS[0]   | out  | CTS            | Transmit enable channel 0    |  |

| TxCLK[0] | in   |                | No function (do not connect) |  |

| RXER[0]  | in   |                | No function (do not connect) |  |

| RXCLK[0] | in   |                | No function (do not connect) |  |

| RxDV[0]  | in   |                | No function (do not connect) |  |

| RxD[0]   | in   | RxD            | Receive data channel 0       |  |

| TxD[1]   | out  | TxD            | Transmit data channel 1      |  |

| CTS[1]   | out  | CTS            | Transmit enable channel 1    |  |

| TxCLK[1] | in   |                | No function (do not connect) |  |

| RXER[1]  | in   |                | No function (do not connect) |  |

| RXCLK[1] | in   |                | No function (do not connect) |  |

| RxDV[1]  | in   |                | No function (do not connect) |  |

| RxD[1]   | in   | RxD            | Receive data channel 1       |  |

#### 7.5 TTP Synchronous Bus Interface

When in synchronous mode of operation, the bus unit uses a synchronous transfer method to transfer data at a rate between 20 and 25 Mbit/s. The interface is designed to run at 25 Mbit/s and to be fully compatible with the commercial 100 Mbit/s Ethernet MII (Media Independent Interface) according to IEEE standard 802.3 (Ethernet CSMA/CD).

Connecting the synchronous TTP bus unit to a 100 Mbit/s Ethernet PHY is done by connecting TxD, CTS, TxCLK, RXER, RXCLK, RxDV and RxD of any channel to TxD0TxD0, TxEN, TxCLK, RXER, RXCLK, RxDV and RxD0 of the PHY's MII. The pins TxD1, TxD2 and TxD3 of the PHY's MII should be linked to VSS. The signals RxD1, RxD2, RxD3, COL and CRS as well as the MMII (Management Interface) should be left open or can be used for diagnostic purposes by the application.

Note that the frames sent by the AS8202B are not Ethernet compatible and that an Ethernet Hub (not a Switch) can be used as a 'star coupler' for proper operation. Also note that the Ethernet PHY must be configured for Full Duplex operation (even though the Hub does not support full duplex), because TTP has its own collision management that should not interfere with the PHY's Half-Duplex collision management. In general, the PHY must not be configured for automatic configuration ('Auto negotiation') but be hard-configured for 100 Mbit/s, Full Duplex operation.

Note: To run the interface at a rate other than 25 Mbit/s other transceiver PHY components have to be used.

Table 11. Synchronous Bus Interface Connections

| Pin Name | Pin Name Mode Conne |          | Note                         |  |

|----------|---------------------|----------|------------------------------|--|

| TxD[0]   | out                 | TxD0TxD0 | Transmit data channel 0      |  |

| CTS[0]   | out                 | TxEN     | Transmit enable channel 0    |  |

| TxCLK[0] | in                  | TxCLK    | Transmit clock channel 0     |  |

| RXER[0]  | in                  | RXER     | Receive error channel 0      |  |

| RXCLK[0] | in                  | RXCLK    | Receive clock channel 0      |  |

| RxDV[0]  | RxDV[0] in RxDV     |          | Receive data valid channel 0 |  |

Table 11. Synchronous Bus Interface Connections

| Pin Name       | Mode     | Connect to PHY | Note                         |  |  |

|----------------|----------|----------------|------------------------------|--|--|

| RxD[0]         | in       | RxD0           | Receive data channel 0       |  |  |

| TxD[1]         | out      | TxD0           | Transmit data channel 1      |  |  |

| CTS[1]         | out TxEN |                | Transmit enable channel 1    |  |  |

| TxCLK[1]       | in TxCLK |                | Transmit clock channel 1     |  |  |

| RXER[1]        | in       | RXER           | Receive error channel 1      |  |  |

| RXCLK[1]       | in       | RXCLK          | Receive clock channel 1      |  |  |

| RxDV[1]        | in       | RxDV           | Receive data valid channel 1 |  |  |

| RxD[1] in RxD0 |          | RxD0           | Receive data channel 1       |  |  |

#### 7.6 Test Interface

The Test Interface supports the manufacturing test and characterization of the chip. In the application environment test pins have to be connected as following:

- STEST, FTEST, FIDIS: connect to VSS

- TTEST: connect to VDD

Caution: Any other connection of these pins may cause permanent damage to the device and to additional devices of the application.

#### 7.7 LED Signals

The LED port consists of three pins. Via the MEDL each of these pins can be independently configured for any of the three modes of operation. At Power-Up and after Reset the LED port is inactive and only weak pull-down resistors are connected. After the controller is switched on by the host and when it is processing its initialization, the LED port is initialized to the selected mode of operation.

Table 12. LED Signals

| Pin Name | Protocol Mode                                         | Timing Mode                | Bus Guardian Mode        |  |

|----------|-------------------------------------------------------|----------------------------|--------------------------|--|

| LED2     | RPV <sup>1</sup> or<br>Protocol activity <sup>7</sup> | Time Overflow <sup>2</sup> | Action Time <sup>3</sup> |  |

| LED1     | Sync Valid <sup>4</sup>                               | Time Tick <sup>2</sup>     | BDE1 <sup>5</sup>        |  |

| LED0     | Protocol activity <sup>6</sup> or RPV <sup>7</sup>    | Microtick <sup>8</sup>     | BDE0 <sup>5</sup>        |  |

- 1. RPV is Remote Pin Voting. RPV is a network-wide agreed signal used typically for agreed power-up or power-down of the application's external drivers.

- 2. Time Overflow is active for one clock cycle at the event of an overflow of the internal 16-bit time counter. Time Tick is active for one clock cycle when the internal time is counted up. Time Overflow and Time Tick can be used to externally clone the internal time control unit (TCU). With this information the application can precisely sample and trigger events, for example.

- 3. Action Time signals the start of a bus access cycle.

- 4. The controller sets this output when cluster synchronization is achieved (after integration from the LISTEN state, after acknowledge in the COLDSTART state).

- 5. BDE0 and BDE1 show the Bus Guardian's activity, '1' signals an activated transmitter gate on the respective channel.

- Protocol activity is typically connected to an optical LED. The flashing frequency and rhythm give a simple view to the internal TTP protocol state.

- 7. LED2's RPV mode and LED0's Protocol activity mode can be swapped with a MEDL parameter.

- 8. Microtick is the internal main clock signal.

Each LED pin can be configured to be either a push/pull driver (drives both LOW and HIGH) or to be only an open-drain output (drives only LOW).

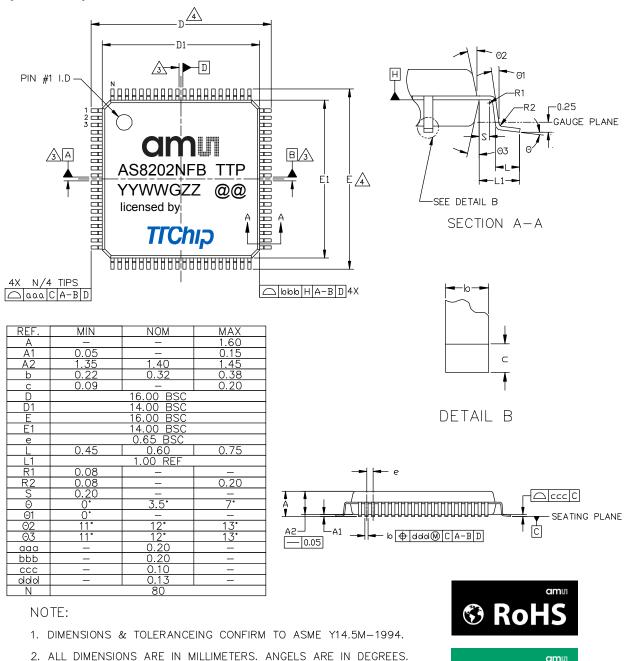

### 8 Package Drawings and Markings

The product is available in a 80-pin LQFP package.

Figure 11. Drawings and Dimensions

### Marking: YYWWGZZ.

| YY                 | ww                 | G                | ZZ                | @@                |

|--------------------|--------------------|------------------|-------------------|-------------------|

| Manufacturing year | Manufacturing week | Plant identifier | Traceability code | Sublot identifier |

**③** Green

3 DATUMS A-B AND D TO BE DETERMINED AT DATUM PLANE H.

1 TO BE DETERMINED AT SEATING DATUM PLANE C.

### **Revision History**

| Revision | Date         | Owner | Description          |

|----------|--------------|-------|----------------------|

| 1.0      | 26 Mar, 2013 | hgl   | Release of datasheet |

|          |              |       |                      |

**Note:** Typos may not be explicitly mentioned under revision history.

## 9 Ordering Information

Table 13. Ordering Information

| Ordering Code | Marking   | Description                  | Delivery Form | Package     |

|---------------|-----------|------------------------------|---------------|-------------|

| AS8202B-ALQR  | AS8202NFB | TTP communication controller | Tray          | 80-pin LQFP |

Note: All products are RoHS compliant and ams green

Technical Support is available at www.ams.com/Technical-Support

For further information and requests, email us at sales@ams.com (or) find your local distributor at www.ams.com/distributor

#### Copyrights

Copyright © 1997-2013, ams AG, Tobelbaderstrasse 30, 8141 Unterpremstaetten, Austria-Europe. Trademarks Registered ®. All rights reserved. The material herein may not be reproduced, adapted, merged, translated, stored, or used without the prior written consent of the copyright owner.

All products and companies mentioned are trademarks or registered trademarks of their respective companies.

#### Disclaimer

Devices sold by ams AG are covered by the warranty and patent indemnification provisions appearing in its Term of Sale. ams AG makes no warranty, express, statutory, implied, or by description regarding the information set forth herein or regarding the freedom of the described devices from patent infringement. ams AG reserves the right to change specifications and prices at any time and without notice. Therefore, prior to designing this product into a system, it is necessary to check with ams AG for current information. This product is intended for use in normal commercial applications. Applications requiring extended temperature range, unusual environmental requirements, or high reliability applications, such as military, medical life-support or life-sustaining equipment are specifically not recommended without additional processing by ams AG for each application. For shipments of less than 100 parts the manufacturing flow might show deviations from the standard production flow, such as test flow or test location.

The information furnished here by ams AG is believed to be correct and accurate. However, ams AG shall not be liable to recipient or any third party for any damages, including but not limited to personal injury, property damage, loss of profits, loss of use, interruption of business or indirect, special, incidental or consequential damages, of any kind, in connection with or arising out of the furnishing, performance or use of the technical data herein. No obligation or liability to recipient or any third party shall arise or flow out of ams AG rendering of technical or other services.

Contact Information

#### Headquarters

ams AG Tobelbaderstrasse 30 A-8141 Unterpremstaetten, Austria

Tel : +43 (0) 3136 500 0 Fax : +43 (0) 3136 525 01

For Sales Offices, Distributors and Representatives, please visit:

http://www.ams.com/contact

Contact Information

#### Headquarters

TTTech Computertechnik AG. Schoenbrunner Strasse 7 A-1040 Vienna, Austria

Tel : +43 (1) 5853 434 0 Fax : +43 (1) 5853 434 90

support@tttech.com www.tttech.com