TT5665

## 8-CHANNEL ADPCM VOICE SYNTEHSIS LSI

#### **GENERAL DESCRIPTION**

The TT5665 is a 8-channel mixing ADPCM voice synthesis LSI which offers R & L sound outputs with 4 channels for each. The TT5665 can access an external voice data ROM for sound effects or speech voice. The maximum external ROM size is 16M\*8 bit and can direct access. The TT5665 has an 8-channel synthesis stage which allows the simultaneous playback of eight different channels. It is used to have a voice with BGM (Back Ground Music) effect, instrumental sound, echo effect etc.

#### **FEATURES**

- Advance ADPCM algorithm

- Number of bits/sample: 4

- 24 address lines for external ROM

- 8-bit control bus for mode setting

- External memory capacity 128Mbit

- Interface with common CPU and MPU

- Clock frequency with Sampling frequency: (clock 1 MHz to 4 MHz)

- At 1.088 MHz clock

DAOR: 8 kHz and 6.4 kHz

DAOL: 8 kHz, 4 kHz, and 6.4 kHz, 3.2 kHz

• At 2.176 MHz clock

DAOR: 16 kHz and 12.8 kHz

DAOL: 16 kHz, 8 kHz, 4 kHz and 12.8 kHz, 6.4 kHz

3.2 kHz

• At 4.352 MHz clock

DAOR: 32 kHz and 25.6 kHz

DAOL: 32 kHz, 16 kHz, 8 kHz, 4 kHz and 25.6 kHz, 12.8 kHz

6.4 kHz, 3.2 kHz

- Number of words: 511 maximum

- Vocalization time: 64 minutes maximum (at 8 kHz, sample rate)

- Sound output channel (DAOR/L with 4 channels for each)

- Built-in DA converter: 12-bit

- DAO output format: A-class

- Voice level attenuation: OdB~-24dB on each channel (9steps) with -3dB/step

- Advance low power CMOS process

- 5 V or 3.3 V single power supply

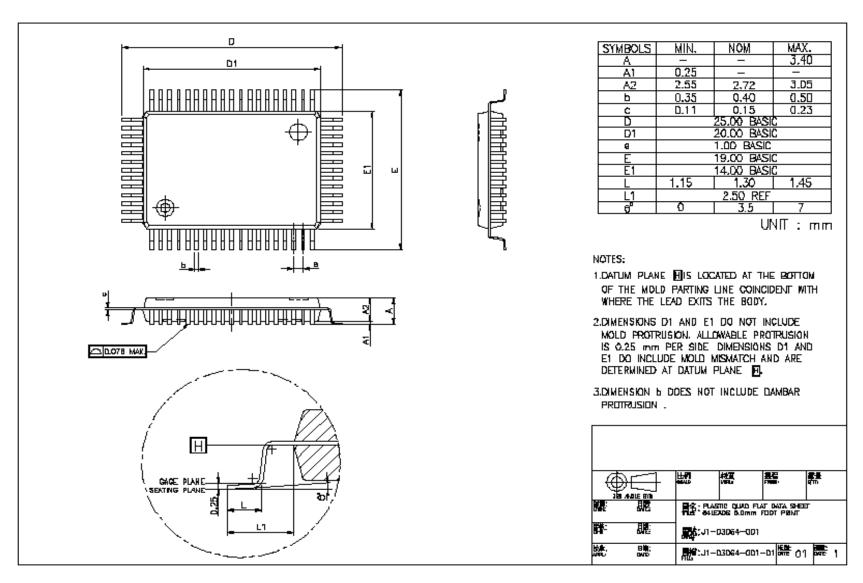

- 64-pin plastic QFP

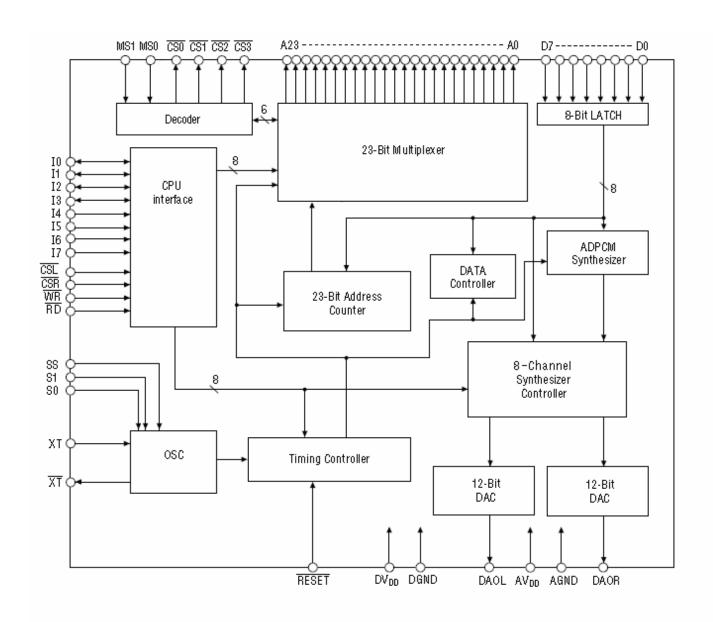

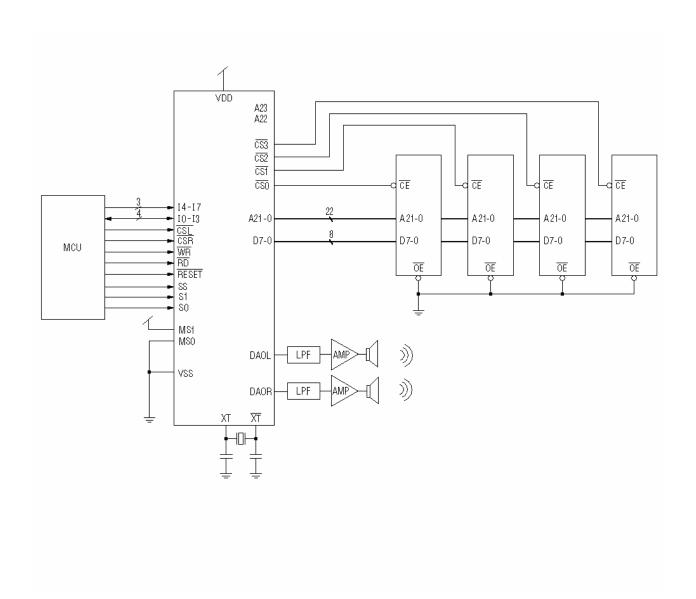

### **BLOCK DIAGRAM**

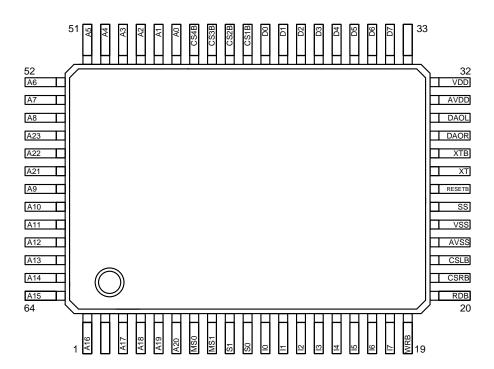

## PIN CONFIGURATION

## PIN DESCRIPTION

| Pin               | Pin            | I/O |                        |                                                                                                            |          |          | Fun        | ction    |          |                        |                 |          |          |

|-------------------|----------------|-----|------------------------|------------------------------------------------------------------------------------------------------------|----------|----------|------------|----------|----------|------------------------|-----------------|----------|----------|

| Name              | <b>No</b> (64) | I/O | T., _44                | 1                                                                                                          | 1 1      | 1:4:     | 4 4 .      |          |          |                        |                 |          |          |

| $I_0 \sim I_3$    | 11~14          | I/O | Instruction These pins |                                                                                                            |          |          | -          |          | on May   | imum n                 | umbar           | of       |          |

|                   |                |     | phrases is             |                                                                                                            |          |          |            |          |          |                        |                 |          | ate      |

|                   | 15.10          |     | for channe             |                                                                                                            |          |          |            |          |          |                        |                 |          |          |

| $I_4 \sim I_7$    | 15~18          | I   | 101 CHailie            | 151 + 4                                                                                                    | ind arc  | Turtin   | n useu     | 1 10 501 | cet the  | CHAIIICI               | attena          | ation it | acc.     |

| WRB               | 19             | I   | Write enal             |                                                                                                            |          |          | ritten     | on the   | data bi  | us of l <sub>0</sub> ~ | - 17 The        | data is  | 3        |

|                   |                |     | written wh             |                                                                                                            |          | OW       |            |          |          |                        |                 |          |          |

| RDB               | 20             | I   |                        | Read enable input. The output busy state of channels $1\sim4$ on the data bus of $l_0\sim l_3$ can be read |          |          |            |          |          |                        |                 |          |          |

|                   |                |     |                        |                                                                                                            |          |          |            |          |          | bus of I               | $_0\sim I_3$ ca | n be re  | ad       |

| CCDD              | 21.22          | T   | using this             |                                                                                                            |          |          |            |          | _        |                        |                 |          |          |

| CSRB              | 21,22          | I   | Chip selec             | Chip select input. Input "L" level either when WR signal is input or                                       |          |          |            |          |          |                        |                 |          |          |

| CSLB              |                | I   | when RD                | signal                                                                                                     | is inp   | ut       |            |          |          |                        |                 |          |          |

| RESETB            | 26             | I   | Reset inpu             | ıt. Re                                                                                                     | eset co  | nditio   | ı is av    | ailable  | by inp   | utting "               | L" leve         | el       |          |

|                   |                |     | All function           | ons are s                                                                                                  | suspen   | ded du   | iring re   | eset     |          |                        |                 |          |          |

| $A_{0\sim}A_{23}$ | 46~64          | O   | Address or             | -                                                                                                          |          |          |            |          |          |                        |                 |          |          |

|                   | 1~6            |     | These pins             |                                                                                                            |          | s the e  | xterna     | 1 ROM    | I in wh  | ich voic               | e data          | is store | :d       |

| $D_0 \sim D_7$    | 34~41          | I   | Voice data             |                                                                                                            |          |          |            |          |          |                        |                 |          |          |

| SS                | 25             | PIH | Sampling               |                                                                                                            |          |          |            |          |          |                        |                 |          |          |

| S1                | 9              | PIL | When osci              |                                                                                                            |          |          |            |          |          |                        |                 | owing    |          |

| S0                | 10             | PIL | choices are            |                                                                                                            |          |          |            |          |          |                        |                 | 100      |          |

|                   |                |     | And " <b>DA</b> (      |                                                                                                            | be set   | ttıng tl | ne othe    | er samp  | pling fr | equency                | y by "S         | 1"&"S    | 0"       |

|                   |                |     | option pins            |                                                                                                            | 41       | . 11     | ( <b>*</b> |          | 4.       |                        |                 |          |          |

|                   |                |     | I ne setting           | The setting is below the table: ( * not suggestion)  Unit :KHz                                             |          |          |            |          |          |                        |                 |          |          |

|                   |                |     |                        |                                                                                                            |          | -22      | = "1"      |          | 1        | -22                    | :"0"            | ι.КПΖ    | <u>,</u> |

|                   |                |     | (S1,S                  | (0)                                                                                                        | 00       | 01       | 10         | 11       | 00       | 01                     | 10              | 11       | -        |

|                   |                |     | Osc =                  | DAOR                                                                                                       | 8        | 8        | 8          | 8        | 6.4      | 6.4                    | 6.4             | 6.4      | -        |

|                   |                |     | 1.088M                 | DAOL                                                                                                       | 8        | 4        | 2*         | 1*       | 6.4      | 3.2                    | 1.6*            | 0.8*     | 1        |

|                   |                |     | Osc =                  | DAOR                                                                                                       | 16       | 16       | 16         | 16       | 12.8     | 12.8                   | 12.8            | 12.8     | 1        |

|                   |                |     | 2.176M                 | DAOL                                                                                                       | 16       | 8        | 4          | 2*       | 12.8     | 6.4                    | 3.2             | 1.6*     | -        |

|                   |                |     | Osc =                  | DAOR                                                                                                       | 32       | 32       | 32         | 32       | 25.6     | 25.6                   | 25.6            | 25.6     | 1        |

|                   |                |     | 4.352M                 | DAOL                                                                                                       | 32       | 16       | 8          | 4        | 25.6     | 12.8                   | 6.4             | 3.2      |          |

| DAOR              | 29             | О   | Voice synt             | thesis or                                                                                                  | itnut    |          | •          |          | •        |                        | •               | •        |          |

| DAOL              | 30             | O   | Voice synt             |                                                                                                            |          | o sion   | al is or   | itnut fi | rom thi  | s nin                  |                 |          |          |

| XT                | 27             | I   | Crystal ose            |                                                                                                            |          | 5 31511  | u1 15 00   | ирис п   | tom tm   | 5 pm.                  |                 |          |          |

| XTB               | 28             | 0   | Crystal os             |                                                                                                            |          |          |            |          |          |                        |                 |          |          |

| VDD               | 32             | P   | Power Sup              |                                                                                                            |          |          |            |          |          |                        |                 |          |          |

| AVDD              | 31             | P   | Analog Po              |                                                                                                            |          | in       |            |          |          |                        |                 |          |          |

| VSS               | 24             | P   | Ground pi              |                                                                                                            | <u> </u> |          |            |          |          |                        |                 |          |          |

| AVSS              | 23             | P   | Analog Gr              |                                                                                                            | n.       |          |            |          |          |                        |                 |          |          |

| MS0               | 7              | PIL | Memory s               |                                                                                                            |          | its:     |            |          |          |                        |                 |          |          |

| MS1               | 8              | PIL | 00: 1M; 01             |                                                                                                            |          |          | M byte     | e (MS1   | ,MS0)    |                        |                 |          |          |

| CS1B              | 42             | О   | 00: 0~1M;              |                                                                                                            |          |          |            |          |          |                        |                 |          |          |

| CS2B              | 43             | О   | 00: 1~2M;              |                                                                                                            |          |          |            |          |          |                        |                 |          |          |

| CS3B              | 44             | О   | 00: 2~3M;              |                                                                                                            |          |          |            |          |          |                        |                 |          |          |

| CS4B              | 45             | О   | 00: 3~4M;              | -                                                                                                          |          | _        |            |          |          |                        | _               |          |          |

## **ELECTRICAL CHARACTERISTICS**

## • Absolute Maximum Ratings

| Parameter            | Symbol       | Conditions | Value             | Unit |

|----------------------|--------------|------------|-------------------|------|

| Power supply voltage | VDD          | Ta=25°C    | -0.3~+7.0         | V    |

| Input voltage        | $V_{\rm IN}$ | Ta=25°C    | -0.3~VDD +0.3     | V    |

| Storage temperature  | $T_{stg}$    |            | <b>-</b> 55 ∼ 150 | °C   |

## • Recommended Operating Conditions

| Parameter             | Symbol | Conditions | Value            | Unit |

|-----------------------|--------|------------|------------------|------|

| Power supply voltage  | VDD    | VSS=0V     | 2.9 ~ +5.5       | V    |

| Operating temperature | Top    | VSS=0V     | <b>-40</b> ∼ +85 | °C   |

| Oscillation frequency | fosc   | VSS=0V     | 1~5              | MHz  |

## • DC Characteristics

$$(Vdd = 2.9 \sim 5.5V, VSS=0V, Ta = -40 \sim 85^{\circ}C)$$

| Parameter                | Symbol             | Conditions                    |        | Limits |        | Unit     |  |

|--------------------------|--------------------|-------------------------------|--------|--------|--------|----------|--|

| 1 at affecter            | Symbol             | Conditions                    | Min.   | Typ.   | Max.   | Omt      |  |

| "L" input current        | $ m I_{IL}$        | V <sub>IL</sub> =VSS          | -10    | _      | ı      |          |  |

| "H" input current        | $ m I_{IH}$        | V <sub>IH</sub> =VDD          | _      | _      | 10     | μΑ       |  |

| "L" input voltage        | $V_{ m IL}$        | _                             | _      | _      | 0.2Vdd | V        |  |

| "H" input voltage        | $ m V_{IH}$        | _                             | 0.8Vdd | _      | -      | <b>V</b> |  |

| "L" output voltage       | $ m V_{OL}$        | $I_{LO}=0.8$ mA               | _      | _      | 0.45   | V        |  |

| "H" output voltage       | $V_{\mathrm{OH}}$  | $I_{OH}$ =-40 $\mu$ A         | Vdd    | _      | 1      | V        |  |

| Output leakage current   | $I_{LO}$           | VSS≤V <sub>OUT</sub> ≤VD<br>D | -10    | _      | 10     | μΑ       |  |

| Operating current        | $I_{DD}$           | $f_{OSC}$ =4.0MHz             | -      | 5      | 10     | mA       |  |

| DA output relative error | $V_{\mathrm{DAE}}$ | No load                       | _      | _      | 20     | mV       |  |

| DA output impedance      | R <sub>DAOUT</sub> | _                             | _      | 15     | _      | kΩ       |  |

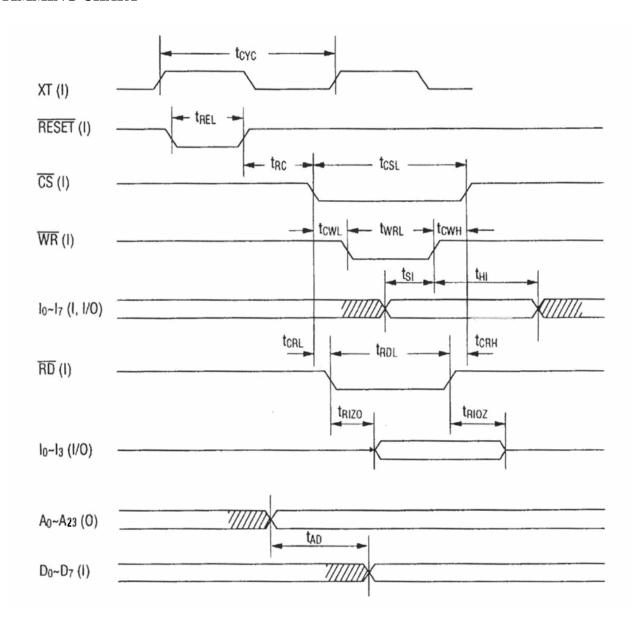

## • AC Characteristics

$VDD = 4.5 \sim 5.5 \text{V,VSS} = 0 \text{V,Ta} = -40 \sim +85 ^{\circ}\text{C}$

| Parameter                                                     | Symbol             | Min. | Тур | Max.                   | Unit |

|---------------------------------------------------------------|--------------------|------|-----|------------------------|------|

| Clock cycle                                                   | $t_{CYC}$          | 200  | -   | -                      | ns   |

| Clock duty cycle                                              | $f_{DUTY}$         | 40   | 50  | 60                     | %    |

| RESET pulse width                                             | $t_{ m REL}$       | 100  | -   | -                      | ns   |

| CS pulse width                                                | $t_{CSL}$          | 250  | -   | -                      | ns   |

| WR pulse width                                                | $t_{\mathrm{WRL}}$ | 200  | -   | -                      | ns   |

| RD pulse width                                                | $t_{ m RDL}$       | 300  | -   | -                      | ns   |

| $\overline{RESET}$ fall to $\overline{CS}$ fall               | $t_{RC}$           | 250  | -   | -                      | ns   |

| $\overline{CS}$ fall to $\overline{WR}$ fall                  | $t_{CWL}$          | 50   | -   | -                      | ns   |

| $\overline{WR}$ raise to $\overline{CS}$ raise                | $t_{CWH}$          | 0    | -   | -                      | ns   |

| Data set up time of $I_0$ - $I_7$ in respect to               | t <sub>SI</sub>    | 80   | -   | -                      | ns   |

| WR raise                                                      |                    |      |     |                        |      |

| Data hold time of $I_0$ - $I_7$ in respect to $\overline{WR}$ | t <sub>HI</sub>    | 80   | -   | -                      | ns   |

| raise                                                         |                    |      |     |                        |      |

| $\overline{RD}$ fall to stable output of $I_0$ - $I_3$        | $t_{RIZO}$         | -    | -   | 120                    | ns   |

| $\overline{RD}$ raise to flow status output of $I_0$ - $I_3$  | $t_{RIOZ}$         | 0    | -   | 120                    | ns   |

| $\overline{CS}$ fall to $\overline{RD}$ fall                  | $t_{CRL}$          | 20   | -   | -                      | ns   |

| $\overline{RD}$ raise to $\overline{CS}$ raise                | $t_{CRH}$          | 0    | -   | -                      | ns   |

| Address stable $(A_0-A_{23})$ to data input of $D_0-D_7$      | $t_{AD}$           | _    | -   | 5•t <sub>CYC</sub> +90 | ns   |

$PS : CS \Rightarrow \overline{CSR}, \overline{CSL}$

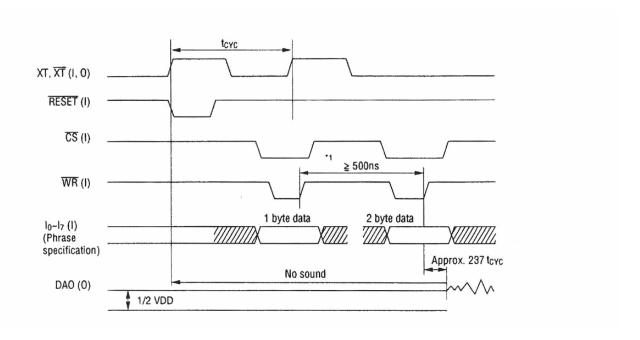

## TIMMING CHART

#### **FUNCTION EXPLANATION**

#### 1. Phrase Selection

Phrase Selection Phrases are specified and read into the 2 byte data which consists of  $I_0 \sim I_7$  data bus. The phrase selection data is latched when WRB goes high while CSLB or CSRB is low (L). The format of the phrase specification input is as follows.

1st Byte 2nd Byte

| <b>I</b> <sub>7</sub> | I <sub>6</sub>            | l <sub>5</sub>        | l <sub>4</sub> | l <sub>3</sub> | $I_2$ | l <sub>1</sub>     | I <sub>0</sub> |  |  |  |  |

|-----------------------|---------------------------|-----------------------|----------------|----------------|-------|--------------------|----------------|--|--|--|--|

| 1                     |                           | Phrase selection data |                |                |       |                    |                |  |  |  |  |

|                       | expansion<br>el specifion | ,                     |                | Re             |       | pecificati<br>~II0 | on             |  |  |  |  |

#### **Relation between Phrase Selection Data and ROM Address**

| Phrase<br>Selection  |                                  | Il <sub>7</sub> | $Il_6$          | 16             | 15    | 14             | 13    | 12    | 11    | 10    | -     | -     | -     |

|----------------------|----------------------------------|-----------------|-----------------|----------------|-------|----------------|-------|-------|-------|-------|-------|-------|-------|

| Data                 |                                  |                 |                 |                |       |                |       |       |       |       |       |       |       |

| External ROM address | A <sub>23</sub> ~A <sub>10</sub> | A <sub>11</sub> | A <sub>10</sub> | A <sub>9</sub> | $A_8$ | A <sub>7</sub> | $A_6$ | $A_5$ | $A_4$ | $A_3$ | $A_2$ | $A_1$ | $A_0$ |

| Selection            |                                  |                 |                 |                |       |                |       |       |       |       |       |       |       |

| Not valid            | 0~0                              | 0               | 0               | 0              | 0     | 0              | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| Phrase 1             | 0~0                              | 0               | 0               | 0              | 0     | 0              | 0     | 0     | 0     | 1     | 0     | 0     | 0     |

| Phrase 2             | 0~0                              | 0               | 0               | 0              | 0     | 0              | 0     | 0     | 1     | 0     | 0     | 0     | 0     |

| Phrase 3             | 0~0                              | 0               | 0               | 0              | 0     | 0              | 0     | 0     | 1     | 1     | 0     | 0     | 0     |

| Phrase 510           | 0~0                              | 1               | 1               | 1              | 1     | 1              | 1     | 1     | 1     | 0     | 0     | 0     | 0     |

| Phrase 511           | 0~0                              | 1               | 1               | 1              | 1     | 1              | 1     | 1     | 1     | 1     |       |       |       |

<sup>\*</sup> Phrases can not be specified with all inputs = "0"

The second byte of data specifies the high phrase address, the synthesis operating channel as well as specific channel reduction of the synthesized play-back. The channel selection format is shown below. It is not possible to specify multiple channels at the same time.

### Phrase expansion bits

The data bits II7 & II6 of second byte and the data bits I6~I0 of first byte will Combine as the total phrase address A11~A3.

## **Channel Specification**

| Channel | II <sub>5</sub> | $II_4$ |

|---------|-----------------|--------|

| 1       | 0               | 0      |

| 2       | 0               | 1      |

| 3       | 1               | 0      |

| 4       | 1               | 1      |

## **Reduction Specification**

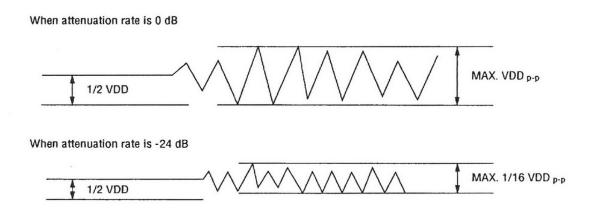

All zero is considered as 0 dB of the relative sound itself. The reduction is made through 9 levels from about 0 dB to - 24 dB with the steps of about - 3 dB. Reduction format is shown below.

#### **Reduction Selection**

| Attenuation level | l <sub>3</sub> | l <sub>2</sub> | I <sub>1</sub> | I <sub>0</sub> |

|-------------------|----------------|----------------|----------------|----------------|

| 0dB               | 0              | 0              | 0              | 0              |

| -3.2 dB           | 0              | 0              | 0              | 1              |

| -6.0 dB           | 0              | 0              | 1              | 0              |

| -9.2 dB           | 0              | 0              | 1              | 0              |

| -12.0dB           | 0              | 1              | 0              | 0              |

| -14.5dB           | 0              | 1              | 0              | 1              |

| -18.0dB           | 0              | 1              | 1              | 0              |

| -20.5dB           | 0              | 1              | 1              | 1              |

| -24.0dB           | 1              | 0              | 0              | 0              |

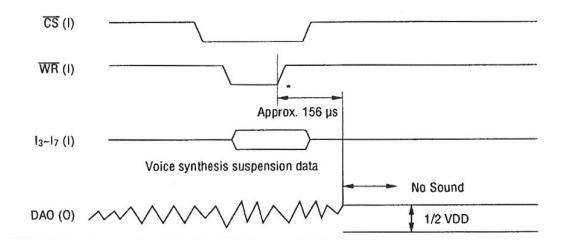

## 2. Voice Synthesis Channel Suspension

Voice synthesis operation of any channel can be suspended. Channel suspension is controlled by bits  $I_3 \sim I_6$  of data bytes  $I_0 \sim I_{07}$ . To suspend a channel, make  $I_7 = 0$ , while  $I_3 \sim I_6$  represent the channels which should be suspended Channel suspension occurs even if multiple channels are selected. For example, if  $I_3 \sim I_6$  are all 1 and  $I_7 = 0$ , then channels  $1 \sim 4$  are suspended simultaneously.

| Suspended channel | l <sub>7</sub> | I <sub>6</sub> | l <sub>5</sub> | l <sub>4</sub> | l <sub>3</sub> | l <sub>2</sub> | I <sub>1</sub> | I <sub>0</sub> |

|-------------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| 1                 | 0              | 0              | 0              | 0              | 1              | ×              | ×              | ×              |

| 2                 | 0              | 0              | 0              | 1              | 0              | ×              | ×              | ×              |

| 3                 | 0              | 0              | 1              | 0              | 0              | ×              | ×              | ×              |

| 4                 | 0              | 1              | 0              | 0              | 0              | ×              | ×              | ×              |

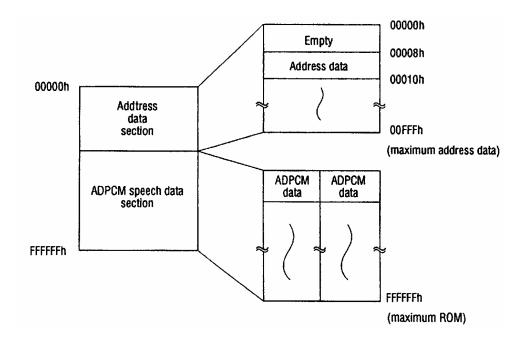

#### 3.Data ROM

#### 1) ADDRESS DATA

This specifics start and stop address of ADPCM speech data. One phrase start and end address consists of 8 bytes. The first 3 bytes show start address while the last 3 bytes show stop address. The other 2 bytes are empty. By selecting the first address in which the start address is stored, the selected speech data is played back.

| Address 0 | $SA_1$          |

|-----------|-----------------|

| Address 1 | $SA_2$          |

| Address 2 | $SA_3$          |

| Address 3 | $EA_1$          |

| Address 4 | $EA_2$          |

| Address 5 | EA <sub>3</sub> |

| Address 6 | EMPTY           |

| Address 7 | EMPTY           |

Start addresses (SA1~SA3) and stop addresses (EA1~EA3) are stored according to the chart shown below

|                                  | D <sub>7</sub>  | D <sub>6</sub> | D <sub>5</sub> | D <sub>4</sub> | D <sub>3</sub> | D <sub>2</sub> | D <sub>1</sub>  | $D_0$           |

|----------------------------------|-----------------|----------------|----------------|----------------|----------------|----------------|-----------------|-----------------|

| $SA_1/EA_1$                      | A23             | A22            | A21            | A20            | A19            | A18            | A <sub>17</sub> | A <sub>16</sub> |

| $SA_2/EA_2$                      | A <sub>15</sub> | $A_{14}$       | $A_{13}$       | $A_{11}$       | $A_{10}$       | $A_{15}$       | $A_9$           | $A_8$           |

| SA <sub>3</sub> /EA <sub>3</sub> | $A_7$           | $A_6$          | $A_5$          | $A_3$          | $A_2$          | $A_{15}$       | $A_1$           | $A_0$           |

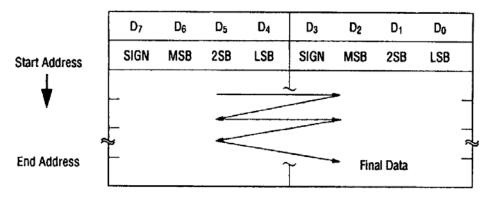

### 2) ADPCM SPEECH DATA

ADPCM speech data consists of (2) 4-bit samples. So, 1 byte stores 2 samples. The data arrangement proceeds from higher rank bits ( $D_4 \sim D_7$ ) to lower rank bits ( $D_0 \sim D_3$ ). The storage of speech data should always be ended with the lower rank bit, So, always store an even number of samples, Speech data is produced by Speech Development Tool TT5665.

#### 3) DATA ROM STRUCTURE

When 1 phrase is selected, address data is written from ROM address 00008h to 0000Fh, When the maximum 511 phrases are selected in address data section, the data is written up to ROM address 00FFFh. and the rest is used as the ADPCM data section. The following chart shows the memory map of the source data ROM.

#### **FUNCTIONAL DESCRIPTION**

#### 1. Phrase Selection Input

This procedure is to input phrase selection data onto the data bus inputs  $I_0 \sim I_7$ . The data is latched internally when  $\overline{WR}$  rises from "L" to "H", while  $\overline{CSL}$  or  $\overline{CSR}$  remains "L". Voice synthesis operation does not start till the second byte is fully latched

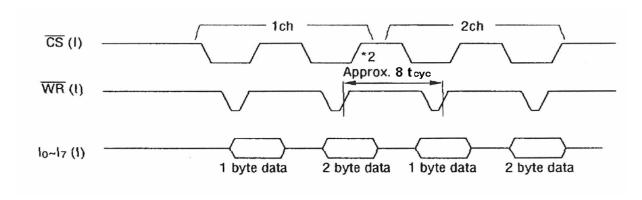

Note: Phrase selection is from channel 1 to channel 8 continuously

If all of CH1~CH8 CMM are latched, then the DAO(R/L) output Arrrox.. 420 tcyc.

\*1 An interval of 75 T<sub>CYC</sub> (max.) is needed between phrases

Note\*2 Oscillation frequency = 1.088 MHz SS = "L'

Voice synthesis playback can be started from any channel, l to 8. The arrangement of each channel can be in any order. The second byte of the phrase selection data contains the phrase attenuation data in bits  $D_0$  -  $D_3$ . Synthesized data is attenuated in -3 dB steps from 0 dB to -24 dB.

## 2. Attenuation of Synthesized Speech

### 3. Speech Synthesis Channel Suspension

This is accomplished by writing the synthesis channel suspension data onto data bus inputs  $I_3 \sim I_7$  The data is latched internally when  $\overline{\text{WR}}$  goes from "L" to "H" while  $\overline{\text{CS}}$  (R/L) remains active (L). Since synthesis suspension data is 1 byte data, synthesis operation is suspended right after the rising edge of  $\overline{\text{WR}}$ . Multiple channels can be specified, making it possible to suspend channels  $1 \sim 4$  simultaneously.

Note: \* Oscillation frequency = 1.088 MHz SS= "L"

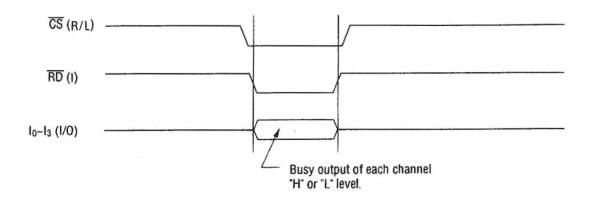

## 4. Reading the Busy Status

While  $\overline{CS}$  (R/L) is "L" and  $\overline{RD}$  is "L", each operation state, the busy state of channels 1~4 is output on I<sub>0</sub>~I<sub>3</sub>. "H" is output during synthesized playback.

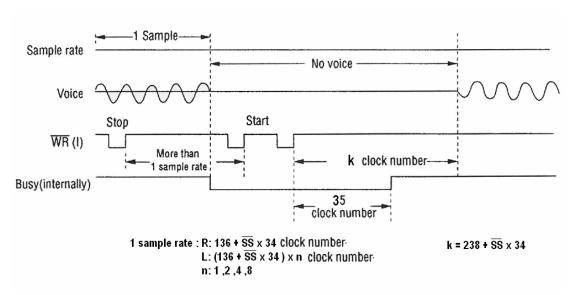

## 5. Start and Stop of 1 Channel

### **Start and Stop of Signal Channel**

When a single channel (either of channels 1-4) starts again after it has stopped, the first write for start must be input with a delay of more than one sample rate from the stop write as shown in the figure above. When stop is entered, voice playback stops all the next sample and BUSY becomes "L" When start is entered again, voice is output after 238 + ( the reverse of SS pin ) x 34 clock from the second byte write. BUSY becomes "H" after 35 clock internally

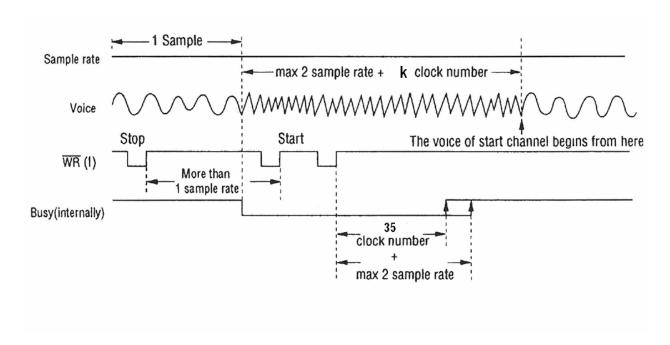

**Start and Stop in Plural Channels**

When channels are operating, the first byte write for start must be input with a delay of more than one sample rate from stop writing. The channel where stop was input, stops at every sample. Voice off the channel where stop was again input is output after a maximum 2 samples +k clocks from the preceding sample point.

The BUSY signal becomes "H" state after the 35 clock + maximum 2 samples time.

## **APPLICATION CIRCUIT**

For 4M Byte ROM  $\times$  4 ( MS0 = "0", MS1 = "1") **Reference Only**

# TŦ

## PACKAGE OUTLINE (64 pin QFP)

# **REVISE HISTORY**

- 1. 2007/6/20 (V1.0)

- -Original version

- 2. 2007/9/7 (V1.1)

- -Fix page 4:

- $1.056\text{MHz} \rightarrow 1.088\text{MHz}$

- $2.112\text{MHz} \rightarrow 2.176\text{MHz}$

- 4.224MHz → 4.352MHz