# MW3753MAE

# 8mm (1/2 inch) 768H CCD Area Image Sensor

#### Overview

The MW3753MAE is a 8mm (1/2 inch) Interline Transfer CCD (IT-CCD) solid state image sensor device.

This device uses photodiodes in the optoelectric conversion section and CCDs for signal read out. The electronic shutter function has made possible an exposure time of 1/10000 seconds. Further, this device has the features of high sensitivity, low noise, broad dynamic range, and low smear.

This device has a total of 410K pixels (816 horizontal × 495 vertical) and provides stable and clear images with a resolution of 560 horizontal TV-lines and 350 vertical TV-lines.

| Type No.  | Type No. Size  |        | Color or B/W |  |  |

|-----------|----------------|--------|--------------|--|--|

| MW3753MAE | 8mm (1/2 inch) | (NTSC) | B/W          |  |  |

#### ■ Features

- Total number of pixels: 816 (horizontal) × 495 (vertical)

- High sensitivity

- Low noise

- Broad dynamic range

- Low smear

- Low image lag

- Electronic shutter function present

- No image distortion

- Small size enables design of compact equipment

- · High reliability

- 20 Pin DIL ceramic package

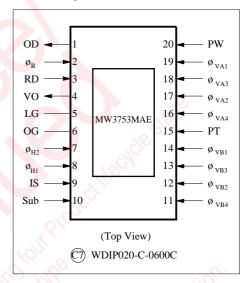

#### ■ Pin Assignments

#### Applications

• Cameras for commercial use

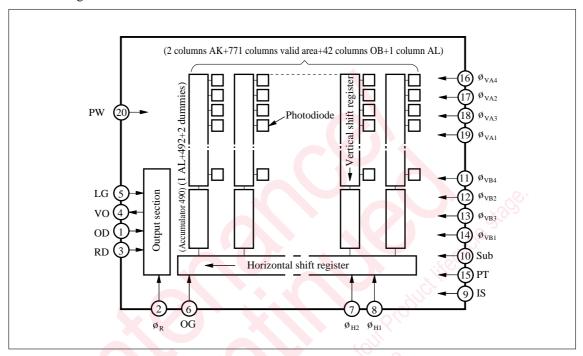

### ■ Block Diagram

### ■ Pin Descriptions

| Pin No. | Symbol          | Descriptions                        | Pin No. | Symbol           | Descriptions                              |

|---------|-----------------|-------------------------------------|---------|------------------|-------------------------------------------|

| 1       | OD              | Output drain                        | 11      | Ø <sub>VB4</sub> | Vertical shift register clock pulse (B4)  |

| 2       | ø <sub>R</sub>  | Reset pulse                         | 12      | ø <sub>VB2</sub> | Vertical shift register clock pulse (B2)  |

| 3       | RD              | Reset drain                         | 13      | Ø <sub>VB3</sub> | Vertical shift register clock pulse (Bb3) |

| 4       | VO              | Video output                        | 14      | ø <sub>VB1</sub> | Vertical shift register clock pulse (B1)  |

| 5       | LG              | Output load transistor gate         | 15      | PT               | P-well for protection circuit             |

| 6       | OG              | Output gate                         | 16      | Ø <sub>VA4</sub> | Vertical shift register clock pulse (A4)  |

| 7       | Ø <sub>H2</sub> | Horizontal register clock pulse (2) | 17      | Ø <sub>VA2</sub> | Vertical shift register clock pulse (A2)  |

| 8       | Ø <sub>H1</sub> | Horizontal register clock pulse (1) | 18      | Ø <sub>VA3</sub> | Vertical shift register clock pulse (A3)  |

| 9       | IS              | Input source                        | 19      | Øva1             | Vertical shift register clock pulse (A1)  |

| 10      | Sub             | Substrate                           | 20      | PW               | P-well                                    |

#### ■ Absolute Maximum Ratings and Operating Conditions

| Parameter                     |        | Symbol                 | Ra                    | Rating     |                                             | Operating condition |        |     |

|-------------------------------|--------|------------------------|-----------------------|------------|---------------------------------------------|---------------------|--------|-----|

| Parameter                     | Symbol | min                    | max                   | min        | typ                                         | max                 | Unit   |     |

| Output drain voltage          |        | $V_{OD}$               | 0                     | 18         | 14.7                                        | 15.0                | 15.3   | V   |

| D . 1 1                       | (P-P)  | $V_{\text{ø R (P-P)}}$ | _                     | 18         | 7.7                                         | 8.0                 | 8.3    | V   |

| Reset pulse voltage           | (L)    | $V_{\text{ø R (L)}}$   | 0                     | _          | 2.7                                         | 3.0                 | 3.3    | V   |

| Reset drain voltage           |        | $V_{RD}$               | 0                     | 18         | 14.7                                        | 15.0                | 15.3   | V   |

| Video output voltage          |        | $V_{ m VO}$            | _                     |            | _                                           |                     | _      | V   |

| Output load transistor gate v | oltage | $V_{LG}$               | (Supplied internally) |            |                                             |                     |        | V   |

| Output gate voltage           |        | $V_{OG}$               | (Supplied internally) |            |                                             |                     |        |     |

| Horizontal register           | (H)    | Vø H2 (H)              |                       | 18         | 4.7                                         | 5.0                 | 5.3    | V   |

| lock pulse voltage (2)        | (L)    | $V_{\text{ø H2 (L)}}$  | 0                     |            | 0                                           | 0                   | 0.3    | V   |

| Horizontal register           | (H)    | V <sub>ø H1 (H)</sub>  |                       | 18         | 4.7                                         | 5.0                 | 5.3    | V   |

| lock pulse voltage (1)        | (L)    | $V_{\phi H1 (L)}$      | 0                     |            | 0                                           | 0                   | 0.3    | V   |

| Input source voltage          |        | $V_{IS}$               | 0                     | 18         | 14.7                                        | 15.0                | 15.3   | V   |

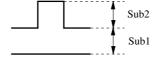

| Substrate voltage 1           |        | $V_{Sub(1)}^*$         | 0                     | 18         | 2.0                                         | Adjust              | 9 14.0 | V   |

| Substrate voltage 2           |        | V <sub>Sub(2)</sub> *  | 0                     | 50         | 28.0                                        | 30.0                | 32.0   | V   |

| Vertical shift register       | (M)    | V <sub>ø VB4 (M)</sub> |                       | 15         | 1.7                                         | 2.0                 | 2.3    | V   |

| lock pulse (B4) voltage       | (L)    | $V_{\text{ø VB4 (L)}}$ | -11                   |            | -9.3                                        | -9.0                | -8.7   | V   |

| Vertical shift register       | (M)    | V <sub>ø VB2 (M)</sub> |                       | 15         | 1.7                                         | 2.0                 | 2.3    | V   |

| lock pulse (B2) voltage       | (L)    | $V_{\text{ø VB2 (L)}}$ | -11                   | _          | -9.3                                        | -9.0                | -8.7   | V   |

| Vertical shift register       | (M)    | V <sub>ø VB3 (M)</sub> |                       | 15         | 0                                           | 0                   | 0.3    | V   |

| lock pulse (B3) voltage       | (L)    | $V_{\text{ø VB3 (L)}}$ | -11                   | ~0         | -9.3                                        | -9.0                | -8.7   | V   |

| Vertical shift register       | (M)    | V <sub>ø VB1 (M)</sub> |                       | 15         | 0                                           | 0                   | 0.3    | V   |

| lock pulse (B1) voltage       | (L)    | $V_{\text{ø VB1 (L)}}$ | -11                   | 11/20      | -9.3                                        | -9.0                | -8.7   | . V |

| Protection P well voltage     |        | $V_{\mathrm{PT}}$      | -,(                   | 3 -c S     | $\phi_{\rm VL} - 0.7 - \phi_{\rm VL} - 1.3$ |                     |        | V   |

| Vertical shift register       | (M)    | Vø va4 (M)             | +0)                   | 15         | 1.7                                         | 2.0                 | 2.3    | V   |

| lock pulse (A4) voltage       | (L)    | Vø VA4 (L)             | -9                    |            | -9.3                                        | -9.0                | -8.7   | V   |

| Vertical shift register       | (M)    | V <sub>ø VA2 (M)</sub> | 10,-10                | 15         | 1.7                                         | 2.0                 | 2.3    | V   |

| lock pulse (A2) voltage       | (L)    | Vø va2 (L)             | _9                    | 2          | -9.3                                        | -9.0                | -8.7   | V   |

|                               | (H)    | Vø va3 (H)             | 9- 1                  | 18         | 15.7                                        | 16.0                | 16.3   | V   |

| Vertical shift register       | (M)    | Vø VA3 (M)             |                       | 18         | 0                                           | 00                  | 0.3    | V   |

| lock pulse (A3) voltage       | (L)    | Vø va3 (L)             | -9                    | 112 1      | -9.3                                        | -9.0                | -8.7   | V   |

|                               | (H)    | Vø val (H)             |                       | 18         | 15.7                                        | 16.0                | 16.3   | V   |

| Vertical shift register       | (M)    | Vø val (M)             | 700                   | 18         | 0                                           | 0                   | 0.3    | V   |

| lock pulse (A1) voltage       | (L)    | Vø val (L)             | -9                    | 05 ~       | -9.3                                        | -9.0                | -8.7   | V   |

| P well voltage                | CO/V   | $V_{PW}$               | Reference             | ce voltage | 340                                         | 0                   | _      | V   |

Note 1) The initial setting of  $V_{Sub}$  shall be 8.0V and shall be adjusted to the minimum voltage at which no blooming or no overflow charge is caused at a light input of 200 times the standard value. The standard light input is the one when the exposure is done at an aperture of F/8 using a light source of 2856K and 920nt, and placing a color temperature conversion filter LB-40 (Hoya) and an IR cutting filter CAW-500S (t=2.5mm) in the light path.

Note 2)  $V_{Sub(1)}$  is the DC component during normal operation.

$V_{\text{Sub}(2)}$  is the amplitude of the pulse added to  $V_{\text{Sub}(1)}$  during electronic shutter operation.

The operation should be made with  $(V_{Sub(1)} + V_{Sub(2)})$  less than or equal to 46V.

Also, the power supply impedance of  $V_{\text{Sub}}$  should be  $100\Omega$  or less.

\* The absolute maximum rating of  $V_{\text{Sub(2)}}$  is 50V and the maximum amplitude of the additional part of the voltage is 30V.

Pins 5 and 6 should each be grounded by 0.047μF capacitors.

## ■ Optical Characteristics

| Type No.  | Color<br>or<br>B/W | Valid | Valid pixels |              | Saturation output | Sensitivity<br>F8 | Vertical<br>smear | Image lag   | Horizontal resolution | Vertical resolution |

|-----------|--------------------|-------|--------------|--------------|-------------------|-------------------|-------------------|-------------|-----------------------|---------------------|

|           |                    | Н     | V            | typ.<br>(dB) | typ.<br>(mV)      | typ.<br>(mV)      | Sm<br>typ. (dB)   | typ.<br>(%) | typ.<br>(TV-lines)    | typ.<br>(TV-lines)  |

| MW3753MAE | B/W                | 771   | 492          | 62           | 1700              | 750               | -125              | 0           | 560                   | 350                 |

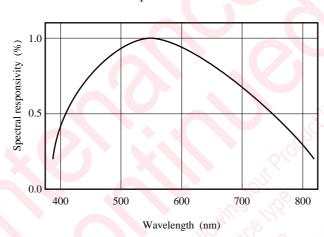

## ■ Graphs of Characteristics

## CCD Spectral Characteristics

**Panasonic**

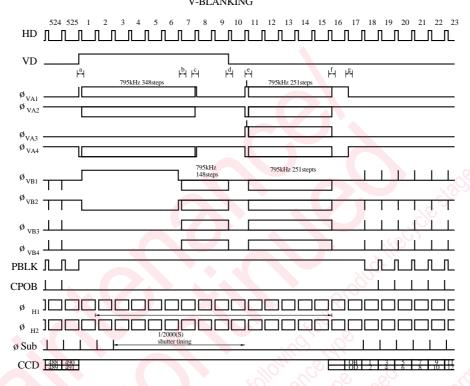

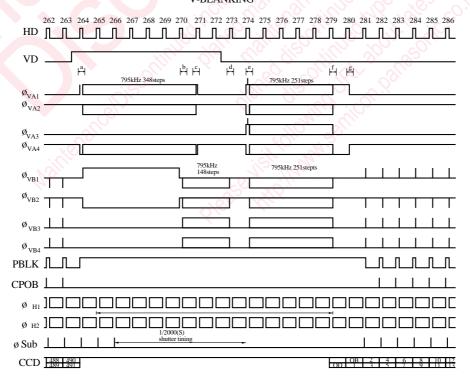

#### ■ Example of Recommended Driving Pulses

## < Field B > V-BLANKING

# Request for your special attention and precautions in using the technical information and semiconductors described in this book

- (1) If any of the products or technical information described in this book is to be exported or provided to non-residents, the laws and regulations of the exporting country, especially, those with regard to security export control, must be observed.

- (2) The technical information described in this book is intended only to show the main characteristics and application circuit examples of the products, and no license is granted under any intellectual property right or other right owned by our company or any other company. Therefore, no responsibility is assumed by our company as to the infringement upon any such right owned by any other company which may arise as a result of the use of technical information described in this book.

- (3) The products described in this book are intended to be used for standard applications or general electronic equipment (such as office equipment, communications equipment, measuring instruments and household appliances).

Consult our sales staff in advance for information on the following applications:

- Special applications (such as for airplanes, aerospace, automobiles, traffic control equipment, combustion equipment, life support systems and safety devices) in which exceptional quality and reliability are required, or if the failure or malfunction of the products may directly jeopardize life or harm the human body.

- Any applications other than the standard applications intended.

- (4) The products and product specifications described in this book are subject to change without notice for modification and/or improvement. At the final stage of your design, purchasing, or use of the products, therefore, ask for the most up-to-date Product Standards in advance to make sure that the latest specifications satisfy your requirements.

- (5) When designing your equipment, comply with the range of absolute maximum rating and the guaranteed operating conditions (operating power supply voltage and operating environment etc.). Especially, please be careful not to exceed the range of absolute maximum rating on the transient state, such as power-on, power-off and mode-switching. Otherwise, we will not be liable for any defect which may arise later in your equipment.

- Even when the products are used within the guaranteed values, take into the consideration of incidence of break down and failure mode, possible to occur to semiconductor products. Measures on the systems such as redundant design, arresting the spread of fire or preventing glitch are recommended in order to prevent physical injury, fire, social damages, for example, by using the products.

- (6) Comply with the instructions for use in order to prevent breakdown and characteristics change due to external factors (ESD, EOS, thermal stress and mechanical stress) at the time of handling, mounting or at customer's process. When using products for which damp-proof packing is required, satisfy the conditions, such as shelf life and the elapsed time since first opening the packages.

- (7) This book may be not reprinted or reproduced whether wholly or partially, without the prior written permission of Matsushita Electric Industrial Co., Ltd.