# **ENC28J60**

### **Stand-Alone Ethernet Controller with SPI Interface**

#### **Ethernet Controller Features**

- IEEE 802.3™ Compatible Ethernet Controller

- Fully Compatible with 10/100/1000Base-T Networks

- Integrated MAC and 10Base-T PHY

- Supports One 10Base-T Port with Automatic Polarity Detection and Correction

- · Supports Full and Half-Duplex modes

- · Programmable Automatic Retransmit on Collision

- Programmable Padding and CRC Generation

- Programmable Automatic Rejection of Erroneous Packets

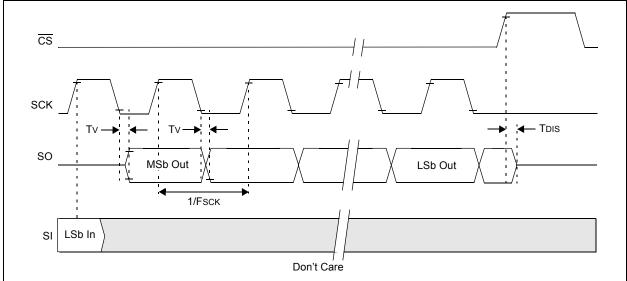

- · SPI Interface with Clock Speeds up to 20 MHz

#### Buffer

- · 8-Kbyte Transmit/Receive Packet Dual Port SRAM

- · Configurable Transmit/Receive Buffer Size

- · Hardware Managed Circular Receive FIFO

- Byte-Wide Random and Sequential Access with Auto-Increment

- · Internal DMA for Fast Data Movement

- Hardware Assisted Checksum Calculation for Various Network Protocols

#### Medium Access Controller (MAC) Features

- Supports Unicast, Multicast and Broadcast

Packets

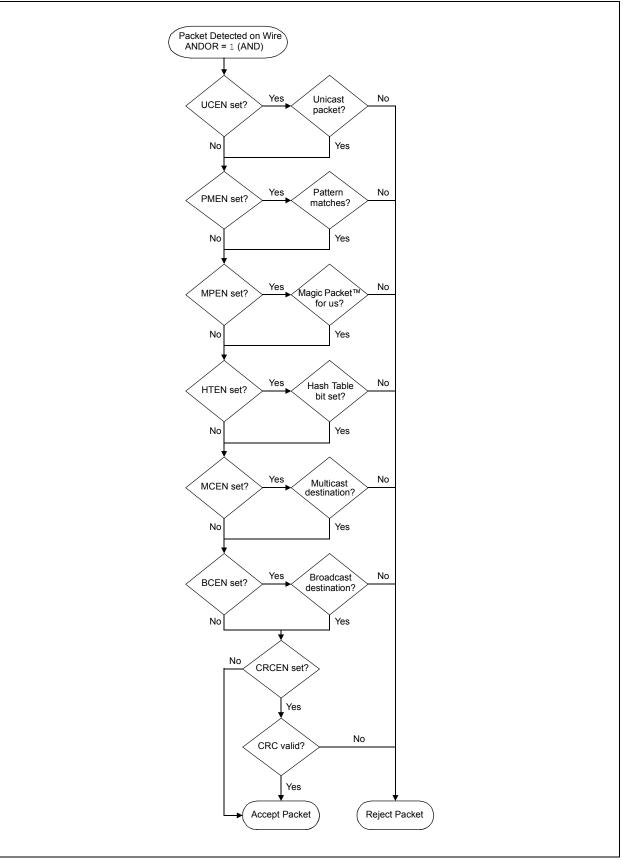

- Programmable Receive Packet Filtering and Wake-up Host on Logical AND or OR of the Following:

- Unicast destination address

- Multicast address

- Broadcast address

- Magic Packet™

- Group destination addresses as defined by 64-bit Hash Table

- Programmable Pattern Matching of up to 64 bytes at user-defined offset

#### **Physical Layer (PHY) Features**

- Loopback mode

- Two Programmable LED Outputs for LINK, TX, RX, Collision and Full/Half-Duplex Status

#### Operational

- · Six Interrupt Sources and One Interrupt Output Pin

- 25 MHz Clock Input Requirement

- · Clock Out Pin with Programmable Prescaler

- Operating Voltage of 3.1V to 3.6V (3.3V typical)

- 5V Tolerant Inputs

- Temperature Range: -40°C to +85°C Industrial, 0°C to +70°C Commercial (SSOP only)

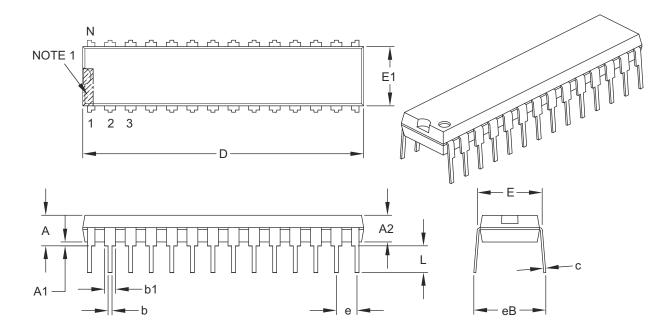

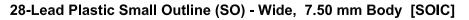

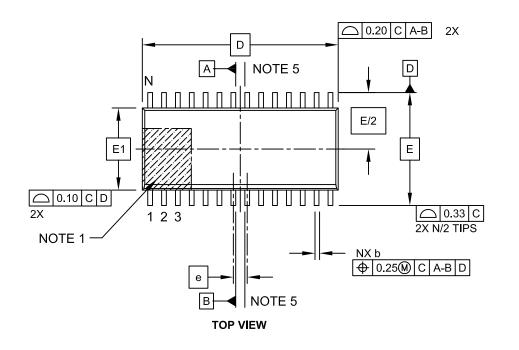

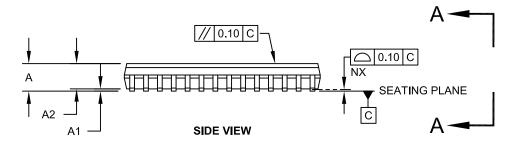

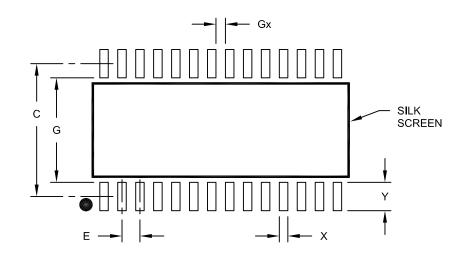

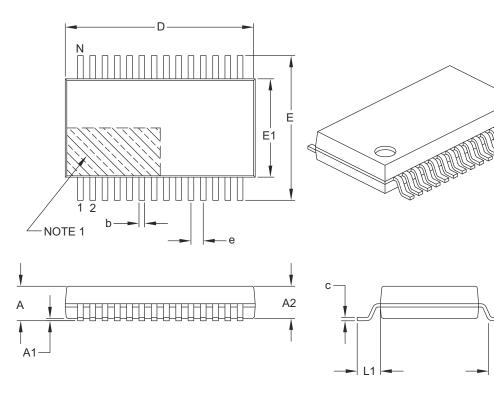

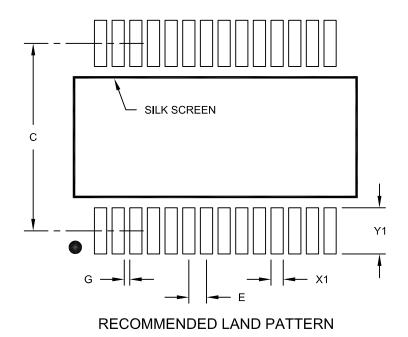

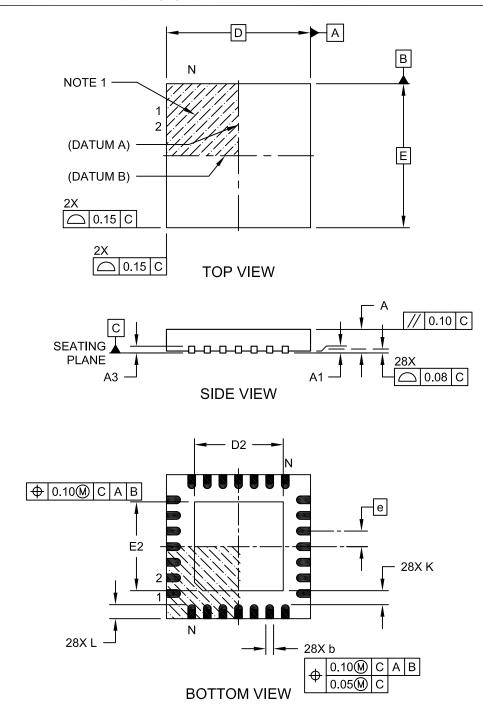

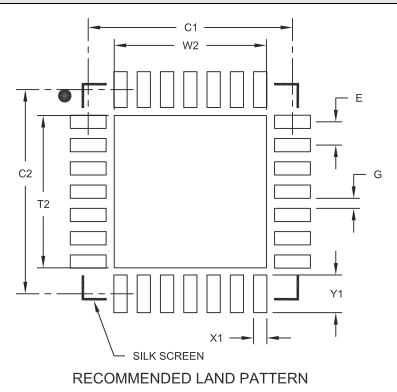

- 28-Pin SPDIP, SSOP, SOIC, QFN Packages

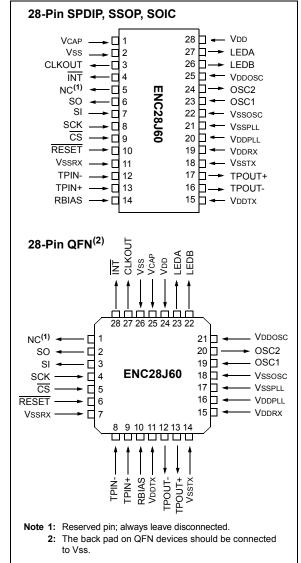

#### Package Types

© 2006-2012 Microchip Technology Inc.

#### **Table of Contents**

| 1.0 (  | Overview                                  | . 3 |

|--------|-------------------------------------------|-----|

| 2.0    | External Connections                      | . 5 |

| 3.0 I  | Memory Organization                       | 11  |

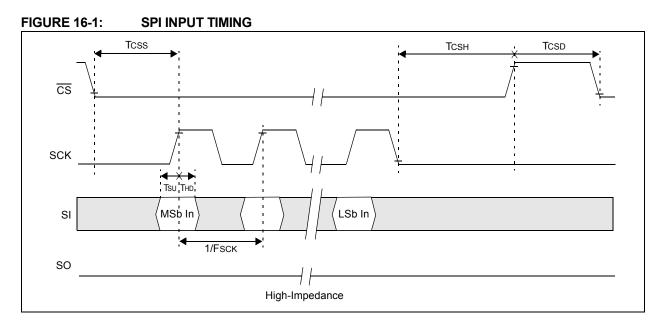

| 4.0 \$ | Serial Peripheral Interface (SPI)         | 25  |

| 5.0 E  | Ethernet Overview                         | 31  |

| 6.0 I  | nitialization                             | 33  |

| 7.0    | Transmitting and Receiving Packets        | 39  |

| 8.0 I  | Receive Filters                           | 47  |

| 9.0    | Duplex Mode Configuration and Negotiation | 53  |

| 10.0 I | Flow Control                              | 55  |

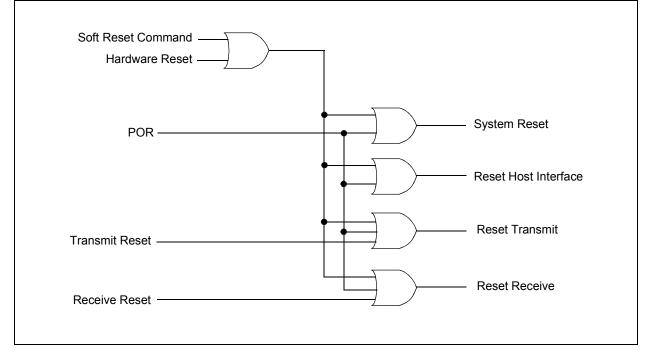

| 11.0 F | Reset                                     | 59  |

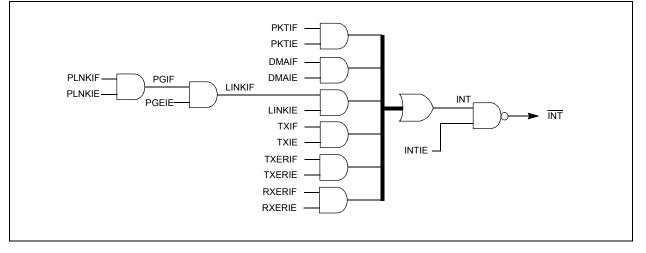

| 12.0 I | nterrupts                                 | 63  |

| 13.0 I | Direct Memory Access Controller           | 71  |

| 14.0 F | Power-Down                                | 73  |

| 15.0 E | Built-in Self-Test Controller             | 75  |

| 16.0 E | Electrical Characteristics                | 79  |

| 17.0 F | Packaging Information                     | 83  |

| Appen  | dix A: Revision History                   | 93  |

| The M  | icrochip Web Site                         | 95  |

| Custor | ner Change Notification Service           | 95  |

| Custor | ner Support                               | 95  |

| Reade  | r Response                                | 96  |

| Produc | t Identification System                   | 99  |

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

#### 1.0 OVERVIEW

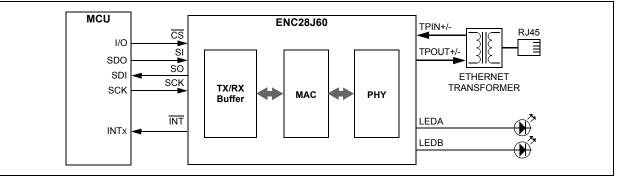

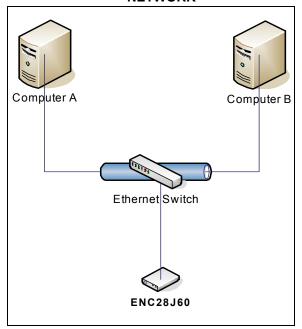

The ENC28J60 is a stand-alone Ethernet controller with an industry standard Serial Peripheral Interface (SPI). It is designed to serve as an Ethernet network interface for any controller equipped with SPI.

The ENC28J60 meets all of the IEEE 802.3 specifications. It incorporates a number of packet filtering schemes to limit incoming packets. It also provides an internal DMA module for fast data throughput and hardware assisted checksum calculation, which is used in various network protocols. Communication with the host controller is implemented via an interrupt pin and the SPI, with clock rates of up to 20 MHz. Two dedicated pins are used for LED link and network activity indication.

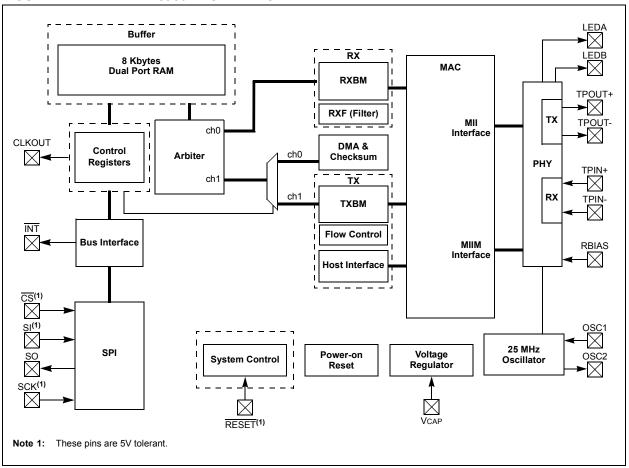

A simple block diagram of the ENC28J60 is shown in Figure 1-1. A typical application circuit using the device is shown in Figure 1-2. With the ENC28J60, two pulse transformers and a few passive components are all that are required to connect a microcontroller to an Ethernet network.

The ENC28J60 consists of seven major functional blocks:

- 1. An SPI interface that serves as a communication channel between the host controller and the ENC28J60.

- 2. Control registers which are used to control and monitor the ENC28J60.

- 3. A dual port RAM buffer for received and transmitted data packets.

- 4. An arbiter to control the access to the RAM buffer when requests are made from DMA, transmit and receive blocks.

- 5. The bus interface that interprets data and commands received via the SPI interface.

- 6. The MAC (Medium Access Control) module that implements IEEE 802.3 compliant MAC logic.

- 7. The PHY (Physical Layer) module that encodes and decodes the analog data that is present on the twisted-pair interface.

The device also contains other support blocks, such as the oscillator, on-chip voltage regulator, level translators to provide 5V tolerant I/Os and system control logic.

#### FIGURE 1-1: ENC28J60 BLOCK DIAGRAM

<sup>© 2006-2012</sup> Microchip Technology Inc.

#### **TABLE 1-1: PINOUT I/O DESCRIPTIONS**

| SPDIP,<br>SOIC, SSOP | QFN                                                                                                                                                     | Pin<br>-                                              | Buffer                                                |                                                                                                                                                                                                     |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                    |                                                                                                                                                         | Ріп<br>Туре                                           | Витег<br>Туре                                         | Description                                                                                                                                                                                         |

| I                    | 25                                                                                                                                                      | Р                                                     | _                                                     | 2.5V output from internal regulator. A low Equivalent Series Resistance (ESR) capacitor, with a typical value of 10 $\mu$ F and a minimum value of 1 $\mu$ F to ground, must be placed on this pin. |

| 2                    | 26                                                                                                                                                      | Р                                                     | —                                                     | Ground reference.                                                                                                                                                                                   |

| 3                    | 27                                                                                                                                                      | 0                                                     | —                                                     | Programmable clock output pin. <sup>(1)</sup>                                                                                                                                                       |

| 4                    | 28                                                                                                                                                      | 0                                                     | _                                                     | INT interrupt output pin. <sup>(2)</sup>                                                                                                                                                            |

| 5                    | 1                                                                                                                                                       | 0                                                     | _                                                     | Reserved function; always leave unconnected.                                                                                                                                                        |

| 6                    | 2                                                                                                                                                       | 0                                                     | —                                                     | Data out pin for SPI interface. <sup>(2)</sup>                                                                                                                                                      |

| 7                    | 3                                                                                                                                                       | I                                                     | ST                                                    | Data in pin for SPI interface. <sup>(3)</sup>                                                                                                                                                       |

| 8                    | 4                                                                                                                                                       | Ι                                                     | ST                                                    | Clock in pin for SPI interface. <sup>(3)</sup>                                                                                                                                                      |

| 9                    | 5                                                                                                                                                       | I                                                     | ST                                                    | Chip select input pin for SPI interface. <sup>(3,4)</sup>                                                                                                                                           |

| 10                   | 6                                                                                                                                                       | Ι                                                     | ST                                                    | Active-low device Reset input. <sup>(3,4)</sup>                                                                                                                                                     |

| 11                   | 7                                                                                                                                                       | Р                                                     | —                                                     | Ground reference for PHY RX.                                                                                                                                                                        |

| 12                   | 8                                                                                                                                                       | I                                                     | ANA                                                   | Differential signal input.                                                                                                                                                                          |

| 13                   | 9                                                                                                                                                       | I                                                     | ANA                                                   | Differential signal input.                                                                                                                                                                          |

| 14                   | 10                                                                                                                                                      | I                                                     | ANA                                                   | Bias current pin for PHY. Must be tied to ground via a resistor (refer to Section 2.4 "Magnetics, Termination and Other External Components" for details).                                          |

| 15                   | 11                                                                                                                                                      | Р                                                     | _                                                     | Positive supply for PHY TX.                                                                                                                                                                         |

| 16                   | 12                                                                                                                                                      | 0                                                     | _                                                     | Differential signal output.                                                                                                                                                                         |

| 17                   | 13                                                                                                                                                      | 0                                                     | _                                                     | Differential signal output.                                                                                                                                                                         |

| 18                   | 14                                                                                                                                                      | Р                                                     | —                                                     | Ground reference for PHY TX.                                                                                                                                                                        |

| 19                   | 15                                                                                                                                                      | Р                                                     | —                                                     | Positive 3.3V supply for PHY RX.                                                                                                                                                                    |

| 20                   | 16                                                                                                                                                      | Р                                                     | _                                                     | Positive 3.3V supply for PHY PLL.                                                                                                                                                                   |

| 21                   | 17                                                                                                                                                      | Р                                                     | _                                                     | Ground reference for PHY PLL.                                                                                                                                                                       |

| 22                   | 18                                                                                                                                                      | Р                                                     | _                                                     | Ground reference for oscillator.                                                                                                                                                                    |

| 23                   | 19                                                                                                                                                      | I                                                     | ANA                                                   | Oscillator input.                                                                                                                                                                                   |

| 24                   | 20                                                                                                                                                      | 0                                                     | _                                                     | Oscillator output.                                                                                                                                                                                  |

| 25                   | 21                                                                                                                                                      | Р                                                     | —                                                     | Positive 3.3V supply for oscillator.                                                                                                                                                                |

| 26                   | 22                                                                                                                                                      | 0                                                     | _                                                     | LEDB driver pin. <sup>(5)</sup>                                                                                                                                                                     |

| 27                   | 23                                                                                                                                                      | 0                                                     | _                                                     | LEDA driver pin. <sup>(5)</sup>                                                                                                                                                                     |

| 28                   | 24                                                                                                                                                      | Р                                                     | _                                                     | Positive 3.3V supply.                                                                                                                                                                               |

|                      | 3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20<br>21<br>21<br>22<br>23<br>24<br>25<br>26<br>27<br>28 | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                               |

.

Note 1: Pins have a maximum current capacity of 8 mA.

2: Pins have a maximum current capacity of 4 mA.

3: Pins are 5V tolerant.

4: Pins have an internal weak pull-up to VDD.

5: Pins have a maximum current capacity of 12 mA.

### 2.0 EXTERNAL CONNECTIONS

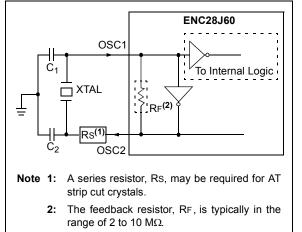

#### 2.1 Oscillator

The ENC28J60 is designed to operate at 25 MHz with a crystal connected to the OSC1 and OSC2 pins. The ENC28J60 design requires the use of a parallel resonance crystal. Use of a series resonance crystal may give a frequency out of the crystal manufacturer specifications. A typical oscillator circuit is shown in Figure 2-1.

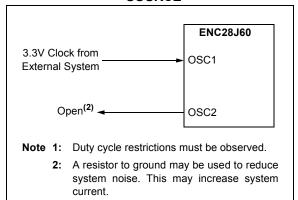

The ENC28J60 may also be driven by an external clock source connected to the OSC1 pin as shown in Figure 2-2.

FIGURE 2-2: EXTERNAL CLOCK SOURCE<sup>(1)</sup>

#### 2.2 Oscillator Start-up Timer

The ENC28J60 contains an Oscillator Start-up Timer (OST) to ensure that the oscillator and integrated PHY have stabilized before use. The OST does not expire until 7500 OSC1 clock cycles ( $300 \ \mu$ s) pass after Power-on Reset or wake-up from Power-Down mode occurs. During the delay, all Ethernet registers and buffer memory may still be read and written to through the SPI bus. However, software should not attempt to transmit any packets (set ECON1.TXRTS), enable reception of packets (set ECON1.RXEN) or access any MAC, MII or PHY registers during this period.

When the OST expires, the CLKRDY bit in the ESTAT register will be set. The application software should poll this bit as necessary to determine when normal device operation can begin.

Note: After a Power-on Reset, or the ENC28J60 is removed from Power-Down mode, the CLKRDY bit must be polled before transmitting packets, enabling packet reception or accessing any MAC, MII or PHY registers.

© 2006-2012 Microchip Technology Inc.

#### 2.3 CLKOUT Pin

The Clock Out (CLKOUT) pin is provided to the system designer for use as the host controller clock or as a clock source for other devices in the system. The CLKOUT has an internal prescaler which can divide the output by 1, 2, 3, 4 or 8. The CLKOUT function is enabled and the prescaler is selected via the ECOCON register (Register 2-1).

To create a clean clock signal, the CLKOUT pin is held low for a period when power is first applied. After the Power-on Reset ends, the OST will begin counting. When the OST expires, the CLKOUT pin will begin outputting its default frequency of 6.25 MHz (main clock divided by 4). At any future time that the ENC28J60 is reset by software or the RESET pin, the CLKOUT function will not be altered (ECOCON will not change value). Additionally, Power-Down mode may be entered and the CLKOUT function will continue to operate. When Power-Down mode is cancelled, the OST will be reset but the CLKOUT function will continue. When the CLKOUT function is disabled (ECOCON = 0), the CLKOUT pin is driven low.

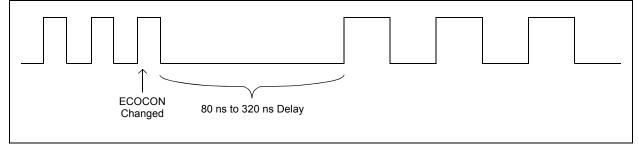

The CLKOUT function is designed to ensure that minimum timings are preserved when the CLKOUT pin function is enabled, disabled or the prescaler value is changed. No high or low pulses will be outputted which exceed the frequency specified by the ECOCON configuration. However, when switching frequencies, a delay between two and eight OSC1 clock periods will occur where no clock pulses will be produced (see Figure 2-3). During this period, CLKOUT will be held low.

#### FIGURE 2-3: CLKOUT TRANSITION

#### REGISTER 2-1: ECOCON: CLOCK OUTPUT CONTROL REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | R/W-1  | R/W-0  | R/W-0  |

|-------|-----|-----|-----|-----|--------|--------|--------|

| —     | —   | —   | —   | —   | COCON2 | COCON1 | COCON0 |

| bit 7 |     |     |     |     |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-3 Unimplemented: Read as '0'

bit 2-0 COCON<2:0>: Clock Output Configuration bits

11x = Reserved for factory test, do not use; glitch prevention is not assured

- 101 = CLKOUT outputs main clock divided by 8 (3.125 MHz)

- 100 = CLKOUT outputs main clock divided by 4 (6.25 MHz)

011 = CLKOUT outputs main clock divided by 3 (8.333333 MHz)

- 010 = CLKOUT outputs main clock divided by 2 (12.5 MHz)

- 001 = CLKOUT outputs main clock divided by 1 (25 MHz)

- 000 = CLKOUT is disabled, the pin is driven low

#### 2.4 Magnetics, Termination and Other External Components

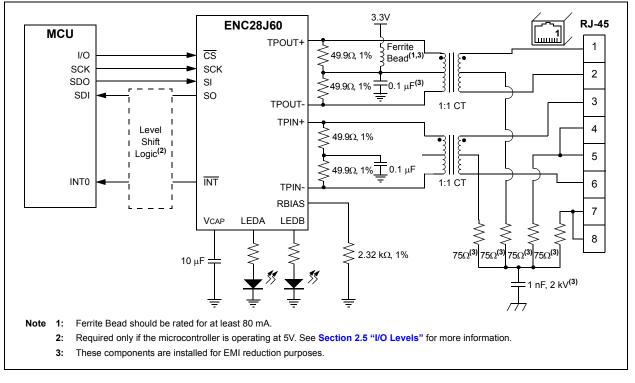

To complete the Ethernet interface, the ENC28J60 requires several standard components to be installed externally. These components should be connected as shown in Figure 2-4.

The internal analog circuitry in the PHY module requires that an external 2.32 k $\Omega$ , 1% resistor be attached from RBIAS to ground. The resistor influences the TPOUT+/-signal amplitude. The resistor should be placed as close as possible to the chip with no immediately adjacent signal traces to prevent noise capacitively coupling into the pin and affecting the transmit behavior. It is recommended that the resistor be a surface mount type.

Some of the device's digital logic operates at a nominal 2.5V. An on-chip voltage regulator is incorporated to generate this voltage. The only external component required is an external filter capacitor, connected from VCAP to ground. The capacitor must have low equivalent series resistance (ESR), with a typical value of 10  $\mu$ F, and a minimum value of 1  $\mu$ F. The internal regulator is not designed to drive external loads.

On the TPIN+/TPIN- and TPOUT+/TPOUT- pins, 1:1 center taped pulse transformers, rated for Ethernet operations, are required. When the Ethernet module is enabled, current is continually sunk through both TPOUT pins. When the PHY is actively transmitting, a differential voltage is created on the Ethernet cable by varying the relative current sunk by TPOUT+ compared to TPOUT-. A common-mode choke on the TPOUT interface, placed between the TPOUT pins and the Ethernet transformer (not shown), is not recommended. If a common-mode choke is used to reduce EMI emissions, it should be placed between the Ethernet transformer and pins 1 and 2 of the RJ-45 connector. Many Ethernet transformer modules include common-mode chokes inside the same device package. The transformers should have at least the isolation rating specified in Table 16-5 to protect against static voltages and meet IEEE 802.3 isolation requirements (see Section 16.0 "Electrical Character-istics" for specific transformer requirements). Both transmit and receive interfaces additionally require two resistors and a capacitor to properly terminate the transmission line, minimizing signal reflections.

All power supply pins must be externally connected to the same power source. Similarly, all ground references must be externally connected to the same ground node. Each VDD and Vss pin pair should have a 0.1  $\mu$ F ceramic bypass capacitor (not shown in the schematic) placed as close to the pins as possible.

Since relatively high currents are necessary to operate the twisted-pair interface, all wires should be kept as short as possible. Reasonable wire widths should be used on power wires to reduce resistive loss. If the differential data lines cannot be kept short, they should be routed in such a way as to have a  $100\Omega$  characteristic impedance.

#### FIGURE 2-4: ENC28J60 ETHERNET TERMINATION AND EXTERNAL CONNECTIONS

© 2006-2012 Microchip Technology Inc.

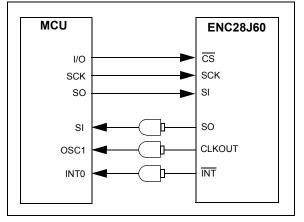

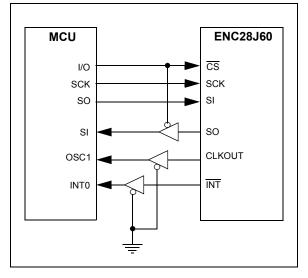

#### 2.5 I/O Levels

The ENC28J60 is a 3.3V part; however, it was designed to be easily integrated into 5V systems. The SPI CS, SCK and SI inputs, as well as the RESET pin, are all 5V tolerant. On the other hand, if the host controller is operated at 5V, it quite likely will not be within specifications when its SPI and interrupt inputs are driven by the 3.3V CMOS outputs on the ENC28J60. A unidirectional level translator would be necessary.

An economical 74HCT08 (quad AND gate), 74ACT125 (quad 3-state buffer) or many other 5V CMOS chips with TTL level input buffers may be used to provide the necessary level shifting. The use of 3-state buffers permits easy integration into systems which share the SPI bus with other devices. Figure 2-5 and Figure 2-6 show example translation schemes.

FIGURE 2-6:

LEVEL SHIFTING USING 3-STATE BUFFERS

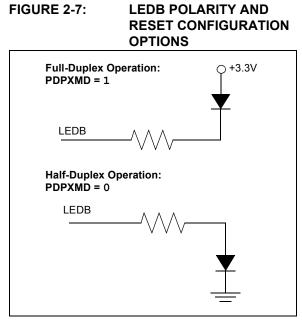

#### 2.6 LED Configuration

The LEDA and LEDB pins support automatic polarity detection on Reset. The LEDs can be connected such that the pin must source current to turn the LED on, or alternately connected such that the pin must sink current to turn the LED on. Upon system Reset, the ENC28J60 will detect how the LED is connected and begin driving the LED to the default state configured by the PHLCON register. If the LED polarity is changed while the ENC28J60 is operating, the new polarity will not be detected until the next system Reset occurs.

LEDB is unique in that the connection of the LED is automatically read on Reset and determines how to initialize the PHCON1.PDPXMD bit. If the pin sources current to illuminate the LED, the bit is cleared on Reset and the PHY defaults to half-duplex operation. If the pin sinks current to illuminate the LED, the bit is set on Reset and the PHY defaults to full-duplex operation. Figure 2-7 shows the two available options. If no LED is attached to the LEDB pin, the PDPXMD bit will reset to an indeterminate value.

The LEDs can also be configured separately to control their operating polarity (on or off when active), blink rate and blink stretch interval. The options are controlled by the LACFG<3:0> and LBCFG<3:0> bits. Typical values for blink stretch are listed in Table 2-1.

#### TABLE 2-1:LED BLINK STRETCH LENGTH

| Stretch Length   | Typical Stretch (ms) |

|------------------|----------------------|

| TNSTRCH (normal) | 40                   |

| Тмstrch (medium) | 70                   |

| TLSTRCH (long)   | 140                  |

| R/W-0            | R/W-0                                                                                                                                                                                                   | R/W-1                                                                                                                                                                                                                           | R/W-1                                                                                                                     | R/W-0             | R/W-1                                                                         | R/W-0            | R/W-0   |  |  |  |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------------------------------------------------------------------|------------------|---------|--|--|--|--|--|--|--|--|--|

| r                | r                                                                                                                                                                                                       | r                                                                                                                                                                                                                               | r                                                                                                                         | LACFG3            | LACFG2                                                                        | LACFG1           | LACFG0  |  |  |  |  |  |  |  |  |  |

| bit 15           |                                                                                                                                                                                                         |                                                                                                                                                                                                                                 |                                                                                                                           |                   |                                                                               |                  | bit 8   |  |  |  |  |  |  |  |  |  |

|                  |                                                                                                                                                                                                         |                                                                                                                                                                                                                                 |                                                                                                                           |                   |                                                                               |                  |         |  |  |  |  |  |  |  |  |  |

| R/W-0            | R/W-0                                                                                                                                                                                                   | R/W-1                                                                                                                                                                                                                           | R/W-0                                                                                                                     | R/W-0             | R/W-0                                                                         | R/W-1            | R/W-x   |  |  |  |  |  |  |  |  |  |

| LBCFG3           | LBCFG2                                                                                                                                                                                                  | LBCFG1                                                                                                                                                                                                                          | LBCFG0                                                                                                                    | LFRQ1             | LFRQ0                                                                         | STRCH            | r       |  |  |  |  |  |  |  |  |  |

| bit 7            |                                                                                                                                                                                                         |                                                                                                                                                                                                                                 |                                                                                                                           |                   |                                                                               |                  | bit C   |  |  |  |  |  |  |  |  |  |

|                  |                                                                                                                                                                                                         |                                                                                                                                                                                                                                 |                                                                                                                           |                   |                                                                               |                  |         |  |  |  |  |  |  |  |  |  |

| Legend:          |                                                                                                                                                                                                         | r = Reserved b                                                                                                                                                                                                                  | it                                                                                                                        |                   |                                                                               |                  |         |  |  |  |  |  |  |  |  |  |

| R = Readable     | e bit                                                                                                                                                                                                   | W = Writable b                                                                                                                                                                                                                  | it                                                                                                                        | U = Unimplem      | ented bit, read a                                                             | as '0'           |         |  |  |  |  |  |  |  |  |  |

| -n = Value at    | POR                                                                                                                                                                                                     | '1' = Bit is set                                                                                                                                                                                                                |                                                                                                                           | '0' = Bit is clea | red                                                                           | x = Bit is unkno | wn      |  |  |  |  |  |  |  |  |  |

|                  |                                                                                                                                                                                                         |                                                                                                                                                                                                                                 |                                                                                                                           |                   |                                                                               |                  |         |  |  |  |  |  |  |  |  |  |

| bit 15-14        | Reserved: Wr                                                                                                                                                                                            | ite as '0'                                                                                                                                                                                                                      |                                                                                                                           |                   |                                                                               |                  |         |  |  |  |  |  |  |  |  |  |

| bit 13-12        | Reserved: Wr                                                                                                                                                                                            | ite as '1'                                                                                                                                                                                                                      |                                                                                                                           |                   |                                                                               |                  |         |  |  |  |  |  |  |  |  |  |

| bit 11-8         |                                                                                                                                                                                                         | LEDA Configur                                                                                                                                                                                                                   | ation bits                                                                                                                |                   |                                                                               |                  |         |  |  |  |  |  |  |  |  |  |

|                  | 1111 = Reserv                                                                                                                                                                                           | ved<br>y duplex status :                                                                                                                                                                                                        | and collision as                                                                                                          | tivity (alwave of | retched)                                                                      |                  |         |  |  |  |  |  |  |  |  |  |

|                  |                                                                                                                                                                                                         | y link status and                                                                                                                                                                                                               |                                                                                                                           |                   |                                                                               |                  |         |  |  |  |  |  |  |  |  |  |

|                  | 1100 = Displa                                                                                                                                                                                           | y link status and                                                                                                                                                                                                               |                                                                                                                           |                   |                                                                               |                  |         |  |  |  |  |  |  |  |  |  |

|                  | 1011 = Blink s                                                                                                                                                                                          |                                                                                                                                                                                                                                 |                                                                                                                           |                   |                                                                               |                  |         |  |  |  |  |  |  |  |  |  |

|                  | 1010 = Blink 1<br>1001 = Off                                                                                                                                                                            | 1010 = Blink fast                                                                                                                                                                                                               |                                                                                                                           |                   |                                                                               |                  |         |  |  |  |  |  |  |  |  |  |

|                  | 1000 <b>= On</b>                                                                                                                                                                                        |                                                                                                                                                                                                                                 |                                                                                                                           |                   |                                                                               |                  |         |  |  |  |  |  |  |  |  |  |

|                  | 0111 = Display transmit and receive activity (stretchable)                                                                                                                                              |                                                                                                                                                                                                                                 |                                                                                                                           |                   |                                                                               |                  |         |  |  |  |  |  |  |  |  |  |

|                  | 0110 = Reserved<br>0101 = Display duplex status                                                                                                                                                         |                                                                                                                                                                                                                                 |                                                                                                                           |                   |                                                                               |                  |         |  |  |  |  |  |  |  |  |  |

|                  | 0100 = Display link status                                                                                                                                                                              |                                                                                                                                                                                                                                 |                                                                                                                           |                   |                                                                               |                  |         |  |  |  |  |  |  |  |  |  |

|                  |                                                                                                                                                                                                         | y collision activit                                                                                                                                                                                                             |                                                                                                                           |                   |                                                                               |                  |         |  |  |  |  |  |  |  |  |  |

|                  |                                                                                                                                                                                                         | y receive activity<br>y transmit activity                                                                                                                                                                                       |                                                                                                                           |                   |                                                                               |                  |         |  |  |  |  |  |  |  |  |  |

|                  | 00001 <b>– Displa</b>                                                                                                                                                                                   |                                                                                                                                                                                                                                 | ly (Stretchable)                                                                                                          |                   |                                                                               |                  |         |  |  |  |  |  |  |  |  |  |

| bit 7-4          | LBCFG<3:0>:                                                                                                                                                                                             | LEDB Configur                                                                                                                                                                                                                   | ation bits                                                                                                                |                   |                                                                               |                  |         |  |  |  |  |  |  |  |  |  |

|                  | 1110 <b>= Displa</b>                                                                                                                                                                                    | y duplex status                                                                                                                                                                                                                 | and collision ac                                                                                                          |                   |                                                                               |                  |         |  |  |  |  |  |  |  |  |  |

|                  | 1101 = Display link status and transmit/receive activity (always stretched)                                                                                                                             |                                                                                                                                                                                                                                 |                                                                                                                           |                   |                                                                               |                  |         |  |  |  |  |  |  |  |  |  |

|                  | 1100 = Display link status and receive activity (always stretched)<br>1011 = Blink slow                                                                                                                 |                                                                                                                                                                                                                                 |                                                                                                                           |                   |                                                                               |                  |         |  |  |  |  |  |  |  |  |  |

|                  | 1011 = Blink slow                                                                                                                                                                                       |                                                                                                                                                                                                                                 |                                                                                                                           |                   |                                                                               |                  |         |  |  |  |  |  |  |  |  |  |

|                  | 1001 <b>= Off</b>                                                                                                                                                                                       |                                                                                                                                                                                                                                 |                                                                                                                           |                   |                                                                               |                  |         |  |  |  |  |  |  |  |  |  |

|                  | 1000 = On                                                                                                                                                                                               |                                                                                                                                                                                                                                 |                                                                                                                           |                   |                                                                               |                  |         |  |  |  |  |  |  |  |  |  |

|                  |                                                                                                                                                                                                         |                                                                                                                                                                                                                                 | conversional activity (                                                                                                   | stretenable)      | 0111 = Display transmit and receive activity (stretchable)<br>0110 = Reserved |                  |         |  |  |  |  |  |  |  |  |  |

|                  | 0101 = Display duplex status                                                                                                                                                                            |                                                                                                                                                                                                                                 |                                                                                                                           |                   |                                                                               |                  |         |  |  |  |  |  |  |  |  |  |

|                  |                                                                                                                                                                                                         |                                                                                                                                                                                                                                 |                                                                                                                           |                   |                                                                               |                  |         |  |  |  |  |  |  |  |  |  |

|                  | 0100 <b>= Displa</b>                                                                                                                                                                                    | y link status                                                                                                                                                                                                                   | a (stratababla)                                                                                                           |                   |                                                                               |                  |         |  |  |  |  |  |  |  |  |  |

|                  | 0100 <b>= Displa</b><br>0011 <b>= Displa</b>                                                                                                                                                            | y link status<br>y collision activi                                                                                                                                                                                             |                                                                                                                           |                   |                                                                               |                  |         |  |  |  |  |  |  |  |  |  |

|                  | 0100 = Displa<br>0011 = Displa<br>0010 = Displa<br>0001 = Displa                                                                                                                                        | y link status<br>y collision activit<br>y receive activity<br>y transmit activity                                                                                                                                               | (stretchable)                                                                                                             |                   |                                                                               |                  |         |  |  |  |  |  |  |  |  |  |

|                  | 0100 = Displa<br>0011 = Displa<br>0010 = Displa<br>0001 = Displa<br>0000 = Reserv                                                                                                                       | y link status<br>y collision activit<br>y receive activit<br>y transmit activit<br>ved                                                                                                                                          | y (stretchable)<br>y (stretchable)                                                                                        |                   |                                                                               |                  |         |  |  |  |  |  |  |  |  |  |

| bit 3-2          | 0100 = Displa<br>0011 = Displa<br>0010 = Displa<br>0001 = Displa<br>0000 = Reserv                                                                                                                       | y link status<br>y collision activit<br>y receive activit<br>y transmit activit<br>ved<br>.ED Pulse Streto                                                                                                                      | y (stretchable)<br>y (stretchable)                                                                                        | ration bits (see  | Table 2-1)                                                                    |                  |         |  |  |  |  |  |  |  |  |  |

| bit 3-2          | 0100 = Displa<br>0011 = Displa<br>0010 = Displa<br>0001 = Displa<br>0000 = Reserved<br>LFRQ<1:0>: L<br>11 = Reserved                                                                                    | y link status<br>y collision activit<br>y receive activit<br>y transmit activit<br>ved<br>.ED Pulse Streto                                                                                                                      | y (stretchable)<br>ty (stretchable)<br>th Time Configu                                                                    | ration bits (see  | Table 2-1)                                                                    |                  |         |  |  |  |  |  |  |  |  |  |

| bit 3-2          | 0100 = Displa<br>0011 = Displa<br>0010 = Displa<br>0001 = Displa<br>0000 = Reserved<br>LFRQ<1:0>: L<br>11 = Reserved<br>10 = Stretch L                                                                  | y link status<br>y collision activit<br>y receive activit<br>y transmit activit<br>ved<br>ED Pulse Stretc<br>b<br>ED events by Ti                                                                                               | y (stretchable)<br>ty (stretchable)<br>th Time Configu<br>STRCH                                                           | ration bits (see  | Table 2-1)                                                                    |                  |         |  |  |  |  |  |  |  |  |  |

| bit 3-2          | 0100 = Displa<br>0011 = Displa<br>0010 = Displa<br>0001 = Displa<br>0000 = Reserved<br>LFRQ<1:0>: L<br>11 = Reserved<br>10 = Stretch L<br>01 = Stretch L                                                | y link status<br>y collision activit<br>y receive activit<br>y transmit activit<br>ved<br>.ED Pulse Streto                                                                                                                      | y (stretchable)<br>ty (stretchable)<br>th Time Configu<br>strch<br>wstrch                                                 | ration bits (see  | Table 2-1)                                                                    |                  |         |  |  |  |  |  |  |  |  |  |

| bit 3-2<br>bit 1 | 0100 = Displa<br>0011 = Displa<br>0010 = Displa<br>0001 = Displa<br>0000 = Reserv<br>LFRQ<1:0>: L<br>11 = Reserved<br>10 = Stretch L<br>01 = Stretch L<br>00 = Stretch L                                | y link status<br>y collision activity<br>y receive activity<br>y transmit activity<br>ved<br>ED Pulse Stretc<br>D<br>ED events by Ti<br>ED events by Ti                                                                         | y (stretchable)<br>ty (stretchable)<br>th Time Configu<br>.strch<br>MSTRCH<br>MSTRCH                                      | ration bits (see  | Table 2-1)                                                                    |                  |         |  |  |  |  |  |  |  |  |  |

|                  | 0100 = Displa<br>0011 = Displa<br>0010 = Displa<br>0001 = Displa<br>0000 = Reserv<br>LFRQ<1:0>: L<br>11 = Reserved<br>10 = Stretch L<br>01 = Stretch L<br>00 = Stretch L<br>STRCH: LED<br>1 = Stretchab | y link status<br>y collision activity<br>y receive activity<br>y transmit activity<br>ed<br>ED Pulse Stretco<br>D<br>ED events by Th<br>ED events by Th<br>Pulse Stretching<br>le LED events w                                  | y (stretchable)<br>ty (stretchable)<br>th Time Configu<br>ISTRCH<br>MSTRCH<br>NSTRCH<br>I Enable bit<br>vill cause length | ened LED pulse    | es based on LFF                                                               | RQ<1:0> configu  | ıration |  |  |  |  |  |  |  |  |  |

|                  | 0100 = Displa<br>0011 = Displa<br>0010 = Displa<br>0001 = Displa<br>0000 = Reserv<br>LFRQ<1:0>: L<br>11 = Reserved<br>10 = Stretch L<br>01 = Stretch L<br>00 = Stretch L<br>STRCH: LED<br>1 = Stretchab | y link status<br>y collision activity<br>y receive activity<br>y transmit activity<br>ed<br>ED Pulse Stretco<br>ED events by Th<br>ED events by Th<br>ED events by Th<br>Pulse Stretching<br>le LED events w<br>le LED events w | y (stretchable)<br>ty (stretchable)<br>th Time Configu<br>ISTRCH<br>MSTRCH<br>NSTRCH<br>I Enable bit<br>vill cause length | ened LED pulse    | es based on LFF                                                               | RQ<1:0> configu  | iration |  |  |  |  |  |  |  |  |  |

·

$\ensuremath{\textcircled{}^{\odot}}$  2006-2012 Microchip Technology Inc.

NOTES:

·

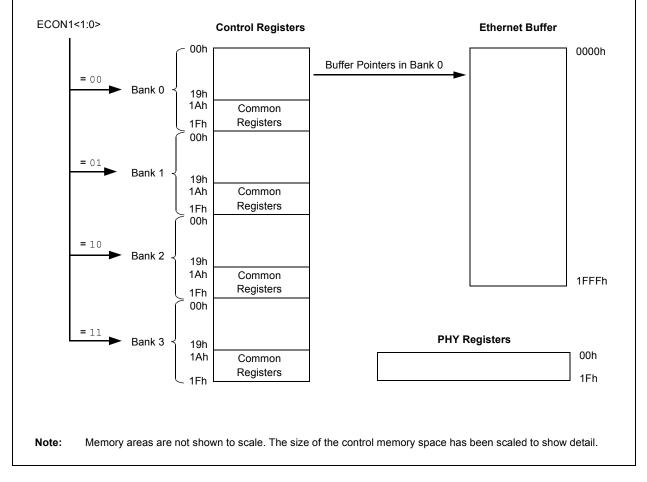

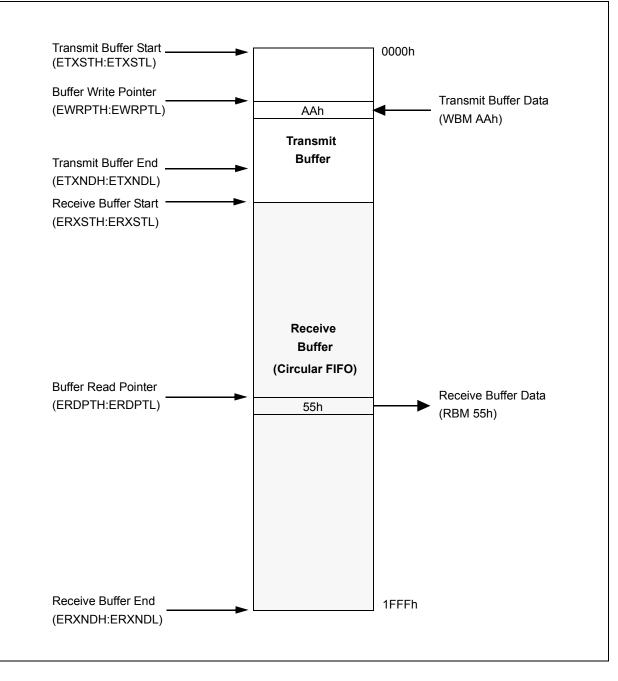

#### 3.0 MEMORY ORGANIZATION

All memory in the ENC28J60 is implemented as static RAM. There are three types of memory in the ENC28J60:

- · Control Registers

- · Ethernet Buffer

- PHY Registers

The Control registers' memory contains the registers that are used for configuration, control and status retrieval of the ENC28J60. The Control registers are directly read and written to by the SPI interface. The Ethernet buffer contains transmit and receive memory used by the Ethernet controller in a single memory space. The sizes of the memory areas are programmable by the host controller using the SPI interface. The Ethernet buffer memory can only be accessed via the read buffer memory and write buffer memory SPI commands (see Section 4.2.2 "Read Buffer Memory Command" and Section 4.2.4 "Write Buffer Memory Command").

The PHY registers are used for configuration, control and status retrieval of the PHY module. The registers are not directly accessible through the SPI interface; they can only be accessed through Media Independent Interface Management (MIIM) implemented in the MAC.

Figure 3-1 shows the data memory organization for the ENC28J60.

#### FIGURE 3-1: ENC28J60 MEMORY ORGANIZATION

<sup>© 2006-2012</sup> Microchip Technology Inc.

#### 3.1 Control Registers

The Control registers provide the main interface between the host controller and the on-chip Ethernet controller logic. Writing to these registers controls the operation of the interface, while reading the registers allows the host controller to monitor operations.

The Control register memory is partitioned into four banks, selectable by the bank select bits, BSEL<1:0>, in the ECON1 register. Each bank is 32 bytes long and addressed by a 5-bit address value.

The last five locations (1Bh to 1Fh) of all banks point to a common set of registers: EIE, EIR, ESTAT, ECON2 and ECON1. These are key registers used in controlling and monitoring the operation of the device. Their common mapping allows easy access without switching the bank. The ECON1 and ECON2 registers are discussed later in this section.

Some of the available addresses are unimplemented. Any attempts to write to these locations are ignored while reads return '0's. The register at address 1Ah in each bank is reserved; read and write operations should not be performed on this register. All other reserved registers may be read, but their contents must not be changed. When reading and writing to registers which contain reserved bits, any rules stated in the register definition should be observed.

Control registers for the ENC28J60 are generically grouped as ETH, MAC and MII registers. Register names starting with "E" belong to the ETH group. Similarly, registers names starting with "MA" belong to the MAC group and registers prefixed with "MI" belong to the MII group.

#### TABLE 3-1: ENC28J60 CONTROL REGISTER MAP

| Bank 0  |          | Bank 1  |          | Bank 2  |          | Bank 3  |          |  |

|---------|----------|---------|----------|---------|----------|---------|----------|--|

| Address | Name     | Address | Name     | Address | Name     | Address | Name     |  |

| 00h     | ERDPTL   | 00h     | EHT0     | 00h     | MACON1   | 00h     | MAADR5   |  |

| 01h     | ERDPTH   | 01h     | EHT1     | 01h     | Reserved | 01h     | MAADR6   |  |

| 02h     | EWRPTL   | 02h     | EHT2     | 02h     | MACON3   | 02h     | MAADR3   |  |

| 03h     | EWRPTH   | 03h     | EHT3     | 03h     | MACON4   | 03h     | MAADR4   |  |

| 04h     | ETXSTL   | 04h     | EHT4     | 04h     | MABBIPG  | 04h     | MAADR1   |  |

| 05h     | ETXSTH   | 05h     | EHT5     | 05h     | —        | 05h     | MAADR2   |  |

| 06h     | ETXNDL   | 06h     | EHT6     | 06h     | MAIPGL   | 06h     | EBSTSD   |  |

| 07h     | ETXNDH   | 07h     | EHT7     | 07h     | MAIPGH   | 07h     | EBSTCON  |  |

| 08h     | ERXSTL   | 08h     | EPMM0    | 08h     | MACLCON1 | 08h     | EBSTCSL  |  |

| 09h     | ERXSTH   | 09h     | EPMM1    | 09h     | MACLCON2 | 09h     | EBSTCSH  |  |

| 0Ah     | ERXNDL   | 0Ah     | EPMM2    | 0Ah     | MAMXFLL  | 0Ah     | MISTAT   |  |

| 0Bh     | ERXNDH   | 0Bh     | EPMM3    | 0Bh     | MAMXFLH  | 0Bh     | —        |  |

| 0Ch     | ERXRDPTL | 0Ch     | EPMM4    | 0Ch     | Reserved | 0Ch     | —        |  |

| 0Dh     | ERXRDPTH | 0Dh     | EPMM5    | 0Dh     | Reserved | 0Dh     | _        |  |

| 0Eh     | ERXWRPTL | 0Eh     | EPMM6    | 0Eh     | Reserved | 0Eh     | —        |  |

| 0Fh     | ERXWRPTH | 0Fh     | EPMM7    | 0Fh     | —        | 0Fh     | —        |  |

| 10h     | EDMASTL  | 10h     | EPMCSL   | 10h     | Reserved | 10h     | _        |  |

| 11h     | EDMASTH  | 11h     | EPMCSH   | 11h     | Reserved | 11h     | _        |  |

| 12h     | EDMANDL  | 12h     | —        | 12h     | MICMD    | 12h     | EREVID   |  |

| 13h     | EDMANDH  | 13h     | —        | 13h     | —        | 13h     | _        |  |

| 14h     | EDMADSTL | 14h     | EPMOL    | 14h     | MIREGADR | 14h     | _        |  |

| 15h     | EDMADSTH | 15h     | EPMOH    | 15h     | Reserved | 15h     | ECOCON   |  |

| 16h     | EDMACSL  | 16h     | Reserved | 16h     | MIWRL    | 16h     | Reserved |  |

| 17h     | EDMACSH  | 17h     | Reserved | 17h     | MIWRH    | 17h     | EFLOCON  |  |

| 18h     | _        | 18h     | ERXFCON  | 18h     | MIRDL    | 18h     | EPAUSL   |  |

| 19h     | _        | 19h     | EPKTCNT  | 19h     | MIRDH    | 19h     | EPAUSH   |  |

| 1Ah     | Reserved | 1Ah     | Reserved | 1Ah     | Reserved | 1Ah     | Reserved |  |

| 1Bh     | EIE      | 1Bh     | EIE      | 1Bh     | EIE      | 1Bh     | EIE      |  |

| 1Ch     | EIR      | 1Ch     | EIR      | 1Ch     | EIR      | 1Ch     | EIR      |  |

| 1Dh     | ESTAT    | 1Dh     | ESTAT    | 1Dh     | ESTAT    | 1Dh     | ESTAT    |  |

| 1Eh     | ECON2    | 1Eh     | ECON2    | 1Eh     | ECON2    | 1Eh     | ECON2    |  |

| 1Fh     | ECON1    | 1Fh     | ECON1    | 1Fh     | ECON1    | 1Fh     | ECON1    |  |

| Register Name | Bit 7                                       | Bit 6          | Bit 5      | Bit 4         | Bit 3          | Bit 2       | Bit 1  | Bit 0                 | Value<br>on<br>Reset | Details<br>on<br>Page |

|---------------|---------------------------------------------|----------------|------------|---------------|----------------|-------------|--------|-----------------------|----------------------|-----------------------|

| EIE           | INTIE                                       | PKTIE          | DMAIE      | LINKIE        | TXIE           | r           | TXERIE | RXERIE                | 0000 0000            | 65                    |

| EIR           | _                                           | PKTIF          | DMAIF      | LINKIF        | TXIF           | r           | TXERIF | RXERIF                | -000 0000            | 66                    |

| ESTAT         | INT                                         | BUFER          | r          | LATECOL       | _              | RXBUSY      | TXABRT | CLKRDY <sup>(1)</sup> | 0000 -000            | 64                    |

| ECON2         | AUTOINC                                     | PKTDEC         | PWRSV      | r             | VRPS           | _           | _      | _                     | 1000 0               | 16                    |

| ECON1         | TXRST                                       | RXRST          | DMAST      | CSUMEN        | TXRTS          | RXEN        | BSEL1  | BSEL0                 | 0000 0000            | 15                    |

| ERDPTL        | Read Pointer                                | Low Byte ER    | DPT<7:0>)  |               |                |             |        |                       | 1111 1010            | 17                    |

| ERDPTH        | —                                           | —              | _          | Read Pointer  | High Byte (E   | RDPT<12:8>) |        |                       | 0 0101               | 17                    |

| EWRPTL        | Write Pointer                               | Low Byte (EV   | VRPT<7:0>) |               |                |             |        |                       | 0000 0000            | 17                    |

| EWRPTH        | _                                           | _              | _          | Write Pointer | High Byte (E   | WRPT<12:8>) |        |                       | 0 0000               | 17                    |

| ETXSTL        | TX Start Low                                | Byte (ETXST    | <7:0>)     |               |                |             |        |                       | 0000 0000            | 17                    |

| ETXSTH        | —                                           | —              | _          | TX Start High | Byte (ETXST    | 「<12:8>)    |        |                       | 0 0000               | 17                    |

| ETXNDL        | TX End Low                                  | Byte (ETXND    | <7:0>)     |               |                |             |        |                       | 0000 0000            | 17                    |

| ETXNDH        | —                                           | —              | _          | TX End High   | Byte (ETXND    | )<12:8>)    |        |                       | 0 0000               | 17                    |

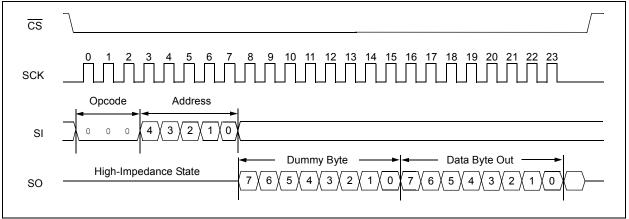

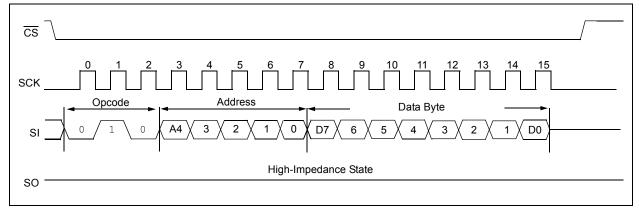

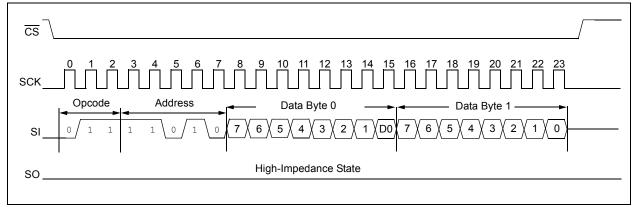

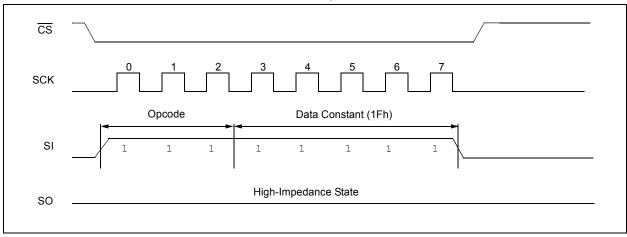

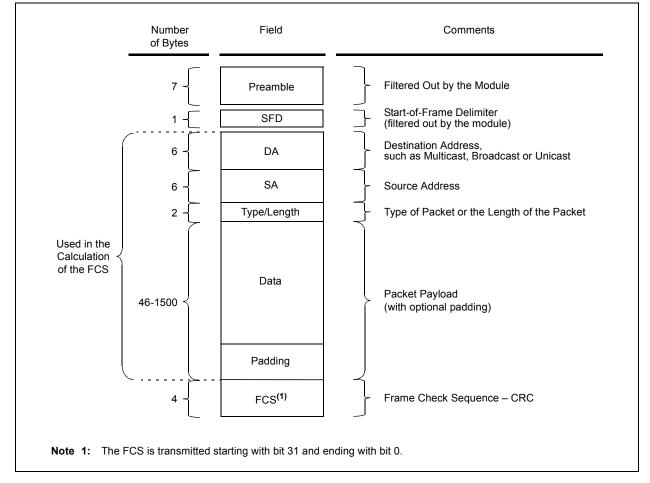

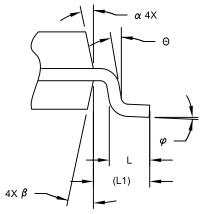

| ERXSTL        | RX Start Low                                | Byte (ERXST    | <7:0>)     |               |                |             |        |                       | 1111 1010            | 17                    |