# AN2816 Application note

# High-efficiency step-down controller with embedded 2 A LDO regulator

#### Introduction

The PM6675S device consists of a single, high-efficiency step-down controller and an independent low dropout (LDO) linear regulator.

The constant on-time (COT) architecture assures fast transient response supporting both electrolytic and ceramic output capacitors. An embedded integrator control loop compensates the DC voltage error due to the output ripple.

Selectable low-consumption mode allows the highest efficiency over a wide range of load conditions. The low-noise mode sets the minimum switching frequency to 33 kHz for audio-sensitive applications. The LDO linear regulator can sink and source up to 2 Apk. Two fixed current limits ( $\pm 1$  A and  $\pm 2$  A) can be chosen.

An active soft-end is independently performed on both the switching and the linear regulators outputs when disabled.

Figure 1. PM6675S demonstration board

Contents AN2816

## **Contents**

| 1  | Main   | features                                                       |

|----|--------|----------------------------------------------------------------|

|    | 1.1    | Switching section 5                                            |

|    | 1.2    | LDO section                                                    |

| 2  | Eval   | uation kit schematic6                                          |

| 3  | Bill   | of material7                                                   |

| 4  | Com    | ponent assembly and layout9                                    |

| 5  | l/O ir | nterface                                                       |

| 6  | Reco   | ommended equipment13                                           |

| 7  | Conf   | iguration                                                      |

|    | 7.1    | JP3 fixed or adjustable output voltage (VSEL pin)              |

|    | 7.2    | JP1 power-saving mode (NOSKIP pin)                             |

|    | 7.3    | JP2 current limit (LILIM pin)                                  |

|    | 7.4    | JP5 compensation network (COMP pin)                            |

| 8  | Test   | setup                                                          |

| 9  | Getti  | ng started                                                     |

| 10 | PM6    | 675S demonstration tests                                       |

|    | 10.1   | V <sub>OUT</sub> and L <sub>OUT</sub> turn-on (soft-start)     |

|    | 10.2   | V <sub>OUT</sub> working mode                                  |

|    | 10.3   | V <sub>OUT</sub> and L <sub>OUT</sub> load regulation 24       |

|    | 10.4   | V <sub>OUT</sub> and L <sub>OUT</sub> load transient responses |

|    | 10.5   | V <sub>OUT</sub> efficiency                                    |

|    | 10.6   | V <sub>OUT</sub> gate drivers                                  |

|    | 10.7   | V <sub>OUT</sub> and L <sub>OUT</sub> turn-off (soft-end)      |

|    | 10.8   | UV, OV and thermal protections                                 |

|    |        |                                                                |

| AN2816 | C     |                                           |    |

|--------|-------|-------------------------------------------|----|

|        | 10.9  | V <sub>OUT</sub> current limit            | 32 |

|        | 10.10 | L <sub>OUT</sub> current limit (foldback) | 33 |

|        | 10.11 | Switching frequency                       | 34 |

| 11     | Revis | sion history                              | 35 |

List of figures AN2816

# **List of figures**

| Figure 1.  | PM6675S demonstration board                                                                                   | . 1 |

|------------|---------------------------------------------------------------------------------------------------------------|-----|

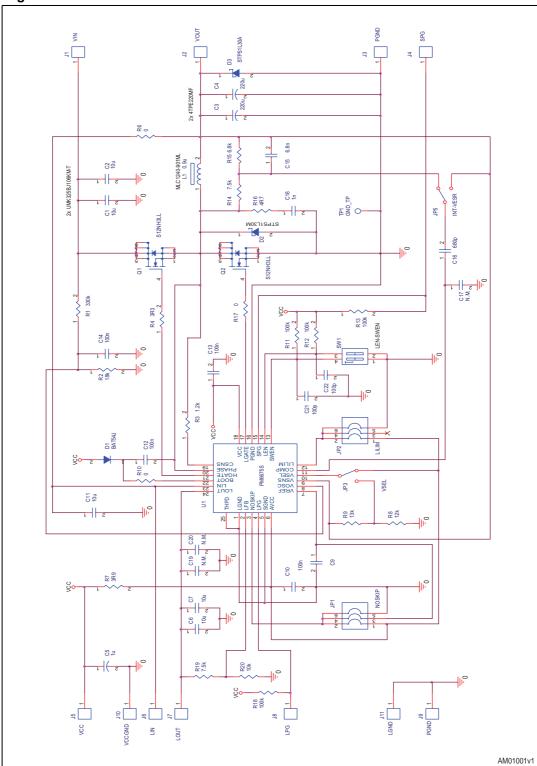

| Figure 2.  | PM6675S demonstration board schematic                                                                         | . 6 |

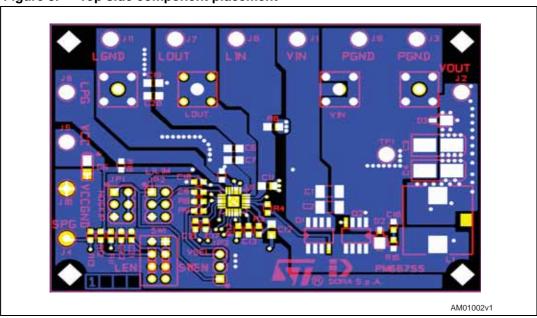

| Figure 3.  | Top side component placement                                                                                  | . 9 |

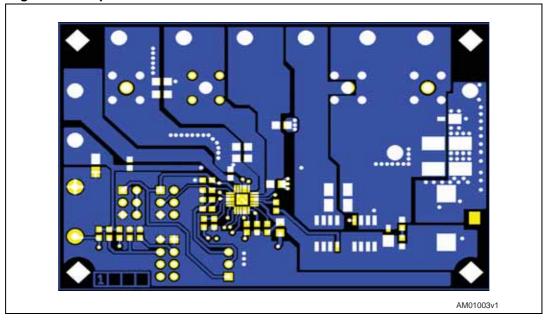

| Figure 4.  | Top view                                                                                                      | . 9 |

| Figure 5.  | Layer 2 view                                                                                                  | 10  |

| Figure 6.  | Layer 3 view                                                                                                  | 10  |

| Figure 7.  | Bottom view                                                                                                   | 11  |

| Figure 8.  | Bottom side component placement                                                                               | 11  |

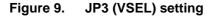

| Figure 9.  | JP3 (VSEL) setting                                                                                            | 14  |

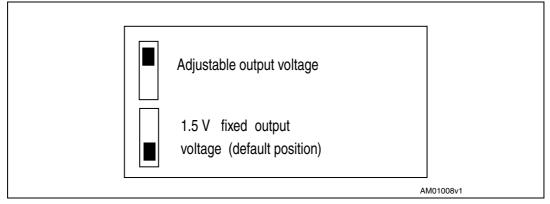

| Figure 10. | JP1 (NOSKIP) setting                                                                                          | 15  |

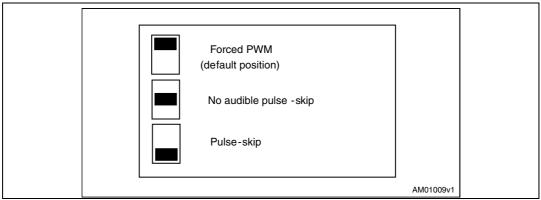

| Figure 11. | JP2 (LILIM) setting                                                                                           | 15  |

| Figure 12. | JP5 (COMP) setting                                                                                            | 16  |

| Figure 13. | PM6675S demonstration board test setup                                                                        |     |

| Figure 14. | VOUT soft-start at 270 mW load, pulse-skip mode                                                               | 19  |

| Figure 15. | L <sub>OUT</sub> turn-on, V <sub>OUT</sub> in pulse-skip mode                                                 | 20  |

| Figure 16. | V <sub>OUT</sub> = 1.5 V, V <sub>IN</sub> = 12 V, I <sub>VOUT</sub> = 0 A, forced-PWM mode                    | 21  |

| Figure 17. | $V_{OUT} = 1.5 \text{ V}, V_{IN} = 12 \text{ V}, I_{VOUT} = 0 \text{ A}, \text{ pulse-skip mode} \dots$       |     |

| Figure 18. | V <sub>OUT</sub> = 1.5 V, V <sub>IN</sub> = 12 V, no load, non-audible pulse-skip mode (33 kHz)               | 23  |

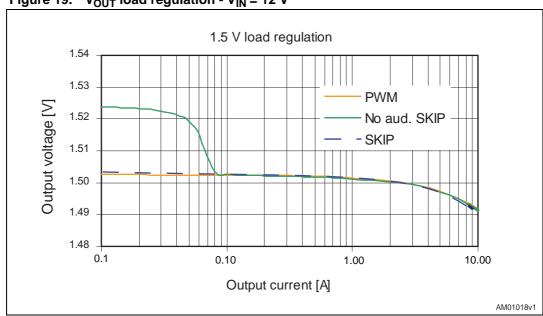

| Figure 19. | V <sub>OUT</sub> load regulation - V <sub>IN</sub> = 12 V                                                     | 24  |

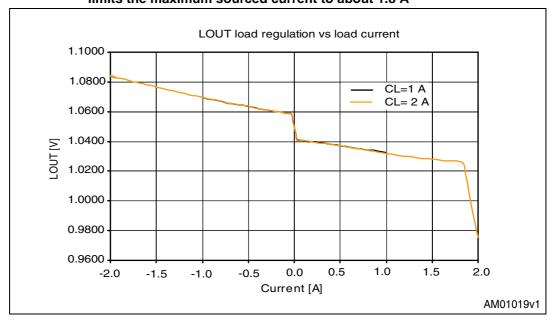

| Figure 20. | $L_{OUT}$ load regulation - LDOIN = 1.5 ( $V_{OUT}$ ), he dropout voltage (0.35 V) limits the                 |     |

|            | maximum sourced current to about 1.8 A                                                                        |     |

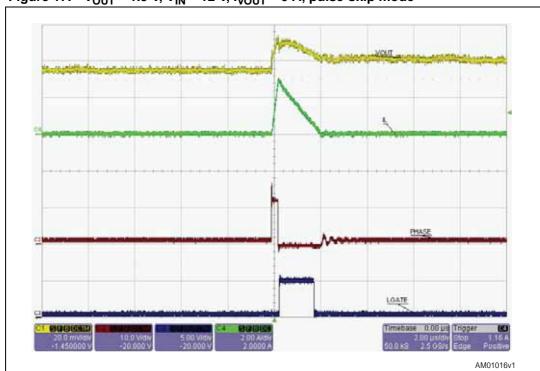

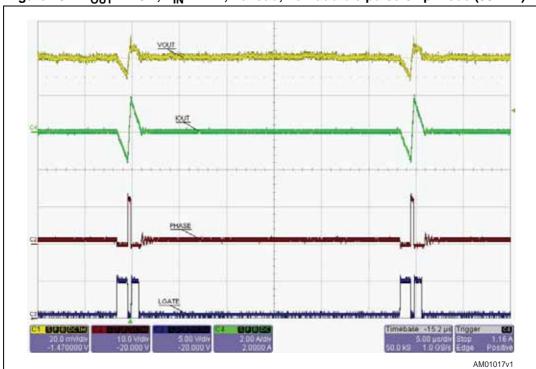

| Figure 21. | $V_{OUT}$ load transient ( $V_{IN}$ = 12 V, LOAD = 0 A to 8 A at 2.5 A/ $\mu$ s), pulse-skip mode             |     |

| Figure 22. | $V_{OUT}$ load transient ( $V_{IN}$ = 12 V, LOAD = 8 A to 0 A at 2.5 A/ $\mu$ s), pulse-skip mode             |     |

| Figure 23. | $L_{OUT}$ load transient ( $V_{IN}$ = 12 V, LOAD = 1.8 A to 1.85 A at 2.5 A/ $\mu$ s), pulse-skip mode        | 25  |

| Figure 24. | Forced PWM (blue), non-audible pulse-skip (green), pulse-skip (red), efficiency vs.                           |     |

|            | output current                                                                                                |     |

| Figure 25. | External MOSFET gate signals (V <sub>IN</sub> = 12 V, LOAD = 0), pulse-skip mode                              |     |

| Figure 26. | External MOSFET gate signals (V <sub>IN</sub> = 12 V, LOAD = 7 A), pulse-skip mode                            |     |

| Figure 27. | V <sub>OUT</sub> and L <sub>OUT</sub> output voltages V <sub>OUT</sub> soft-end                               |     |

| Figure 28. | V <sub>OUT</sub> and L <sub>OUT</sub> output voltages, L <sub>OUT</sub> soft-end                              |     |

| Figure 29. | UV protection, pulse-skip mode                                                                                |     |

| Figure 30. | OV protection, pulse-skip mode                                                                                |     |

| Figure 31. | $V_{OUT}$ and $L_{OUT}$ rails, thermal shutdown, pulse-skip mode, $L_{OUT}$ powered by $V_{OUT}$              |     |

| Figure 32. | $V_{OUT}$ current limit protection during a load transient (0 A to 9 A at 2.5 A/ $\mu$ s, valley current      |     |

|            | limit programmed at about 9 A (R <sub>ILIM</sub> = 1 kW) pulse-skip mode                                      |     |

| Figure 33. | L <sub>OUT</sub> current limit during an output short                                                         |     |

| Figure 34. | Switching frequency vs. input voltage, $V_{OUT} = 1.5 \text{ V}$ , $I_{VOUT} = 7 \text{ A}$ , forced PWM mode | 34  |

| Figure 35. | Switching frequency vs. output current, V <sub>OUT</sub> = 1.5 V, V <sub>IN</sub> = 12 V                      | 34  |

4/36

AN2816 Main features

### 1 Main features

### 1.1 Switching section

- 4.5 V to 28 V input voltage range

- 0.6 V, ±1% voltage reference

- 1.5 V fixed output voltage

- 0.6 V to 3.3 V adjustable output voltage

- 1.237 V ±1% reference voltage available

- Very fast load transient response constant on-time loop control

- No-R<sub>SENSE</sub> current sensing using low-side MOSFETs' R<sub>DS(on)</sub>

- Negative current limit

- Latched OVP, UVP and thermal shutdown

- Fixed 3 ms soft-start

- Selectable pulse-skipping at light load

- Selectable non-audible (33 kHz) pulse-skip mode

- All ceramic output capacitor applications supported

- Output voltage ripple compensation

- Output soft-end

#### 1.2 LDO section

- 0.6 V to 3.3 V adjustable output voltage

- Selectable ±1 A or ±2 A current limit

- Dedicated Power Good signal

- Ceramic output capacitors supported

- Output soft-end

Evaluation kit schematic AN2816

## 2 Evaluation kit schematic

Figure 2. PM6675S demonstration board schematic

AN2816 Bill of material

# 3 Bill of material

Table 1. PM6675S demonstration board bill of material

| Qty | Component            | Description              | Package         | Part number         | Manufacturer | Value  |

|-----|----------------------|--------------------------|-----------------|---------------------|--------------|--------|

| 2   | C1, C2               | Ceramic, 50 V, X5R, 20%  | SMD<br>1210     | UMK325BJ106K<br>M-T | Taiyo Yuden  | 10 μF  |

| 2   | C3, C4               | POSCAP, 4 V,15 mΩ, 20%   | SMD<br>7343 (D) | 4TPE220MF           | Sanyo        | 220 μF |

| 1   | C5                   | Ceramic, 6.3 V, X5R, 10% | SMD<br>3216-12  |                     | Standard     | 1 μF   |

| 3   | C6, C7, C11          | Ceramic, 6.3 V, X5R, 10% | SMD<br>0805     | JMK212BJ106K<br>G-T | Taiyo Yuden  | 10 μF  |

| 4   | C9, C10,<br>C13, C14 | Ceramic, 50 V, X7R, 20%  | SMD<br>0603     |                     | Standard     | 100 nF |

| 1   | C12                  | Ceramic, 50 V, X7R, 10%  | SMD<br>0805     |                     | Standard     | 100 nF |

| 1   | C15                  | Ceramic, 50 V, X7R, 10%  | SMD<br>0603     |                     | Standard     | 6n8    |

| 1   | C16                  | Ceramic, 50 V, X7R, 10%  | SMD<br>0603     |                     | Standard     | 680 p  |

| 1   | C17                  | Ceramic, 20%             | SMD<br>0603     |                     | Standard     | N.M    |

| 1   | C18                  | Ceramic, 50 V , X7R, 10% | SMD<br>0805     |                     | Standard     | 1 nF   |

| 2   | C19, C20             | Ceramic, 6.3 V, X5R, 10% | SMD<br>0805     | JMK212BJ106K<br>G-T | Taiyo Yuden  | N.M    |

| 2   | C21, C22             | Ceramic, 50 V, X7R, 10%  | SMD<br>0603     |                     | Standard     | 100 pF |

| 1   | R1                   | Chip resistor, 0.1 W, 1% | SMD<br>0603     |                     | Standard     | 300 kΩ |

| 1   | R2                   | Chip resistor, 0.1 W, 1% | SMD<br>0603     |                     | Standard     | 18 kΩ  |

| 1   | R3                   | Chip resistor, 0.1 W, 1% | SMD<br>0603     |                     | Standard     | 1.2 kΩ |

| 1   | R4                   | Chip resistor, 0.1 W, 1% | SMD<br>0603     |                     | Standard     | 3R3    |

| 1   | R6                   | Chip resistor, 0.1 W, 1% | SMD<br>0805     |                     | Standard     | 0      |

| 1   | R7                   | Chip resistor, 0.1 W, 1% | SMD<br>0603     |                     | Standard     | 3R9    |

| 1   | R8                   | Chip resistor, 0.1 W, 1% | SMD<br>0603     |                     | Standard     | 12 kΩ  |

7/36

Bill of material AN2816

Table 1. PM6675S demonstration board bill of material (continued)

| Qty | Component                                            | Description                       | Package                      | Part number       | Manufacturer       | Value      |

|-----|------------------------------------------------------|-----------------------------------|------------------------------|-------------------|--------------------|------------|

| 1   | R9                                                   | Chip resistor, 0.1 W, 1%          | SMD<br>0603                  |                   | Standard           | 13 kΩ      |

| 1   | R10                                                  | Chip resistor, 0.1 W, 1%          | SMD<br>0603                  |                   | Standard           | 0          |

| 4   | R11, R12,<br>R13,R18                                 | Chip resistor, 0.1 W, 1%          | SMD<br>0603                  |                   | Standard           | 100 kΩ     |

| 2   | R14, R15                                             | Chip resistor, 0.1 W, 1%          | SMD<br>0805                  |                   | Standard           | N.M        |

| 1   | R16                                                  | Chip resistor, 0.1 W, 1%          | SMD<br>0805                  |                   | Standard           | 4R7        |

| 1   | R17                                                  | Chip resistor, 0.1 W, 1%          | SMD<br>0603                  |                   | Standard           | 0          |

| 1   | R19                                                  | Chip resistor, 0.1 W, 1% SMD 0603 |                              |                   | Standard           | 7k5        |

| 1   | R20                                                  | Chip resistor, 0.1 W, 1%          | Stor, 0.1 W, 1% SMD 0603 Sta |                   | Standard           | 10 kΩ      |

| 1   | L1                                                   | SMT, 13.4 Arms, 2.57 m $\Omega$   | 10.5x10.5<br>mm              | MLC1240-<br>901MX | Coilcraft          | 0.9 µH     |

| 2   | Q1, Q2                                               | N-Channel, 30 V                   | SO-8                         | STS12NH3LL        | STMicroelectronics | STS12NH3LL |

| 1   | D1                                                   | Schottky, 30 V, 0.3 A             | SOD-323                      | BAT54J            | STMicroelectronics | BAT54J     |

| 1   | D2                                                   | Schottky, 30 V, 1 A               | DO216-<br>AA                 | STPS1L30M         | STMicroelectronics | STPS1L30M  |

| 1   | D3                                                   | Schottky, 30 V, 1 A               | DO216-<br>AA                 | STPS1L30M         | STMicroelectronics | N.M.       |

| 1   | U1                                                   | Controller                        | VFQFPN-<br>24                | PM6675S           | STMicroelectronics | PM6675S    |

| 11  | J1, J2, J3,<br>J4, J5, J6,<br>J7, J8, J9,<br>J10,J11 | Header, single pin                |                              |                   |                    |            |

| 3   | JP1, JP2,<br>JP3                                     | Jumper, 2x3, 100 mils             |                              |                   |                    |            |

| 1   | JP5                                                  | PCB pads selector                 |                              |                   |                    |            |

| 1   | TP6                                                  | Test point                        |                              |                   |                    |            |

| 1   | SW1                                                  | Dip switch 2                      |                              |                   | Standard           |            |

# 4 Component assembly and layout

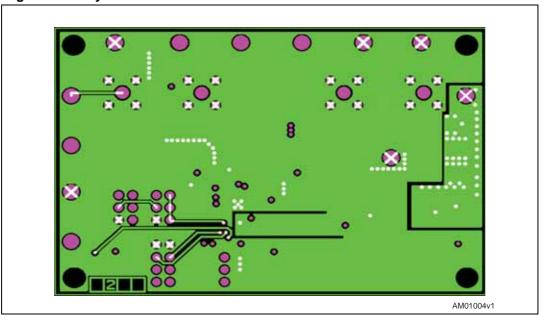

Figure 3. Top side component placement

Figure 4. Top view

**47/**

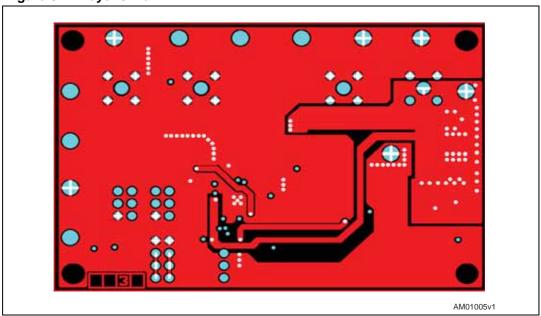

Figure 5. Layer 2 view

Figure 6. Layer 3 view

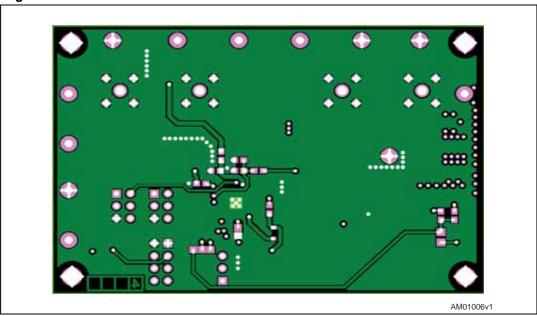

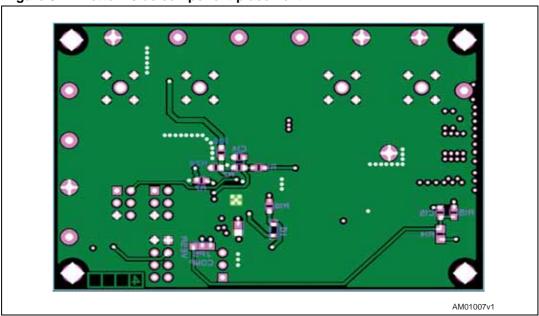

Figure 7. Bottom view

Figure 8. Bottom side component placement

I/O interface AN2816

# 5 I/O interface

The PM6675S demonstration board has the following test points as shown in *Table 2*.

Table 2. PM6675S demonstration board input and output interface

| Test point       | Description                                             |

|------------------|---------------------------------------------------------|

| V <sub>IN</sub>  | Battery input voltage positive terminal                 |

| V <sub>OUT</sub> | Switching regulator output                              |

| PGND             | Battery input and V <sub>OUT</sub> output common return |

| L <sub>IN</sub>  | LDO linear regulator input                              |

| L <sub>OUT</sub> | LDO linear regulator output                             |

| LGND             | LDO linear regulator output return                      |

| LPG              | LDO linear regulator Power Good signal                  |

| VCC              | +5 V supply, positive terminal                          |

| VCCGND           | Signal ground and VCC supply return                     |

| SPG              | V <sub>OUT</sub> SW regulator Power Good signal         |

| TP1              | Connection point between power and signal grounds       |

# 6 Recommended equipment

- 4 V to 28 V, 30 W power supply

- Active loads

- Digital mutimeters

- 200 MHz four-trace oscilloscope

Configuration AN2816

### 7 Configuration

The PM6675S demonstration board allows the user to choose the desired mode of operation using four jumpers (JP1, JP2, JP3 and JP5) and two resistors. Refer to the following configuration description.

#### 7.1 JP3 fixed or adjustable output voltage (VSEL pin)

The JP3 jumper is used to choose between fixed output voltage (1.5 V) and a user-defined output voltage in the range 0.6 V to 3.3 V. When connected in the lower position, the fixed 1.5 V output voltage is selected (*Figure 9*).

If JP3 is in the upper position, the output voltage is given by:

#### **Equation 1**

$$VOUT_{ADJ} = 0.6 \cdot \frac{R8 + R9}{R8}$$

The R8 and R9 resistors are set to 12 k $\Omega$  and 13 k $\Omega$  respectively (1.25 V output voltage) and can be changed by the user.

### 7.2 JP1 power-saving mode (NOSKIP pin)

The JP1 jumper allows choosing the mode of operation of the switching section. Three options (forced-PWM, pulse-skip and non-audible pulse-skip) can be selected by changing the JP1 setting as shown in *Figure 10*:

AN2816 Configuration

Figure 10. JP1 (NOSKIP) setting

### 7.3 JP2 current limit (LILIM pin)

The JP2 jumper is used to select the LDO current limit. In the upper position the LDO output current limit is set to 2 A, while in the lower position the current limit is set to 1 A. The middle position is not used.

Figure 11. JP2 (LILIM) setting

15/36

Configuration AN2816

### 7.4 JP5 compensation network (COMP pin)

The JP5 jumper is located on the bottom side of the PM6675S board and allows connecting the integrator input (COMP pin) to the output through a simple capacitor (integrative compensation) or using the "virtual ESR" network for very low ESR output capacitor applications (e.g. all ceramic output cap applications). The integrative compensation is set by default. Refer to the PM6675S datasheet for details about the all-ceramic output capacitor applications and the virtual ESR design.

Figure 12. JP5 (COMP) setting

AN2816 Test setup

## 8 Test setup

*Figure 13* shows the suggested setup connections between the PM6675S demonstration board, the loads and the external supply. The LDO input (LIN) is connected to  $V_{OUT}$  by default (R6 = 0  $\Omega$ ).

LOAD

0.6V to 3.3V

@1A.2A

DC supply

4V-28V

LOAD

0.6V to 3.3V

@1DA

DC supply

5V 100mA

DC supply

5V 100mA

AM01012v1

Figure 13. PM6675S demonstration board test setup

Getting started AN2816

### 9 Getting started

The following step-by-step power-up and power-down sequences are provided in order to correctly evaluate the PM6675S demonstration board performance.

#### Power-up sequence

- Working in an ESD-protected environment is highly recommended. Check all wrist straps and ground mat connections before handling the PM6675S demonstration hoard

- Connect power supplies as shown in the PM6675S demonstration board test setup (*Figure 13*) and insert the meters in order to perform the desired performance evaluation. Connect the scope-probes as desired

- Set the JP1 through JP5 jumpers in order to properly configure the PM6675S board (default position suggested). Set the SWEN-LEN switches to the on position (upper position). Do not change jumper settings when the board is powered

- Set the V<sub>CC</sub> supply to 5 V±5% and the current limit to 100 mA

- $-\,$  Set the  $V_{\text{IN}}$  supply to a voltage in the range 4.5 V to 28 V. An initial test at 12 V and 3 A current limit is suggested

- Set all the loads to 0 A

- Turn-on the V<sub>IN</sub> supply

- Turn-on the V<sub>CC</sub> supply

- Vary the V<sub>OUT</sub> load from 0 A to 10 A

- Vary the L<sub>OUT</sub> load from 0 A to 2 A to test source capability. If a different LDO input is desired, connect the external rail as dashed in *Figure 13* and remove the R6 resistor. All changes must be done when the board is not powered

- Vary V<sub>IN</sub> supply from 4.5 V to 28 V

#### Power-down sequence

- Decrease L<sub>OUT</sub> loads to 0 A

- Reduce V<sub>OUT</sub> load to 5 A

- Decrease V<sub>CC</sub> supply from 5 V to 3.8 V in order to test the UVLO

- Increase V<sub>CC</sub> supply from 3.8 V to 5 V to restart the device

- Use the SWEN-LEN switches to test soft-start and soft-end on both outputs

- Turn-off the V<sub>OUT</sub> load

- Turn-off the V<sub>CC</sub> supply

- Turn-off the V<sub>IN</sub> supply

### 10 PM6675S demonstration tests

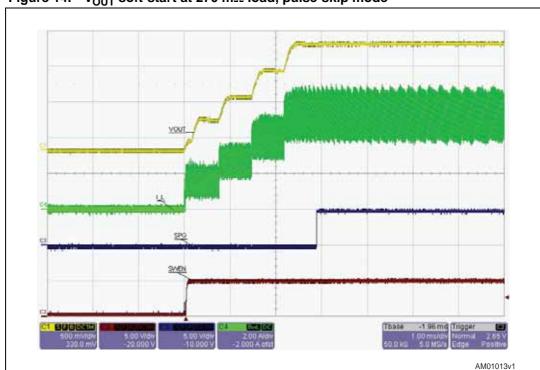

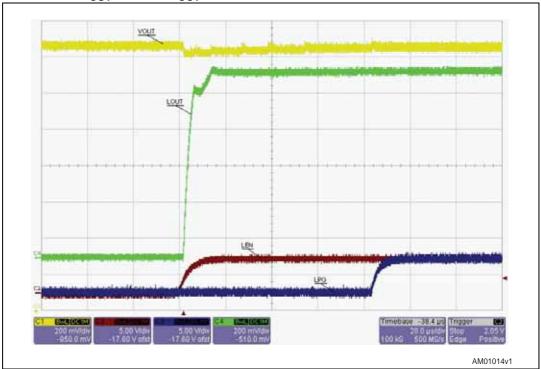

## 10.1 V<sub>OUT</sub> and L<sub>OUT</sub> turn-on (soft-start)

The  $V_{OUT}$  soft-start is divided in 4 steps. In each step the current limit is increased by ¼ of the nominal value. This behavior is well understood by loading the rail, as performed in the test.  $L_{OUT}$  soft-start is performed at its maximum available current.

Figure 14.  $V_{OUT}$  soft-start at 270 m $\Omega$  load, pulse-skip mode

Figure 15.  $L_{OUT}$  turn-on,  $V_{OUT}$  in pulse-skip mode

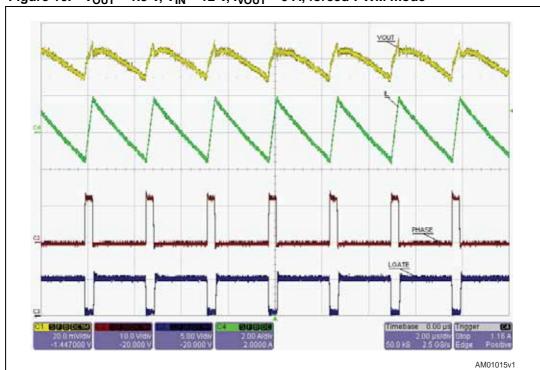

# 10.2 V<sub>OUT</sub> working mode

V<sub>OUT</sub> forced PWM mode

When the forced PWM working mode is selected (JP1 in the upper position), the inductor current is allowed to become negative and the following waveform can be captured.

Figure 16.  $V_{OUT} = 1.5 \text{ V}, V_{IN} = 12 \text{ V}, I_{VOUT} = 0 \text{ A}, forced-PWM mode}$

### V<sub>OUT</sub> pulse-skip mode

The default working mode is the pulse-skip algorithm, in which the low-side MOSFET is turned off when the inductor current becomes equal to zero. This behavior allows reaching the maximum efficiency.

Figure 17.  $V_{OUT} = 1.5 \text{ V}, V_{IN} = 12 \text{ V}, I_{VOUT} = 0 \text{ A}, \text{ pulse-skip mode}$

#### V<sub>OUT</sub> non-audible pulse-skip mode

In order to avoid too low switching frequencies, the non-audible pulse-skip mode can be selected (JP1 in the middle). Doing so, the minimum switching frequency allowed is 33 kHz as depicted in *Figure 18*.

Figure 18.  $V_{OUT} = 1.5 \text{ V}$ ,  $V_{IN} = 12 \text{ V}$ , no load, non-audible pulse-skip mode (33 kHz)

## 10.3 V<sub>OUT</sub> and L<sub>OUT</sub> load regulation

*Figure 19* and 20 refer to  $V_{OUT}$  and  $L_{OUT}$  output voltage variations versus load current. The switching section directly supplies the linear LDO.

Figure 19.  $V_{OUT}$  load regulation -  $V_{IN}$  = 12 V

Figure 20.  $L_{OUT}$  load regulation - LDOIN = 1.5 ( $V_{OUT}$ ), he dropout voltage (0.35 V) limits the maximum sourced current to about 1.8 A

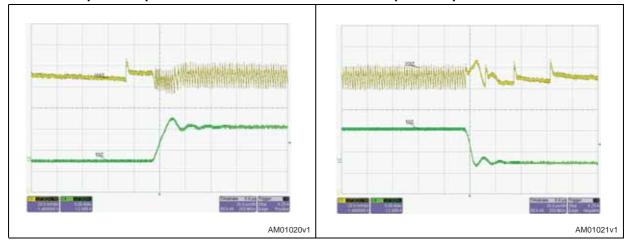

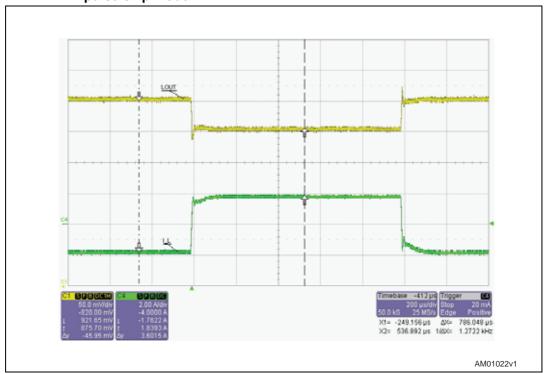

### 10.4 V<sub>OUT</sub> and L<sub>OUT</sub> load transient responses

Load transient responses are evaluated by loading  $V_{OUT}$  and  $L_{OUT}$  output rails with a current slew rate of 2.5 A/µs. In this test the switching section  $V_{OUT}$  works in pulse-skip mode and directly supplies the linear regulator.

Figure 21.  $V_{OUT}$  load transient ( $V_{IN}$  = 12 V, LOAD = 0 A to 8 A at 2.5 A/ $\mu$ s), pulse-skip mode

Figure 22.  $V_{OUT}$  load transient ( $V_{IN}$  = 12 V, LOAD = 8 A to 0 A at 2.5 A/ $\mu$ s), pulse-skip mode

Figure 23.  $L_{OUT}$  load transient ( $V_{IN}$  = 12 V, LOAD = 1.8 A to 1.85 A at 2.5 A/ $\mu$ s), pulse-skip mode

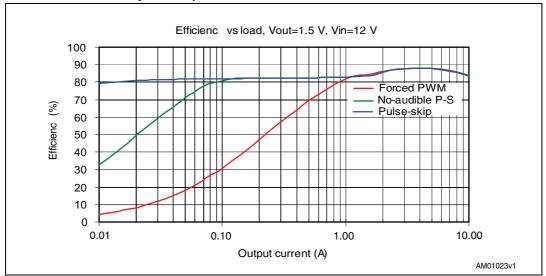

### 10.5 V<sub>OUT</sub> efficiency

The three working modes lead to different power efficiency. The test setup is  $V_{IN}=12 \text{ V}$ , FSW=330 kHz,  $V_{OUT}=1.5 \text{ V}$ . Figure 24 summarizes the results.

Figure 24. Forced PWM (blue), non-audible pulse-skip (green), pulse-skip (red), efficiency vs. output current

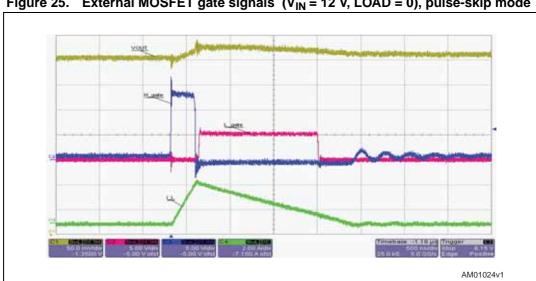

#### **V<sub>OUT</sub>** gate drivers 10.6

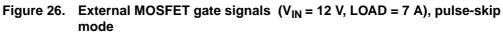

The PM6675S power MOSFET driver turns on and off the high-side and low-side external MOSFETs, avoiding cross-conduction. In the following two pictures the gates signals are shown in two different load conditions: without load (Figure 25) and with load (Figure 26).

Figure 25. External MOSFET gate signals ( $V_{IN} = 12 \text{ V}$ , LOAD = 0), pulse-skip mode

# 10.7 V<sub>OUT</sub> and L<sub>OUT</sub> turn-off (soft-end)

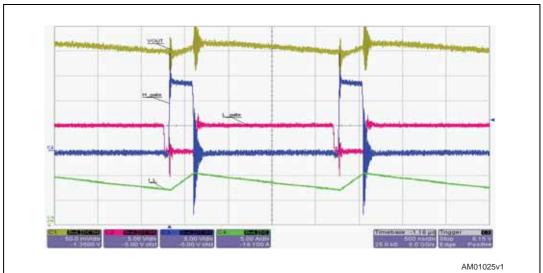

#### V<sub>OUT</sub> soft-end

When the SWEN pin is pulled down, the switching section performs the output capacitor discharge by turning on the discharge MOSFET. The external low-side MOSFET is turned on when the output voltage is lower than about 400 mV.

Figure 27.  $V_{OUT}$  and  $L_{OUT}$  output voltages  $V_{OUT}$  soft-end

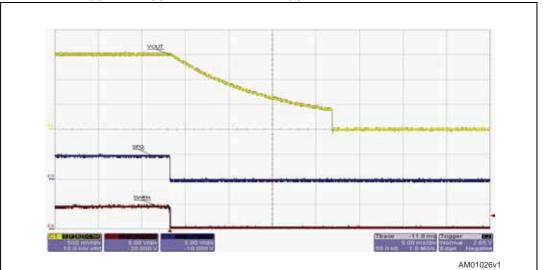

#### L<sub>OUT</sub> soft-end

By pulling down the LEN pin the linear regulator is forced to discharge its output capacitor, by turning on its discharge MOSFET. Doing so, the  $L_{OUT}$  rail is turned off in a safe way, avoiding output voltage under ground spikes.

Figure 28.  $V_{OUT}$  and  $L_{OUT}$  output voltages,  $L_{OUT}$  soft-end

Table 3. Typical discharge MOSFETs R<sub>DS(on)</sub> resistance

| Description                                   | V <sub>OUT</sub> output | L <sub>OUT</sub> output |

|-----------------------------------------------|-------------------------|-------------------------|

| Typical discharge MOSFETs R <sub>DS(on)</sub> | 25 Ω                    | 25 Ω                    |

### 10.8 UV, OV and thermal protections

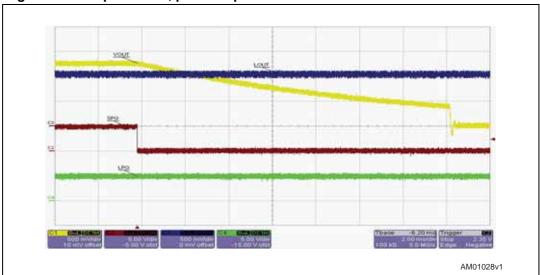

#### • Latched UV protection

If the switching section output voltage is lower than the 70% nominal value, the undervoltage state is entered and the discharge MOSFET is turned on (as in the the soft-end state).

Figure 29. UV protection, pulse-skip mode

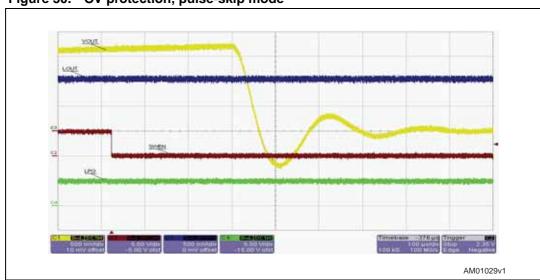

#### Latched OV protection

If the switching section output voltage is higher than the 115% nominal value, the overvoltage state is entered and the low-side MOSFET is turned on in order to quickly discharge the output capacitor and avoid load damages.

Figure 30. OV protection, pulse-skip mode

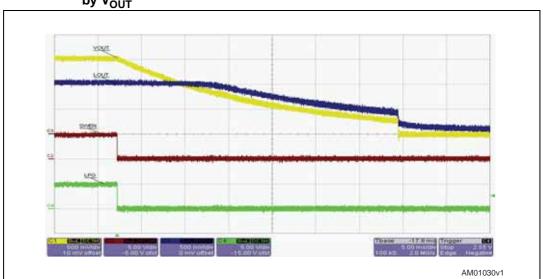

#### Latched thermal shutdown

If the junction temperature rises above 150 deg, the thermal protection circuit turns off the device and discharges the switching section output capacitor by performing the soft-end.

Figure 31.  $V_{OUT}$  and  $L_{OUT}$  rails, thermal shutdown, pulse-skip mode,  $L_{OUT}$  powered by  $V_{OUT}$

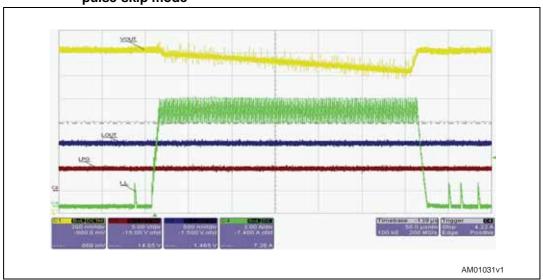

### 10.9 V<sub>OUT</sub> current limit

The valley current limit avoids any high-side turn-on if the inductor current is higher than the programmed value. This current limit can be designed with the following equation:

#### **Equation 2**

$$I_{CL} = \frac{100\mu A \cdot R_{ILIM}}{R_{LS, DS(on)}}$$

The current sensing is performed by comparing the voltage drop in the low-side MOSFET, during the TOFF period, with the voltage drop given by an injected current and the current limit resistor.

Figure 32.  $V_{OUT}$  current limit protection during a load transient (0 A to 9 A at 2.5 A/ $\mu$ s, valley current limit programmed at about 9 A ( $R_{ILIM}$  = 1 k $\Omega$ ) pulse-skip mode

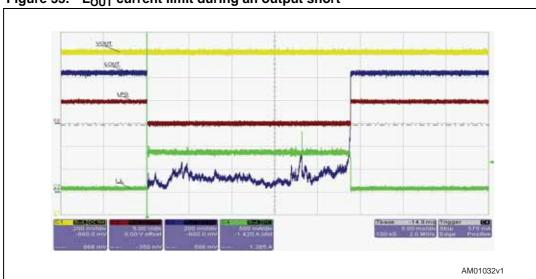

## 10.10 L<sub>OUT</sub> current limit (foldback)

The linear LDO regulator has a foldback protection feature which reduces the current limit to about 1 A when the output voltage is outside the  $\pm 10\%$  Power Good window. The current limit is restored to about 2 A when the output voltage re-enters the Power Good window. If the LDO programmed current limit is 1 A, when the output voltage is outside the  $\pm 10\%$  power good window, the short circuit current is about 500 mA.

Figure 33. L<sub>OUT</sub> current limit during an output short

**\_**

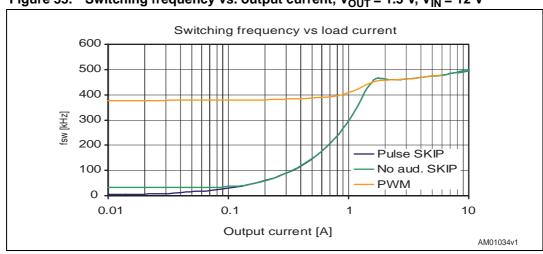

### 10.11 Switching frequency

Switching frequency vs. input voltage

The constant on-time controller leads to a quasi-constant switching frequency, slightly following the input voltage.

1.5 V switching frequency vs input voltage 600 PWM @ 0 A 550 PWM @ 7 A 500 450 fsw [kHz] 400 350 300 250 15 25 0 5 10 20 30 Input voltage [V] AM01033v1

Figure 34. Switching frequency vs. input voltage, V<sub>OUT</sub> = 1.5 V, I<sub>VOUT</sub> = 7 A, forced PWM mode

Switching frequency vs. output current

The switching frequency can decrease to very low values in pulse-skip mode but in non-audible pulse-skip there is a lower limit (about 33 kHz). By increasing the load, however, the switching frequency increases a bit, as a consequence of conduction and switching losses.

Figure 35. Switching frequency vs. output current,  $V_{OUT} = 1.5 \text{ V}$ ,  $V_{IN} = 12 \text{ V}$

AN2816 Revision history

# 11 Revision history

Table 4. Document revision history

| Date        | Revision | Changes         |

|-------------|----------|-----------------|

| 20-Aug-2008 | 1        | Initial release |

35/36

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2008 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com