## 1.1 Overview

### 1.1.1 Overview

The MN101E series of 8-bit single-chip microcomputers (the memory expansion version of MN101C series) incorporate multiple types of peripheral functions. This chip series is well suited for camera, TV, CD, printer, telephone, home appliance, PPC, fax machine, music instrument and other applications.

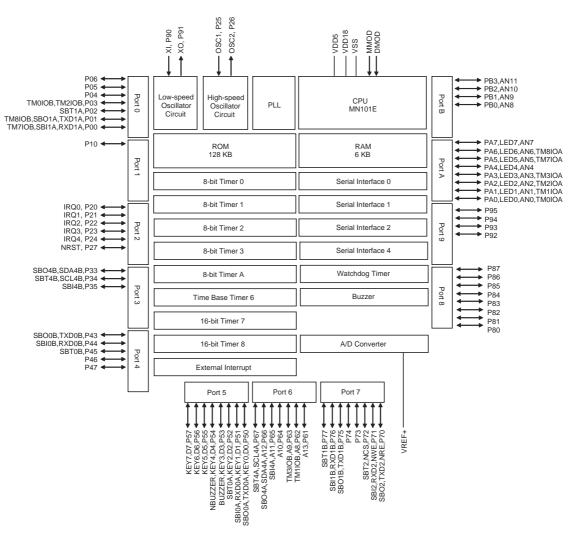

This LSI brings to embedded microcomputer applications flexible, optimized hardware configurations and a simple efficient instruction set. MN101EF93G have an internal 128 KB of ROM and 6 KB of RAM. Peripheral functions include 5 external interrupts, including NMI, 9 timer counters, 4 types of serial interfaces, A/D converter, watchdog timer and buzzer output. The system configuration is suitable for system control microcontroller.

With 3 oscillation systems (internal frequency: 16 MHz, high-speed crystal/ceramic frequency: max. 10 MHz, low-speed crystal/ceramic frequency: 32.768 kHz) contained on the chip, the system clock can be switched to high-speed frequency input (NORMAL mode) or PLL input (PLL mode), or low-speed frequency input (SLOW mode). The system clock is generated by dividing the oscillation clock or PLL clock. The best operation clock for the system can be selected by switching its frequency ratio by programming. High speed mode has NORMAL mode which is based on the clock dividing fpll, (fpll is generated by original oscillation and PLL), by 2 (fpll/2), and the double speed mode which is based on the clock not dividing fpll.

A machine cycle (minimum instruction execution time) in NORMAL mode is 200 ns when the original oscillation fosc is 10 MHz (PLL is not used). A machine cycle in the double speed mode, in which the CPU operates on the same clock as the external clock, is 100 ns when fosc is 10 MHz. A machine cycle in the PLL mode is 50 ns (maximum).

## 1.1.2 Product Summary

This manual describes the following model.

Table:1.1.1 Product Summary

| Model      | ROM Size | RAM Size | Classification       | Package     |

|------------|----------|----------|----------------------|-------------|

| MN101EF93G | 128 KB   | 6 KB     | Flash EEPROM version | 80 Pin LQFP |

## 1.2 Hardware Functions

#### Feature

- Memory Capacity: ROM 128 KB RAM 6 KB

#### - Package:

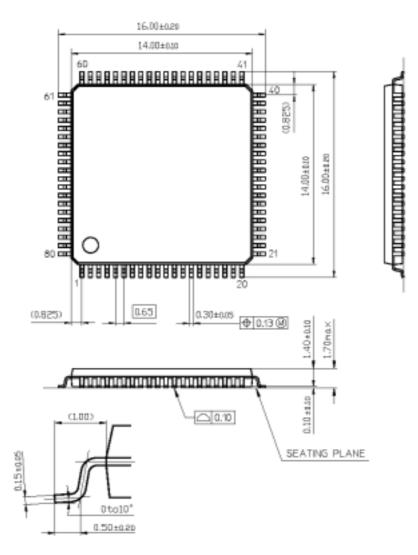

80-Pin LQFP (14 mm × 14 mm / 0.65 mm pitch, halogen free)

Panasonic "halogen free" semiconductor products refer to the products made of molding resin and interposer which conform to the following standards.

- Bromine : 900 ppm (Maximum Concentration Value)

- Chlorine : 900 ppm (Maximum Concentration Value)

- Bromine + Chlorine : 1500 ppm (Maximum Concentration Value)

The above-mentioned standards are based on the numerical value described in IEC61249-2-21. Antimony and its compounds are not added intentionally.

- Machine Cycle: High-speed mode 0.05  $\mu s$  / 20 MHz (4.0 V to 5.5 V) Low-speed mode 62.5  $\mu s$  / 32 kHz (4.0 V to 5.5 V)

Oscillation circuit: 3 channel oscillation circuit Internal oscillation (frc): 16 MHz Crystal/ceramic (fosc): Maximum 10 MHz Crystal/ceramic (fx): Maximum 32.768 kHz

-Clock Multiplication circuit (PLL Circuit) PLL circuit output clock (fpll): fosc multiplied by 2, 3, 4, 5, 6, 8, 10,  $1/2 \times \text{frc}$  multiplication by 4, 5 enable

-Clock Gear for System Clock System Clock (fs): fpll divided by 1, 2, 4, 16, 32, 64, 128

-Clock Gear for control clock of peripheral function Control clock of peripheral function (fpll-div): stop or fpll divided by 1, 2, 4, 8, 16

- Memory Bank:

Expands data memory space by the bank system (by 64 KB, 16 banks) Source address bank / Destination address bank

Operation Mode: NORMAL mode (High-speed mode) SLOW mode (Low-speed mode) HALT mode STOP mode (The operation clock can be switched in each mode.)

- Operating Voltage: 4.0 V to 5.5 V

- Operation ambient temperature: -40 °C to +85 °C

- Interrupt: 25 levels

- <Non-maskable interrupt>

- Non-maskable interrupt and Watchdog timer overflow interrupt

<Timer interrupts>

- Timer 0 interrupt

- Timer 1 interrupt

- Timer 2 interrupt

- Timer 3 interrupt

- Timer 6 interrupt

- Time base timer interrupt

- Timer 7 interrupt

- Timer 7 compare register 2 match interrupt

- Timer 8 interrupt

- Timer 8 compare register 2 match interrupt

<Serial Interface interrupts>

- Serial interface 0 interrupt

- Serial interface 0 UART reception interrupt

- Serial interface 1 interrupt

- Serial interface 1 UART reception interrupt

- Serial interface 2 interrupt

- Serial interface 2 UART reception interrupt

- Serial interface 4 interrupt

- Serial interface 4 stop condition interrupt

<A/D interrupt>

- A/D conversion interrupt

<External interrupts>

- IRQ0: Edge selectable, noise filter connection available

- IRQ1: Edge selectable, noise filter connection available

- IRQ2: Edge selectable, noise filter connection available, both edges interrupt

- IRQ3: Edge selectable, noise filter connection available, both edges interrupt

- IRQ4: Edge selectable, noise filter connection available, both edges interrupt, Key scan interrupt

- Timer Counter: 9 timers

- 8-bit timer for general use  $\times$  4 sets

- 16-bit timer for general use  $\times 2$  sets

- 8-bit free-run timer  $\times 1$  set

- Time base timer  $\times 1$  set

- Baud rate timer  $\times 1$  set

Timer 0 (8-bit timer for general use)

- Square wave output (Timer pulse output)

- Added pulse (2-bit) type PWM output can be output to large current pin TM0IOA

- Event count

- Simple pulse measurement

- Clock source

fpll-div/4, fpll-div/16, fpll-div/32, fpll-div/64, fpll-div/128, fs/2, fs/4, fs/8, fx, External clock, Timer A output

### Timer 1 (8-bit timer for general use)

- Square wave output (Timer pulse output) can be output to large current pin TM1IOA

- Event count

- 16-bit cascade connected (with Timer 0)

- Clock source

fpll-div/4, fpll-div/16, fpll-div/32, fpll-div/64, fpll-div/128, fs/2, fs/4, fs/8, fx, External clock, Timer A output

### Timer 2 (8-bit timer for general use)

- Square wave output (Timer pulse output)

- Added pulse (2-bit) type PWM output can be output to large current pin TM2IOA

- Event count

- Simple pulse measurement

- 24-bit cascade connected (with Timer 0 and Timer 1)

- Clock source

fpll-div/4, fpll-div/16, fpll-div/32, fpll-div/64, fpll-div/128, fs/2, fs/4, fs/8, fx, External clock, Timer A output

### Timer 3 (8-bit timer for general use)

- Square wave output (Timer pulse output) can be output to large current pin TM3IOA

- Event count

- 16-bit cascade connected (with Timer 2)

- 32-bit cascade connected (with Timer 0 and Timer 1 and Timer 2)

- Clock source

fpll-div/4, fpll-div/16, fpll-div/32, fpll-div/128, fs/2, fs/4, fs/8, fx, External clock, Timer A output

Timer 6 (8-bit free-run timer, Time base timer)

- 8-bit free-run timer

- Clock source

- fpll-div, fpll-div/2<sup>12</sup>, fpll-div/2<sup>13</sup>, fs, fx, fx/2<sup>2</sup>, fx/2<sup>3</sup>, fx/2<sup>12</sup>, fx/2<sup>13</sup>

- Time base timer

- Interrupt generation cycle

fpll-div/2<sup>7</sup>, fpll-div/2<sup>8</sup>, fpll-div/2<sup>9</sup>, fpll-div/2<sup>10</sup>, fpll-div/2<sup>13</sup>, fpll-div/2<sup>15</sup>, fx/2<sup>7</sup>, fx/2<sup>8</sup>, fx/2<sup>9</sup>, fx/2<sup>10</sup>, fx/2<sup>13</sup>, fx/2<sup>15</sup>

Timer 7 (16-bit timer for general use)

- Square wave output (Timer pulse output)

- High precision PWM output (Cycle/Duty continuous changeable) can be output to large current pin TM7IOA

- Event count

- Input capture function (Both edges can be operated)

- Clock source

- fpll-div, fpll-div/2, fpll-div/4, fpll-div/16, fs, fs/2, fs/4, fs/16,

Timer A divided by 1, 2, 4, 16, External clock divided by 1, 2, 4, 16

Timer 8 (16-bit timer for general use)

- Square wave output (Timer pulse output)

- High precision PWM output (Cycle/Duty continuous changeable) can be output to large current pin

TM8IOA

- Event count

- Input capture function (Both edges can be operated)

- Clock source

- fpll-div, fpll-div/2, fpll-div/4, fpll-div/16, fs, fs/2, fs/4, fs/16,

- Timer A divided by 1, 2, 4, 16, External clock divided by 1, 2, 4, 16

- Timer A (Baud rate timer)

- Clock output for peripheral functions

- Clock source

- fpll-div, fpll-div/2, fpll-div/4, fpll-div/8, fpll-div/16, fpll-div/32, fs/2, fs/4

- Watchdog timer

Time-out cycle can be selected from  $fs/2^{16}$ ,  $fs/2^{18}$ ,  $fs/2^{20}$ On detection of 2 errors, forcibly hard reset inside LSI. Operation start timing is selectable. (At reset release or write to register)

- Buzzer Output/ Reverse Buzzer Output

Output frequency can be selected from fpll-div/2<sup>9</sup>, fpll-div/2<sup>10</sup>, fpll-div/2<sup>11</sup>, fpll-div/2<sup>12</sup>, fpll-div/2<sup>13</sup>, fpll-div/2<sup>14</sup>, fx/2<sup>3</sup>, fx/2<sup>4</sup>

- A/D Converter: 10-bit × 12 channels

- Serial Interface: 4 channels

Serial 0: UART (full duplex)/ Clock synchronous

Clock synchronous serial interface

- Transfer clock source fpll-div/2, fpll-div/4, fpll-div/16, fpll-div/64, fs/2, fs/4, Timer 0 to 3 or Timer A divided by 1, 2, 4, 8, 16, External clock

- MSB/LSB can be selected as the first bit to be transferred, arbitrary sizes of 2 to 8 bits are selectable.

- Sequence transmission, reception or both are available

- Full duplex UART

- Baud rate timer, selected from Timer 0 to 3 or Timer A

- Parity check, overrun error/ framing error detection

- Transfer size 7 to 8 bits can be selected

Serial 1: UART (full duplex)/ Clock synchronous

Clock synchronous serial interface

- Transfer clock source fpll-div/2, fpll-div/4, fpll-div/16, fpll-div/64, fs/2, fs/4, Timer 0 to 3 or Timer A divided by 1, 2, 4, 8, 16, External clock

- MSB/LSB can be selected as the first bit to be transferred, arbitrary sizes of 2 to 8 bits are selectable.

- Sequence transmission, reception or both are available.

- Full duplex UART

- Baud rate timer, selected from Timer 0 to 3 or Timer A

- Parity check, overrun error/ framing error detection

- Transfer size 7 to 8 bits can be selected

Serial 2: UART (full duplex)/ Clock synchronous

Clock synchronous serial interface

- Transfer clock source fpll-div/2, fpll-div/4, fpll-div/16, fpll-div/64, fs/2, fs/4, Timer 0 to 3 or Timer A divided by 1, 2, 4, 8, 16, External clock

- MSB/LSB can be selected as the first bit to be transferred,

arbitrary sizes of 2 to 8 bits are selectable.

- Sequence transmission, reception or both are available.

Full duplex UART

- Baud rate timer, selected from Timer 0 to 3 or Timer A

- Parity check, overrun error/ framing error detection

- Transfer size 7 to 8 bits can be selected

- Serial 4: Multi master IIC/ Clock synchronous

Clock synchronous serial interface

- Transfer clock source fpll-div/2, fpll-div/4, fpll-div/16, fpll-div/32, fs/2, fs/4, Timer 0 to 3 or Timer A divided by 1, 2, 4, 8, 16, External clock

- MSB/LSB can be selected as the first bit to be transferred,

- arbitrary sizes of 2 to 8 bits are selectable.

- Sequence transmission, reception or both are available.

Multi master IIC

- 7-bit slave address is settable.

- General call communication mode is supported.

- Automatic Reset:

Power detection level: 4.3 V (at rising), 4.2 V (at falling)

- LED Driver: 8 pins (Port A)

#### - Ports

| I/O ports                          | 72 pins |

|------------------------------------|---------|

| Serial Interface pins              | 21 pins |

| Timer I/O                          | 11 pins |

| Buzzer output pins                 | 2 pins  |

| A/D input pins                     | 12 pins |

| External Interrupt pins            | 5 pins  |

| LED (large current) driver         | 8 pins  |

| High-speed oscillation             | 2 pins  |

| Low-speed oscillation              | 2 pins  |

| Special pins                       | 8 pins  |

| Operation mode input pins          | 3 pins  |

| Reset input pin                    | 1 pin   |

| Analog reference voltage input pin | 1 pin   |

| Power pins                         | 3 pins  |

|                                    |         |

## 1.3 Pin Description

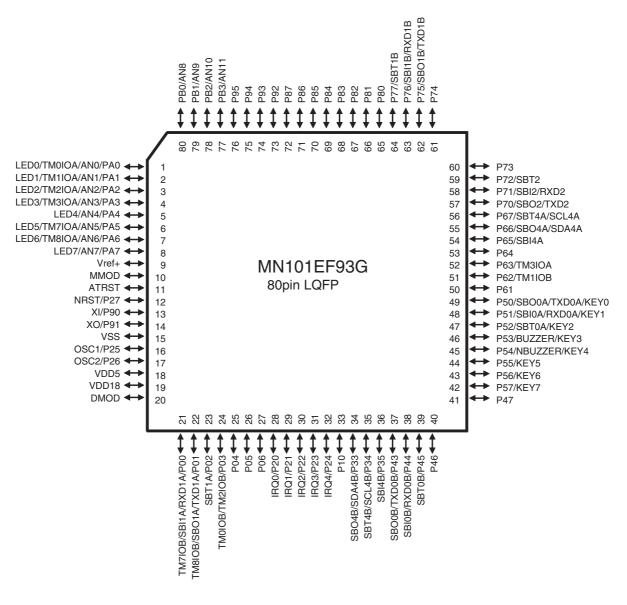

### 1.3.1 Pin configuration

Figure:1.3.1 Pin Configuration (80-pin LQFP)

## Panasonic -

## 1.3.2 Pin Specification

|      | 1                    | 1      | 1                    | 1              |                                         |

|------|----------------------|--------|----------------------|----------------|-----------------------------------------|

| Pins | Special<br>Functions | I/O    | Direction<br>Control | Pin<br>Control | Functions Description                   |

|      | TM7IOB               | in/out |                      |                | Timer 7 input/output                    |

| P00  | SBI1A                | in/out | P0DIR0               | P0PLU0         | Serial 1 data input                     |

|      | RXD1A                | in/out | ]                    |                | UART 1 data input                       |

|      | TM8IOB               | in/out |                      |                | Timer 8 input/output                    |

| P01  | SBO1A                | in/out | P0DIR1               | P0PLU1         | Serial 1 data input/output              |

| FUI  | TXD1A                | in/out | PUDIRI               | FUFLUI         | UART 1 data input/output                |

|      | OCD_DATA             | in/out |                      |                | On-boad programmer data pin             |

| P02  | SBT1A                | in/out | P0DIR2               | P0PLU2         | Serial 1 clock input/output             |

| F UZ | OCD_CLK              | in/out | FUDINZ               | FUFLUZ         | On-boad programmer clock supply pin     |

| P03  | TM0IOB               | in/out | P0DIR3               | P0PLU3         | Timer 0 input/output                    |

| F03  | TM2IOB               | in/out | FUDIKS               | FUFLUS         | Timer 2 input/output                    |

| P04  | -                    | in/out | P0DIR4               | P0PLU4         | -                                       |

| P05  | -                    | in/out | P0DIR5               | P0PLU5         | -                                       |

| P06  | -                    | in/out | P0DIR6               | P0PLU6         | -                                       |

| P10  | -                    | in/out | P0DIR10              | P0PLU10        | -                                       |

| P20  | IRQ0                 | in/out | P2DIR0               | P2PLU0         | External Interrupt 0                    |

| P21  | IRQ1                 | in/out | P2DIR1               | P2PLU1         | External Interrupt 1                    |

| P22  | IRQ2                 | in/out | P2DIR2               | P2PLU2         | External Interrupt 2                    |

| P23  | IRQ3                 | in/out | P2DIR3               | P2PLU3         | External Interrupt3                     |

| P24  | IRQ4                 | in/out | P2DIR4               | P2PLU4         | External Interrupt4                     |

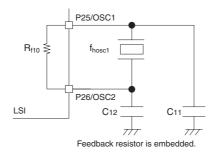

| P25  | OSC1                 | in/out | P2DIR5               | P2PLU5         | Ceramic/crystal high-speed clock input  |

| P26  | OSC2                 | in/out | P2DIR6               | P2PLU6         | Ceramic/crystal high-speed clock output |

| P27  | NRST                 | in/out | -                    | -              | Reset                                   |

| P33  | SB04B                | in/out | P3DIR3               | P3PLU3         | Serial 4 data input/output              |

| F 33 | SDA4B                | in/out | FSDIKS               | FSFLUS         | Multi-master IIC 4 data input/output    |

| P34  | SBT4B                | in/out | P3DIR4               | P3PLU4         | Serial 4 clock input/output             |

| F 34 | SCL4B                | in/out | F3DIR4               | F3FL04         | Multi-master IIC 4 clock input/output   |

| P35  | SBI4B                | in/out | P3DIR5               | P3PLU5         | Serial 4 data input                     |

| P43  | SBO0B                | in/out |                      | P4PLU3         | Serial 0 data input/output              |

| F43  | TXD0B                | in/out | P4DIR3               | F4FL03         | UART 0 data input/output                |

| P44  | SBI0B                | in/out | P4DIR4               | P4PLU4         | Serial 0 data input                     |

| F 44 | RXD0B                | in/out |                      | 1 41 LU4       | UART 0 data input                       |

| P45  | SBT0B                | in/out | P4DIR5               | P4PLU5         | Serial 0 clock input/output             |

| P46  | -                    | in/out | P4DIR6               | P4PLU6         | -                                       |

| P47  | -                    | in/out | P4DIR7               | P4PLU7         | -                                       |

|      | KEY0                 | in/out |                      |                | Key interrupt 0                         |

| P50  | SBO0A                | in/out | P5DIR0               | P5PLU0         | Serial 0 data input/output              |

|      | TXD0A                | in/out | 1                    |                | UART 0 data input/output                |

|      | KEY1                 | in/out |                      |                | Key interrupt 1                         |

| P51  | SBIOA                | in/out | P5DIR1               | P5PLU1         | Serial 0 data input                     |

|      | RXD0A                | in/out | 1                    |                | UART 0 data input                       |

|      |                      |        |                      |                |                                         |

| Pins | Special<br>Functions | I/O    | Direction<br>Control | Pin<br>Control | Functions Description                  |

|------|----------------------|--------|----------------------|----------------|----------------------------------------|

| 550  | KEY2                 | in/out | 050100               | DEDLUG         | Key interrupt 2                        |

| P52  | SBT0A                | in/out | P5DIR2               | P5PLU2         | Serial 0 clock input/output            |

| P53  | KEY3                 | in/out | P5DIR3               | P5PLU3         | Key interrupt 3                        |

| F33  | BUZZER               | in/out | FSDIKS               | 1 01 200       | Buzzer output                          |

| P54  | KEY4                 | in/out | P5DIR4               | P5PLU4         | Key interrupt 4                        |

| F 34 | NBUZZER              | in/out | F JDIR4              | F JF LO4       | Buzzer reverse output                  |

| P55  | KEY5                 | in/out | P5DIR5               | P5PLU5         | Key interrupt 5                        |

| P56  | KEY6                 | in/out | P5DIR6               | P5PLU6         | Key interrupt 6                        |

| P57  | KEY7                 | in/out | P5DIR7               | P5PLU7         | Key interrupt 7                        |

| P61  | -                    | in/out | P6DIR1               | P6PLU1         | -                                      |

| P62  | TM1IOB               | in/out | P6DIR2               | P6PLU2         | Timer 1 input/output                   |

| P63  | ТМЗІОВ               | in/out | P6DIR3               | P6PLU3         | Timer 3 input/output                   |

| P64  | -                    | in/out | P6DIR4               | P6PLU4         | -                                      |

| P65  | SBI4A                | in/out | P6DIR5               | P6PLU5         | Serial 4 data input                    |

| P66  | SBO4A                | in/out | P6DIR6               | P6PLU6         | Serial 4 data input/output             |

| FOO  | SDA4A                | in/out | FODINO               | FOFLOO         | Multi-master IIC 4 data input/output   |

| P67  | SBT4A                | in/out | P6DIR7               | P6PLU7         | Serial 4 clock input/output            |

| 107  | SCL4A                | in/out | 1 OBIN               | FOPLU/         | Multi-master IIC 4 clock input/output  |

| P70  | SBO2                 | in/out | P7DIR0               | P7PLU0         | Serial 2 data input/output             |

| F70  | TXD2                 | in/out | PTDINO               | F 7 F LOO      | UART 2 data input/output               |

| P71  | SBI2                 | in/out | P7DIR1               | P7PLU1         | Serial 2 data input                    |

| F71  | RXD2                 | in/out | FIDIN                |                | UART 2 data input                      |

| P72  | SBT2                 | in/out | P7DIR2               | P7PLU2         | Serial 2 clock input/output            |

| P73  | -                    | in/out | P7DIR3               | P7PLU3         | -                                      |

| P74  | -                    | in/out | P7DIR4               | P7PLU4         | -                                      |

| P75  | SBO1B                | in/out | P7DIR5               | P7PLU5         | Serial 1 data input/output             |

| 170  | TXD1B                | in/out | 17Bitto              | 111 200        | UART 1 data input/output               |

| P76  | SBI1B                | in/out | P7DIR6               | P7PLU6         | Serial 1 data input                    |

|      | RXD1B                | in/out | 1.12.110             |                | UART 1 data input                      |

| P77  | SBT1B                | in/out | P7DIR7               | P7PLU7         | Serial 1 clock input/output            |

| P80  | -                    | in/out | P8DIR0               | P8PLU0         | -                                      |

| P81  | -                    | in/out | P8DIR1               | P8PLU1         | -                                      |

| P82  | -                    | in/out | P8DIR2               | P8PLU2         | -                                      |

| P83  | -                    | in/out | P8DIR3               | P8PLU3         | -                                      |

| P84  | -                    | in/out | P8DIR4               | P8PLU4         | -                                      |

| P85  | -                    | in/out | P8DIR5               | P8PLU5         | -                                      |

| P86  | -                    | in/out | P8DIR6               | P8PLU6         | -                                      |

| P87  | -                    | in/out | P8DIR7               | P8PLU7         | -                                      |

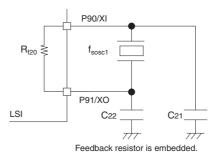

| P90  | XI                   | in/out | P9DIR0               | P9PLU0         | Ceramic/crystal low-speed clock input  |

| P91  | хо                   | in/out | P9DIR1               | P9PLU1         | Ceramic/crystal low-speed clock output |

| P92  | -                    | in/out | P9DIR2               | P9PLU2         | -                                      |

| P93  | -                    | in/out | P9DIR3               | P9PLU3         |                                        |

| P94  | -                    | in/out | P9DIR4               | P9PLU4         | -                                      |

| P95  | -                    | in/out | P9DIR5               | P9PLU5         | -                                      |

| Pins | Special<br>Functions | I/O    | Direction<br>Control | Pin<br>Control | Functions Description |

|------|----------------------|--------|----------------------|----------------|-----------------------|

|      | AN0                  | in/out |                      |                | Analog 0 input        |

| PA0  | LED0                 | in/out | PADIR0               | PAPLU0         | LED driving pin 0     |

|      | TM0IOA               | in/out |                      |                | Timer 0 input/output  |

|      | AN1                  | in/out |                      |                | Analog 1 input        |

| PA1  | LED1                 | in/out | PADIR1               | PAPLU1         | LED driving pin 1     |

|      | TM1IOA               | in/out |                      |                | Timer 1 input/output  |

|      | AN2                  | in/out |                      |                | Analog 2 input        |

| PA2  | LED2                 | in/out | PADIR2               | PAPLU2         | LED driving pin 2     |

|      | TM2IOA               | in/out |                      |                | Timer 2 input/output  |

|      | AN3 in/out           | in/out |                      | PAPLU3         | Analog 3 input        |

| PA3  | LED3                 | in/out | PADIR3               |                | LED driving pin 3     |

|      | TM3IOA               | in/out |                      |                | Timer 3 input/output  |

| PA4  | AN4                  | in/out | PADIR4               | PAPLU4         | Analog 4 input        |

| FA4  | LED4                 | in/out | FADIR4               |                | LED driving pin 4     |

|      | AN5                  | in/out | PADIR5               | PAPLU5         | Analog 5 input        |

| PA5  | LED5                 | in/out |                      |                | LED driving pin 5     |

|      | TM7IOA               | in/out |                      |                | Timer 7 input/output  |

|      | AN6                  | in/out |                      | PAPLU6         | Analog 6 input        |

| PA6  | LED6                 | in/out | PADIR6               |                | LED driving pin 6     |

|      | TM8IOA               | in/out |                      |                | Timer 8 input/output  |

| PA7  | AN7                  | in/out | PADIR7               | PAPLU7         | Analog 7 input        |

| FA/  | LED7                 | in/out | FADIR/               | FAFLUI         | LED driving pin 7     |

| PB0  | AN8                  | in/out | PBDIR0               | PBPLU0         | Analog 8 input        |

| PB1  | AN9                  | in/out | PBDIR1               | PBPLU1         | Analog 9 input        |

| PB2  | AN10                 | in/out | PBDIR2               | PBPLU2         | Analog 10 input       |

| PB3  | AN11                 | in/out | PBDIR3               | PBPLU3         | Analog 11 input       |

## 1.3.3 Pin Functions

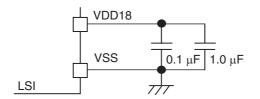

|                                                                                                                                                                                                      | D5 and 0 V connect 0.1 μF + 1 μF or                                                                                                                                                                                                                                                              |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                  |  |

|                                                                                                                                                                                                      | internal power stabilization.                                                                                                                                                                                                                                                                    |  |

| VDD18 19 - Internal power output pin power supply to external de                                                                                                                                     | m internal power circuit. Don't use the evice. For internal power circuit output .1 $\mu$ F + 1 $\mu$ F one bypass capacitor                                                                                                                                                                     |  |

|                                                                                                                                                                                                      | bins to ceramic or crystal ocsillators for ation. If the clock is an external input,                                                                                                                                                                                                             |  |

|                                                                                                                                                                                                      | ave OSC2 open. The chip will not oper-                                                                                                                                                                                                                                                           |  |

| NRST 12 I/O Reset pin [Active low] P27 and contains an interm<br>this pin low initialize the intu<br>setting the input to high rele<br>the system clock to stabiliz<br>a capacitor is to be inserted | ten power is turned on, is allocated as<br>al pull-up resistor (Typ. 50 kΩ). Setting<br>ernal state of the device. Thereafter,<br>eases the reset. The hardware waits for<br>re, then processes the reset interrupt. If<br>d between NRST and VSS, it is recom-<br>licities to be tween NRST and |  |

| ATRST 11 input Auto reset setting pin Input "High" to enable auto function                                                                                                                           | reset function and "Low" to disable this                                                                                                                                                                                                                                                         |  |

| P00 21                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                  |  |

| P01 22                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                  |  |

|                                                                                                                                                                                                      | ort. Each bit can be set individually as                                                                                                                                                                                                                                                         |  |

| P03 24 I/O I/O port 0 each bit can be selected in                                                                                                                                                    | either an input or output by PODIR register. A pull-up resistor for<br>each bit can be selected individually by POPLU register. At reset,<br>the input mode is selected and pull-up resistor is disabled (high<br>impedance).                                                                    |  |

|                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                  |  |

| P05 26                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                  |  |

| P06 27                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                  |  |

| P10 33 I/O I/O port 1 put by P1DIR register. A put                                                                                                                                                   | rt. It can be set as either an input or out-<br>Il-up resistor can be selected by P1PLU<br>mode is selected and pull-up resistor is                                                                                                                                                              |  |

| P20 28                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                  |  |

| P21 29                                                                                                                                                                                               | 7-bit CMOS tri-state I/O port. Each bit can be set individually as<br>either an input or output by P2DIR register. A pull-up resistor for<br>each bit can be selected individually by P2PLU register. At reset,                                                                                  |  |

|                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                  |  |

| P23 31 I/O I/O port 2 each bit can be selected in                                                                                                                                                    |                                                                                                                                                                                                                                                                                                  |  |

| P24 32 the input mode is selected i impedance)                                                                                                                                                       | and pull-up resistor is disabled (high                                                                                                                                                                                                                                                           |  |

| P25 16                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                  |  |

| P26 17                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                  |  |

| P27 12 input input port 2 P27 has an N-channel oper                                                                                                                                                  | en-drain configuration.                                                                                                                                                                                                                                                                          |  |

|                                                                                                                                                                                                      | ort. Each bit can be set individually as                                                                                                                                                                                                                                                         |  |

| P34 35 I/O I/O port 3 each bit can be selected in                                                                                                                                                    | / P3DIR register. A pull-up resistor for<br>adividually by P3PLU register.                                                                                                                                                                                                                       |  |

| P35 36 At reset, the input mode is s (high impedance).                                                                                                                                               | selected and pull-up resistor is disabled                                                                                                                                                                                                                                                        |  |

| P43 37                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                  |  |

|                                                                                                                                                                                                      | 5-bit CMOS tri-state I/O port. Each bit can be set individually as                                                                                                                                                                                                                               |  |

| P45 39 I/O I/O port 4 each bit can be selected in                                                                                                                                                    | / P4DIR register. A pull-up resistor for<br>idividually by P4PLU register. At reset,<br>and pull-up resistor is disabled (high                                                                                                                                                                   |  |

| P46 40 the input mode is selected i impedance).                                                                                                                                                      | ana pairap resistor is disabled (nigh                                                                                                                                                                                                                                                            |  |

| P47 41                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                  |  |

| Pins | NO | I/O         | Function     | Description                                                                                                                                                                                                                                                                                         |

|------|----|-------------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P50  | 49 |             |              |                                                                                                                                                                                                                                                                                                     |

| P51  | 48 |             |              |                                                                                                                                                                                                                                                                                                     |

| P52  | 47 |             |              | A bit AMAA bi state VA and East bit and he and individually an                                                                                                                                                                                                                                      |

| P53  | 46 | I/O         |              | 8-bit CMOS tri-state I/O port. Each bit can be set individually as<br>either an input or output by PSDIR register. A pull-up resistor for                                                                                                                                                           |

| P54  | 45 |             | I/O port 5   | each bit can be selected individually by P5PLU register.<br>At reset, the input mode is selected and pull-up resistor is disabled                                                                                                                                                                   |

| P55  | 44 |             |              | (high impedance).                                                                                                                                                                                                                                                                                   |

| P56  | 43 |             |              |                                                                                                                                                                                                                                                                                                     |

| P57  | 42 |             |              |                                                                                                                                                                                                                                                                                                     |

| P61  | 50 |             |              |                                                                                                                                                                                                                                                                                                     |

| P62  | 51 |             |              |                                                                                                                                                                                                                                                                                                     |

| P63  | 52 |             |              | 7-bit CMOS tri-state I/O port. Each bit can be set individually as                                                                                                                                                                                                                                  |

| P64  | 53 | I/O         | I/O port 6   | either an input or output by P6DIR register. A pull-up resistor for<br>each bit can be selected individually by P6PLU register. At reset,                                                                                                                                                           |

| P65  | 54 |             |              | the input mode is selected and pull-up resistor is disabled (high impedance).                                                                                                                                                                                                                       |

| P66  | 55 |             |              |                                                                                                                                                                                                                                                                                                     |

| P67  | 56 |             |              |                                                                                                                                                                                                                                                                                                     |

| P70  | 57 |             |              |                                                                                                                                                                                                                                                                                                     |

| P71  | 58 |             |              |                                                                                                                                                                                                                                                                                                     |

| P72  | 59 |             |              | 8-bit CMOS tri-state I/O port. Each bit can be set individually as<br>either an input or output by P7DIR register. A pull-up resistor for<br>each bit can be selected individually by P7PLU register. At reset,<br>the input mode is selected and pull-up resistor is disabled (high<br>impedance). |

| P73  | 60 |             | O I/O port 7 |                                                                                                                                                                                                                                                                                                     |

| P74  | 61 | I/O         |              |                                                                                                                                                                                                                                                                                                     |

| P75  | 62 |             |              |                                                                                                                                                                                                                                                                                                     |

| P76  | 63 |             |              |                                                                                                                                                                                                                                                                                                     |

| P77  | 64 |             |              |                                                                                                                                                                                                                                                                                                     |

| P80  | 65 |             |              |                                                                                                                                                                                                                                                                                                     |

| P81  | 66 |             |              |                                                                                                                                                                                                                                                                                                     |

| P82  | 67 |             |              |                                                                                                                                                                                                                                                                                                     |

| P83  | 68 | I/O I/O poi |              | 8-bit CMOS tri-state I/O port. Each bit can be set individually as<br>either an input or output by P8DIR register. A pull-up resistor for                                                                                                                                                           |

| P84  | 69 |             | the input    | each bit can be selected individually by P8PLU register. At reset,<br>the input mode is selected and pull-up resistor is disabled (high<br>impedance).                                                                                                                                              |

| P85  | 70 |             |              |                                                                                                                                                                                                                                                                                                     |

| P86  | 71 |             |              |                                                                                                                                                                                                                                                                                                     |

| P87  | 72 |             |              |                                                                                                                                                                                                                                                                                                     |

| P90  | 13 |             |              |                                                                                                                                                                                                                                                                                                     |

| P91  | 14 |             |              |                                                                                                                                                                                                                                                                                                     |

| P92  | 73 |             |              | 6-bit CMOS tri-state I/O port. Each bit can be set individually as<br>either an input or output by P9DIR register. A pull-up resistor for                                                                                                                                                           |

| P93  | 74 | I/O         | I/O port 9   | each bit can be selected individually by P9PLU register.<br>At reset, the input mode is selected and pull-up resistor is disabled                                                                                                                                                                   |

| P94  | 75 |             |              | (high impedance).                                                                                                                                                                                                                                                                                   |

| P95  | 76 |             |              |                                                                                                                                                                                                                                                                                                     |

| PA0  | 1  |             |              |                                                                                                                                                                                                                                                                                                     |

| PA1  | 2  |             |              |                                                                                                                                                                                                                                                                                                     |

| PA2  | 3  |             |              |                                                                                                                                                                                                                                                                                                     |

| PA3  | 4  |             |              | 8-bit CMOS tri-state I/O port. Each bit can be set individually as<br>either an input or output by PADIR register. A pull-up resistor for                                                                                                                                                           |

| PA4  | 5  | I/O         | I/O port A   | each bit can be selected individually by PAPLU register. At reset,<br>the input mode is selected and pull-up resistor is disabled (high                                                                                                                                                             |

| PA5  | 6  |             |              | impedance).                                                                                                                                                                                                                                                                                         |

| PA6  | 7  |             |              |                                                                                                                                                                                                                                                                                                     |

| PA7  | 8  |             |              |                                                                                                                                                                                                                                                                                                     |

| I    |    |             |              |                                                                                                                                                                                                                                                                                                     |

| Pins  | NO | I/O    | Function                                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|-------|----|--------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PB0   | 80 |        |                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| PB1   | 79 |        |                                                     | 4-bit CMOS tri-state I/O port. Each bit can be set individually as<br>either an input or output by PBDIR register. A pull-up resistor for                                                                                                                                                                                                                                                                                                                                                                             |  |

| PB2   | 78 | I/O    | I/O port B                                          | each bit can be selected individually by PBPLU register.<br>At reset, the input mode is selected and pull-up resistor is disabled                                                                                                                                                                                                                                                                                                                                                                                     |  |

| PB3   | 77 |        |                                                     | (high impedance).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| SBO0A | 49 |        |                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| SBO0B | 37 |        |                                                     | Transmission data output pins for serial interface 0,1,2,4. The out-<br>put configuration, either COMS push-pull or Nch open-drain can be                                                                                                                                                                                                                                                                                                                                                                             |  |

| SBO1A | 22 |        |                                                     | selected in P0ODC, P3ODC, P4ODC, P5ODC, P6ODC and                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

| SBO1B | 62 | Output | Serial interface transmission data out-<br>put pins | P7ODC registers. Pull-up resistor can be selected in P0PLU,<br>P3PLU, P4PLU, P5PLU, P6PLU, and P7PLU registers. Select out-                                                                                                                                                                                                                                                                                                                                                                                           |  |

| SBO2  | 57 |        |                                                     | put mode in P0DIR, P3DIR, P4DIR, P5DIR, P6DIR, and P7DIR<br>registers and set serial data output mode in serial mode register 1<br>(2000) 2010 1001 2010 1001 2010 2010 2010                                                                                                                                                                                                                                                                                                                                          |  |

| SBO4A | 55 |        |                                                     | (SC0MD1, SC1MD1, SC2MD1, SC4MD1). These can be used as<br>normal I/O pins when serial interface is not used.                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| SBO4B | 34 |        |                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| SBI0A | 48 |        |                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| SBI0B | 38 |        |                                                     | Percention data input nine for parial interface 0.4.0.4. Dull up and                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| SBI1A | 21 |        |                                                     | Reception data input pins for serial interface 0,1,2,4. Pull-up resis-<br>tor can be selected in POPLU, P3PLU, P4PLU, P5PLU, P6PLU<br>and P7PLU registers. Select the output mode in POIDE P3PLP                                                                                                                                                                                                                                                                                                                      |  |

| SBI1B | 63 | Input  | Serial interface reception data input<br>pins       | and P7PLU registers. Select the output mode in P0DIR, P3DIR,<br>P4DIR, P5DIR, P6DIR and P7DIR registers and select serial data<br>input mode in serial mode register 1 (SC0MD1, SC1MD1,                                                                                                                                                                                                                                                                                                                               |  |

| SBI2  | 58 |        |                                                     | SC2MD1, SC4MD1). These can be used as normal I/O pins when serial interface is not used.                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| SBI4A | 54 |        |                                                     | Serial Intellate IS HUL USEU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| SBI4B | 36 | 1      |                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| SBT0A | 47 |        |                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| SBT0B | 39 |        | Serial interface Clock I/O pins                     | Clock I/O pins for serial interface 0,1,2,4. The output configuration,<br>either COMS push-pull or Nch open-drain can be selected in<br>PODDC, P3ODC, P4ODC, P5ODC, P6ODC and P7ODC registers.<br>Pull-up resistor can be selected in P0PLU, P3PLU, P4PLU,<br>P5PLU, P6PLU and P7PLU registers. Select clock I/O in P0DIR,<br>P3DIR, P4DIR, P5DIR, P6DIR and P7DIR registers and serial<br>mode register 1 (SC0MD1, SC1MD1, SC2MD1, SC4MD1) with the<br>communication mode. These can be used as normal I/O pins when |  |

| SBT1A | 23 |        |                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| SBT1B | 64 | I/O    |                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| SBT2  | 59 |        |                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| SBT4A | 56 |        |                                                     | serial interface is not used.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| SBT4B | 35 |        |                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| TXD0A | 49 |        |                                                     | In serial interface 0,1,2 in UART mode, this pin is configured as the transmission data output pin. The output configuration of ther                                                                                                                                                                                                                                                                                                                                                                                  |  |

| TXD0B | 37 |        |                                                     | transmission data output pin. The output configuration, either<br>COMS push-pull or Nch open-drain can be selected in PODDC,<br>P4ODC, P5ODC, P6ODC and P7ODC registers. Pull-up resistor<br>can be selected by P0PLU, P4PLU, P5PLU(D), P6PLU and<br>P7PLU registers. Select the output mode in P0DIR, P4DIR,                                                                                                                                                                                                         |  |

| TXD1A | 22 | Output | UART transmission data output pins                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| TXD1B | 62 |        |                                                     | P5DIR, P6DIR and P7DIR registers and select serial data output<br>mode in serial mode register 1 (SC0MD1, SC1MD1, SC2MD1).                                                                                                                                                                                                                                                                                                                                                                                            |  |

| TXD2  | 57 |        |                                                     | These can be used as normal I/O pins when serial interface is not used.                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |