Highly Integrated 6A Single-input Voltage, Synchronous Buck Regulator with PMBus Interface

## IR38060

## **FEATURES**

International

**ICR** Rectifier

AN INFINEON TECHNOLOGIES COMPANY

- Internal LDO allows single 21V operation

- Output Voltage Range: 0.5V to 0.875\*PVin

- 0.5% accurate Reference Voltage

- Programmable Switching Frequency up to 1.5MHz using Rt/Sync pin or PMBus

- Internal Soft-Start with Pre-Bias Start-up

- Enable input with Voltage Monitoring Capability

- Remote Sense Amplifier with True Differential Voltage Sensing

- Fast mode I2C and 400 kHz PMBus interface

- Sequencing and tracking capable

- Selectable analog mode or digital mode

- 75 PMBus commands for configuration, control, fault protection and telemetry.

- Thermally compensated current limit with configurable overcurrent responses

- Optional light load efficiency mode

- External synchronization with Smooth Clocking

- Dedicated output voltage sensing protection which remains active even when Enable is low.

- Integrated MOSFETs and Bootstrap diode

- Operating junction temp: -40°C<Tj<125°C

- Small Size 5mmx7mm PQFN

- Pb-Free (RoHS Compliant)

## DESCRIPTION

The IR38060 PMBus SupIRBuck<sup>™</sup> is an easy-to-use, fully integrated and highly efficient DC/DC regulator with I2C/PMBus interface. The onboard PWM controller and MOSFETs make IR38060 a space-efficient solution, providing accurate power delivery for low output voltage and high current applications.

The IR38060 can be comprehensively configured via PMBus and the configuration stored in internal memory. In addition, PMBus commands allow run-time control, fault status and telemetry.

The IR38060 can also operate as a standard analog regulator without any programming and can provide current and temperature telemetry in an analog format.

# **APPLICATIONS**

Server Applications Netcomm applications Embedded telecom Systems Distributed Point Of Load Architectures

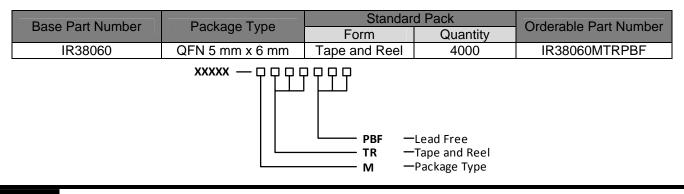

## **ORDERING INFORMATION**

# **BASIC APPLICATION**

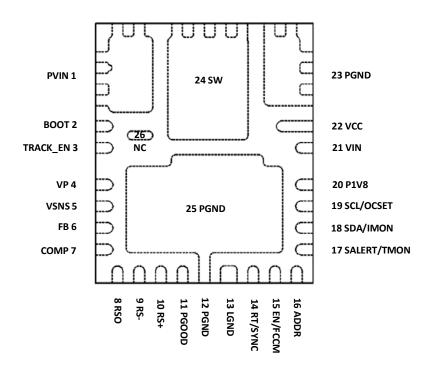

#### **PINOUT DIAGRAM**

2