## HIGH-SPEED 8K x 16 TriPort STATIC RAM

## IDT70P5258ML IDT70P525ML IDT70V525ML

## **Features**

- High-speed access

- Industrial: 55ns (max.)

- Low-power operation

IDT70P5258ML and IDT70P525ML

- Active: 54mW (typ.) Standby: 7.2μW (typ.)

- IDT70V525ML

- IDT70V525WL Active: 450mW (typ.)

- Standby: 250µW (typ.)

- TriPort architecture allows simultaneous access to the memory from all three ports

- Fully asynchronous operation from each of the three ports: P1, P2, and P3

- IDT70P5258 supports 3.0V and 1.8V I/O's

- Available in 144-ball 0.5mm-pitch fpBGA

- Industrial temperature range (-40°C to +85°C)

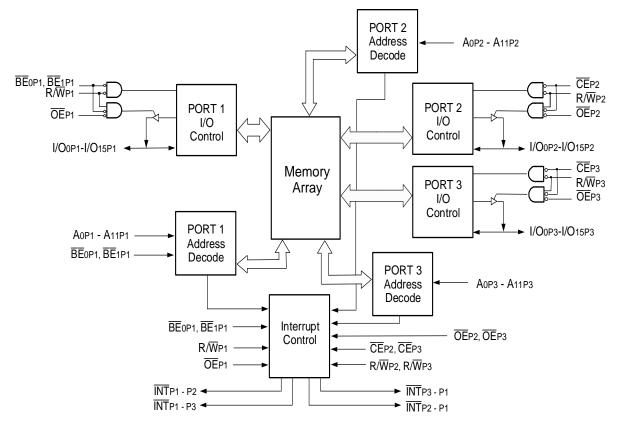

## **Functional Block Diagram**

5681 drw 01

#### Description

The IDT70X525X is a high-speed 8K x 16 TriPort Static RAM designed to be used in systems where multiple access into a common RAM is required. This TriPort Static RAM offers increased system performance in multiprocessor systems that have a need to communicate in real time and also offers added benefit for high-speed systems in which multiple access is required in the same cycle.

The IDT70X525X is also designed to be used in systems where onchip hardware port arbitration is not needed. This part lends itself to those systems which cannot tolerate wait states or are designed to be able to externally arbitrated or withstand contention when more than one port simultaneously accesses the same TriPort RAM location.

The IDT70X525X provides three independent ports with separate control, address, and I/O pins that permit independent, asynchronous access for reads or writes to any location in memory. It is the user's responsibility to ensure data integrity when simultaneously accessing the same memory location from mutiple ports. An automatic power down feature, controlled by BE0 and BE1 on Port 1 and CE on Port 2 and on Port 3, permits the on-chip circuitry of each port to enter a very low power standby power mode.

Preliminary

Industrial Temperature Range

The IDT70X525X is packaged in a 144-ball 0.5mm-pitch fpBGA.

## Pin Configurations<sup>(1,2,3)</sup>

#### 70(P/V)525XBZ BZ-144

| 12/19/03 |               |         |                    |                    | Тор            | View               |               |               |              |                     |                     |

|----------|---------------|---------|--------------------|--------------------|----------------|--------------------|---------------|---------------|--------------|---------------------|---------------------|

| А1       | а2            | Аз      | А4                 | А5                 | А6             | A7                 | A8            | A9            | A10          | A11                 | A12                 |

| І/О7Р3   | I/O6р2        | I/O4P3  | I/Озр2             | І/О1Р2             | <b>ОЕ</b> РЗ   | R/WP2              | NC            | A11P2         | A9P2         | A7P2                | A6P2                |

| в1       | в2            | вз      | в4                 | в5                 | B6             | в7                 | B8            | в9            | B10          | в11                 | в12                 |

| I/O7Р2   | I/O6р3        | Vdd(1)  | I/O2P3             | I/Оорз             | OEp2           | <u>СЕ</u> рз       | NC            | А10Р3         | А8Р3         | А6рз                | А5Р3                |

| C1       | <sup>C2</sup> | C3      | C4                 | С5                 | с6             | C7                 | C8            | C9            | C10          | C11                 | C12                 |

| I/O9P2   | Vss           | I/O5P2  | I/O2P2             | I/O0Р2             | R/WРз          | CEp2               | A11P3         | A10P2         | A8P2         | A5P2                | A4P3                |

| D1       | D2            | d3      | D4                 | D5                 | d6             | D7                 | <sup>D8</sup> | D9            | D10          | D11                 | D12                 |

| I/O10P3  | I/O8P2        | I/O5p3  | I/Озрз             | I/O1P3             | Vdd            | VDD <sup>(1)</sup> | Vss           | A9P3          | A7P3         | A4P2                | A3P2                |

| Е1       | Е2            | Е3      | Е4                 | e5                 | <sup>E6</sup>  | <sup>E7</sup>      | <sup>E8</sup> | E9            | E10          | E11                 | E12                 |

| I/O11Р3  | I/O11Р2       | I/O8Р3  | I/O4P2             | Vdd                | Vss            | Vss                | Vss           | A0P3          | Азрз         | A2P3                | A2P2                |

| F1       | F2            | F3      | <sup>F4</sup>      | <sup>F5</sup>      | <sup>F6</sup>  | <sup>F7</sup>      | <sup>F8</sup> | <sup>F9</sup> | f10          | F11                 | F12                 |

| I/O12P3  | I/O12P2       | I/О9Р3  | Vdd <sup>(1)</sup> | Vdd <sup>(1)</sup> | Vss            | Vss                | Vss           | Vss           | Vdd          | A1P3                | A0P2                |

| G1       | G2            | G3      | G4                 | <sup>G5</sup>      | <sub>G6</sub>  | <sub>G7</sub>      | <sup>G8</sup> | <sup>G9</sup> | g10          | G11                 | G12                 |

| I/O15P2  | I/O13P3       | I/O10P2 | I/O13P2            | Vss                | Vss            | Vss                | Vss           | Vss           | Vdd          | A1P2                | VDD <sup>(1)</sup>  |

| Н1       | н2            | нз      | h4                 | <sup>H5</sup>      | <sup>H6</sup>  | <sup>H7</sup>      | <sup>H8</sup> | h9            | h10          | Н11                 | H12                 |

| I/O15P3  | I/O14P3       | I/O14P2 | Vdd                | Vss                | Vss            | Vss                | Vss           | Vdd           | Vdd          | INT <sub>РЗР1</sub> | INT <sub>P2P1</sub> |

| J1       | J2            | j3      | J4                 | <sub>J5</sub>      | <sub>J6</sub>  | <sub>J7</sub>      | j8            | J9            | J10          | J11                 | J12                 |

| I/O2P1   | I/O1P1        | Vdd     | Vss                | Vss                | Vss            | Vss                | Vdd           | Vdd           | <b>A</b> 0P1 | INT <sub>Р1Р3</sub> | INT <sub>P1P2</sub> |

| к1       | к2            | кз      | к4                 | k5                 | к <sub>6</sub> | кт                 | k8            | к9            | к10          | к11                 | к12                 |

| I/Oзр1   | I/O0р1        | I/O4р1  | Vss                | Vdd                | Vss            | Vdd                | Vdd           | А10Р1         | Азр1         | А2Р1                | А1Р1                |

| L1       | l2            | l3      | L4                 | l5                 | l6             | L7                 | L8            | L9            | L10          | L11                 | L12                 |

| I/O6P1   | I/O5P1        | I/O8P1  | I/O10P1            | I/O12P1            | I/O14P1        | OEp1               | BE0P1         | NC            | A9P1         | A7P1                | A4P1                |

| м1       | m2            | мз      | м4                 | м5                 | м6             | м7                 | M8            | м9            | M10          | м11                 | M12                 |

| I/O7р1   | Vdd           | I/O9P1  | I/O11Р1            | I/O13P1            | I/O15P1        | R/WP1              | BE1P1         | А11Р1         | A8P1         | АбР1                | A5P1                |

**Top View**

NOTES:

1. VDDQ for 70P5258.

5681 drw 02

## **Pin Configurations**<sup>(1,2)</sup>

| Symbol           | Pin Name                                   |

|------------------|--------------------------------------------|

| A0P1 - A11P1     | Address Lines - Port 1 (Input)             |

| A0P2 - A11P2     | Address Lines - Port 2 (Input)             |

| A0P3 - A11P3     | Address Lines - Port 3 (Input)             |

| VO0P1 - VO15P1   | Data I/O - Port 1                          |

| 1/00P2 - 1/015P2 | Data I/O - Port 2                          |

| 1/O0P3 - 1/O15P3 | Data I/O - Port 3                          |

| R/WP1            | Read/Write - Port 1 (Input)                |

| R/WP2            | Read/Write - Port 2 (Input)                |

| R/WP3            | Read/Write - Port 3 (Input)                |

| CEP2             | Chip Enable - Port 2 (Input)               |

| <b>CE</b> P3     | Chip Enable - Port 3 (Input)               |

| 0Ep1             | Output Enable - Port 1 (Input)             |

| OEP2             | Output Enable - Port 2 (Input)             |

| <del>OE</del> P3 | Output Enable - Port 3 (Input)             |

| BE0P1            | Bank Enable 0 - Port 1 (Input)             |

| BE1P1            | Bank Enable 1 - Port 1 (Input)             |

| ĪNTP1 - P2       | Interrupt P1 - P2 - Port 1 (Output)        |

| INTP1 - P3       | Interrupt P1 - P3 - Port 1 (Output)        |

| ĪNTP2 - P1       | Interrupt P2 - P1 - Port 2 (Output)        |

| ĪNTP3 - P1       | Interrupt P3 - P1 - Port 3 (Output)        |

| VDD              | Power (Input)                              |

| VDDQ             | Port Power Supply (Input) <sup>(3,4)</sup> |

| Vss              | Ground (Input)                             |

Preliminary Industrial Temperature Range

#### NOTES:

All Vob pins must be connected to the power supply.

All Vss pins must be connected to the ground supply.

IDT70P5258 only.

For Port 2 and Port 3.

## **Recommended DC Operating Conditions**

| Symbol | Device             | Port       | Parameter                         | Min. | Тур. | Мах.     | Unit       |  |

|--------|--------------------|------------|-----------------------------------|------|------|----------|------------|--|

|        | 70P5258            |            |                                   | 1.7  | 1.8  | 1.9      |            |  |

| VDD    | 70P525             | All        | Supply Voltage                    | 1.7  | 1.8  | 1.9      | v          |  |

|        | 70V525             |            |                                   | 2.7  | 3    | 3.3      |            |  |

|        | 70P5258 Port 2 & 3 |            | 2.7                               | 3    | 3.3  |          |            |  |

| VDDQ   | 70P525             | N/A        | I/O Supply Voltage <sup>(1)</sup> |      | _    |          | v          |  |

|        | 70V525             | N/A        |                                   |      |      |          |            |  |

| Vss    | All                | All        | Ground                            | 0    | 0    | 0        | V          |  |

|        | 70P5258            | Port 1     |                                   | 1.2  | _    | VDD+0.2  |            |  |

| ViH    |                    | Port 2 & 3 | Input Lligh Voltogo               | 2    |      | VDDQ+0.2 | v          |  |

| VIH    | 70P525             | All        | Input High Voltage                | 1.2  |      | VDD+0.2  |            |  |

|        | 70V525             | All        |                                   | 2    |      | VDD+0.2  |            |  |

|        | 70P5258            | Port 1     |                                   | -0.2 |      | 0.4      |            |  |

| Vil    | 70P3236            | Port 2 & 3 | Innut Louis Voltonio              | -0.2 |      | 0.6      |            |  |

| VIL    | 70P525             | All        | Input Low Voltage                 | -0.2 | _    | 0.4      | V          |  |

|        | 70V525             | All        |                                   | -0.2 |      | 0.6      |            |  |

|        |                    |            |                                   |      |      | 5        | 681 tbl 02 |  |

#### NOTES:

1. The supply voltage for all ports on the IDT70P525 and IDT70V525 is supplied by Vob so there are no Vobo pins on these devices.

5681 tbl 03

2. VIL  $\geq$  -1.5V for pulse width less than 10ns.

3. VTERM must not exceed VDD + 10% for Port 1 or VDDQ + 10% for Port 2 and Port 3.

# Capacitance<sup>(1)</sup>

#### $(T_{A} = +25^{\circ}C, f = 1.0MHz)$

| Symbol | Parameter   | Port       | Conditions <sup>(2)</sup> | Max | Unit |

|--------|-------------|------------|---------------------------|-----|------|

| CIN    | Input       | Port 1     | VIN = 3dV                 | 18  | pF   |

| CIN    | Capacitance | Port 2 & 3 | VIN = 3dV                 | 9   | pF   |

| 0      | Output      | Port 1     | Vout = 3dV                | 20  | pF   |

| Соит   | Capacitance | Port 2 & 3 | Vout = 3dV                | 11  | pF   |

#### NOTES:

- 1. This parameter is determined by device characterization but is not production tested.

- 3dV references the interpolated capacitance when the input and the output signals switch from 0V to 3V or from 3V to 0V.

# Maximum Operating Temperature and Supply Voltage<sup>(1)</sup>

| Grade      | Ambient Temperature | Device            | Vss | Vdd                 |   |

|------------|---------------------|-------------------|-----|---------------------|---|

| Industrial | -40°C to +85°C      | 70P525<br>70P5258 | 0V  | 1.8V <u>+</u> 100mV |   |

|            |                     | 70V525            | 0V  | 3.0V <u>+</u> 300mV |   |

|            |                     |                   |     | 5681 tbl 04         | • |

#### NOTES:

1. This is the parameter TA. This is the "instant on" case temperature.

### Absolute Maximum Ratings<sup>(1)</sup>

| Symbol                              | Rating                                  | Industrial            | Unit |  |  |  |  |  |

|-------------------------------------|-----------------------------------------|-----------------------|------|--|--|--|--|--|

| Vterm <sup>(2)</sup>                | Terminal Voltage<br>with Respect to GND | -0.5 to VDDMAX + 0.3V | V    |  |  |  |  |  |

| TBIAS                               | Temperature Under Bias                  | -55 to +125           | °C   |  |  |  |  |  |

| Tstg                                | Storage Temperature                     | -65 to +150           | °C   |  |  |  |  |  |

| NIT                                 | Junction Temperatue                     | +150                  | °C   |  |  |  |  |  |

| юлт<br>(for 70V525)                 | DC Output Current                       | 50                    | mA   |  |  |  |  |  |

| lout<br>(for 70P525<br>and 70P5258) | DC Output Current                       | 20                    | mA   |  |  |  |  |  |

#### NOTES:

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

5681 tbl 05

VTERM must not exceed VDD + 10% for Port 1 or VDDQ + 10% for Port 2 and Port 3 for more than 25% of the cycle time or 10ns maximum, and is limited to ≤ 20mA for the period of VTERM ≥ VDD + 10% (Port 1) or VDDQ + 10% (Port 2 and Port 3).

## DC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range<sup>(1,4)</sup>

|        |                                                                         |                                                                                                                                                                                                                                |         | 70F                 | 5258<br>2525<br>Only |                     | /525<br>Only |            |

|--------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------------|----------------------|---------------------|--------------|------------|

| Symbol | Parameter                                                               | Test Condition                                                                                                                                                                                                                 | Version | Typ. <sup>(1)</sup> | Мах.                 | Typ. <sup>(1)</sup> | Мах.         | Unit       |

| Idd    | Dynamic Operating Current<br>(Both Ports Active - CMOS<br>Level Inputs) | $\label{eq:expectation} \begin{array}{l} \overline{CE} = V_{IL}, \mbox{ Outputs Open} \\ f = f_{MAX}^{(2)} \end{array}$                                                                                                        | IND'L L | 30                  | 50                   | 150                 | 180          | mA         |

| ISB1   | Standby Current (Both Ports -<br>CMOS Level Inputs)                     | $\overline{CE}R$ and $\overline{CE}L = VH$<br>f = $Max^{(2)}$                                                                                                                                                                  | IND'L L | .004                | .016                 | 5                   | 10           | mA         |

| ISB2   | Standby Current (One Port -<br>CMOS Level Inputs)                       | $\overline{CE}"_{A}" = V_{IL}$ and $\overline{CE}"_{B}" = V_{IH}^{(3)}$ , Active Port Outputs Open $f = f_{MAX}^{(2)}$                                                                                                         | IND'L L | 17                  | 28                   | 90                  | 110          | mA         |

| ISB3   | Full Standby Current (Both<br>Ports - CMOS Level Inputs)                | Both Ports $\overline{CE}_L$ and $\overline{CE}_R \ge V_{DD} - 0.2V$ ,<br>$V_IN \ge V_{DD} - 0.2V$ or $V_{IN} \le 0.2V$<br>$f = \int_{Max^{(2)}}$                                                                              | IND'L L | 4                   | 16                   | 84                  | 150          | μA         |

| ISB4   | Standby Current (One Port -<br>CMOS Level Inputs)                       | $\overline{CE}^* \mathbb{A}^* \leq 0.2V$ and $\overline{CE}^* \mathbb{B}^* \geq V \text{DD} - 0.2V^{(3)}$<br>$V \text{N} \geq V \text{DD} - 0.2V$ or $V \text{IN} \leq 0.2V$ , Active Port Outputs Open $f = \text{Max}^{(2)}$ | IND'L L | 17                  | 28                   | 90                  | 110          | mA         |

|        | •                                                                       |                                                                                                                                                                                                                                | •       | -                   |                      |                     | 5            | 681 tbl 06 |

NOTES:

1. VDD = 1.8V for 70P5258 and 70P525. VDD = 3.0V for 70V525, TA = +25°C, and are not production tested. IDD DC = 15mA (typ.)

2. At f = fmax, address and control lines are cycling at the maximum frequency read cycle of 1/trc, and using "AC Test Conditions".

3. For the 70P5258, if Port "A" is Port 1 then Port "B" may be either Port 2 or Port 3. If Port "A" is either Port 2 or Port 3, Port "B" must be Port 1.

4.  $V_{DD} = 1.8V \pm 100mV$  for 70P525 and 70P5258.  $V_{DD} = 3.0V \pm 300mV$  for 70V525.

# DC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range<sup>(2)</sup>

| Symbol | Device  | Port       | Parameter              | Test Conditions                                               | Min. | Мах. | Unit |  |

|--------|---------|------------|------------------------|---------------------------------------------------------------|------|------|------|--|

|        | 70P5258 | All        |                        | Vdd = 1.8V, $Vin$ = 0V to $Vdd$                               |      | 1    |      |  |

| lu     | 70P525  | All        | Input Leakage Current  | $V_{DD} = 1.8V$ , $V_{IN} = 0V$ to $V_{DD}$                   | -    | 1    | μΑ   |  |

|        | 70V525  | All        |                        | VdD = 3.0V, $Vin$ = 0V to $VdD$                               |      | 1    |      |  |

|        | 70P5258 | All        |                        | $\overline{CE}x = \overline{BE}x = V_{IH}$ , Vout = 0V to VDD |      | 1    |      |  |

| Ilo    | 70P525  | All        | Output Leakage Current | $\overline{CE}x = \overline{BE}x = VIH$ , Vout = 0V to VDD    |      | 1    | μΑ   |  |

|        | 70V525  | All        |                        | $\overline{CE}x = \overline{BE}x = VIH$ , Vout = 0V to VDD    |      | 1    | 1    |  |

|        | 7005050 | Port 1     |                        | Iol = +0.1mA                                                  |      | 0.2  |      |  |

| Max    | 70P5258 | Port 2 & 3 | IoL = +2mA             |                                                               |      | 0.4  | v    |  |

| Vol    | 70P525  | All        | Output Low Voltage     | lol = +0.1mA                                                  |      | 0.2  | V    |  |

|        | 70V525  | All        |                        | lol = +2mA                                                    | _    | 0.4  |      |  |

|        | 70P5258 | Port 1     |                        | юн = -0.1mA                                                   | 1.4  |      |      |  |

| Mau    | 70P5258 | Port 2 & 3 | Output Lligh Voltage   | юн = -2mA                                                     | 2.1  |      | v    |  |

| Vон    | 70P525  | All        | Output High Voltage    | юн = -0.1mA                                                   | 1.4  |      |      |  |

|        | 70V525  | All        |                        | <b>І</b> он = -2mA                                            |      |      |      |  |

NOTE:

1. At V\_DD  $\leq$  2.0V input leakages are undefined.

2. VDD = 1.8V ± 100mV for 70P525 and 70P5258. VDD = 3.0V ± 300mV for 70V525.

5681 tbl 07

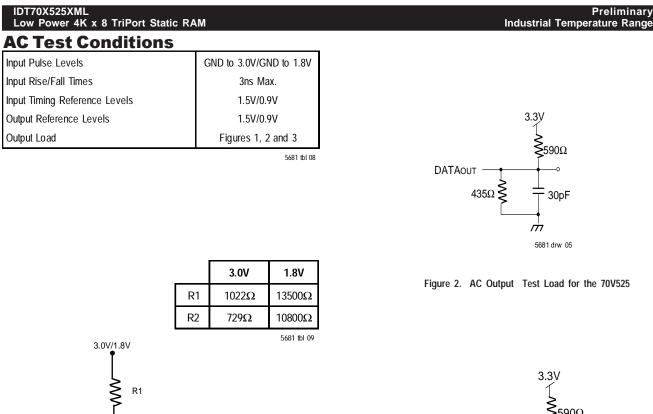

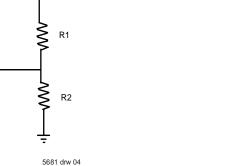

Figure 1. AC Output Test Load for the 70P525 and 70P5258

30pF<sup>(1)</sup>

DATAOUT 435Ω 590Ω 590Ω 590Ω 590Ω 590Ω 590Ω 590Ω

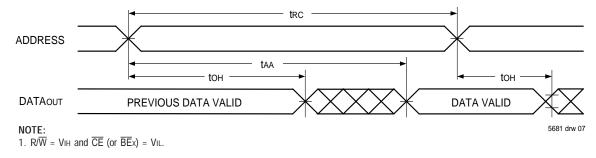

## Timing Waveform of Read Cycle No. 1, Any Port<sup>(1)</sup>

## AC Electrical Characteristics Over the Operating Temperature and Supply Voltage

|            |                                                |      | 525X<br>Only |           |

|------------|------------------------------------------------|------|--------------|-----------|

| Symbol     | Parameter                                      | Min. | Max.         | Unit      |

| READ CYCLE |                                                |      |              |           |

| trc        | Read Cycle Time                                | 55   |              | ns        |

| taa        | Address Access Time                            |      | 55           | ns        |

| tace       | Chip Enable Access Time                        | -    | 55           | ns        |

| taoe       | Output Enable Access Time                      |      | 30           | ns        |

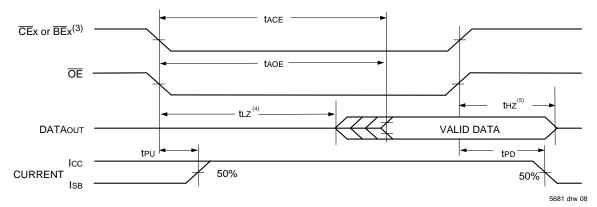

| toн        | Output Hold from Address Change                | 5    |              | ns        |

| tLZ        | Output Low-Z Time <sup>(1,2)</sup>             | 5    |              | ns        |

| tHZ        | Output High-Z Time <sup>(1,2)</sup>            |      | 25           | ns        |

| tpu        | Chip Enable to Power Up Time <sup>(2)</sup>    | 0    |              | ns        |

| tpd        | Chip Disable to Power Down Time <sup>(2)</sup> |      | 55           | ns        |

| NOTES:     |                                                |      |              | 5681 tb10 |

NOTES:

1. Transition is measured 0mV from Low or High-impedance voltage with the Output Test Load (Figure 2).

2. This parameter is guaranteed by device characterization but is not production tested.

# Timing Waveform of Read Cycle No. 2, Any Port<sup>(1, 2)</sup>

#### NOTES:

- 1.  $R/\overline{W} = V_{IH}$  for Read Cycles.

- 2. Addresses valid prior to or coincident with  $\overline{CE}$  (or  $\overline{BEx}$ ) transition LOW.

- 3.  $\overline{CE}$  for Port 2 or Port 3,  $\overline{BEx}$  for Port 1.

- 4. Timing depends on which signal is asserted last,  $\overline{CE}$  (or  $\overline{BEx}$ ) or  $\overline{OE}$ .

- 5. Timing depends on which signal is deasserted first,  $\overline{CE}$  (or  $\overline{BEx}$ ) or  $\overline{OE}$ .

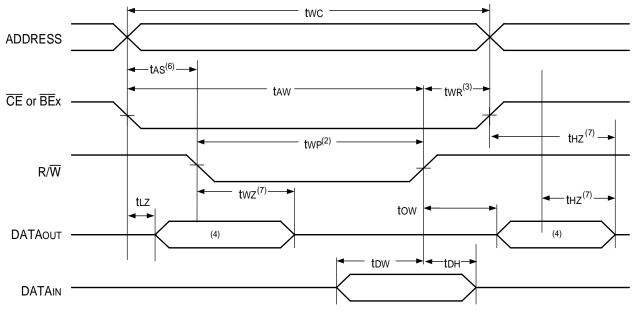

## AC Electrical Characteristics Over the Operating Temperature and Supply Voltage

|             |                                                   |      | 525X<br>Only |             |

|-------------|---------------------------------------------------|------|--------------|-------------|

| Symbol      | Parameter                                         | Min. | Max.         | Unit        |

| WRITE CYCLE |                                                   |      |              |             |

| twc         | Write Cycle Time                                  | 55   |              | ns          |

| tew         | Chip Enable to End-of-Write                       | 45   |              | ns          |

| taw         | Address Valid to End-of-Write                     | 45   |              | ns          |

| tas         | Address Set-up Time                               | 0    |              | ns          |

| twp         | Write Pulse Width <sup>(3)</sup>                  | 40   |              | ns          |

| twr         | Write Recovery Time                               | 0    |              | ns          |

| tow         | Data Valid to End-of-Write                        | 30   |              | ns          |

| tHZ         | Output High-Z Time <sup>(1,2)</sup>               |      | 25           | ns          |

| tDH         | Data Hold Time                                    | 0    |              | ns          |

| twz         | Write Enable to Output in High-Z <sup>(1,2)</sup> |      | 25           | ns          |

| tow         | Output Active from End-of-Write <sup>(1,2)</sup>  | 0    |              | ns          |

|             |                                                   |      | !            | 5681 tbl 11 |

NOTES:

1. Transition is measured 0mV from Low or High-impedance voltage with the Output Test Load (Figure 2).

2. This parameter is guaranteed by device characterization but is not production tested.

# Timing Waveform of Write Cycle No. 1, R/W Controlled Timing<sup>(5)</sup>

5681 drw 09

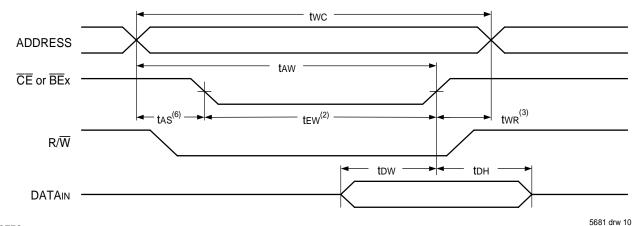

## Timing Waveform of Write Cycle No. 2, CE Controlled Timing<sup>(1,5)</sup>

#### NOTES:

- 1.  $R/\overline{W}$  or  $\overline{CE}$  (or  $\overline{BEx}$ ) = VIH during all address transitions.

- 2. A write occurs during the overlap (tew or twp) of a  $\overline{CE}$  (or  $\overline{BEx}$ ) = VIL and a R/W = VIL.

- 3. two is measured from the earlier of  $\overline{CE}$  (or  $\overline{BEx}$ ) or  $R/\overline{W} = V_{IH}$  to the end of write cycle.

- 4. During this period, the I/O pins are in the output state, and input signals must not be applied.

- 5. If the  $\overline{CE}$  (or  $\overline{BEx}$ ) LOW transition occurs simultaneously with or after the  $R/\overline{W} = V_{IL}$  transition, the outputs remain in the High-impedance state. 6. Timing depends on which enable signal is asserted last,  $\overline{CE}$  (or  $\overline{BEx}$ ) or  $R/\overline{W}$ .

- 7. Transition is measured 0mV from Low or High-impedance voltage with the Output Test Load (Figure 3). This parameter is guaranteed but is not production tested.

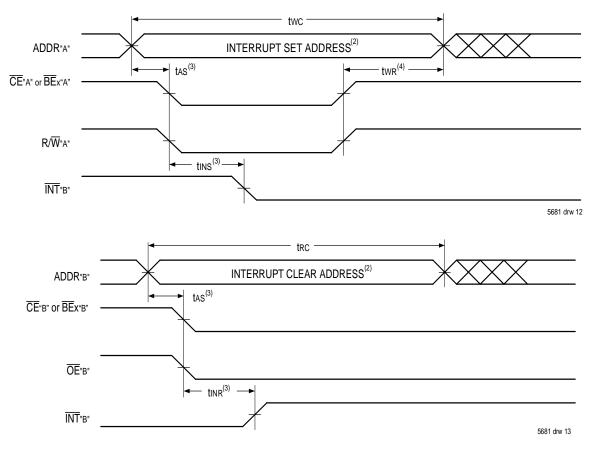

### **AC Electrical Characteristics Over the Operating Temperature and Supply Voltage Range**

|           |                      | 70X<br>Ind'l |      |      |

|-----------|----------------------|--------------|------|------|

| Symbol    | Parameter            | Min.         | Мах. | Unit |

| INTERRUPT | TIMING               |              |      |      |

| tas       | Address Set-up Time  | 0            |      | ns   |

| twr       | Write Recovery Time  | 0            |      | ns   |

| tins      | Interrupt Set Time   |              | 45   | ns   |

| tinr      | Interrupt Reset Time |              | 45   | ns   |

5681 tbl 12

# Waveform of Interrupt Timing<sup>(1)</sup>

#### NOTES:

- 1. If Port A is Port 1, Port B may be either Port 2 or Port 3. If Port A is either Port 2 or Port 3, Port B must be Port 1.

- 2. See Interrupt Truth Table II.

- 3. Timing depends on which enable signal ( $\overline{CE}$  or  $\overline{RW}$ ) is asserted last. 4. Timing depends on which enable signal ( $\overline{CE}$  or  $\overline{RW}$ ) is de-asserted first.

#### **Functional Description**

The IDT70X525X provides three ports with separate control, address, and I/O pins that permit independent access for reads or writes to the two banks of memory. These devices have an automatic power down feature controlled by  $\overline{BE}o$  and  $\overline{BE}1$  on Port 1 and  $\overline{CE}$  on Port 2 and Port 3. The  $\overline{CE}$  (or  $\overline{BEx}$ ) controls on-chip power down circuitry that permits the respective port to go into standby mode when not selected ( $\overline{CE}$  or  $\overline{BEx}$  = VIH). When Port 1 is enabled, it has access to the full memory. When Port 2 is active it has access to Bank 1 of the memory. When Port 3 is active it has access to Bank 2 of the memory. See Truth Table I for a description of the Read/Write operation.

| II GUII I    | $a \nu i \in I -$ | ncau/w |     |    |    |         |                                                                              |

|--------------|-------------------|--------|-----|----|----|---------|------------------------------------------------------------------------------|

|              | BE0               | BE1    | R/W | CE | ŌE | D0-D15  | Function                                                                     |

|              | Н                 | Н      | Х   | Х  | Х  | Z       | Port Deselected                                                              |

|              | L                 | Н      | L   | Х  | Х  | DATAIN  | Data on port written into Memory Bank 0                                      |

|              | L                 | Н      | Н   | Х  | L  | DATAout | Data in Memory Bank 0 output on port                                         |

| PORT 1       | Н                 | L      | L   | Х  | Х  | DATAIN  | Data on port written into Memory Bank 1                                      |

|              | Н                 | L      | Н   | Х  | L  | DATAout | Data in Memory Bank 1 output on port                                         |

|              | Х                 | Х      | Х   | Х  | Н  | Z       | Outputs Disabled                                                             |

|              | L                 | L      | Х   | Х  | Х  | Х       | Not Allowed                                                                  |

|              | Х                 | Х      | Х   | Н  | Х  | Z       | Port Deselected                                                              |

| PORT 2<br>or | Х                 | Х      | L   | L  | Х  | DATAIN  | Data on port written into Memory Bank <sup>(2)</sup>                         |

| PORT 3       | Х                 | Х      | Н   | L  | L  | DATAOUT | Data in Memory Bank <sup>(2)</sup> output on port                            |

|              | Х                 | Х      | Х   | Х  | Н  | Z       | Outputs Disabled                                                             |

|              | Н                 | Н      | Х   | Н  | Х  | Z       | $\overline{BE}0 = \overline{BE}1 = \overline{CE}_{P3} = V_{IH}$ , Sleep mode |

## Truth Table I - Read/Write Control

NOTE:

1. Both  $\overline{BE}_0$ , and  $\overline{BE}_1$  cannot be active ( $\overline{BE}x = V_{1L}$ ) simultaneously.

2. Memory Bank 0 for Port 2. Memory Bank 1 for Port 3.

5681 tbl 13

#### Interrupts

If the user chooses the interrupt function, a memory location (mailbox or message center) is assigned to each port. Interrupt P1 - P2 of Port 1 ( $\overline{INTP1} - P2$ ) is asserted when Port 2 writes to memory location FFE(HEX), where a write is defined as  $\overline{CE} = R/\overline{W} = V_{IL}$  per Truth Table II. Port 1 clears the interrupt by accessing address location FFE when  $\overline{BE0} = V_{IL}$ ,  $R/\overline{W}$  is a "don't care". Interrupt P1 - P3 of Port 1 ( $\overline{INTP1} - P3$ ) is asserted when Port 3 writes to memory location FFE (HEX), where a write is defined as  $\overline{CE} = R/\overline{W} = V_{IL}$ . Port 1 clears the interrupt by accessing address location FFE when  $\overline{BE}_1 = V_{IL}$ ,  $\overline{RW}$  is a "don't care". Port 2's interrupt flag ( $\overline{INT}_{P2}$ -P1) is asserted when Port 1 writes to memory location FFF (HEX), where a write is defined as  $\overline{BE}_0 = R/\overline{W} = V_{IL}$ . Port 2 clears the interrupt by accessing address location FFF when  $\overline{CE} = V_{IL}$ ,  $R/\overline{W}$  is a "don't care". Likewise, Port 3's interrupt flag ( $\overline{INT}_{P3}$ -P1) is asserted when Port 1 writes to memory location FFF (HEX), where a write is defined as  $\overline{BE}_1 = R/\overline{W} = V_{IL}$ . Port 3 clears the interrupt by accessing address location FFF when  $\overline{CE} = V_{IL}$ , R/W is a "don't care".

| Port 1 |             |     |    |          |                    |            | Port 2 or 3 |    |    |          |            |                                     |

|--------|-------------|-----|----|----------|--------------------|------------|-------------|----|----|----------|------------|-------------------------------------|

| R/₩    | <b>BE</b> 0 | BE1 | ŌĒ | A11 - A0 | <b>INT</b> p1 - p2 | INTp1 - p3 | R/W         | ĈĒ | ŌĒ | A11 - A0 | INTPx - P1 | Function                            |

| L      | L           | Н   | Х  | FFF      | х                  | х          | Х           | Х  | Х  | Х        | L          | Set P2 INT Flag                     |

| Х      | х           | Х   | Х  | х        | х                  | х          | Х           | L  | L  | FFF      | Н          | Reset P2 INT Flag                   |

| L      | Н           | L   | Х  | FFF      | х                  | х          | Х           | Х  | Х  | Х        | L          | Set P3 INT Flag                     |

| Х      | Х           | Х   | Х  | Х        | х                  | х          | Х           | L  | L  | FFF      | Н          | Reset P3 INT Flag                   |

| Х      | Х           | Х   | Х  | Х        | L                  | х          | L           | L  | Х  | FFE      | Х          | Set P1 INTP1-P2 Flag <sup>(1)</sup> |

| Х      | L           | Н   | L  | FFE      | Н                  | х          | Х           | Х  | Х  | Х        | Х          | Reset P1 INTP1-P2 Flag              |

| Х      | Х           | Х   | Х  | Х        | х                  | L          | L           | L  | Х  | FFE      | Х          | Set P1 INTP1-P3 Flag <sup>(2)</sup> |

| Х      | Н           | L   | L  | FFE      | х                  | Н          | Х           | Х  | Х  | Х        | Х          | Reset P1 INTP1-P3 Flag              |

## Truth Table II - Interrupt Flag

#### NOTE:

1. Port 2 sets the  $\overline{INT}_{P1 - P2}$  flag on Port 1 so all signals refer to Port 2.

2. Port 3 sets the  $\overline{INT}_{P1}$  -  $_{P3}$  flag on Port 1 so all signals refer to Port 3.

5681 tbl 14

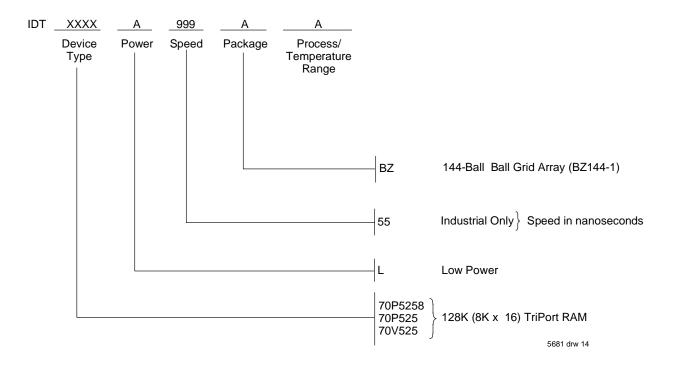

#### **Ordering Information**

## **Datasheet Document History**

| 10/14/03: | Initial datasheet                                                             |

|-----------|-------------------------------------------------------------------------------|

| 03/23/04: | Page 7 Corrected toH spec min to 5ns in AC Electrical CharacteristicsTable 10 |

CORPORATE HEADQUARTERS 2975 Stender Way Santa Clara, CA 95054

for SALES: 800-345-7015 or 408-727-6116 fax: 408-492-8674 www.idt.com

for Tech Support: 831-754-4613 DualPortHelp@idt.com

The IDT logo is a registered trademark of Integrated Device Technology, Inc.