# LIBERATOR CL10K50S

#### **Key Features**

LIBERATOR □ □ □

- ◆ Fully Compatible to the Altera® FLEX® 10KS Family

- ◆ Prototype Your System With Altera FPGAs

- ◆ Seamlessly Migrate Production To Clear Logic

- ◆ No ASIC Engineering, No NRE, And No Test Vector Development

- ◆ "Gate Array" Option Eliminates Configuration EPROMs

- ◆ Fabricated Using 0.25 Micron CMOS Process

- ◆ Very Low Power Consumption (Active And Standby)

- ♦ High Density

- 50,000 Usable Gates

- 2,880 Logic Elements

- 40,960 RAM Bits

- 254 Maximum User I/O Pins

#### **CL10KE Product Family Overview**

| Parameter                        | CL10K30E                                                     | CL10K50E<br>CL10K50S                                                                         | CL10K100E                                                                    | CL10K200E<br>CL10K200S                                                       |

|----------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| Typical Gates<br>(Logic and RAM) | 30,000                                                       | 50,000                                                                                       | 100,000                                                                      | 200,000                                                                      |

| Maximum System Gates             | 119,000                                                      | 199,000                                                                                      | 257,000                                                                      | 513,000                                                                      |

| Logic Elements                   | 1,728                                                        | 2,880                                                                                        | 4,992                                                                        | 9,984                                                                        |

| Embedded Array Blocks            | 6                                                            | 10                                                                                           | 12                                                                           | 24                                                                           |

| Total RAM Bits                   | 24,576                                                       | 40,960                                                                                       | 49,152                                                                       | 98,304                                                                       |

| Max User I/O pins                | 220                                                          | 254                                                                                          | 338                                                                          | 470                                                                          |

| Speed Grades                     | -1, -2, -3                                                   | -1, -2, -3                                                                                   | -1, -2, -3                                                                   | -1, -2, -3                                                                   |

| Packages                         | 144-pin TQFP<br>208-pin PQFP<br>256-pin FBGA<br>484-pin FBGA | 144-pin TQFP<br>208-pin PQFP<br>240-pin PQFP<br>256-pin FBGA<br>356-pin SBGA<br>484-pin FBGA | 208-pin PQFP<br>240-pin PQFP<br>256-pin FBGA<br>356-pin SBGA<br>484-pin FBGA | 240-pin PQFP<br>356-pin SBGA<br>484-pin FBGA<br>600-pin SBGA<br>672-pin FBGA |

10KE tbl 01

June 2001 Page 1

#### **Description**

The LIBERATOR™ CL10KS family offers you all of the time-to-market benefits of designing with programmable logic. Simply use Altera FLEX 10KS FPGAs to prototype and verify the design. Then, take five minutes to submit the bitstream using Clear Logic's web site! Within eight weeks, your system can be in volume production using compatible Clear Logic devices.

LIBERATOR technology frees you to completely design, prototype, and verify your custom logic using Altera FLEX 10KS products. Clear Logic's innovative technology eliminates NRE costs, test vector development, ordering minimums, and long lead times. No re-simulation or re-layout is required, because Clear Logic offers an architecture that is exactly compatible to the functionality of the FPGA prototype. Clear Logic's NoFault® test technology ensures complete test coverage through the use of special scan test registers.

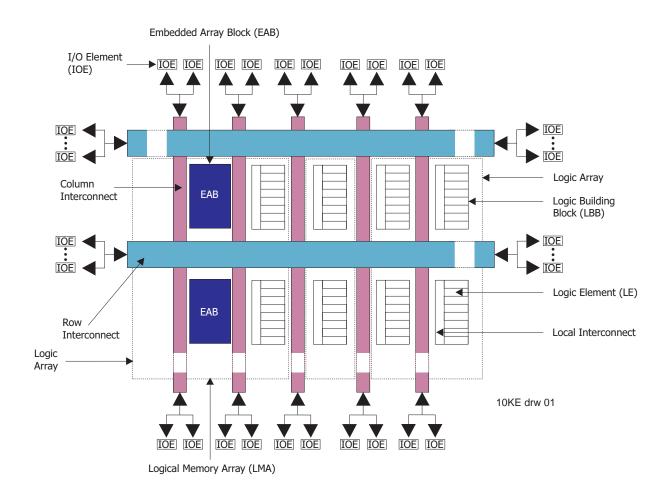

The LIBERATOR family is based upon an array of logic elements. Each logic element contains a configurable look-up table for combinatorial functions and a register for sequential operations. Eight logic elements in a group form a block. Logic functions and signal routing are defined by Clear Logic's proprietary vertical metal links.

Laser-based configuration allows quick-turn prototyping and eliminates NRE costs for photomasks. Inherent CL10KS family performance benefits include extremely consistent propagation delays, reduced power consumption, and improved immunity to noise and upset events.

#### Configuration

The "Gate Array" configuration mode eliminates the need for external EPROMs or software configuration. The LIBERATOR device is already factory-configured when it is shipped. When using the device in the "Gate Array" mode, it powers up fully configured. In this mode, if the customer selects INIT\_DONE option, this pin will always be high.

# Additional Information

For further information on designing with the LIBERATOR family, please refer to these documents:

- ◆ AN-01: Requesting a First Article. This document provides instructions on how to request first articles by submitting a bitstream file to Clear Logic's web site.

- ◆ AN-02: Clear Logic Packaging Guide. This document provides specifications and drawings for packages used by the CL10K family and other Clear Logic devices.

- ◆ AN-13: LIBERATOR -- A New Way To Design. This document describes the most efficient path for custom logic designs up to 200K gates using FPGA design techniques and going to production with Clear Logic.

- ◆ AN-14: CL10K Technology White Paper. This document outlines the technologies employed by the LIBERATOR family.

- ◆ AN-15: LIBERATOR System Configuration. This document contains a detailed discussion of all aspects of configuring CL10K-based systems.

- ◆ AN-16: Introduction to the Clear Logic Verilog Model Generator. Clear Logic now has Verilog models of your FPGA converted design. Learn what it is and how it can help you.

- ◆ AN-17: Clear Logic LIBERATOR Design Models. This document outlines the capabilities and freedom available in the Clear Logic Verilog and VHDL design models.

- ◆ AN-18: Debugging Designs Using Clear Logic Models. This document shows the enhanced troubleshooting capabilities that the Clear Logic LIBERATOR Verilog/VHDL design models bring to the system debugging process.

# **Block Diagram**

| Pin Name  | 144-Pin TQFP | 208-Pin PQFP | 240-Pin PQFP |

|-----------|--------------|--------------|--------------|

| MSEL0     | 77           | 108          | 124          |

| MSEL1     | 76           | 107          | 123          |

| nSTATUS   | 35           | 52           | 60           |

| nCONFIG   | 74           | 105          | 121          |

| DCLK      | 107          | 155          | 179          |

| CONF_DONE | 2            | 2            | 2            |

| INIT_DONE | 14           | 19           | 26           |

| nCE       | 106          | 154          | 178          |

| nCEO      | 3            | 3            | 3            |

| nWS       | 142          | 206          | 238          |

| nRS       | 141          | 204          | 236          |

| nCS       | 144          | 208          | 240          |

| cs        | 143          | 207          | 239          |

| RDYnBSY   | 11           | 16           | 23           |

| CLKUSR    | 7            | 10           | 11           |

| DATA7     | 116          | 166          | 190          |

| DATA6     | 114          | 164          | 188          |

| DATA5     | 113          | 162          | 186          |

| DATA4     | 112          | 161          | 185          |

| DATA3     | 111          | 159          | 183          |

| DATA2     | 110          | 158          | 182          |

| DATA1     | 109          | 157          | 181          |

| DATA0     | 108          | 156          | 180          |

10K50S tbl 01A

| Pin Name             | 144-Pin TQFP                                                                  | 208-Pin PQFP                                                 | 240-Pin PQFP                                                                           |

|----------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------|

| TDI                  | 105                                                                           | 153                                                          | 177                                                                                    |

| TDO                  | 4                                                                             | 4                                                            | 4                                                                                      |

| тск                  | 1                                                                             | 1                                                            | 1                                                                                      |

| TMS                  | 34                                                                            | 50                                                           | 58                                                                                     |

| TRST                 |                                                                               | 51                                                           | 59                                                                                     |

| Dedicated Inputs     | 54, 56, 124, 126                                                              | 78, 80, 182, 184                                             | 90, 92, 210, 212                                                                       |

| Dedicated Clock Pins | 55, 125                                                                       | 79, 183                                                      | 91, 211                                                                                |

| DEV_CLRn             | 122                                                                           | 180                                                          | 209                                                                                    |

| DEV_OE               | 128                                                                           | 186                                                          | 213                                                                                    |

| VCCINT               | 6, 25, 52, 53, 75, 93, 123                                                    | 6, 23, 35, 43, 76, 106, 109,<br>117, 137, 145, 181           | 5, 27, 47, 96, 122, 130, 150,<br>170                                                   |

| VCCIO                | 5, 24, 45, 61, 71, 94, 115, 134                                               | 5, 22, 34, 42, 66, 84, 98, 110, 118, 138, 146, 165, 178, 194 | 16, 37, 57, 77, 112, 140, 160,<br>189, 205, 224                                        |

| VCC_CKLK             | 53                                                                            | 77                                                           | 89                                                                                     |

| GNDINT               | NDINT 15, 16, 40, 50, 58, 66, 84, 85, 82, 91, 123, 124, 129, 130, 104, 125, 1 |                                                              | 10, 22, 32, 42, 52, 69, 85, 93,<br>104, 125, 135, 145, 155, 165,<br>176, 197, 216, 232 |

| GND_CKLK             | 57                                                                            | 81                                                           | 93                                                                                     |

| No Connect           | -                                                                             | -                                                            | -                                                                                      |

| Total user I/O Pins  | 102                                                                           | 147                                                          | 189                                                                                    |

10K50S tbl 01B

| Pin Name             | 256-Pin FBGA   | 356-Pin SBGA         | 484-Pin FBGA       |

|----------------------|----------------|----------------------|--------------------|

| MSEL0                | P1             | D4                   | U4                 |

| MSEL1                | R1             | D3                   | V4                 |

| nSTATUS              | T16            | D24                  | W19                |

| nCONFIG              | N4             | D2                   | Т7                 |

| DCLK                 | B2             | AC5                  | E5                 |

| CONF_DONE            | C15            | AC24                 | F18                |

| INIT_DONE            | G16            | T24                  | K19                |

| nCE                  | B1             | AC2                  | E4                 |

| nCEO                 | B16            | AC22                 | E19                |

| nWS                  | B14            | AE24                 | E17                |

| nRS                  | C14            | AE23                 | F17                |

| nCS                  | A16            | AD24                 | D19                |

| cs                   | A15            | AD23                 | D18                |

| RDYnBSY              | G14            | U22                  | K17                |

| CLKUSR               | D15            | AA24                 | G18                |

| DATA7                | B5             | AF4                  | E8                 |

| DATA6                | D4             | AD8                  | G7                 |

| DATA5                | A4             | AE5                  | D7                 |

| DATA4                | B4             | AD6                  | E7                 |

| DATA3                | C3             | AF2                  | F6                 |

| DATA2                | A2             | AD5                  | D5                 |

| DATA1                | В3             | AD4                  | E6                 |

| DATA0                | A1             | AD3                  | D4                 |

| TDI                  | C2             | AC3                  | F5                 |

| TDO                  | C16            | AC23                 | F19                |

| тск                  | B15            | AD25                 | E18                |

| TMS                  | P15            | D22                  | U18                |

| TRST                 | R16            | D23                  | V19                |

| Dedicated Inputs     | B9, E8, M9, R9 | A13, B14, AF14, AE13 | E12, H11, R12, V11 |

| Dedicated Clock Pins | A9, L8         | A14, AF13            | D12, P11           |

10K50S tbl 01C

| Pin Name            | 256-Pin FBGA                                                                   | 356-Pin SBGA                                                                                                                                                                                                                                                                      | 484-Pin FBGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DEV_CLRn            | D8                                                                             | AD13                                                                                                                                                                                                                                                                              | G11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| DEV_OE              | C9                                                                             | AE14                                                                                                                                                                                                                                                                              | F12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| VCCINT              | E11, F5, F7, F9, F12, H6, H7,<br>H10, J7, J10, J11, K9, L5,L7,<br>L12, M11, R2 | A1, A26, C26, D5, F1, H22, J1,<br>M26, N1, T26, U5, AA1, AD26,<br>AF1, AF26                                                                                                                                                                                                       | C11, C15, H14, J8, J10, J12,<br>J15, L9, L10, L13, M10, M13,<br>M14, N12, P8, P10, P15, R14,<br>V5, W21, Y8, AA12                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| VCCIO               | D12, E6, F8, F10, G6, G8, G11,<br>H11, J6, K6, K8, K11, L10, M6,<br>N12        | A7, A23, B3, C15, D25, F4,<br>H24, K5, M23, P2, T25, V2,<br>W22, AB1, AC25, AD18M, AF3,<br>AF7, AF16                                                                                                                                                                              | A6, A13, B5, E1, G1, G15, H9,<br>H20, J11, J13, K9, K11, K14,<br>K20, L14, M9, N3, N9, N11,<br>N14, N20, P13, R1, R9, T3,<br>T15, T22, V22, AB13                                                                                                                                                                                                                                                                                                                                                                                                                    |

| VCC_CKLK            | L9                                                                             | C14                                                                                                                                                                                                                                                                               | P12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| GND                 | E5, E12, F6, F11, G7, G9, G10,<br>H8, H9, J8, J9, K7, K10, L6,<br>L11, M5, M12 | A2, A10, A20, B1, B22, B25,<br>B26, C2, C9, C13, C25, H23,<br>J26, K1, M1, N26, R1, R26, T1,<br>U26, W1, AD2, AD14, AD20,<br>AE1, AE2, AE7, AE25, AE26,<br>AF11, AF19, AF25                                                                                                       | A1, A8, A22, B1, B2, B17, B21, B22, C2, C21, E21, G3, G21, H2, H8, H15, J9, J14, J20, K3, K10, K12, K13, L11, L12, M11, M12, M20, N10, N13, P9, P14, R8, R15, R22, T1, V3, W20, Y1, Y2, Y3, Y21, Y22, AA1, AA6, AA22, AB11, AB16                                                                                                                                                                                                                                                                                                                                    |

| GND_CKLK            | Т8                                                                             | B13                                                                                                                                                                                                                                                                               | W11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| No Connect          | _                                                                              | D1, E2, E22, E25, F5, F23,<br>F26, G3, G22. G25, H4, H5, J2,<br>J4, J23, J24, K2, K3, K25, K26,<br>L2, L23, L26, M2, M5, M22,<br>M25, N4, N25, P1, P5, P22,<br>P23, R5, T22, U2, U3, U23,<br>U24, V4, W3, W4, W24, W26,<br>Y2, Y5, AA3, AA22, AA25, AB3,<br>AB5, AB22, AB24, AB26 | A2, A3. A4. A5, A7, A9, A11, A12, A14, A15, A20, A21, B3, B4, B9, B10, B12, B16, B19, B20, C1, C6, C9, C10, C12, C13, C14, C16, C17, C22, D1, D2, D3, D20, D21, E2, E3, E20, E22, F1, F2, F20, F21, G2, G20, G22, J1, J2, J3, J21, K1, K2, K22, L1, L2, L20, L22, M2, M3, M22, N1, N2, N21, N22, P3, P20, P21, P22, R2, R3, R21, T2, T20, T21, U1, U2, U3, U20, U21, U22, V2, V20, W1, W2, W22, Y4, Y9, Y12, Y13, Y16, Y19, Y20, AA2, AA3, AA4, AA9, AA11, AA13, AA15, AA21, AB1, AB2, AB3, AB4, AB5, AB7, AB8, AB9, AB12, AB15, AB17, AB18, AB19, AB20, AB21, AB22 |

| Total user I/O Pins | 191                                                                            | 220                                                                                                                                                                                                                                                                               | 254                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

10K50S tbl 01D

# **DC Electrical Specifications**

#### **Absolute Maximum Ratings**

| Symbol           | Parameter                       | Conditions | Min  | Max  | Unit |

|------------------|---------------------------------|------------|------|------|------|

| V <sub>CC</sub>  | Supply Voltage                  |            | -0.5 | 3.6  | V    |

| V <sub>I</sub>   | DC Input Voltage <sup>[1]</sup> |            | -2.0 | 5.75 | V    |

| I <sub>OUT</sub> | DC Output Current, per Pin      |            | -25  | 25   | mA   |

| T <sub>STG</sub> | Storage Temperature             | No Bias    | -65  | 150  | °C   |

| T <sub>AMB</sub> | Ambient Temperature             | Under Bias | -65  | 135  | °C   |

| TJ               | Junction Temperature            | Under Bias |      | 135  | °C   |

10KE tbl 02

#### Recommended Operating Conditions [2]

| Symbol             | Parameter                                                                                                | Conditions | Min            | Max            | Unit     |

|--------------------|----------------------------------------------------------------------------------------------------------|------------|----------------|----------------|----------|

| V <sub>CCINT</sub> | Supply Voltage, Internal Logic and Input Buffers<br>Commercial Grade Devices<br>Industrial Grade Devices |            | 2.375<br>2.375 | 2.625<br>2.625 | V        |

| V <sub>CCIO</sub>  | DC Input Voltage for 3.3V Operation Commercial Grade Devices Industrial Grade Devices                    |            | 3.00<br>3.00   | 3.60<br>3.60   | V<br>V   |

| V <sub>CCIO</sub>  | DC Input Voltage for 2.5V Operation Commercial Grade Devices Industrial Grade Devices                    |            | 2.375<br>2.375 | 2.625<br>2.625 | V<br>V   |

| V <sub>I</sub>     | Input Voltage                                                                                            |            | -0.5           | 5.75           | V        |

| V <sub>O</sub>     | Output Voltage                                                                                           |            | 0              | VCCIO          | V        |

| T <sub>A</sub>     | Operating Temperature Commercial Temperature Range Industrial Temperature Range                          |            | 0<br>-40       | 70<br>85       | °C<br>°C |

| t <sub>R</sub>     | Input Signal Rise Time                                                                                   |            |                | 40             | ns       |

| t <sub>F</sub>     | Input Signal Fall Time                                                                                   |            |                | 40             | ns       |

|                    |                                                                                                          |            |                |                |          |

10KE tbl 03B

#### ${f DC}$ Electrical Characteristics (over the operating range)

| Symbol           | Parameter                               | Conditions                                              | Min                                            | Typ <sup>[3]</sup> | Max                     | Unit |

|------------------|-----------------------------------------|---------------------------------------------------------|------------------------------------------------|--------------------|-------------------------|------|

| V <sub>IH</sub>  | Input HIGH Voltage                      |                                                         | Lower of<br>1.7 or 0.5<br>x V <sub>CCINT</sub> |                    | 5.75                    | V    |

| V <sub>IL</sub>  | Input LOW Voltage                       |                                                         | -0.5                                           |                    | 0.3 x V <sub>CCIO</sub> | V    |

|                  | 3.3-V High-Level TTL Output<br>Voltage  | I <sub>OH</sub> = -8 mA DC, V <sub>CCIO</sub> = 3.00 V  | 2.4                                            |                    |                         | V    |

|                  | 3.3-V High-Level CMOS<br>Output Voltage | $I_{OH}$ = -0.1 mA DC, $V_{CCIO}$ = 3.00 V              | V <sub>CCIO</sub> -0.2                         |                    |                         | V    |

| $V_{OH}$         | 3.3-V High-Level PCI Output Voltage     | $I_{OH}$ = -0.5 mA DC, $V_{CCIO}$ = 3 to 3.60 V         | 0.9 x V <sub>CCIO</sub>                        |                    |                         | V    |

| VOH              |                                         | $I_{OH}$ = -0.1 mA DC, $V_{CCIO}$ = 2.30 V              | 2.1                                            |                    |                         | V    |

|                  | 2.5-V High-Level Output<br>Voltage      | I <sub>OH</sub> = -1 mA DC, V <sub>CCIO</sub> = 2.30 V  | 2.0                                            |                    |                         | V    |

|                  |                                         | I <sub>OH</sub> = -2 mA DC, V <sub>CCIO</sub> = 2.30 V  | 1.7                                            |                    |                         | V    |

|                  | 3.3-V Low-Level TTL Output<br>Voltage   | I <sub>OL</sub> = 9 mA DC, V <sub>CCIO</sub> = 3.00 V   |                                                |                    | 0.45                    | V    |

|                  | 3.3-V Low-Level CMOS<br>Output Voltage  | I <sub>OL</sub> = 0.1 mA DC, V <sub>CCIO</sub> = 3.00 V |                                                |                    | 0.2                     | V    |

| $V_{OL}$         | 3.3-V Low-Level PCI Output<br>Voltage   | $I_{OL}$ = 1.5 mA DC, $V_{CCIO}$ = 3 to 3.60 V          |                                                |                    | 0.1 x V <sub>CCIO</sub> | V    |

| VOL              |                                         | $I_{OL} = 0.1 \text{ mA DC}, V_{CCIO} = 2.30 \text{ V}$ |                                                |                    | 0.2                     | V    |

|                  | 2.5-V Low-Level Output<br>Voltage       | I <sub>OL</sub> = 1 mA DC, V <sub>CCIO</sub> = 2.30 V   |                                                |                    | 0.4                     | V    |

|                  |                                         | I <sub>OL</sub> = 2 mA DC, V <sub>CCIO</sub> = 2.30 V   |                                                |                    | 0.7                     | V    |

| I <sub>IN</sub>  | Input Leakage Current                   | V <sub>I</sub> = 5.3V to -0.3V                          | -10                                            |                    | 10                      | μΑ   |

| l <sub>oz</sub>  | Output Leakage Current                  | V <sub>O</sub> = 5.3V to -0.3V                          | -10                                            |                    | 10                      | μΑ   |

| I <sub>CC0</sub> | Standby Current                         | V <sub>I</sub> = GND, No Load                           |                                                | 5                  |                         | mA   |

|                  |                                         |                                                         |                                                |                    | 10KE thi                | 04   |

10KE tbl 04

#### $Capacitance^{[4]} \\$

| Symbol           | Parameter          | Conditions                          | Min | Max   | Unit   |

|------------------|--------------------|-------------------------------------|-----|-------|--------|

| C <sub>IN</sub>  | Input Capacitance  | $V_{IN} = 0 V, f = 1.0 MHz$         |     | 10    | pF     |

| C <sub>OUT</sub> | Output Capacitance | V <sub>OUT</sub> = 0 V, f = 1.0 MHz |     | 10    | pF     |

|                  |                    |                                     |     | 10KE1 | tbl 05 |

| I/O Element Timing Parameters [5] |                                                                                            | <sup>5]</sup> Spee | ] Speed: -1 |     | Speed: -2 |     | Speed: -3 |      |

|-----------------------------------|--------------------------------------------------------------------------------------------|--------------------|-------------|-----|-----------|-----|-----------|------|

| Symbol                            | Parameter                                                                                  | Min                | Max         | Min | Max       | Min | Max       | Unit |

| t <sub>IOD</sub>                  | IOE Register Data Delay                                                                    |                    | 2.4         |     | 2.8       |     | 3.8       | ns   |

| t <sub>IOC</sub>                  | IOE Register Control Signal Delay                                                          |                    | 0.3         |     | 0.3       |     | 0.5       | ns   |

| t <sub>loco</sub>                 | IOE Register Clock to Output Delay                                                         |                    | 0.2         |     | 0.2       |     | 0.3       | ns   |

| t <sub>IOCOMB</sub>               | IOE Combinatorial Delay                                                                    |                    | 0.5         |     | 0.6       |     | 0.8       | ns   |

| t <sub>iosu</sub>                 | IOE Register Setup Time Before Clock                                                       | 2.2                |             | 2.6 |           | 3.5 |           | ns   |

| t <sub>IOH</sub>                  | IOE Register Hold Time After Clock                                                         | 0.5                |             | 0.6 |           | 0.8 |           | ns   |

| t <sub>IOCLR</sub>                | IOE Register Clear Delay                                                                   |                    | 0.2         |     | 0.2       |     | 0.3       | ns   |

| t <sub>OD1</sub>                  | Output Buffer and Pad Delay Slow Slew Rate = off, VCCIO = V <sub>CCINT</sub>               |                    | 1.1         |     | 1.3       |     | 1.8       | ns   |

| t <sub>OD2</sub>                  | Output Buffer and Pad Delay<br>Slow Slew Rate = off, VCCIO = Low Voltage                   |                    | 0.6         |     | 0.9       |     | 1.6       | ns   |

| t <sub>OD3</sub>                  | Output Buffer and Pad Delay<br>Slow Slew Rate = on                                         |                    | 3.0         |     | 3.5       |     | 4.8       | ns   |

| t <sub>ZX</sub>                   | Output Buffer Disable Delay <sup>[6]</sup>                                                 |                    | 1.1         |     | 1.3       |     | 1.8       | ns   |

| t <sub>ZX1</sub>                  | Output Buffer Disable Delay Slow Slew Rate = off, VCCIO = V <sub>CCINT</sub> [6]           |                    | 1.1         |     | 1.3       |     | 1.6       | ns   |

| t <sub>zx2</sub>                  | Output Buffer Disable Delay<br>Slow Slew Rate = off, VCCIO = Low<br>Voltage <sup>[6]</sup> |                    | 0.6         |     | 0.9       |     | 1.6       | ns   |

| t <sub>zx3</sub>                  | Output Buffer Disable Delay<br>Slow Slew Rate = on <sup>[6]</sup>                          |                    | 3.0         |     | 3.5       |     | 4.8       | ns   |

| t <sub>INREG</sub>                | IOE Input Pad and Buffer to IOE Register<br>Delay                                          |                    | 5.0         |     | 5.9       |     | 8.0       | ns   |

| t <sub>IOFD</sub>                 | IOE Register Feedback Delay                                                                |                    | 3.0         |     | 3.6       |     | 4.8       | ns   |

| t <sub>INCOMB</sub>               | IOE Input Pad and Buffer to Interconnect Delay                                             |                    | 3.0         |     | 3.6       |     | 4.8       | ns   |

10KE tbl 06A

| External | Timing | Parameters <sup>[4]</sup> | Speed: -1 |

|----------|--------|---------------------------|-----------|

|          |        |                           |           |

| External Timing Parameters[4] |                                                                                                      | Speed: -1 |     | Speed: -2 |      | Speed: -3 |      |      |

|-------------------------------|------------------------------------------------------------------------------------------------------|-----------|-----|-----------|------|-----------|------|------|

| Symbol                        | Parameter                                                                                            | Min       | Max | Min       | Max  | Min       | Max  | Unit |

| t <sub>DRR</sub>              | Register to Register Delay via Four LEs,<br>Three Row Interconnects, and Four Local<br>Interconnects |           | 8.5 |           | 10.0 |           | 13.5 | ns   |

| t <sub>INSU</sub>             | Setup Time with Global Clock at IOE<br>Register                                                      | 3.0       |     | 3.6       |      | 4.8       |      | ns   |

| t <sub>INH</sub>              | Hold time with Global Clock at IOE Register                                                          | 0.0       |     | 0.0       |      | 0.0       |      | ns   |

| t <sub>outco</sub>            | Output Data Hold Time After Clock                                                                    | 2.0       | 3.5 | 2.0       | 4.5  | 2.0       | 7.1  | ns   |

10KE tbl 07C

#### Logic Element Timing Parameters<sup>[5]</sup>

|                     | Diement Timing Latameter                        | Speed: -1 |     | Speed: -2 |     | Speed: -3 |     |      |

|---------------------|-------------------------------------------------|-----------|-----|-----------|-----|-----------|-----|------|

| Symbol              | Parameter                                       | Min       | Max | Min       | Max | Min       | Max | Unit |

| t <sub>LUT</sub>    | Look-up Table Delay for Data-in                 |           | 0.6 |           | 8.0 |           | 1.1 | ns   |

| t <sub>CLUT</sub>   | Look-up Table Delay for Carry-in                |           | 0.5 |           | 0.6 |           | 0.8 | ns   |

| t <sub>RLUT</sub>   | Look-up Table Delay for LE Register<br>Feedback |           | 0.7 |           | 0.8 |           | 1.1 | ns   |

| t <sub>PACKED</sub> | Data-in to Packed Register Delay                |           | 0.5 |           | 0.6 |           | 0.8 | ns   |

| t <sub>EN</sub>     | LE Register Enable Delay                        |           | 0.6 |           | 0.7 |           | 0.9 | ns   |

| t <sub>CICO</sub>   | Carry-in to Carry-out Delay                     |           | 0.2 |           | 0.2 |           | 0.3 | ns   |

| t <sub>CGEN</sub>   | Data-in to Carry-out Delay                      |           | 0.5 |           | 0.5 |           | 0.8 | ns   |

| t <sub>CGENR</sub>  | LE Register Feedback to Carry-out Delay         |           | 0.2 |           | 0.2 |           | 0.3 | ns   |

| t <sub>CASC</sub>   | Cascade Chain Routing Ddelay                    |           | 0.8 |           | 0.9 |           | 1.2 | ns   |

| t <sub>C</sub>      | LE Register Control Signal Delay                |           | 0.5 |           | 0.6 |           | 0.8 | ns   |

| t <sub>CO</sub>     | LE Register Clock-to-output Delay               |           | 0.5 |           | 0.6 |           | 0.7 | ns   |

| t <sub>COMB</sub>   | Combinatorial Delay                             |           | 0.5 |           | 0.6 |           | 0.7 | ns   |

| t <sub>SU</sub>     | LE Register Setup Time Before Clock             | 0.5       |     | 0.6       |     | 0.8       |     | ns   |

| t <sub>H</sub>      | LE Register Hold Time After Clock               | 0.9       |     | 1.1       |     | 1.5       |     | ns   |

| t <sub>PRE</sub>    | LE Register Preset Delay                        |           | 0.5 |           | 0.6 |           | 0.8 | ns   |

| t <sub>CLR</sub>    | LE Register Clear Delay                         |           | 0.5 |           | 0.6 |           | 0.8 | ns   |

| t <sub>CH</sub>     | Clock High Time                                 | 2.0       |     | 2.5       |     | 3.0       |     | ns   |

| t <sub>CL</sub>     | Clock Low Time                                  | 2.0       |     | 2.5       |     | 3.0       |     | ns   |

10KE tbl 08A

#### Interconnect Timing Parameters<sup>[5]</sup>

|                         | Speed: -1                                                                            |         | Speed: -2 | Speed: -3 |      |  |

|-------------------------|--------------------------------------------------------------------------------------|---------|-----------|-----------|------|--|

| Symbol                  | Parameter                                                                            | Min Max | Min Max   | Min Max   | Unit |  |

| t <sub>DIN2IOE</sub>    | Delay from dedicated input pin to IOE control input                                  | 4.1     | 4.6       | 5.9       | ns   |  |

| t <sub>DIN2LE</sub>     | Delay from dedicated input pin to LE or EAB control input                            | 0.9     | 1.0       | 1.3       | ns   |  |

| t <sub>DIN2DATA</sub>   | Delay from dedicated input or clock pin to LE or EAB data                            | 1.8     | 1.9       | 2.3       | ns   |  |

| t <sub>DCLK2IOE</sub>   | Delay from dedicated clock pin to IOE clock                                          | 3.9     | 4.6       | 6.2       | ns   |  |

| t <sub>DCLK2LE</sub>    | Delay from dedicated clock pin to LE or EAB clock                                    | 0.9     | 1.0       | 1.3       | ns   |  |

| t <sub>SAMELAB</sub>    | Delay from an LE to LE in same LAB                                                   | 0.1     | 0.1       | 0.2       | ns   |  |

| t <sub>SAMEROW</sub>    | Delay for driving a row IOE, LE or EAB to a row IOE, LE or EAB in the same row       | 1.3     | 1.3       | 1.8       | ns   |  |

| t <sub>SAMECOLUMN</sub> | Delay from an LE to IOE in the same column                                           | 0.7     | 0.8       | 1.5       | ns   |  |

| t <sub>DIFFROW</sub>    | Delay for driving a column IOE, LE or EAB to an LE or EAB in a different row         | 2.0     | 2.1       | 3.3       | ns   |  |

| t <sub>TWOROWS</sub>    | Delay for driving a row IOE or EAB to an LE or EAB in a different row                | 3.3     | 3.4       | 5.1       | ns   |  |

| t <sub>LEPERIPH</sub>   | Delay from an LE to IOE control signal via the peripheral contol bus                 | 3.8     | 4.1       | 5.3       | ns   |  |

| t <sub>LABCARRY</sub>   | Delay from an LE carry-out signal to an LE carry-in signal in a different LAB        | 0.1     | 0.1       | 0.2       | ns   |  |

| t <sub>LABCASC</sub>    | Delay from an LE cascade-out signal to an<br>LE cascade-in signal in a different LAB | 0.3     | 0.3       | 0.5       | ns   |  |

10KE tbl 09C

# EAB Timing Parameters<sup>[5]</sup>

|                        |                                                              | Speed: -1 |     | Speed: -2 |     | Speed: -3 |     |      |

|------------------------|--------------------------------------------------------------|-----------|-----|-----------|-----|-----------|-----|------|

| Symbol                 | Parameter                                                    | Min       | Max | Min       | Max | Min       | Max | Unit |

| t <sub>EABDATA1</sub>  | Delay from Data or Address to EAB for<br>Combinatorial Input |           | 1.7 |           | 2.0 |           | 2.7 | ns   |

| t <sub>EABDATA2</sub>  | Delay from Data or Address to EAB for<br>Registered Input    |           | 0.6 |           | 0.7 |           | 0.9 | ns   |

| t <sub>EABWE1</sub>    | WE Delay to EAB for Combinatorial Input                      |           | 1.1 |           | 1.3 |           | 1.8 | ns   |

| t <sub>EABWE2</sub>    | WE Delay to EAB for Registered Input                         |           | 0.4 |           | 0.4 |           | 0.6 | ns   |

| t <sub>EABCLK</sub>    | EAB Register Clock Delay                                     |           | 0.0 |           | 0.0 |           | 0.0 | ns   |

| t <sub>EABCO</sub>     | EAB Register Clock-to-output Delay                           |           | 0.3 |           | 0.3 |           | 0.5 | ns   |

| t <sub>EABBYPASS</sub> | Bypass Register Delay                                        |           | 0.5 |           | 0.6 |           | 0.8 | ns   |

| t <sub>EABSU</sub>     | EAB Register Setup Time                                      | 0.9       |     | 1.0       |     | 1.4       |     | ns   |

| t <sub>EABH</sub>      | EAB Register Hold Time                                       | 0.4       |     | 0.4       |     | 0.6       |     | ns   |

| t <sub>AA</sub>        | Address Access Delay                                         |           | 3.2 |           | 3.8 |           | 5.1 | ns   |

| t <sub>WP</sub>        | Write Pulse Width                                            | 2.5       |     | 2.9       |     | 3.9       |     | ns   |

| t <sub>wosu</sub>      | Data Setup Time Before Falling Edge of Write Pulse           | 0.9       |     | 1.0       |     | 1.4       |     | ns   |

| t <sub>WDH</sub>       | Data Hold Time After Falling Edge of Write<br>Pulse          | 0.1       |     | 0.1       |     | 0.2       |     | ns   |

| t <sub>WASU</sub>      | Address Setup Time Before Rising Edge of Write Pulse         | 1.7       |     | 2.0       |     | 2.7       |     | ns   |

| t <sub>WAH</sub>       | Address Hold After Falling Edge of Write Pulse               | 1.8       |     | 2.1       |     | 2.9       |     | ns   |

| t <sub>WO</sub>        | Write Enable to Date Output Delay                            |           | 2.5 |           | 2.9 |           | 3.9 | ns   |

| t <sub>DD</sub>        | Data-in to Date-out Delay                                    |           | 2.5 |           | 2.9 |           | 3.9 | ns   |

| t <sub>EABOUT</sub>    | Data-out Delay                                               |           | 0.5 |           | 0.6 |           | 0.8 | ns   |

| t <sub>EABCH</sub>     | Clock High Time                                              | 1.5       |     | 2.0       |     | 2.5       |     | ns   |

| t <sub>EABCL</sub>     | Clock Low Time                                               | 1.5       |     | 2.0       |     | 2.5       |     | ns   |

|                        | -                                                            |           |     |           |     |           |     |      |

10KE tbl 10A

#### EAB Timing Parameters<sup>[5]</sup>

|                        |                                                                                              | Speed: -1 |     | Speed: -2 |     | Speed: -3 |      |             |

|------------------------|----------------------------------------------------------------------------------------------|-----------|-----|-----------|-----|-----------|------|-------------|

| Symbol                 | Parameter                                                                                    | Min       | Max | Min       | Max | Min       | Max  | Unit        |

| t <sub>EABAA</sub>     | EAB Address Access Delay                                                                     |           | 6.4 |           | 7.6 |           | 10.2 | ns          |

| t <sub>EABRCCOMB</sub> | EAB Asynchronous Read Cycle Time                                                             | 6.4       |     | 7.6       |     | 10.2      |      | ns          |

| t <sub>EABRCREG</sub>  | EAB Synchronous Read Cycle Time                                                              | 4.4       |     | 5.1       |     | 7.0       |      | ns          |

| t <sub>EABWP</sub>     | EAB Write Pulse Width                                                                        | 2.5       |     | 2.9       |     | 3.9       |      | ns          |

| t <sub>EABWCCOMB</sub> | EAB Asynchronous Write Cycle Time                                                            | 6.0       |     | 7.0       |     | 9.5       |      | ns          |

| t <sub>EABWCREG</sub>  | EAB Synchronous Write Cycle Time                                                             | 6.8       |     | 7.8       |     | 10.6      |      | ns          |

| t <sub>EABDD</sub>     | EAB Data-in to Data-out Delay                                                                |           | 5.7 |           | 6.7 |           | 9.0  | ns          |

| teabdataco             | EAB Clock-to-output Delay Using Output Registers                                             |           | 0.8 |           | 0.9 |           | 1.3  | ns          |

| t <sub>EABDATASU</sub> | EAB Data/Address Setup Time Using Input Register                                             | 1.5       |     | 1.7       |     | 2.3       |      | ns          |

| t <sub>EABDATAH</sub>  | EAB Data/Address Hold Time Using Input<br>Register                                           | 0.0       |     | 0.0       |     | 0.0       |      | ns          |

| t <sub>EABWESU</sub>   | EAB WE Setup When Using Input Register                                                       | 1.3       |     | 1.4       |     | 2.0       |      | ns          |

| t <sub>EABWESH</sub>   | EAB WE Hold Time When Using Input<br>Register                                                | 0.0       |     | 0.0       |     | 0.0       |      | ns          |

| t <sub>EABWDSU</sub>   | EAB Data Setup Time to Falling Edge of<br>Write Pulse When Not Using Input Registers         | 1.5       |     | 1.7       |     | 2.3       |      | ns          |

| t <sub>EABWDH</sub>    | EAB Data Hold Time After Falling Edge of<br>Write Pulse When Not Using Input Registers       | 0.0       |     | 0.0       |     | 0.0       |      | ns          |

| t <sub>EABWASU</sub>   | EAB Address Setup Time to Rising Edge of Write Pulse When Not Using Input Registers          | 3.0       |     | 3.6       |     | 4.8       |      | ns          |

| t <sub>EABWAH</sub>    | EAB Address Hold Time After Falling Edge<br>of Write Pulse When Not Using Input<br>Registers | 0.5       |     | 0.5       |     | 0.8       |      | ns          |

| t <sub>EABWO</sub>     | EAB WE to Data Output Delay                                                                  |           | 5.1 |           | 6.0 |           | 8.1  | ns          |

|                        |                                                                                              |           |     |           |     | !         |      | <del></del> |

10KE tbl 11A

#### External Bidirectional Timing Parameters<sup>[5]</sup>

| _                      |                                                                                 | Speed: -1 |     | Speed: -2 |     | Speed: -3 |     |      |

|------------------------|---------------------------------------------------------------------------------|-----------|-----|-----------|-----|-----------|-----|------|

| Symbol                 | Parameter                                                                       | Min       | Max | Min       | Max | Min       | Max | Unit |

| t <sub>INSUBIDIR</sub> | Setup for Bi-directional Pins with Global<br>Clock at Adjacent LE Registers     | 1.5       |     | 2.2       |     | 3.6       |     | ns   |

| t <sub>INHBIDIR</sub>  | Hold Time for Bi-directional Pins with Global Glock at Adjacent LE Registers    | 0.0       |     | 0.0       |     | 0.0       |     | ns   |

| toutcobidir            | Clock-to-output Delay for Bi-directional Pins with Global Clock at IOE Register | 2.0       | 3.5 | 2.0       | 4.5 | 2.0       | 7.1 | ns   |

| t <sub>XZBIDIR</sub>   | Synchronous IOE Output Buffer Disable<br>Delay                                  | 2.0       | 5.8 | 2.0       | 6.3 | 2.0       | 8.0 | ns   |

| t <sub>ZXBIDIR</sub>   | Synchronous IOE Output Buffer Disable<br>Delay, Slow Slew Rate = off            | 2.0       | 4.7 | 2.0       | 5.3 | 2.0       | 7.2 | ns   |

10KE tbl 12C

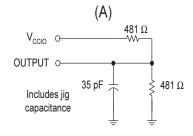

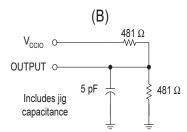

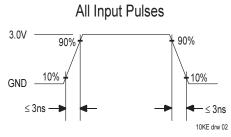

#### **AC Test Conditions**

- A: Test fixture set-up A is for general testing.

- B: Test fixture set-up B is for high Z testing  $(t_{ZX\#})$ .

#### Notes to Tables

- 1. During transitions, inputs may undershoot to -2.0V or overshoot to 5.75V for periods shorter than 20ns. Otherwise, minimum DC input voltage is -0.5V.

- 2. Device inputs may be driven before  $V_{\rm CCINT}$  and  $V_{\rm CCIO}$  are powered.

- 3. Typical values are at  $V_{\rm CC}$  of 3.3 volts and ambient temperature of 25 °C.

- 4. Guaranteed but not tested. Characterized initially, and after any design changes which may affect these parameters.

- 5. Internal timing delays are based on characterization, and cannot be explicitly tested. Internal timing parameters should be used for performance estimation only.

- 6. Use AC Test Conditions set-up B for these parameters.

#### **Revision History**

02 Dec. 2000: Created new document 22 May 2001: Corrected VCCINT table

# Ordering Information

| Part Number       | Temperature Range | Package Type        | Speed | Altera Equivalent |

|-------------------|-------------------|---------------------|-------|-------------------|

| CL10K50STC144-3   | Commercial        | 144-pin TQFP        | -3    | EPF10K50STC144-3  |

| CL10K50STC144-2   |                   |                     | -2    | EPF10K50STC144-2  |

| CL10K50STC144-2X* |                   |                     | -2    | EPF10K50STC144-2X |

| CL10K50STC144-1   |                   |                     | -1    | EPF10K50STC144-1  |

| CL10K50STC144-1X* |                   |                     | -1    | EPF10K50STC144-1X |

| CL10K50SQC208-3   | Commercial        | 208-pin Plastic QFP | -3    | EPF10K50SQC208-3  |

| CL10K50SQC208-2   |                   |                     | -2    | EPF10K50SQC208-2  |

| CL10K50SQC208-2X* |                   |                     | -2    | EPF10K50SQC208-2X |

| CL10K50SQC208-1   |                   |                     | -1    | EPF10K50SQC208-1  |

| CL10K50SQC208-1X* |                   |                     | -1    | EPF10K50SQC208-1X |

| CL10K50SQI208-2   | Industrial        |                     | -2    | EPF10K50SQI208-2  |

| CL10K50SQC240-3   | Commercial        | 240-pin Plastic QFP | -3    | EPF10K50SQC240-3  |

| CL10K50SQC240-2   |                   |                     | -2    | EPF10K50SQC240-2  |

| CL10K50SQC240-2X* |                   |                     | -2    | EPF10K50SQC240-2X |

| CL10K50SQC240-1   |                   |                     | -1    | EPF10K50SQC240-1  |

| CL10K50SQC240-1X* |                   |                     | -1    | EPF10K50SQC240-1X |

| CL10K50SFC256-4   | Commercial        | 256-pin FBGA        | -4    | EPF10K50SFC256-4  |

| CL10K50SFC256-3   |                   |                     | -3    | EPF10K50SFC256-3  |

| CL10K50SFC256-2   |                   |                     | -2    | EPF10K50SFC256-2  |

| CL10K50SFC256-2X* |                   |                     | -2    | EPF10K50SFC256-2X |

| CL10K50SFC256-1   |                   |                     | -1    | EPF10K50SFC256-1  |

| CL10K50SFC256-1X* |                   |                     | -1    | EPF10K50SFC256-1X |

10K50S tbl 02A

<sup>\*</sup> Contact your local Clear Logic Representative for availability.

# Ordering Information

| Part Number       | Temperature Range | Package Type | Speed | Altera Equivalent |

|-------------------|-------------------|--------------|-------|-------------------|

| CL10K50SBC356-3   | Commercial        | 356-pin SBGA | -3    | EPF10K50SBC356-3  |

| CL10K50SBC356-2   |                   |              | -2    | EPF10K50SBC356-2  |

| CL10K50SBC356-2X* |                   |              | -2    | EPF10K50SBC356-2X |

| CL10K50SBC356-1   |                   |              | -1    | EPF10K50SBC356-1  |

| CL10K50SBC356-1X* |                   |              | -1    | EPF10K50SBC356-1X |

| CL10K50SFC484-3   | Commercial        | 484-pin FBGA | -3    | EPF10K50SFC484-3  |

| CL10K50SFC484-2   |                   |              | -2    | EPF10K50SFC484-2  |

| CL10K50SFC484-2X* |                   |              | -2    | EPF10K50SFC484-2X |

| CL10K50SFC484-1   |                   |              | -1    | EPF10K50SFC484-1  |

| CL10K50SFC484-1X* | ]                 |              | -1    | EPF10K50SFC484-1X |

| CL10K50SFI484-2   | Industrial        |              | -2    | EPF10K50SFI484-2  |

10K50S tbl 02B

<sup>\*</sup> Contact your local Clear Logic Representative for availability.