# 7025E (8K x 16-Bit) Dual Port RAM High-Speed CMOS

12.19.01 Rev 2

#### **FEATURES:**

- 8K x 16-bit dual port RAM

- Stand Alone

- Master Slave

- Rad-Pak® radiation-hardened against natural space radiation

- · Total dose hardness:

- > 100 krad (Si), depending upon space mission

- · Excellent Single Event Effects:

- $-SEL_{TH}$  LET = >100 MeV/mg/cm<sup>2</sup>

- -SEU<sub>TH</sub> LET = 7 MeV/mg/cm<sup>2</sup>

- · Package:

- -84 Pin Rad-Pak® quad flat pack

- Separate upper byte and lower byte control for multiplexed bus compatibility

- High speed access time: 35/45 ns

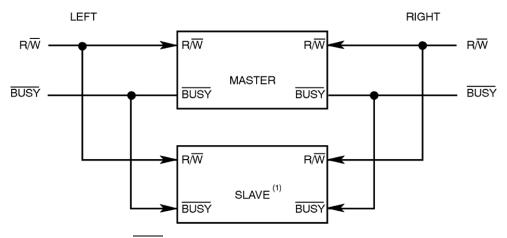

- Expandable to 32 bits or more using master/slave select when cascading

- High speed CMOS technology

- -TTL compatible, single 5V power supply

- -Interrupt flag for port-to-port communication

- -On chip port arbitration logic

- -Asynchronous operation from either port

### **DESCRIPTION:**

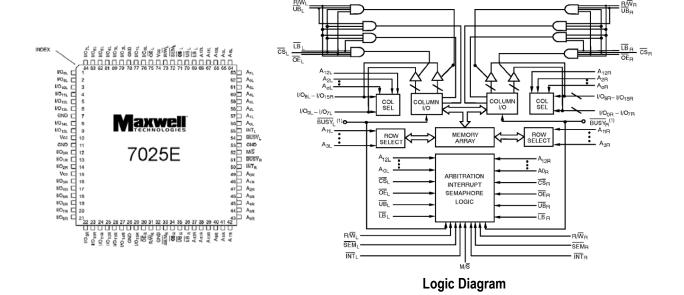

Maxwell Technologies' 7025E Dual Port RAM High Speed CMOS® microcircuit features a greater than 100 krad (Si) total dose tolerance, depending upon space mission. The 7025E is designed to be used as a stand-alone 128k-bit Dual Port RAM or as a combination MASTER/SLAVE Dual-Port RAM for 32-bit or more word systems. This design results in full-speed, error-free operation without the need for additional discrete logic. The 7025E provides two independent ports with separate control, address, and I/O pins that permit independent, asynchronous access for reads or writes to any location in memory. An automatic power down feature controlled by CS permits the on-chip circuitry of each port to enter a very low standby power mode.

Maxwell Technologies' patented Rad-Pak® packaging technology incorporates radiation shielding in the microcircuit package. It eliminates the need for box shielding while providing the required radiation shielding for a lifetime in orbit or space mission. In a GEO orbit, Rad-Pak provides greater than 100 krad (Si) radiation dose tolerance. This product is available with screening up to Class S.

TABLE 1. 7025E PINOUT DESCRIPTION

| Names             | LEFT PORT                             | RIGHT PORT                            |

|-------------------|---------------------------------------|---------------------------------------|

| Chip Select       | <u>CS</u> <sub>L</sub>                | ∇S <sub>R</sub>                       |

| Read/Write Select | R/W <sub>L</sub>                      | R/W <sub>R</sub>                      |

| Output Select     | ŌS <sub>L</sub>                       | ŌS <sub>R</sub>                       |

| Address           | AO <sub>L</sub> -A12 <sub>L</sub>     | AO <sub>R</sub> -A12 <sub>R</sub>     |

| Data Input/Output | I/OO <sub>L</sub> -I/O15 <sub>L</sub> | I/OO <sub>R</sub> -I/O15 <sub>R</sub> |

| Semaphore Select  | SEM <sub>L</sub>                      | SEM <sub>R</sub>                      |

| Upper Byte Select | UB <sub>L</sub>                       | ŪB <sub>R</sub>                       |

| Lower Byte Select | LB <sub>L</sub>                       | LB <sub>R</sub>                       |

| Interrupt Flag    | INT <sub>L</sub>                      | ĪNT <sub>R</sub>                      |

| Busy Flag         | BUSY <sub>L</sub>                     | BUSY <sub>R</sub>                     |

| M                 | /S                                    | Master or Slave Select                |

| V                 | CC                                    | Power                                 |

| Gl                | ND                                    | Ground                                |

TABLE 2. 7025E ABSOLUTE MAXIMUM RATINGS

| PARAMETER                                     | Symbol           | Min       | Max                   | Units |

|-----------------------------------------------|------------------|-----------|-----------------------|-------|

| Supply Voltage (Relative to V <sub>SS</sub> ) | V <sub>CC</sub>  | -0.3      | 7.0                   | V     |

| Operating Temperature Range                   | T <sub>A</sub>   | -55       | 125                   | °C    |

| Input or Output Voltage Applied               |                  | GND -0.3V | V <sub>CC</sub> + 0.3 | V     |

| Storage Temperature Range                     | T <sub>STG</sub> | -65       | 150                   | °C    |

TABLE 3. 7025E RECOMMENDED OPERATING CONDITIONS

| PARAMETER                   | Symbol                             | Min         | Max        | Units |

|-----------------------------|------------------------------------|-------------|------------|-------|

| Supply Voltage Positive     | V <sub>CC</sub>                    | 4.5         | 5.5        | V     |

| Input Voltage               | V <sub>IL</sub><br>V <sub>IH</sub> | -0.5<br>2.2 | 0.8<br>6.0 | V     |

| Thermal Impedance           | $\Theta_{	extsf{JC}}$              |             | 1.02       | °C/W  |

| Operating Temperature Range | T <sub>A</sub>                     | -55         | 125        | °C    |

TABLE 4. 7025E CAPACITANCE

| PARAMETER                                            | Symbol           | Min | Max | Units |

|------------------------------------------------------|------------------|-----|-----|-------|

| Input Capacitance: V <sub>IN</sub> = 0V <sup>1</sup> | C <sub>IN</sub>  |     | 5   | pF    |

| Output Capacitance: V <sub>OUT</sub> = 0V¹           | C <sub>OUT</sub> |     | 7   | pF    |

1. Guaranteed by design.

#### TABLE 5. 7025E DC ELECTRICAL CHARACTERISTICS

( $V_{\rm CC}$  = 5V  $\pm$  10%,  $T_{\rm A}$  = -55 to 125  $^{\circ}{\rm C}$  unless otherwise)

| PARAMETER                                                           | Symbol                             | Min     | Max          | Units |

|---------------------------------------------------------------------|------------------------------------|---------|--------------|-------|

| Input Leakage Current <sup>1</sup>                                  | I <sub>LI</sub>                    |         | ±10          | μΑ    |

| Output Leakage Current <sup>2</sup>                                 | I <sub>LO</sub>                    |         | ±10          | μA    |

| Standby Supply Current, Both ports TTL level inputs -35 -45         | I <sub>CCSB</sub>                  |         | 50<br>50     | mA    |

| Standby Supply Current, Both ports CMOS level inputs -35 -45        | I <sub>CCSB1</sub>                 | <br>    | 5000<br>5000 | μΑ    |

| Operating Supply Current, Both ports Active -35 -45                 | I <sub>CCOP</sub>                  |         | 320<br>280   | mA    |

| Operating Supply Current, One Port Active, One Port Standby -35 -45 | I <sub>CCOP1</sub>                 |         | 190<br>180   | mA    |

| Input Low Voltage Input High Voltage                                | V <sub>IL</sub><br>V <sub>IH</sub> | <br>2.2 | 0.8          | V     |

| Output Low Voltage <sup>3</sup> Output High Voltage                 | V <sub>OL</sub><br>V <sub>OH</sub> | <br>2.4 | 0.4<br>      | V     |

- 1. VCC = 5.5V, VIN = GND to VCC, CS = VIH, VOUT = 0 to VCC.

- 2. VIH max = VCC + 0.3V, VIL min = -0.3V or -1V pulse width 50 ns.

- 3.  $V_{CC}$  min,  $I_{OL}$  = 4 mA,  $I_{OH}$  = -4 mA.

### TABLE 6. 7025E AC ELECTRICAL CHARACTERISTICS FOR READ CYCLE

$(V_{CC} = 5V \pm 10\%, V_{SS} = 0V, T_A = -55 \text{ to } 125 \text{ °C})$

| PARAMETER               | Symbol          | Min      | Max | Unit |

|-------------------------|-----------------|----------|-----|------|

| Read Cycle Time -35 -45 | t <sub>RC</sub> | 35<br>45 | 1 1 | ns   |

Table 6. 7025E AC Electrical Characteristics for Read Cycle ( $V_{\text{CC}}$  = 5V ± 10%,  $V_{\text{SS}}$  = 0V,  $T_{\text{A}}$  = -55 to 125 °C)

| PARAMETER                                    | SYMBOL           | Mın    | Max      | Unit |

|----------------------------------------------|------------------|--------|----------|------|

| Address Access Time -35 -45                  | t <sub>AA</sub>  |        | 35<br>45 | ns   |

| Chip Select Access Time <sup>1</sup> -35 -45 | t <sub>ACS</sub> | <br>   | 35<br>45 | ns   |

| Byte Select Access Time <sup>1</sup> -35 -45 | t <sub>ABE</sub> | <br>   | 35<br>45 | ns   |

| Output Select to Output Valid -35 -45        | t <sub>AOE</sub> |        | 20<br>25 | ns   |

| Output Low Z Time <sup>2,3</sup> -35 -45     | t <sub>LZ</sub>  | 3<br>3 |          | ns   |

| Output High Z Time <sup>2,3</sup> -35 -45    | t <sub>HZ</sub>  |        | 20<br>20 | ns   |

| Chip Enable to Power Up Time <sup>2</sup>    | t <sub>PU</sub>  | 0      |          | ns   |

| Chip Disable to Power Up Time <sup>2</sup>   | t <sub>PD</sub>  |        | 50       | ns   |

| Semaphore Flag Update Pulse (OE or SEM)      | t <sub>SOP</sub> | 15     |          | ns   |

<sup>1.</sup> To access RAM,  $\overline{CS} = V_{IL}$ ,  $\overline{UB}$  or  $\overline{LB} = V_{IL}$ ,  $\overline{SEM} = V_{IH}$ . To access semaphore,  $\overline{CS} = V_{IN}$  and  $\overline{SEM} = V_{IL}$ . Either condition must be valid for the entire  $t_{EW}$  time.

TABLE 7. 7025E AC ELECTRICAL CHARACTERISTICS FOR WRITE CYCLE ( $V_{CC}$  = 5V ± 10%,  $V_{SS}$  = 0V,  $T_A$  = -55 to 125 °C)

| Parameter                     | Symbol          | Min | Max | Unit |

|-------------------------------|-----------------|-----|-----|------|

| Write Cycle Time              | t <sub>wc</sub> |     |     | ns   |

| -35                           | ****            | 35  |     |      |

| -45                           |                 | 45  |     |      |

| Address Valid to End of Write | t <sub>AW</sub> |     |     | ns   |

| -35                           |                 | 30  |     |      |

| -45                           |                 | 40  |     |      |

| Chip Select to End of Write 1 | t <sub>sw</sub> |     |     | ns   |

| -35                           |                 | 30  |     |      |

| -45                           |                 | 40  |     |      |

<sup>2.</sup> Guaranteed by design.

<sup>3.</sup> Transition is measured ± 500 mV from low or high impedance voltage with load.

# (8K x 16-Bit) Dual Port RAM High-Speed CMOS

Table 7. 7025E AC Electrical Characteristics for Write Cycle ( $V_{CC}$  = 5V ± 10%,  $V_{SS}$  = 0V,  $T_A$  = -55 to 125 °C)

| PARAMETER                                               | Symbol            | Min      | Max      | Unit |

|---------------------------------------------------------|-------------------|----------|----------|------|

| Address Setup Time -35 -45                              | t <sub>AS</sub>   | 0<br>0   | <br>     | ns   |

| Write Pulse Width -35 -45                               | t <sub>WP</sub>   | 30<br>35 |          | ns   |

| Write Recovery Time -35 -45                             | t <sub>WR</sub>   | 0        |          | ns   |

| Data Valid to End of Write -35 -45                      | t <sub>DW</sub>   | 25<br>25 |          | ns   |

| Output High Z Time <sup>2,3</sup> -35 -45               | t <sub>HZ</sub>   |          | 20<br>20 | ns   |

| Data Hold Time -35 -45                                  | t <sub>DH</sub>   | 0        |          | ns   |

| Write Select to Output in High Z <sup>2,3</sup> -35 -45 | t <sub>WZ</sub>   | <br>     | 20<br>20 | ns   |

| Output Active from End of Write 2.3.4 -35 -45           | t <sub>ow</sub>   | 0<br>0   | <br>     | ns   |

| SEM Flag Write to Read Time -35 -45                     | t <sub>SWRD</sub> | 10<br>10 |          | ns   |

| SEM Flag Contention Window<br>-35<br>-45                | t <sub>SPS</sub>  | 10<br>10 | <br>     | ns   |

<sup>1.</sup> To access RAM,  $\overline{CS} = V_{IL}$ ,  $\overline{UB}$  or  $\overline{LB} = V_{IL}$ ,  $\overline{SEM} = V_{IH}$ . To access semaphore,  $\overline{CS} = V_{IN}$  and  $\overline{SEM} = V_{IL}$ . Either condition must be valid for the entire  $t_{EW}$  time.

<sup>2.</sup> Guaranteed by design.

<sup>3.</sup> Transition is measured ± 500 mV from low or high impedance voltage with load.

<sup>4.</sup> The specification for  $t_{DH}$  must be met by the device supplying write data to the RAM under all operating conditions. Although  $t_{DH}$  and  $t_{DW}$ .

Table 8. 7025E AC Electrical Characteristics for Write Master/Slave Configuration ( $V_{CC}$  = 5V ± 10%,  $V_{SS}$  = 0V,  $T_A$  = -55 to 125 °C)

| Parameter                                                | SYMBOL           | Min    | Max      | Unit |

|----------------------------------------------------------|------------------|--------|----------|------|

| For Master Only                                          |                  |        | <u> </u> | I    |

| BUSY Access Time to Address Match<br>-35<br>-45          | t <sub>BAA</sub> | <br>   | 35<br>35 | ns   |

| BUSY Disable Time to Address Not Matched<br>-35<br>-45   | t <sub>BDA</sub> | <br>   | 30<br>30 | ns   |

| BUSY Access Time to Chip Select Low -35 -45              | t <sub>BAC</sub> |        | 30<br>30 | ns   |

| BUSY Disable Time to Chip Select High -35 -45            | t <sub>BDC</sub> |        | 25<br>25 | ns   |

| Write Pulse to Data Delay <sup>1</sup> -35 -45           | t <sub>WDD</sub> | <br>   | 60<br>70 | ns   |

| Write Data Valid to Read Data Delay <sup>1</sup> -35 -45 | t <sub>DDD</sub> |        | 45<br>55 | ns   |

| Arbitration Priority Setup Time <sup>2</sup> -35 -45     | t <sub>APS</sub> | 5<br>5 | <br>     | ns   |

| BUSY Disable to Valid Data -35 -45                       | t <sub>BDD</sub> |        | 3        | ns   |

| For Slave Only                                           |                  |        |          |      |

| Write to BUSY Input <sup>4</sup>                         | t <sub>WB</sub>  | 0      |          | ns   |

| Write Hold after BUSY <sup>5</sup>                       | t <sub>wh</sub>  | 25     |          | ns   |

| Write Pulse to Data Delay <sup>1</sup> -35 -45           | t <sub>WDD</sub> | <br>   | 60<br>70 | ns   |

| Write Data Valid to Read Data Delay <sup>1</sup> -35 -45 | t <sub>DDD</sub> | <br>   | 45<br>55 | ns   |

- 1. Port to port timing delay through RAM cells from writing port to reading port.

- 2. To ensure that the earlier of the two ports wins.

- 3.  $t_{BDD}$  is a calculated parameter and is the greater of 0,  $t_{WDD}$   $t_{WP}$  (actual) or  $t_{DDD}$   $t_{WD}$  (actual).

- 4. To ensure that the write cycle is inhibited during contention.

- 5. To ensure that a write cycle is completed after contention.

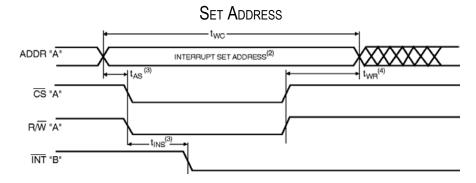

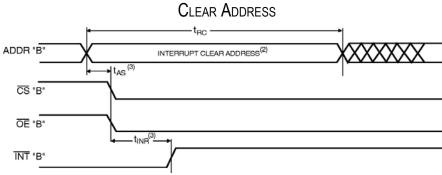

TABLE 9. 7025E AC PARAMETERS FOR INTERRUPT TIMING

( $V_{CC}$  = 5V  $\pm$  10%,  $T_A$  = -55 to 125 °C, f = 1 MHz)

| PARAMETER                    | Symbol           | Min | Max      | Units |

|------------------------------|------------------|-----|----------|-------|

| Address Setup Time           | t <sub>AS</sub>  | 0   |          | ns    |

| Write Recovery Time          | t <sub>WR</sub>  | 0   |          | ns    |

| Interrupt Set Time -35 -45   | t <sub>INS</sub> |     | 30<br>35 | ns    |

| Interrupt Reset Time -35 -45 | t <sub>INR</sub> |     | 30<br>35 | ns    |

### TABLE 10. 7025E TRUTH TABLE FOR INTERRUPT FLAG CONTROL 1

| FUNCTION                          | R/W | CS | ŌS | A <sub>0</sub> -A <sub>12</sub> | ĪNT            |

|-----------------------------------|-----|----|----|---------------------------------|----------------|

| Left Port                         |     | ı  | ı  | ı                               |                |

| Set right INT <sub>L</sub> flag   | L   | L  | Х  | 1FFF                            | Χ              |

| Reset right INT <sub>L</sub> flag | Х   | Х  | Х  | Х                               | Х              |

| Set left INT <sub>L</sub> flag    | Х   | Х  | Х  | Х                               | L 2            |

| Reset left INT <sub>L</sub> flag  | Х   | L  | L  | 1FFE                            | H <sup>3</sup> |

| Right Port                        |     |    |    |                                 |                |

| Set right INT <sub>R</sub> flag   | Х   | Х  | Х  | Х                               | L 3            |

| Reset right INT <sub>R</sub> flag | Х   | L  | L  | 1FFF                            | H <sup>2</sup> |

| Set left INT <sub>R</sub> flag    | L   | L  | Х  | 1FFE                            | Х              |

| Reset left INT <sub>R</sub> flag  | Х   | Х  | Х  | Х                               | Х              |

<sup>1.</sup> Assumes  $\overline{BUSY}_L = \overline{BUSY}_R = H$ .

<sup>2.</sup> If  $\overline{\text{BUSY}}_{\text{R}}$  = L, then no change.

<sup>3.</sup> If  $\overline{\text{BUSY}}_{L}$  = L, then no change.

TABLE 11. 7025E TRUTH TABLE FOR ARBITRATION OPTIONS

| OPTIONS           | Inputs |        |        |        | Оитритѕ |               |               |

|-------------------|--------|--------|--------|--------|---------|---------------|---------------|

|                   | CS     | ŪB     | LB     | M/S    | SEM     | BUSY          | ĪNT           |

| Busy Logic Master | L<br>L | X<br>L | L<br>X | H<br>H | H<br>H  | Output Signal |               |

| Busy Logic Slave  | L<br>L | X<br>L | L<br>X | L<br>L | H<br>H  | Input Signal  |               |

| Interrupt Logic   | L<br>L | X<br>L | L<br>X | X<br>X | H<br>H  |               | Output Signal |

| Semaphore Logic   | H<br>H | X<br>X | X<br>X | H<br>L | L<br>L  | H<br>HI-Z     |               |

TABLE 12. 7025E NON-CONTENTION READ/WRITE CONTROL

| INPUTS 1 |     |    |    |    | Оитритѕ |            | Mode      |                                      |

|----------|-----|----|----|----|---------|------------|-----------|--------------------------------------|

| CS       | R/W | ŌĒ | ŪB | LB | SEM     | I/O8-I/O15 | 1/00-1/07 |                                      |

| Н        | Х   | Х  | Х  | Х  | Н       | HI-Z       | HI-Z      | Deselected power down                |

| Х        | Х   | Х  | Н  | Н  | Н       | HI-Z       | HI-Z      | Both bytes deselected:<br>Power down |

| L        | L   | Х  | L  | Н  | Н       | DATAIN     | HI-Z      | Write to upper byte only             |

| L        | L   | Х  | Н  | L  | Н       | HI-Z       | DATAIN    | Write to lower byte only             |

| L        | L   | Х  | L  | L  | Н       | DATAIN     | DATAIN    | Write to both bytes                  |

| L        | Н   | L  | L  | Н  | Н       | DATAOUT    | HI-Z      | Read upper byte only                 |

| L        | Н   | L  | Н  | L  | Н       | HI-Z       | DATAOUT   | Read lower byte only                 |

| L        | Н   | L  | L  | L  | Н       | DATAOUT    | DATAOUT   | Read both bytes                      |

| Х        | Х   | Н  | Х  | Х  | Χ       | HI-Z       | HI-Z      | Outputs disabled                     |

<sup>1.</sup> AO<sub>L</sub> - A12<sub>L</sub> ¼ AO<sub>R</sub>-A12<sub>R</sub>.

TABLE 13. 7025E SEMAPHORE READ/WRITE CONTROL 1

| INPUTS |     |    |    |    | Оитритѕ |            | Mode      |                                 |

|--------|-----|----|----|----|---------|------------|-----------|---------------------------------|

| CS     | R/W | ŌE | UB | LB | SEM     | I/O8-I/O15 | 1/00-1/07 |                                 |

| Н      | Н   | L  | Х  | Х  | L       | DATAOUT    | DATAOUT   | Read data in semaphore flag     |

| Х      | Н   | L  | Н  | Н  | L       | DATAOUT    | DATAOUT   | Read data in semaphore flag     |

| Н      |     | Х  | Х  | Х  | L       | DATAIN     | DATAIN    | Write DinO into semaphore flagf |

| Х      |     | Х  | Н  | Н  | L       | DATAIN     | DATAIN    | Write DinO into semaphore flag  |

| L      | Х   | Х  | L  | Х  | L       |            |           | Not allowed                     |

| L      | Χ   | Χ  | Χ  | L  | L       |            |           | Not allowed                     |

<sup>1.</sup> AO<sub>L</sub> - A12<sub>L</sub> ¼ AO<sub>R</sub>-A12<sub>R</sub>.

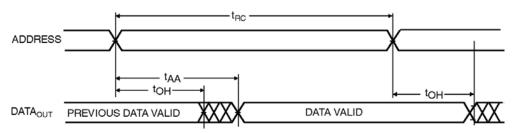

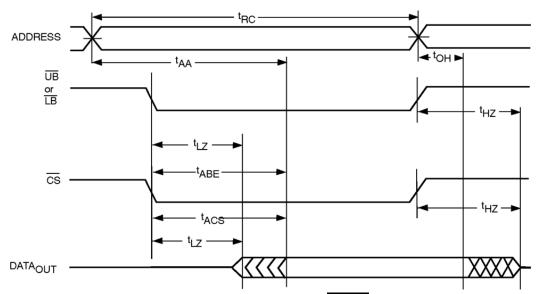

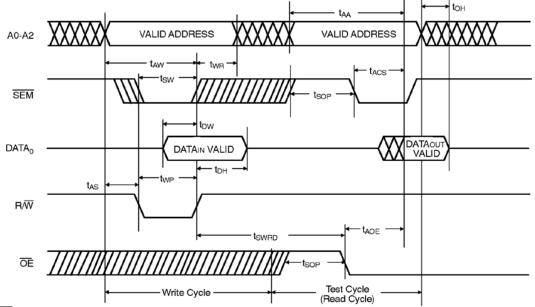

FIGURE 1. TIMING WAVEFORM OF READ CYCLE NO. 1, EITHER SIDE 1,2,3

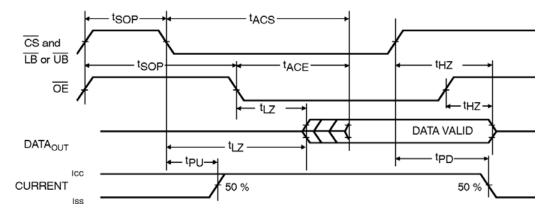

FIGURE 2. TIMING WAVEFORM OF READ CYCLE No. 2, EITHER SIDE 1,4,5

<sup>1.</sup>  $F/\overline{W}$  is high for read cycles.

<sup>2.</sup> Device is continuously enabled,  $\overline{CS} = V_{IL}$ ,  $\overline{UB}$  or  $\overline{LB} = V_{L}$ . This waveform cannot be used for semaphore reads.

<sup>3.</sup>  $\overline{CE} = V_{II}$ .

<sup>4.</sup> Addresses valid prior to or coincident with <u>CS</u> transition.

5. To access RAM, <u>CS</u> = V<sub>L</sub>, <u>UB</u> or <u>LB</u> = V<sub>IL</sub>, <u>SEM</u> = V<sub>IH</sub>. To access semaphore, <u>CS</u> = V<sub>IH</sub>, <u>SEM</u> = V<sub>IL</sub>.

FIGURE 3. TIMING WAVEFORM OF READ CYCLE No. 3, EITHER SIDE 1,3,4,5

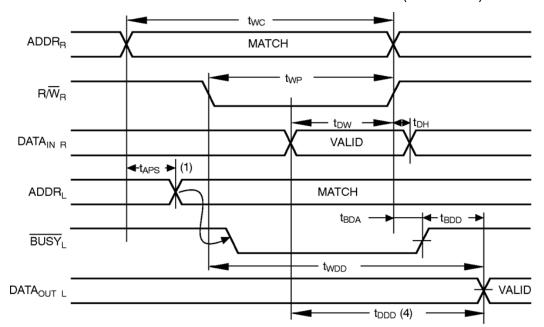

FIGURE 4. TIMING WAVEFORM OF READ WITH BUSY 2,3,4 (FOR MASTER)

- 1. To ensure math, the earlier of the two ports wins.

- 2. Write cycle parameters should be adhered to, to ensure proper writing.

- 3. Device is continuously enable for both ports.

- 4.  $\overline{OE}$  = L for the reading port.

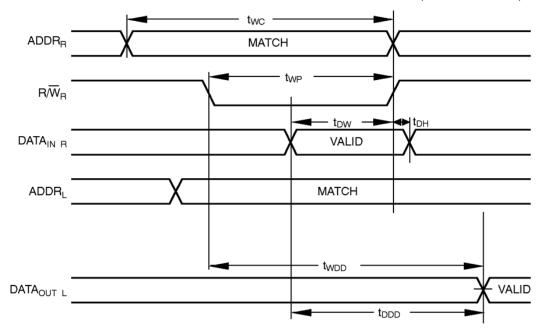

FIGURE 5. TIMING WAVEFORM OF WRITE WITH PORT-TO-PORT 1,2,3 (FOR SLAVE ONLY)

- 1. Assume  $\overline{BUSY}$  Input = H or the writing port, and  $\overline{OE}$  = L for the reading port.

- 2. Write cycle parameters should be adhered to, to ensure proper writing.

- 3. Device is continuously enable for both ports.

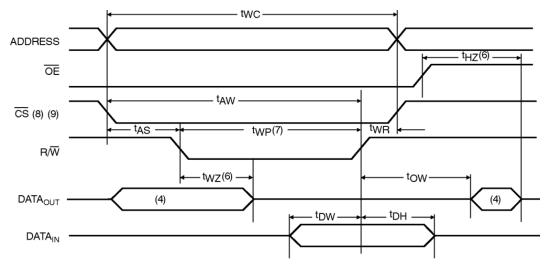

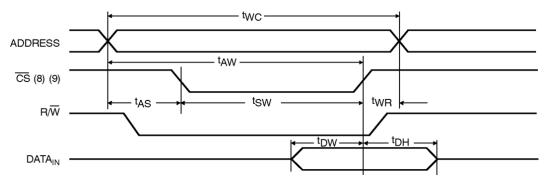

FIGURE 6. TIMING WAVEFORM OF WRITE CYCLE No. 1, R/W CONTROLLED TIMING<sup>1,2,3,7</sup>

FIGURE 7. TIMING WAVEFORM OF WRITE CYCLE No. 2, CS CONTROLLED TIMING 1,2,3,5

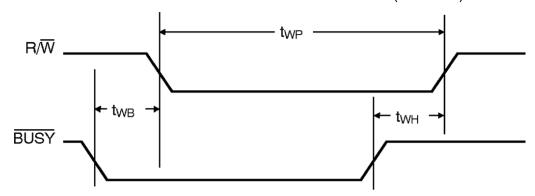

FIGURE 8. TIMING WAVEFORM OF WRITE WITH BUSY (FOR SLAVE)

<sup>1.</sup> R/W must be high during all address transitions.

<sup>2.</sup> A write occurs during the overlap ( $t_{SW}$  to  $t_{WF}$ ) of a low  $\overline{CS}$  or  $\overline{SEM}$  and a low  $R/\overline{W}$ .

<sup>3.</sup>  $T_{WF}$  is measured from the earlier of  $\overline{CS}$  or  $R/\overline{W}$  (or  $\overline{SEM}$  or  $R/\overline{W}$ ) going high to the end of write cycle.

<sup>4.</sup> During this period, the I/O pins are in the output state, and input signals must not be applied.

<sup>5.</sup> If the  $\overline{\text{CS}}$  or  $\overline{\text{SEM}}$  low transition occurs simultaneously with or after the R/W low transition, the outputs remain in the high impedance state.

Transitions measured = 500 mV from steady state with a 5 pF load (including scope and jig). This parameter is sample and not 100% tested.

<sup>7.</sup> If  $\overline{OE}$  is low during a R/W controlled write cycle, the write pulse width must be the larger of two or  $(t_{WZ} + t_{DW})$  to allow the I/O driver to turn off and data to be placed on the bus for the required  $t_{DW}$ . If  $\overline{OE}$  is high during an R/W controlled write cycle, this requirement does not apply and the write pulse can be as short as the specified  $t_{WP}$ .

<sup>8.</sup> To access RAM,  $\overline{\text{CS}} = V_{\text{IL}}$ ,  $\overline{\text{SEM}} = V_{\text{IH}}$ .

<sup>9.</sup> To access upper byte,  $\overline{CS} = V_{IL}$ ,  $\overline{UB} = V_{IL}$ ,  $\overline{SEM} = V_{IH}$ . To access lower byte,  $\overline{CS} = V_{II}$ ,  $\overline{LB} = V_{II}$ ,  $\overline{SEM} = V_{IH}$ .

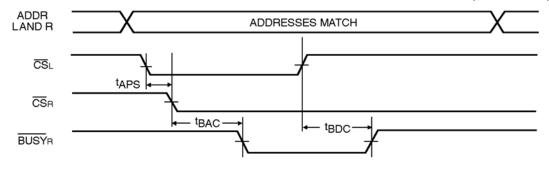

FIGURE 9. TIMING WAVEFORM OF CONTENTION CYCLE NO. 1, CS ARBITRATION (FOR MASTER)

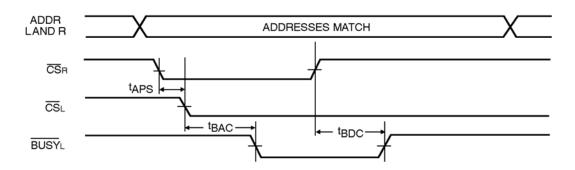

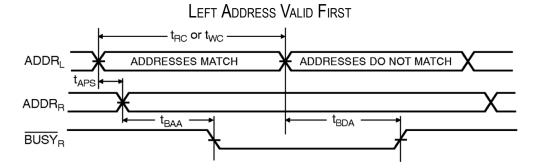

FIGURE 10. TIMING WAVEFORM OF CONTENTION CYCLE No. 2, ADDRESS VALID ARBITRATION (FOR MASTER ONLY) 1

## RIGHT ADDRESS VALID FIRST t<sub>RC</sub> or t<sub>WC</sub> ADDRESSES MATCH ADDRESSES DO NOT MATCH $t_{BAA}$ $t_{BDA}$

1.  $\overline{CS}_L = CS_R = V_{IL}$ .

ADDR

**ADDR**

BUSY

FIGURE 11. WAVEFORM OF INTERRUPT TIMING 1

- 1. All timing is the same for left and right ports. Port "A" may be either the left or right port. Port "B" is the port opposite from "A".

- 2. See interrupt truth table.

1000586

- 3. Timing depends on which enable signal is asserted last.

- 4. Timing depends on which enable signal is de-asserted first.

All data sheets are subject to change without notice

FIGURE 12. 32-BIT MASTER/SLAVE DUAL-PORT MEMORY SYSTEMS

1. No arbitration in Master/Slave. BUSY - IN inhibits write in Master/Slave.

FIGURE 13. TIMING WAVEFORM OF SEMAPHORE READ AFTER WRITE TIMING, EITHER SIDE <sup>1</sup>

1.  $\overline{\text{CS}} = V_{\text{IH}}$  for the duration of the above timing (both write and read cycle).

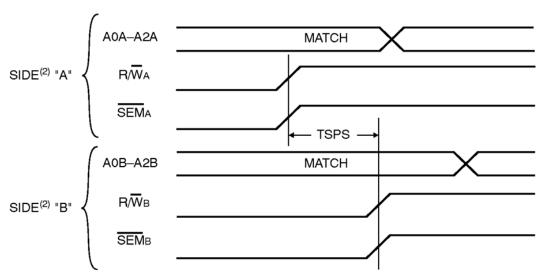

FIGURE 14. TIMING WAVEFORM OF SEMAPHORE CONTENTION 1,3,4

- 1.  $D_{OR} = D_{OL} = V_{IL}$ ,  $\overline{CS}_R = \overline{CS}_L = V_{IH}$ , semaphore Flag is released from both sides (reads as ones from both sides) at cycle start.

- 2. Either side "A" = left and side "B" = right, or side "A" = right and side "B" = left.

- 3. This parameter is measured from the point where  $R/\overline{W}_A$  or  $\overline{SEM}_A$  goes high until  $R/\overline{W}_B$  or  $\overline{SEM}_B$  goes high.

- 4. If t<sub>SPS</sub> is violated, the semaphore will fall positively to one side or the other, but there is no guaranty which side will obtain the flag.

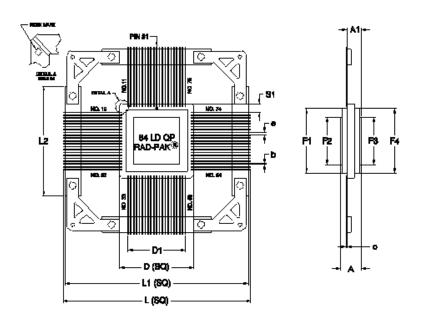

84 PIN RAD-PAK® FLAT PACKAGE

| SYMBOL | DIMENSION |       |       |  |  |  |  |

|--------|-----------|-------|-------|--|--|--|--|

|        | Min       | Nом   | Max   |  |  |  |  |

| A      | 0.163     | 0.176 | 0.189 |  |  |  |  |

| A1     | 0.113     | 0.123 | 0.133 |  |  |  |  |

| b      | 0.006     | 0.010 | 0.014 |  |  |  |  |

| С      | 0.004     | 0.006 | 0.010 |  |  |  |  |

| D      | 0.635     | 0.650 | 0.665 |  |  |  |  |

| D1     | 0.500 BSC |       |       |  |  |  |  |

| е      | 0.025 BSC |       |       |  |  |  |  |

| S1     | 0.005     | 0.070 |       |  |  |  |  |

| F1     | 0.540     | 0.545 | 0.550 |  |  |  |  |

| F2     | 0.415     | 0.420 | 0.425 |  |  |  |  |

| F3     | 0.412     | 0.415 | 0.418 |  |  |  |  |

| F4     | 0.560     | 0.565 | 0.570 |  |  |  |  |

| L      |           | 1.620 | 1.635 |  |  |  |  |

| L1     | 1.595     | 1.600 | 1.615 |  |  |  |  |

| L2     | 0.940     | 0.950 | 0.960 |  |  |  |  |

| N      | 84        |       |       |  |  |  |  |

Q84-01 Note: All dimensions in inches

All data sheets are subject to change without notice

7025E

## (8K x 16-Bit) Dual Port RAM High-Speed CMOS

Important Notice:

1000586

These data sheets are created using the chip manufacturers published specifications. Maxwell Technologies verifies functionality by testing key parameters either by 100% testing, sample testing or characterization.

The specifications presented within these data sheets represent the latest and most accurate information available to date. However, these specifications are subject to change without notice and Maxwell Technologies assumes no responsibility for the use of this information.

Maxwell Technologies' products are not authorized for use as critical components in life support devices or systems without express written approval from Maxwell Technologies.

Any claim against Maxwell Technologies must be made within 90 days from the date of shipment from Maxwell Technologies. Maxwell Technologies' liability shall be limited to replacement of defective parts.

All data sheets are subject to change without notice

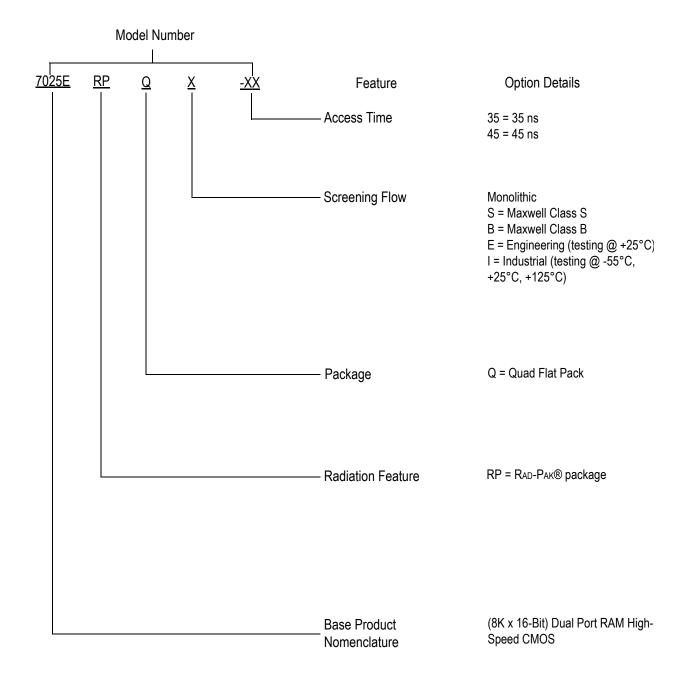

### **Product Ordering Options**