Vishay Siliconix

### 15 A microBUCK<sup>®</sup> SiC401A/B Integrated Buck Regulator with Programmable LDO

### DESCRIPTION

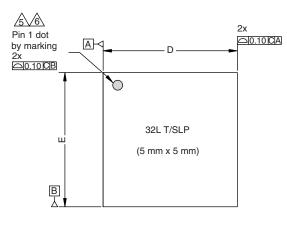

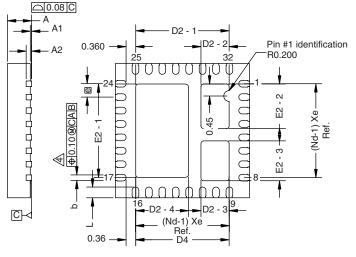

The Vishay Siliconix SiC401A/B an adv anced stand-alone synchronous b uck re gulator f eaturing i ntegrated power MOSFETs, bootstrap switch, and a programmable LDO in a space-saving PowerPAK MLP55-32L pin packages.

The SiC40 1A/B is capa ble of ope rating with all cer amic solutions an d s witching frequ encies up to 1 MHz. The programmable frequ ency, synch ronous op eration and selectable p ower-save all ow ope ration at h igh e fficiency across the full range of load current. The internal LDO may be used to supply 5 V for the gate drive circuits or it may be bypassed with an external 5 V for op timum efficiency and used to drive external n-channel MOSFETs or o ther loads. Additional f eatures include cycle-b y-cycle current limit,

voltage soft-star t, unde r-voltage protection, pro grammable over-current protection, soft shu tdown an d sel ectable power-save. The Visha y Siliconix SiC401A/B also provides an enable input and a power good output.

| PRODUCT SUMMARY           |                    |  |  |  |  |  |

|---------------------------|--------------------|--|--|--|--|--|

| Input Voltage Range       | 3 V to 17 V        |  |  |  |  |  |

| Output Voltage Range      | 0.6 V to 5.5 V     |  |  |  |  |  |

| Operating Frequency       | 200 kHz to 1 MHz   |  |  |  |  |  |

| Continuous Output Current | 15 A               |  |  |  |  |  |

| Peak Efficiency           | 93 %               |  |  |  |  |  |

| Package                   | PowerPAK MLP55-32L |  |  |  |  |  |

#### FEATURES

- High efficiency > 93 %

- 15 A continuous output current capability

- Integrated bootstrap switch

- Programmable 200 mA LDO with bypass logic

- Temperature compensated current limit

- All ceramic solution enabled

- Pseudo fixed-frequency adaptive on-time control

- Programmable input UVLO threshold

- Independent enable pin for switcher and LDO

- Selectable ultra-sonic power-save mode (SiC401A)

- Selectable power-save mode (SiC401B)

- Programmable soft-start and soft-shutdown

- 1 % internal reference voltage

- Power good output

- · Over-voltage and under-voltage protections

- Material catego rization: Fo r d efinitions of comp liance please see <u>www.vishay.com/doc?99912</u>

#### APPLICATIONS

- Notebook, desktop and server computers

- Digital HDTV and digital consumer applications

- Networking and telecommunication equipment

- Printers, DSL, and STB applications

- Embedded applications

- Point of load power supplies

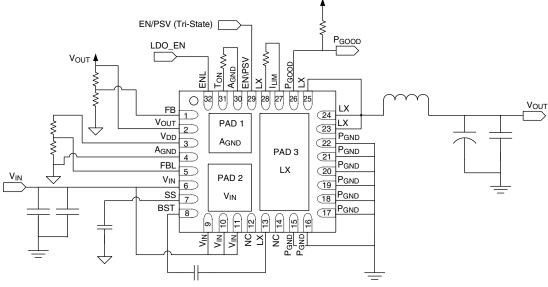

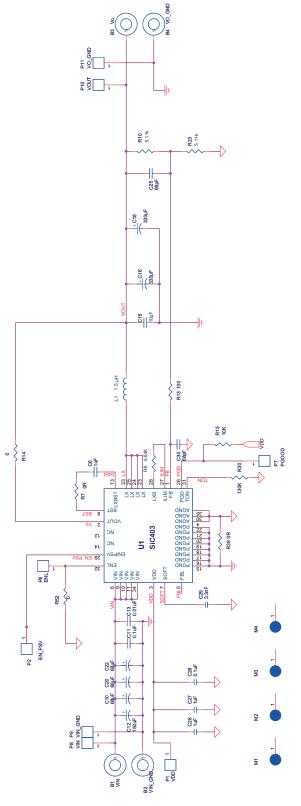

### TYPICAL APPLICATION CIRCUIT AND PACKAGE OPTIONS

Typical Application Circuit for SiC401A/B (PowerPAK MLP5x5-32L)

COMPLIANT

Vishay Siliconix

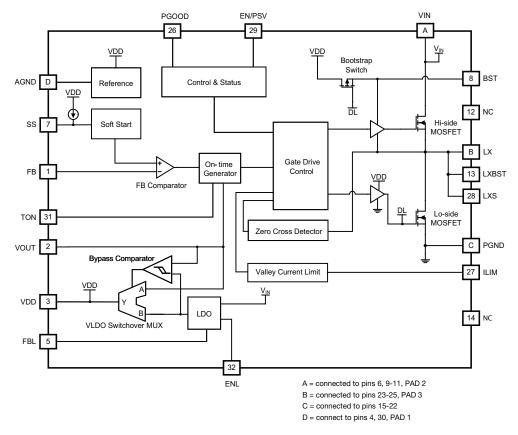

### FUNCTIONAL BLOCK DIAGRAM

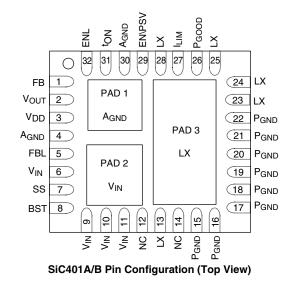

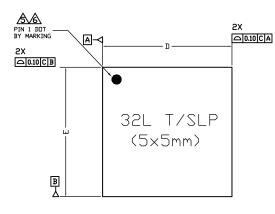

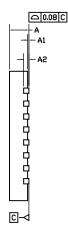

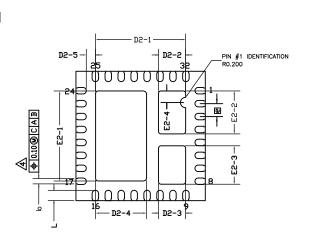

#### **PIN CONFIGURATION**

Document Number: 63835 S12-2109-Rev. C, 03-Sep-12

# VISHAY

### Vishay Siliconix

| Pin Number        | Symbol            | Description                                                                                                                                                                                                                                 |

|-------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                 | FB                | Feedback input for switching regulator used to program the output voltage - connect to an externa resistor divider from V <sub>OUT</sub> to A <sub>GND</sub> .                                                                              |

| 2V                | OUT               | Switcher output voltage sense pin - also the input to the inter nal switch-over between $V_{OUT}$ and $V_{LDO}$ . The voltage at this pin must be less than or equal to the voltage at the $V_{DD}$ pin.                                    |

| ЗV                | DD                | Bias supply for the IC - when using the internal LDO as a bias power supply, $V_{DD}$ is the LDO output When using an external power supply as the bias for the IC, the LDO output should be disabled.                                      |

| 4, 30, PAD 1      | A <sub>GND</sub>  | Analog ground                                                                                                                                                                                                                               |

| 5F                | BL                | Feedback input for the internal LDO - used to program the LDO output. Connect to an externa resistor divider from V <sub>DD</sub> to A <sub>GND</sub> .                                                                                     |

| 6, 9 to 11, PAD 2 | V <sub>IN</sub>   | Input supply voltage                                                                                                                                                                                                                        |

| 7                 | SS                | The soft start ramp will be programmed by an internal current source charging a capacitor on this pin                                                                                                                                       |

| 8B                | ST                | Bootstrap pin - connect a capacitor of at least 100 nF from BST to LX to develop the floating supply for the high-side gate drive.                                                                                                          |

| 12, 14            | NC                | No connection                                                                                                                                                                                                                               |

| 13                | LXBST             | LX Boost - connect to the BST capacitor.                                                                                                                                                                                                    |

| 23 to 25, PAD3    | LX                | Switching (phase) node                                                                                                                                                                                                                      |

| 15 to 22          | P <sub>GND</sub>  | Power ground                                                                                                                                                                                                                                |

| 26                | P <sub>GOOD</sub> | Open-drain power good in dicator - high impedan ce in dicates power is goo d. An external pull-up resistor is required.                                                                                                                     |

| 27                | I <sub>LIM</sub>  | Current limit sense pin - used to program the current limit by connecting a resistor from ILIM to LXS                                                                                                                                       |

| 28                | LXS               | LX sense - connects to R <sub>ILIM</sub>                                                                                                                                                                                                    |

| 29                | EN/PSV            | Enable/power save input for the s witching regulator - connect to $A_{GND}$ to disab le the s witching regulator, connect to $V_{DD}$ to operate with power-save mode and float to operate in forced continuous mode.                       |

| 31                | t <sub>ON</sub>   | On-time programming input - set the on-time by connecting through a resistor to $A_{GND}$                                                                                                                                                   |

| 32                | ENL               | Enable input for the LDO - connect ENL to A <sub>GND</sub> to disable the LDO. Drive with logic signal for logic control, or program the V <sub>IN</sub> UVLO with a resistor divider between V <sub>IN</sub> , ENL, and A <sub>GND</sub> . |

| ORDERING INFORMATION |                    |                       |  |  |  |  |

|----------------------|--------------------|-----------------------|--|--|--|--|

| Part Number          | Package            | Marking (Line 1: P/N) |  |  |  |  |

| SiC401ACD-T1-GE3     | PowerPAK MLP55-32L | SiC401A               |  |  |  |  |

| SiC401BCD-T1-GE3     | PowerPAK MLP55-32L | SiC401B               |  |  |  |  |

| SiC401DB             | Reference          | ce board              |  |  |  |  |

Format:

LINE 1: P/N LINE 2: Siliconix logo + Lot code + ESD symbol LINE 3: Factory code + Year code + Work week code

Vishay Siliconix

| Electrical Parameter                                                      | Conditions                    | Limits                             | Unit |

|---------------------------------------------------------------------------|-------------------------------|------------------------------------|------|

| V <sub>IN</sub>                                                           | to P <sub>GND</sub>           | - 0.3 to + 20                      |      |

| V <sub>IN</sub>                                                           | to V <sub>DD</sub>            | - 0.4 max.                         |      |

| LX                                                                        | to P <sub>GND</sub>           | - 0.3 to + 20                      |      |

| LX (Transient < 100 ns)                                                   | to P <sub>GND</sub>           | - 2 to + 20                        |      |

| V <sub>DD</sub>                                                           | to P <sub>GND</sub>           | - 0.3 to + 6                       |      |

| EN/PSV, P <sub>GOOD</sub> , I <sub>LIM</sub>                              | Reference to P <sub>GND</sub> | - 0.3 to + (V <sub>DD</sub> + 0.3) | V    |

| t <sub>ON</sub>                                                           | to P <sub>GND</sub>           | - 0.3 to + (V <sub>DD</sub> - 1.5) |      |

| BST                                                                       | to LX                         | - 0.3 to + 6                       |      |

|                                                                           | to P <sub>GND</sub>           | - 0.3 to + 25                      | 7    |

| ENL                                                                       |                               | - 0.3 to V <sub>IN</sub>           |      |

| A <sub>GND</sub> to P <sub>GND</sub>                                      |                               | - 0.3 to + 0.3                     |      |

| Temperature                                                               |                               |                                    | •    |

| Maximum Junction Temperature                                              |                               | 150                                |      |

| Storage Temperature                                                       |                               | - 65 to 150                        |      |

| Power Dissipation                                                         |                               |                                    |      |

| Junction to Ambient Thermal Impedance (R <sub>thJA</sub> ) <sup>(b)</sup> | IC Section                    | 50                                 | °C/W |

| Maximum Dawar Dissinction                                                 | Ambient Temperature = 25 °C   | 3.4                                | w    |

| Maximum Power Dissipation                                                 | Ambient Temperature = 100 °C  | 1.3                                | vv   |

| ESD Protection                                                            |                               |                                    |      |

|                                                                           | НВМ                           | 2                                  | kV   |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating/conditions for extended periods may affect device reliability.

| <b>RECOMMENDED OPERATING CONDITIONS</b> (all voltages referenced to GND = 0 V) |                  |           |      |      |      |  |

|--------------------------------------------------------------------------------|------------------|-----------|------|------|------|--|

| Parameter Symb                                                                 | ol               | Min.      | Тур. | Max. | Unit |  |

| Input Voltage                                                                  | V <sub>IN</sub>  | 3         |      | 17   |      |  |

| V <sub>DD</sub> to P <sub>GND</sub>                                            |                  | 3         |      | 5.5  | V    |  |

| Output Voltage                                                                 | V <sub>OUT</sub> | 0.6       |      | 5.5  |      |  |

| Temperature                                                                    |                  |           |      |      |      |  |

| Ambient Temperature                                                            |                  | - 40 to 8 | 35   |      | °C   |  |

# SiC401A, SiC401BCD Vishay Siliconix

|                                                 | 1                                                    | Test Conditions Unless Specified                                                                                                                                                       |       |              |       | 1       |

|-------------------------------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------|-------|---------|

| Parameter S                                     | ymbol                                                | $V_{IN} = 12 \text{ V}, V_{DD} = 5 \text{ V}, T_A = +25 \text{ °C for typ.}, -40 \text{ °C to } +85 \text{ °C for min. and max.}, T_J = < 125 \text{ °C, typical application circuit}$ | Min.  | Тур.         | Max.  | Uni     |

| Input Power Supplies                            | •                                                    |                                                                                                                                                                                        |       | •            | •     |         |

| Input Supply Voltage                            | V <sub>IN</sub>                                      |                                                                                                                                                                                        | 3     |              | 17    |         |

| V <sub>DD</sub>                                 | V <sub>DD</sub>                                      |                                                                                                                                                                                        | 3     |              | 5.5   |         |

|                                                 | N                                                    | Sensed at ENL pin, rising                                                                                                                                                              | 2.4   | 2.6          | 2.95  |         |

| V <sub>IN</sub> UVLO Threshold <sup>(a)</sup>   | V <sub>UVLO</sub>                                    | Sensed at ENL pin, falling                                                                                                                                                             | 2.23  | 2.4          | 2.57  |         |

| V <sub>IN</sub> UVLO Hysteresis                 | V <sub>UVLO, HYS</sub>                               |                                                                                                                                                                                        |       | 0.25         |       | V       |

|                                                 |                                                      | Measured at V <sub>DD</sub> pin, rising                                                                                                                                                | 2.5   |              | 3     | 1       |

| V <sub>DD</sub> UVLO Threshold                  | V <sub>UVLO</sub>                                    | Measured at V <sub>DD</sub> pin, falling                                                                                                                                               | 2.4   |              | 2.9   |         |

| V <sub>DD</sub> UVLO Hysteresis                 | V <sub>UVLO, HYS</sub>                               |                                                                                                                                                                                        |       | 0.2          |       |         |

| V. Oursels Ourset                               |                                                      | ENL, EN/PSV = 0 V , V <sub>IN</sub> = 17 V                                                                                                                                             |       | 10           | 20    |         |

| V <sub>IN</sub> Supply Current                  | I <sub>IN</sub>                                      | Standby mode; ENL= V <sub>DD</sub> , EN/PSV = 0 V                                                                                                                                      |       | 130          |       | μA      |

|                                                 | I <sub>DD</sub>                                      | ENL, EN/PSV = 0 V                                                                                                                                                                      |       | 190          | 300   |         |

|                                                 |                                                      | SiC401A, EN/PSV = $V_{DD}$ , no load<br>(f <sub>SW</sub> = 25 kHz), $V_{FB} > 0.6 V$ <sup>(b)</sup>                                                                                    |       | 0.3          |       |         |

| V <sub>DD</sub> Supply Current                  |                                                      | SiC401B, EN/PSV = $V_{DD}$ , no load,<br>$V_{FB} > 0.6 V^{(b)}$                                                                                                                        |       | 0.7          |       |         |

|                                                 |                                                      | $V_{DD} = 5 \text{ V}, f_{SW} = 250 \text{ kHz},$<br>EN/PSV = floating, no load <sup>(b)</sup>                                                                                         |       | 9            |       | mA      |

|                                                 |                                                      | $V_{DD}$ = 3 V, f <sub>SW</sub> = 250 kHz,<br>EN/PSV = floating, no load <sup>(b)</sup>                                                                                                |       | 5.5          |       |         |

| FB On-Time Threshold                            |                                                      | Static V <sub>IN</sub> and load                                                                                                                                                        | 0.594 | 0.600        | 0.606 | V       |

| Framer Danas                                    | f <sub>SW</sub>                                      | Continuous mode operation                                                                                                                                                              |       |              | 1000  |         |

| Frequency Range                                 | _                                                    | Minimum f <sub>SW</sub> , (SiC401A only)                                                                                                                                               |       | 25           |       | kHz     |

| Bootstrap Switch Resistance                     |                                                      |                                                                                                                                                                                        |       | 10           |       | Ω       |

| Timing                                          |                                                      |                                                                                                                                                                                        |       |              |       |         |

| On-Time                                         | t <sub>ON</sub>                                      | Continuous mode operation V <sub>IN</sub> = 12 V, V <sub>OUT</sub> = 5 V, f <sub>SW</sub> = 300 kHz, R <sub>ton</sub> = 133 k $\Omega$                                                 | 999   | 1110         | 1220  |         |

| Minimum On-Time <sup>(b)</sup>                  | t <sub>ON, min.</sub>                                |                                                                                                                                                                                        |       | 80           |       | ns      |

| Minimum Off-Time <sup>(b)</sup>                 | torr                                                 | $V_{DD} = 5 V$                                                                                                                                                                         |       | 250          |       |         |

|                                                 | <sup>t</sup> OFF, min.                               | $V_{DD} = 3 V$                                                                                                                                                                         |       | 370          |       |         |

| Soft Start                                      |                                                      |                                                                                                                                                                                        |       |              |       |         |

| Soft Start Current (b)                          | I <sub>SS</sub>                                      |                                                                                                                                                                                        |       | 3μ           |       | A       |

| Soft Start Voltage <sup>(b)</sup>               | V <sub>SS</sub>                                      | When V <sub>OUT</sub> reaches regulation                                                                                                                                               |       | 1.5          |       | V       |

| Analog Inputs/Outputs                           |                                                      |                                                                                                                                                                                        |       | 1            | 1     |         |

| V <sub>OUT</sub> Input Resistance               | R <sub>O-IN</sub>                                    |                                                                                                                                                                                        |       | 500          |       | kΩ      |

| Current Sense                                   |                                                      |                                                                                                                                                                                        |       | 1            | 1     |         |

| Zero-Crossing Detector Threshold Voltage        | V <sub>Sense-th</sub>                                | LX-P <sub>GND</sub>                                                                                                                                                                    | - 3   |              | + 3   | mV      |

| Power Good                                      | 1                                                    |                                                                                                                                                                                        |       |              | 1     |         |

| Power Good Threshold                            | PG_V <sub>TH_UPPER</sub><br>PG_V <sub>TH_LOWER</sub> | Upper limit, V <sub>FB</sub> > internal 600 mV reference<br>Lower limit, V <sub>FB</sub> < internal 600 mV reference                                                                   |       | ± 20<br>- 10 |       | %       |

| Start-Up Delay Time                             |                                                      | V <sub>DD</sub> = 5 V, C <sub>SS</sub> = 10 nF                                                                                                                                         |       | 12           |       | † – – † |

| (between PWM enable and P <sub>GOOD</sub> high) | PG_T <sub>d</sub>                                    | $V_{DD} = 3 V, C_{SS} = 10 nF$                                                                                                                                                         |       | 7            |       | ms      |

| Fault (noise-immunity) Delay Time (b)           | PG_I <sub>CC</sub>                                   |                                                                                                                                                                                        |       | 5μ           |       | s       |

| Leakage Current                                 | PG_I <sub>LK</sub>                                   |                                                                                                                                                                                        |       |              | 1μ    | A       |

| Power Good On-Resistance                        | PG_R <sub>DS_ON</sub>                                |                                                                                                                                                                                        |       | 10           |       | Ω       |

| Fault Protection                                | 0011                                                 | L                                                                                                                                                                                      |       | !            | !     |         |

| Valley Current Limit                            | I <sub>LIM</sub>                                     | $V_{DD} = 5 V$ , $R_{ILIM} = 3945$ , $T_J = 0 \degree C$ to +125 $\degree C$<br>$V_{DD} = 3.3 V$ , $R_{ILIM} = 3945$                                                                   | 12.75 | 15<br>13.5   | 17.25 | A       |

| -                                               |                                                      |                                                                                                                                                                                        |       |              |       |         |

Document Number: 63835 S12-2109-Rev. C, 03-Sep-12 For technical questions, contact: powerictechsupport@vishay.com

www.vishay.com

<sup>5</sup>

### **Vishay Siliconix**

| Parameter Symbol                                                              |                        | $\label{eq:VIN} \begin{array}{l} \textbf{Test Conditions Unless Specified} \\ V_{IN} = 12 \text{ V}, V_{DD} = 5 \text{ V}, T_A = +25 \ ^\circ\text{C} \text{ for typ.}, \\ -40 \ ^\circ\text{C} \text{ to } +85 \ ^\circ\text{C} \text{ for min. and max.}, \\ T_J = < 125 \ ^\circ\text{C}, \text{ typical application circuit} \end{array}$ | Min.  | Тур. | Max.  | Unit |

|-------------------------------------------------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------|

| ILIM Comparator Offset Voltage                                                | V <sub>ILM-LK</sub>    | With respect to A <sub>GND</sub>                                                                                                                                                                                                                                                                                                              | - 10  | 0    | + 10  | mV   |

| Output Under-Voltage Fault                                                    | V <sub>OUV_Fault</sub> | V <sub>FB</sub> with respect to Internal 600 mV reference, 8 consecutive clocks                                                                                                                                                                                                                                                               |       | - 25 |       |      |

| Smart Power-Save Protection<br>Threshold Voltage <sup>b</sup>                 | P <sub>Save_VTH</sub>  | $V_{\mbox{\scriptsize FB}}$ with respect to internal 600 mV                                                                                                                                                                                                                                                                                   |       | + 10 |       | %    |

| Over-Voltage Protection Threshold                                             |                        | V <sub>FB</sub> with respect to internal 600 mV                                                                                                                                                                                                                                                                                               |       | + 20 |       |      |

| Over-Voltage Fault Delay <sup>b</sup>                                         | t <sub>OV-Delay</sub>  |                                                                                                                                                                                                                                                                                                                                               |       | 5μ   |       | s    |

| Over Temperature Shutdown <sup>b</sup>                                        | T <sub>Shut</sub>      | 10 °C hysteresis                                                                                                                                                                                                                                                                                                                              |       | 150  |       | °C   |

| Logic Inputs/Outputs                                                          |                        |                                                                                                                                                                                                                                                                                                                                               |       |      | •     |      |

| Logic Input High Voltage                                                      | V <sub>IH</sub>        |                                                                                                                                                                                                                                                                                                                                               | 1     |      |       |      |

| Logic Input Low Volatge                                                       | V <sub>IL</sub>        |                                                                                                                                                                                                                                                                                                                                               |       |      | 0.4   |      |

| EN/PSV Input for P-Save Operation (b)                                         |                        | $V_{DD} = 5 V$                                                                                                                                                                                                                                                                                                                                | 2.2   |      | 5     | v    |

| EN/PSV Input for Forced Continuous<br>Operation <sup>(b)</sup>                |                        |                                                                                                                                                                                                                                                                                                                                               | 12    |      |       |      |

| EN/PSV Input for Disabling Switcher                                           |                        |                                                                                                                                                                                                                                                                                                                                               | 00    |      | .4    |      |

| EN/PSV Input Bias Current                                                     | I <sub>EN</sub>        |                                                                                                                                                                                                                                                                                                                                               | - 10  |      | + 10  |      |

| ENL Input Bias Current                                                        | I <sub>ENL</sub>       |                                                                                                                                                                                                                                                                                                                                               |       | 81   | 5     | μA   |

| FBL, FB Input Bias Current                                                    | FBL_I <sub>LK</sub>    |                                                                                                                                                                                                                                                                                                                                               | - 1   |      | + 1   |      |

| Linear Dropout Regulator                                                      |                        |                                                                                                                                                                                                                                                                                                                                               |       |      | •     |      |

| FBL <sup>(b)</sup>                                                            | V <sub>LDO ACC</sub>   |                                                                                                                                                                                                                                                                                                                                               |       | 0.75 |       | V    |

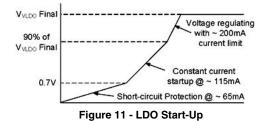

|                                                                               |                        | Short-circuit protection,<br>V <sub>IN</sub> = 12 V, V <sub>DD</sub> < 0.75 V                                                                                                                                                                                                                                                                 |       | 65   |       |      |

| LDO Current Limit                                                             | LDO_I <sub>LIM</sub>   | Start-up and foldback, $V_{IN}$ = 12 V,<br>0.75 < $V_{DD}$ < 90 % of final $V_{DD}$ value                                                                                                                                                                                                                                                     |       | 115  |       | mA   |

|                                                                               |                        | Operating current limit, $V_{IN} = 12 V$ ,<br>$V_{DD} > 90 \%$ of final $V_{DD}$ value                                                                                                                                                                                                                                                        | 135   | 200  |       |      |

| $V_{LDO}$ to $V_{OUT}$ Switch-over Threshold <sup>(d)</sup>                   | V <sub>LDO-BPS</sub>   |                                                                                                                                                                                                                                                                                                                                               | - 130 |      | + 130 |      |

| V <sub>LDO</sub> to V <sub>OUT</sub> Non-switch-over Threshold <sup>(d)</sup> | V <sub>LDO-NBPS</sub>  |                                                                                                                                                                                                                                                                                                                                               | - 500 |      | + 500 | mV   |

| V <sub>LDO</sub> to V <sub>OUT</sub> Switch-over Resistance                   | R <sub>LDO</sub>       | V <sub>OUT</sub> = 5 V                                                                                                                                                                                                                                                                                                                        |       | 2    |       | Ω    |

| LDO Drop Out Voltage <sup>(e)</sup>                                           |                        | From $V_{IN}$ to $V_{DD}$ ,<br>$V_{DD} = +5 V$ , $I_{VLDO} = 100 mA$                                                                                                                                                                                                                                                                          |       | 1.2  |       | v    |

Notes:

a. VIN UVLO is programmable using a resistor divider from VIN to ENL to AGND. The ENL voltage is compared to an internal reference.

b. Typical value measured on standard evaluation board.

c. SiC401A/B has first order temperature compensation for over current. Results vary based upon the PCB thermal layout

d. The switch-over threshold is the maximum voltage dif f erential b etween the V  $_{LDO}$  and V  $_{OUT}$  pins which ensures that V  $_{LDO}$  will internally switch-over to V $_{OUT}$ . The non-switch-over threshold is the minimum voltage diff erential between the V $_{LDO}$  and V $_{OUT}$  pins which ensures that V  $_{LDO}$  will not switch-over to V $_{OUT}$ .

e. The LDO drop out voltage is the voltage at which the LDO output drops 2 % below the nominal regulation point.

Vishay Siliconix

#### **ELECTRICAL CHARACTERISTICS**

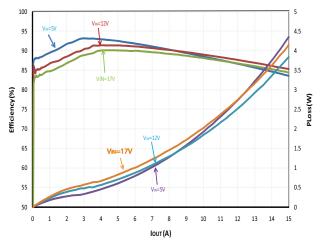

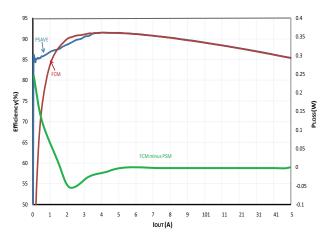

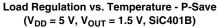

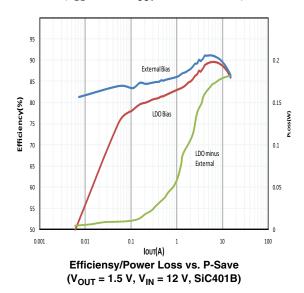

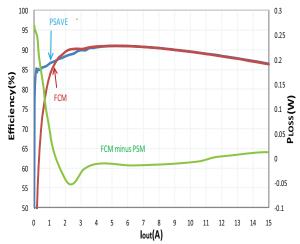

Effiency/Power Loss vs. Load P-Save (V<sub>DD</sub> = 3.3 V, V<sub>OUT</sub> = 1.5 V, SiC401B)

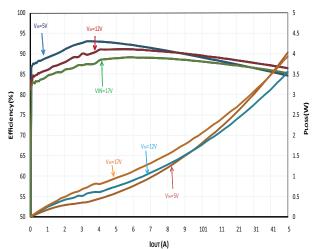

Effiency/Power Loss-P-Save vs. FCM  $(V_{DD} = 3.3 \text{ V}, V_{OUT} = 1.5 \text{ V}, V_{IN} = 12 \text{ V}, \text{SiC401B})$

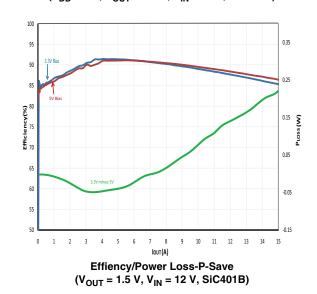

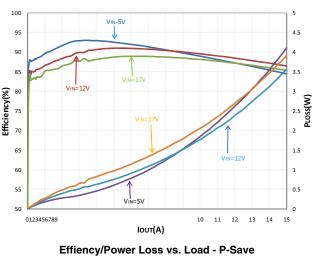

Effiency/Power Loss-P-Save vs. FCM  $(V_{DD} = 5 V, V_{OUT} = 1.5 V, V_{IN} = 12 V, SiC401B)$

Document Number: 63835 For technical questions, contact: powerictechsupport@vishay.com S12-2109-Rev. C, 03-Sep-12 This document is subject to change without notice. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishay.com/doc?91000

Vishay Siliconix

### **ELECTRICAL CHARACTERISTICS**

**SHAY**

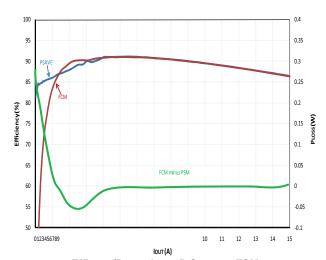

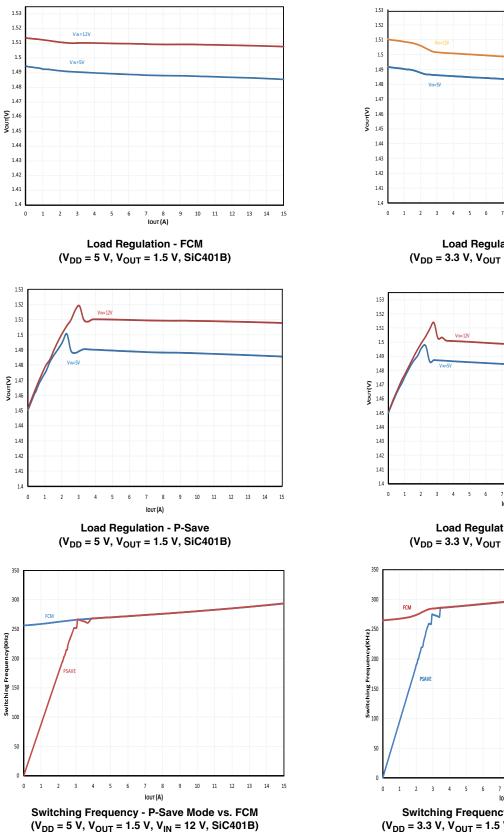

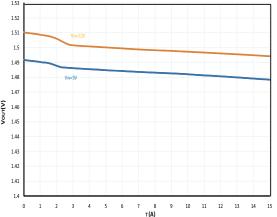

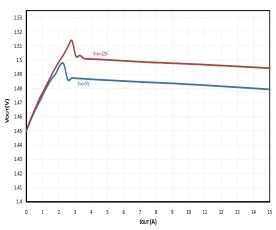

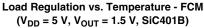

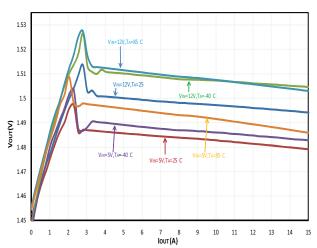

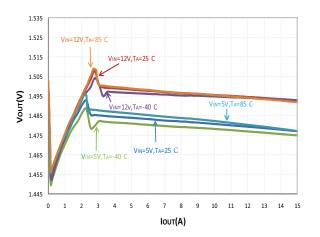

Load Regulation - FCM (V<sub>DD</sub> = 3.3 V, V<sub>OUT</sub> = 1.5 V, SiC401B)

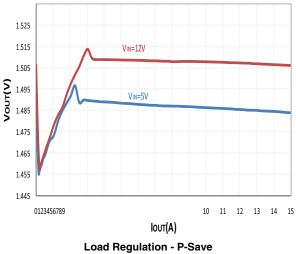

Load Regulation - P-Save (V<sub>DD</sub> = 3.3 V, V<sub>OUT</sub> = 1.5 V, SiC401B)

www.vishay.com 8

For technical questions, contact: powerictechsupport@vishay.com

Document Number: 63835 S12-2109-Rev. C, 03-Sep-12

Vishay Siliconix

#### **ELECTRICAL CHARACTERISTICS**

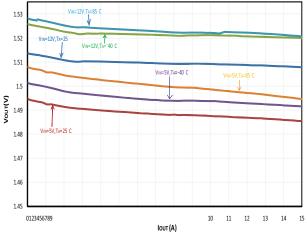

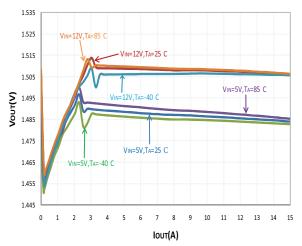

Load Regulation vs. Temperature - P-Save (V<sub>DD</sub> = 3.3 V, V<sub>OUT</sub> = 1.5 V, SiC401B)

Load Regulation vs. Temperature - FCM  $(V_{DD} = 3.3 \text{ V}, V_{OUT} = 1.5 \text{ V}, \text{SiC401B})$

Document Number: 63835 For technical questions, contact: <u>powerictechsupport@vishay.com</u> S12-2109-Rev. C, 03-Sep-12

### **ELECTRICAL CHARACTERISTICS**

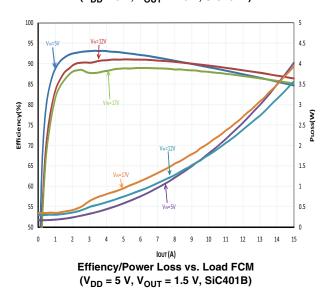

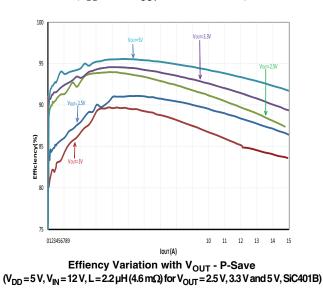

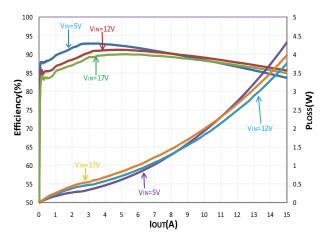

Effiency/Power Loss vs. Load - P-Save  $(V_{DD} = 3.3 V, V_{OUT} = 1.5 V, SiC401A)$

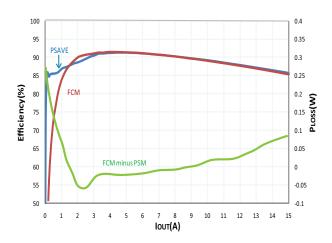

Effiency/Power Loss - P-Save vs. FCM ( $V_{DD} = 5 V$ ,  $V_{OUT} = 1.5 V$ ,  $V_{IN} = 12 V$ , SiC401A)

Effiency/Power Loss vs. Load - P-Save (V<sub>DD</sub> = 5 V, V<sub>OUT</sub> = 1.5 V, SiC401A)

VISHAY

Effiency/Power Loss - P-Save vs. FCM ( $V_{DD}$  = 3.3 V,  $V_{OUT}$  = 1.5 V,  $V_{IN}$  = 12 V, SiC401A)

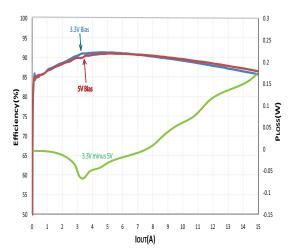

Effiency/Power Loss - P-Save (V<sub>OUT</sub> = 1.5 V, V<sub>IN</sub> = 12 V, SiC401A)

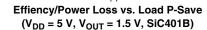

$(V_{DD} = 5 V, V_{OUT} = 1.5 V, SiC401A)$

www.vishay.com 10

For technical questions, contact: powerictechsupport@vishay.com

Document Number: 63835 S12-2109-Rev. C, 03-Sep-12

### SiC401A, SiC401BCD Vishay Siliconix

#### **ELECTRICAL CHARACTERISTICS**

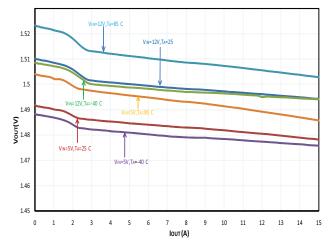

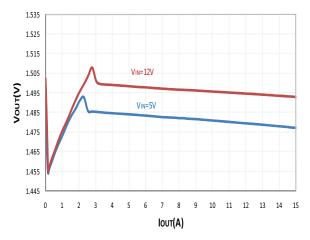

#### Load Regulation - P-Save (V<sub>DD</sub> = 3.3 V, V<sub>OUT</sub> = 1.5 V, SiC401A)

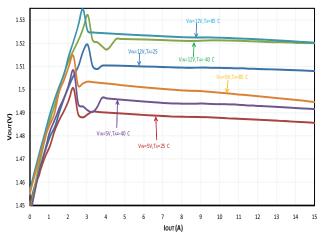

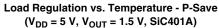

Load Regulation vs. Temperature - P-Save (V<sub>DD</sub> = 5 V, V<sub>OUT</sub> = 1.5 V, SiC401A)

Document Number: 63835 For technical questions, contact: <u>powerictechsupport@vishay.com</u> S12-2109-Rev. C, 03-Sep-12

**Vishay Siliconix**

### **ELECTRICAL CHARACTERISTICS**

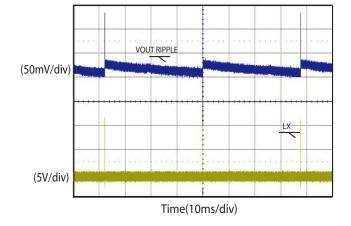

Power-Save Mode  $(V_{DD}=5~V,~V_{IN}=12~V,~V_{OUT}=1.5~V,~I_{OUT}=0~A,~SiC401A)$

$\label{eq:vdv} \begin{array}{l} \mbox{Power-Save Mode} \\ \mbox{(V}_{DD} = 5 \mbox{ V}, \mbox{ V}_{IN} = 12 \mbox{ V}, \mbox{ V}_{OUT} = 1.5 \mbox{ V}, \mbox{ I}_{OUT} = 0 \mbox{ A}, \mbox{ SiC401B}) \end{array}$

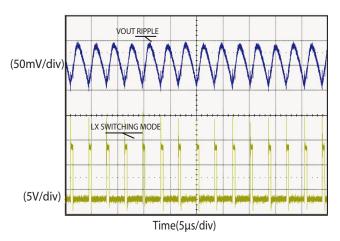

Forced Continuous Mode ( $V_{DD}$  = 5 V,  $V_{IN}$  = 12 V,  $V_{OUT}$  = 1.5 V,  $I_{OUT}$  = 15 A, SiC401B)

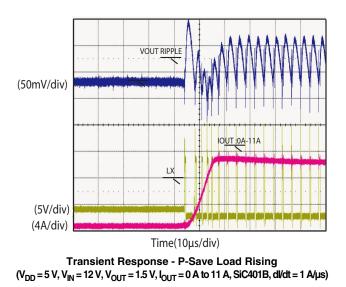

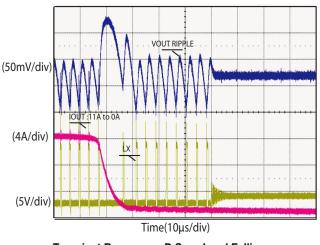

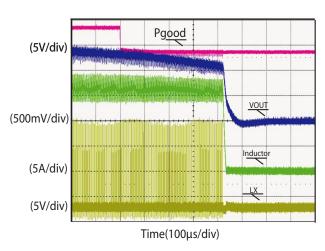

Transient Response - P-Save Load Falling (V\_{DD} = 5 V, V\_{IN} = 12 V, V\_{OUT} = 1.5 V, I\_{OUT} = 11 A to 0 A, SiC401B, dl/dt = 1 A/µs)

**Vishay Siliconix**

### **ELECTRICAL CHARACTERISTICS**

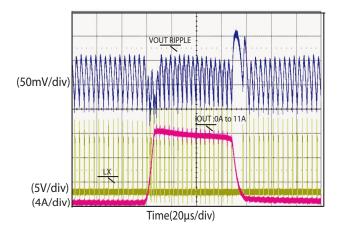

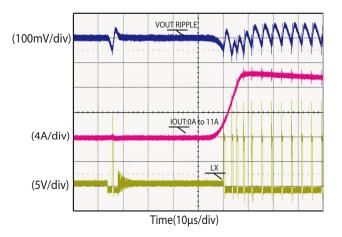

**Transient Response - FCM**

(V\_{DD} = 5 V, V\_{IN} = 12 V, V\_{OUT} = 1.5 V, I\_{OUT} = 0 A to 11 A, SiC401B, dl/dt = 1 A/\mu s)

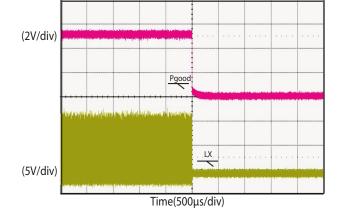

Over Temperature Shutdown at 133.4 °C (V<sub>IN</sub> = 12 V, V<sub>OUT</sub> = 1.5 V, I<sub>OUT</sub> = 0 A, LDO Mode, SiC401B)

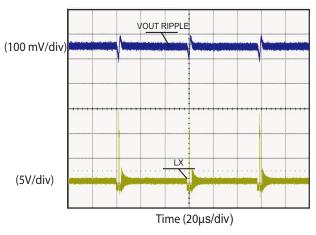

Transient Response - P-Save Load Rising  $(V_{DD} = 5 V, V_{IN} = 12 V, V_{OUT} = 1.5 V, I_{OUT} = 0 A to 11 A, SiC401A, dl/dt = 1 A/µs)$

(100mV/div) (4A/div) (5V/div) (5V/div) (5V/div) (5V/div)

Transient Response - P-Save Load Falling ( $V_{DD}$  = 5 V,  $V_{IN}$  = 12 V,  $V_{OUT}$  = 1.5 V,  $I_{OUT}$  = 11 A to 0 A, SiC401A, dl/dt = 1 A/µs)

Vishay Siliconix

#### **OPERATIONAL DESCRIPTION**

#### **Device Overview**

The SiC40 1A/B is a step down synchronous DC/DC buck co nverter with i ntegrated power MOSFETs and a 200 mA capable programmable LDO. The device is capable of 15 A ope ration at very high efficiency. A space saving  $5 \times 5$  (mm) 32- pin package is used. The programmable operating frequency of up to 1 MHz enables optimizing the configuration for PCB area and efficiency.

The buck controller uses a pseudo-fixed frequency adaptive on-time con trol. This con trol method al lows fast transient igponse which permits the use of smaller output capacitors.

#### **Input Voltage Requirements**

The SiC4 01A/B requires two input t supplies for normal operation: V<sub>IN</sub> and V<sub>DD</sub>. V<sub>IN</sub> operates over a wide range from 3 V to 17 V. V<sub>DD</sub> requires a 3 V to 5.5 V supply input that can be a n external source or the internal LDO configured to supply 3 V to 5.5 V from V<sub>IN</sub>.

#### **Power Up Sequence**

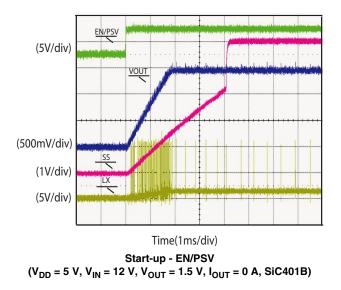

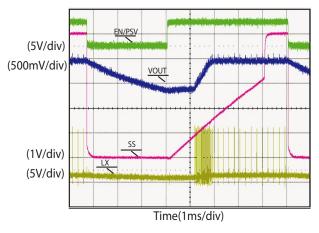

When the SiC401A/B uses an external power source at the  $V_{DD}$  pin, the switching regulator initiates the start up when  $V_{IN}$ ,  $V_{DD}$ , and EN/PSV are above their respective thresholds. When EN/PSV is at logic high,  $V_{DD}$  needs to be applied after  $V_{IN}$  rises. It is also recommend ed to use a 10  $\Omega$  resistor between an external power source and the  $V_{DD}$  pin. To start up by using the EN/PSV pin when both  $V_{DD}$  and  $V_{IN}$  are above their respective thresholds, apply EN/PSV to e nable the start-up p rocess. For SiC401A/B in self-bi ased mode, refer to the LDO section for a full description.

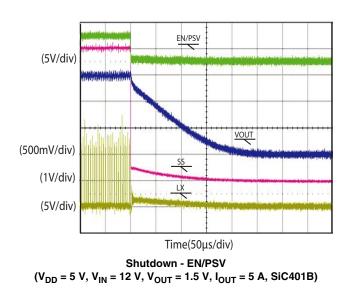

#### Shutdown

The SiC401A/B can be sh ut-down by pulling either V<sub>DD</sub> or EN/PSV below its threshold. When using an external power source, it is recommended that the V<sub>DD</sub> voltage ramps down before the V<sub>IN</sub> voltage. When V<sub>DD</sub> is active and EN/PSV at logic low, the output voltage discharges into the V<sub>OUT</sub> pin through an internal FET.

#### **Pseudo-Fixed Frequency Adaptive On-Time Control**

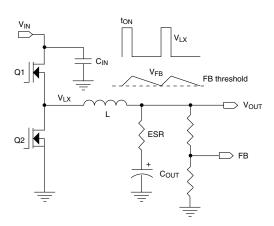

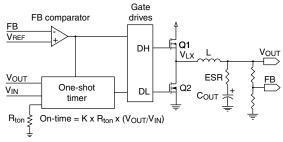

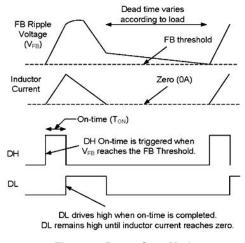

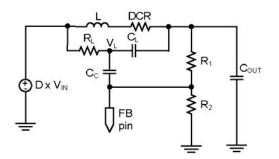

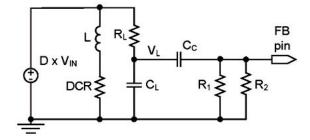

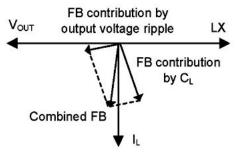

The PW M control method u sed by the SiC 401A/B is pseudo- fi xed freq uency, ad aptive on-time, as shown in figure 1. The ripple voltage generated at the output capacitor ESR is used as a PWM ramp signal. This ripple is used to trigger the on-time of the controller.

Figure 1 - Output Ripple and PWM Control Method

The adaptive on-time is determined by an internal one- shot timer. When the one-shot is triggered by the output ripple, the device se nds a si ngle on -time p ulse t o th e high-sid e MOSFET. The pulse period is determined by  $V_{OUT}$  and  $V_{IN}$ ; the pe riod is proportional to o utput vo Itage and in versely proportional to input voltage. With this adaptive on-time arrangement, the device automatically anticipates the on-time ne eded to regul ate V <sub>OUT</sub> for the present V <sub>IN</sub> condition and at the selected frequency.

The advantages of adaptive on-time control are:

- Predictable operating fre quency comp ared to other variable frequency methods.

- Reduced compon ent count by el iminating th e error amplifier and compensation components.

- Reduced component count by removing the need to sense and control inductor current.

- Fast transient response the response time is controlled by a fast comparator instead of a typically slow error amplifier.

- Reduced o utput cap acitance du e to fast transient response.

#### **One-Shot Timer and Operating Frequency**

The one-shot timer operates as shown in figure 2. The FB Comparator output g oes h igh when V <sub>FB</sub> is less than the internal 600 mV reference. This feeds into the gate drive and turns on the high-side MOSFET, and also starts the one-shot timer. The one-shot timer uses an internal comparator and a capacitor. One comparator input is connected to V<sub>OUT</sub>, the other input is connected to the capacitor. When the on-time begins, the in ternal capa citor charges from zero vol ts through a current which is proportional to V<sub>IN</sub>. When the capacitor voltage reaches V<sub>OUT</sub>, the on-time is completed and the high-side MOSFET turns off.

Figure 2 - On-Time Generation

This method automatically produces an on-time that is proportional to  $V_{OUT}$  and inversely proportional to  $V_{IN}$ . Under steady-state conditions, the switching frequency can be determined from the on-time by the following equation.

$$f_{SW} = \frac{V_{OUT}}{t_{ON} \times V_{IN}}$$

The SiC401A/B uses an external resistor to set the ontime which ind irectly sets the frequency. The on-time can be programmed to provide operating frequency up to 1 MHz using a resistor between the  $t_{ON}$  pin and ground. The resistor value is selected by the following equation.

$$R_{ton} = \frac{k}{25 \text{ pF x f}_{SW}}$$

The constant, k, equals 1, w hen V<sub>DD</sub> is greater than 3.6 V. If V<sub>DD</sub> is less than 3.6 V and V<sub>IN</sub> is greater than (V<sub>DD</sub> -1.75) x 10, k is shown by the following equation.

$$k = \frac{(V_{DD} - 1.75) \times 10}{V_{IN}}$$

The maximum RTON value allowed is shown by the following equation.

$$R_{ton\_MAX} = \frac{V_{IN\_MIN}}{15 \ \mu A}$$

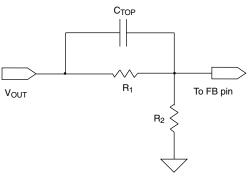

#### **VOUT Voltage Selection**

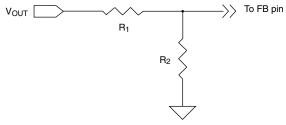

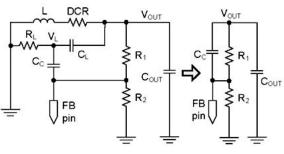

The switcher output voltage is regulated by comparing  $V_{OUT}$  as seen through a resistor divider at the FB pin to the internal 600 mV reference voltage, see figure 3.

Figure 3 - Output Voltage Selection

Note that this control method regulates the valley of the output ripple voltage , n ot the DC value. The DC output voltage  $V_{OUT}$  is offset by the output ripple according to the following equation.

$$V_{OUT} = 0.6 \ x \left(1 + \frac{R_1}{R_2}\right) + \left(\frac{V_{RIPPLE}}{2}\right)$$

When a large capacitor is placed in parallel with R1 (C<sub>TOP</sub>)  $V_{OUT}$  is shown by the following equation.

$$V_{OUT} = 0.6 \ x \left(1 + \frac{R_1}{R_2}\right) + \left(\frac{V_{\text{RIPPLE}}}{2}\right) x \sqrt{\frac{1 + (R_1 \omega C_{\text{TOP}})^2}{1 + \left(\frac{R_2 \ x \ R_1}{R_2 + R_1} \omega C_{\text{TOP}}\right)^2}}$$

#### **Enable and Power-Save Inputs**

The EN/PSV input is used to enable or disable the switching regulator. When EN/PSV is low (grounded), the switching regulator is off and in its lowe st power state. When off, the output of the switching regulator soft-discharges the output into a 15  $\Omega$  internal resistor via the V<sub>OUT</sub> pin. When EN/PSV is allowed to float, the pin voltage will float to 33 % of the voltage at V  $_{DD}$ . The switching regulator turns on with power-save disabled and all switching is in forced continuous mode.

When EN/PSV is high (above 44 % of the voltage at  $V_{DD}$ ), the switching regulator turns on with power-save enabled. The Si C401A/B P-Save operation re duces the switching frequency according to the I oad for in creased efficiency at light load conditions.

#### **Forced Continuous Mode Operation**

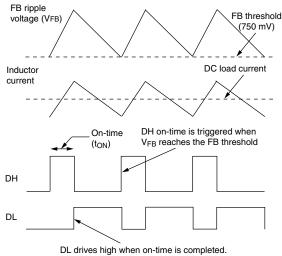

The Si C401A/B o perates the switcher i n FCM (Forced Continuous Mode) by floating the EN/PSV pin (see figure 4). In this mode one of the power MOSFETs is always on, with no in tentional d ead time o ther than to avoid cross-conduction. This feature results in uniform frequency across the full load range with the trade-off being poor efficiency at light loads due to the hi gh-frequency switching of the MOSFETs. DH is gate signal to drive upper MOSFET. DL is lower gate signal to drive lower MOSFET

### Vishay Siliconix

DL drives high when on-time is completed. DL remains high until V<sub>FB</sub> falls to the FB threshold.

Figure 4 - Forced Continuous Mode Operation

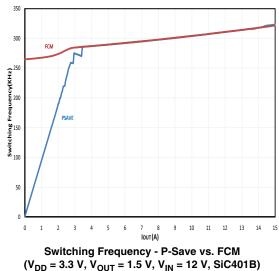

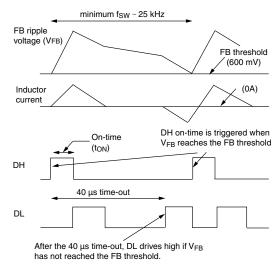

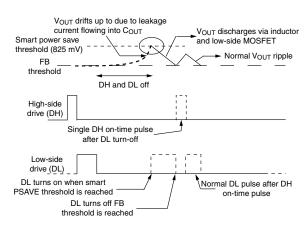

#### Ultrasonic Power-Save Operation (SiC401A)

The SiC 401A provides ul trasonic pow er-save operation at light loads, with the minimum operating frequency fixed at slightly und er 25 kHz. This is accomplish ed by using an internal timer that monitors the time between consecutive high-side gate pulses. If the time exceeds 40 µs, DL drives high to turn the low-side MOSFET on. This draws current from  $V_{OUT}$  through the inductor, forcing both  $V_{OUT}$  and  $V_{FB}$ to fall. When V<sub>FB</sub> drops to the 600 mV threshdd, the next DH (the drive signal for the high side FET) on-time is trigg ered. After the on-time is completed the high -side MOSFET is turned off and the low-side MOSFET turns on. The low-side MOSFET remains on until the in ductor current ramps down to zero, at which point the low-side MOSFET is turned off. Because the o n-times are forc ed to occur at interval s n o greater than 40 µs, the freque ncy will not fall far below 25 kHz. Figure 5 shows ultrasonic power-save operation.

#### Power-Save Operation (SiC401B)

The SiC401B provides power-save operation at light loads with n o min imum op erating freque ncy. Wi th po wer-save enabled, the internal zero crossing comparator monitors the inductor current via the voltage across the low-side MOSFET during the o ff-time. If the inductor current falls to zero for 8 c onsecutive switching cycles, the controller enters MOSFET on each subs equent cycle provided that the power-save operation. It will turn off the low-side MOSFET on each subsequent cycle provided that the current crosses zero. At this time both MOSFETs remain off until V<sub>FB</sub> drops to the 600 mV threshold. Because the MOSFETs are off, the load is supplied by the output capacitor.

If the inductor current does not reach zero on any switching cycle, the controller immedi ately exits power-save and returns to forced continuous mode.

Figure 6 shows power-save operation at light loads.

Figure 6 - Power-Save Mode

#### **Smart Power-Save Protection**

Active loads may leak current from a higher voltage into the switcher output. Under light load conditions with power-save enabled, this can force VOUT to slowly rise and reach the over-voltage threshold, resulting in a hard shut-down. Smart power-save prevents this condition. When the FB vol tage exceeds 10 % abo ve nominal, the device immediately disables po wer-save, and DL drives h igh to turn on the low-side MOSFET. This draws current from V<sub>OUT</sub> through the inductor and causes  $V_{\text{OUT}}$  to fall. When  $V_{\text{FB}}$  drops back to the 600 mV trip point, a normal toN switching cycle begins. This method pre vents a ha rd OVP sh ut-down a nd a lso cycles energy from V  $_{\rm OUT}$  back to V  $_{\rm IN}$ . It also minimizes operating power by avoid ing fo rced co nduction mode operation. Figure 7 shows typical waveforms for the Smart Power Save feature.

Figure 5 - Ultrasonic Power-Save Operation

Document Number: 63835 S12-2109-Rev. C, 03-Sep-12

Figure 7 - Smart Power-Save

#### SmartDrive<sup>™</sup>

For each DH pulse, the DH driver initially turns on the high side MOSFET at a lo wer speed, allowing a softer, smoo th turn-off of the low-side diode. Once the diode is off and the LX voltag e has risen 0.5 V a bove P <sub>GND</sub>, th e SmartDrive circuit a utomatically drives the h igh-side MOSFET on at a rapid rate. This techn ique reduces switching losses while maintaining high efficiency and al so avoids the ne ed for snubbers for the power MOSFETs.

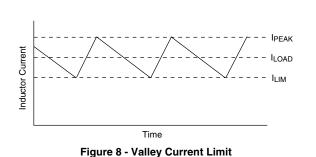

#### **Current Limit Protection**

The device features programmable current limiting, which is accomplished by using the R<sub>DS-ON</sub> of the lower MOSFET for current sensing. The current limit is set by RILIM resistor. The  $R_{ILIM}$  resistor connects from the  $I_{LIM}$  pin to the LXS pin which is also the drain of the low-side MOSFET. When the low-side MOSFET is on, an internal ~ 10 µA current flows from the ILIM pin and through the RILIM resistor, creating a voltage drop across the resistor. While the low-side MOSFET is on, the inductor current flows thr ough it and creates a voltage across the R DS-ON. The voltage across the MOSFET is negative with respect to ground. If this MOSFET voltage drop exceeds the voltage across R<sub>II IM</sub>, the voltage at the I<sub>I IM</sub> pin will be ne gative and current limit will activate. The current limit then keeps the low-side MOSFET on and will not allow another high-side on-time, un til the current in the I ow-side MOSFET reduces enough to bring the ILIM voltage back up to zero. This method regulates the inductor valley current at the level shown by ILIM in figure 8.

SiC401A, SiC401BCD

**Vishay Siliconix**

Setting the vall ey current limit to 15 A results in a pe ak inductor current of 15 A plus peak ripple current. In this situation, the average (load) current through the inductor is 15 A plus one-half the peak-to-peak ripple current.

The in ternal 10  $\,\mu A$  current source is tempe rature compensated at 4100 ppm in order to provide tracking with the R\_{DS-ON}.

The R<sub>ILIM</sub> value is calculated by the following equation.

$R_{ILIM} = 263 \times I_{LIM} \times [0.112 \times (5 \text{ V} - \text{V}_{DD}) + 1]$

When selecting a value for  $R_{ILIM}$  be sure not to exceed the absolute maximum voltage value for the  $I_{LIM}$  pin. Note that because the low-side MOSFET with low  $R_{DS-ON}$  is used for current sen sing, the PCB layout, so lder connections, and PCB connection to the LX nod e must be done carefully to obtain good results.  $R_{ILIM}$  should be connected directly to LXS (pin 28).

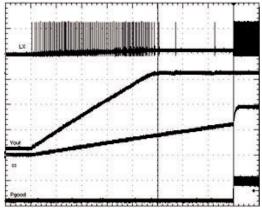

#### Soft-Start of PWM Regulator

SiC401A/B has a programmable soft-start time th at is controlled by an external capacitor at the SS pin. After the controller meets both UVLO and EN/PSV th resholds, the controller has a n i nternal cu rrent source of 3  $\mu$  A flowing through the SS pin to charge the capacitor. During the start up process (figure 9), 50 % of the voltage at the SS pin is used as the reference for the FB comparator. Th  $\,$ e PWM comparator issues an on-time pulse when the voltage at the FB pin is less than 40 % of the SS pin. As a result, the output voltage follows the SS voltage. The output voltage reaches and ma intains regulation when n th e so ft start voltage is  $\geq$  1.5 V. Th e time between the first LX pul se and V<sub>OUT</sub> reaching regulation is the s oft-start time (t $_{SS}$ ). The calculation for the soft-start time is shown by the following equation.

$$t_{SS} = C_{SS} \times \frac{1.5 \text{ V}}{3 \mu \text{A}}$$

The vo Itage at the SS pin continues to ramp u p and eventually equals 64 % of V<sub>DD</sub>. After the soft start completes, the FB pin voltage is compared to an internal reference of 0.6 V. The delay time between the V<sub>OUT</sub> regulation point and P<sub>GOOD</sub> going high is shown by the following equation.

$t_{PGOOD\text{-}DELAY} = \frac{C_{SS} \text{ x } (0.64 \text{ x } \text{V}_{DD} \text{ - } 1.5 \text{ V})}{3 \text{ } \mu \text{A}}$

For technical questions, contact: <a href="mailto:powerictechsupport@vishay.com">powerictechsupport@vishay.com</a>

www.vishay.com 17

### Vishay Siliconix

Figure 9 - Soft-start Timing Diagram

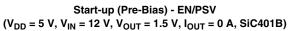

#### **Pre-Bias Start-Up**

The SiC401A/B can start up normally even when there is an existing output voltage present. The soft start time is still the same as normal start up (when the output voltage starts from zero). The output voltage starts to ramp up when 40 % of the voltage at SS pi n mee ts the exi sting FB vol tage I evel. Pre-bias startup i s achi eved by turning off the I ower gate when the in ductor current fa IIs bel ow zero. Th is method prevents the output voltage from discharging.

#### **Power Good Output**

The P <sub>GOOD</sub> (p ower good) o utput is an op en-drain output which requires a pull-up resistor. When the voltage at the FB pin is 10 % below the nominal voltage, P<sub>GOOD</sub> is pulled low. It is held low until the output voltage returns above - 8 % of nominal.

$P_{GOOD}$  will transition low if the V  $_{FB}$  pin exceeds + 20  $\,\%$  of nominal, which is also the over-voltage shutdown threshold.  $P_{GOOD}$  also pulls low if the EN/PSV pin is low when V\_{DD} is present.

#### **Output Over-Voltage Protection**

Over-voltage pr otection be comes active as so on a s the device is enabled. The threshold is set at 600 mV + 20 % (720 mV). When V<sub>FB</sub> exceeds the OVP threshold, DL latches high and the low-side MOSFET is turned on. DL remains high and the controller remains off, until the EN/PSV input is toggled or V<sub>DD</sub> is cycled. There is a 5  $\mu$ s delay built into the OVP detector to prevent false transitions. P<sub>GOOD</sub> is also low after an OVP event.

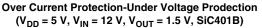

#### **Output Under-Voltage Protection**

When V <sub>FB</sub> falls 25 % be low its nomin al vol tage (falls to 450 mV) for eight consecutive clock cycles, the switcher is shut off and the DH and DL drives are pulled low to tristate the MOSFETs. The controller stays off until EN/PSV is toggled or V<sub>DD</sub> is cycled.

#### $V_{\text{DD}}$ UVLO, and POR

UVLO (Under-Voltage Lock-Out) circu itry inhibits switching and tri-states the DH/DL drivers until V<sub>DD</sub> rises above3 V. An internal POR (Power-On Reset) occurs when V<sub>DD</sub> exceeds 3 V, which resets the fault latch and a soft-start counter cycle begins which prepares for soft-start. The SiC401A/B then begins a soft-start cycle. The PWM will shut off if V<sub>DD</sub> falls below 2.4 V.

#### LDO Regulator

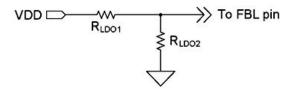

SiC401A/B has an op tion to bi as the switcher b y using an internal LDO from V<sub>IN</sub>. The LDO output is connected to V<sub>DD</sub> internally. The output of the LDO is programmable by using external resistors from the V<sub>DD</sub> pin to A<sub>GND</sub> (see figure 10). The feedback pin (FBL) for the LDO is regulated to 750 mV.

Figure 10- LDO Output Voltage Selection

The LDO output voltage is set by the following equation.

$$V_{LDO} = 750 \text{ mV x} \left( 1 + \frac{R_{LDO1}}{R_{LDO2}} \right)$$

A minimum capa citance of 1  $\mu$ F referenced to A<sub>GND</sub> is normally required at the output of the LDO for stability. Note that if the LDO vo Itage is set lower than 4.5 V, the minimum output capacitance for the LDO is 10  $\mu$ F.

#### **LDO ENL Functions**

The ENL input is used to e nable/disable the internal LDO. When ENL is a logic low, the LDO is off. When ENL is above the V  $_{\rm IN}$  U VLO threshold, the LDO is en abled and the switcher is also enabled if the EN/PSV and VDD are above their threshold. The table below summarizes the function of ENL and EN/PSV pins.

| EN/PSV   | ENL                | LDO | Switcher |

|----------|--------------------|-----|----------|

| Disabled | Low, < 0.4 V       | Off | Off      |

| Enabled  | Low, < 0.4 V       | Off | On       |

| Disabled | 1 V < High < 2.6 V | On  | Off      |

| Enabled  | 1 V < High < 2.6 V | On  | Off      |

| Disabled | High, > 2.6 V      | On  | Off      |

| Enabled  | High, > 2.6 V      | On  | On       |

The ENL pin also acts as the switcher under-voltage lockout for the V<sub>IN</sub> supply. When SiC401A/B is self-biased from the LDO and runs from the V<sub>IN</sub> power source only, the V<sub>IN</sub> UVLO

feature can be used to prevent false UV faults for the PWM output by programming with a resistor divider at the V<sub>IN</sub>, ENL and A <sub>GND</sub> pi ns. Whe n SiC4 01A/B has a n external bia s voltage at V<sub>DD</sub> and the ENL pin is used to program the V<sub>IN</sub> UVLO feature, the voltage at FBL n eeds to be higher than 750 mV to force the LDO off.

Timing is important when driving ENL with logic and not implementing V<sub>IN</sub> UVLO. The ENL pin must transition from high to low within 2switching cycles to avoid the PWM output turning off. If ENL goes below the V<sub>IN</sub> UVLO th reshold and stays above 1 V, then the switcher will turn off but the LDO will remain on.

#### LDO Start-up

Before start-up, the LDO checks the status of the following signals to ensure proper operation can be maintained.

- 1. ENL pin

- 2. V<sub>LDO</sub> output

When the ENL pin is high and VIN is above the UVLO point, the LDO will begin start-up. During the initial phase, when the V<sub>DD</sub> voltage (which is the LD O output voltage) is less than 0.75 V, the LDO initiates a current-limited start-up (typically 65 mA) to charge the output capacitors while protecting from a short circuit event. When  $V_{\text{DD}}$  is greater than 0.75 V but still less than 90 % of its final value (as sensed at the FBL pin), the LDO current limit is increased to ~1 15 mA. When V<sub>DD</sub> has reached 90 % of the final value (as sensed at the FBL pin), the LDO current limit is increased to ~ 200 mA and the LDO output is guickly driven to the nominal value by the internal LDO regulator. It is recommend ed that during LDO start-up to h old the PW M switching off un til the LDO has reached 90 % of the fin al value. This prevents overloading the current-limited LDO output during the LDO start-up. Due to the initial current limitations on the LDO during power up (figure 11), any external load attached to the V<sub>DD</sub> pin must be limited to less than the start up current before the LDO

has reached 90 % of its final regulation value.

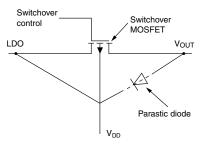

#### LDO Switch-Over Poeration

The SiC401A/B includes a switch-over function for the LDO. The switch-over function is designed to increase efficiency by using the more efficient DC/DC converter to power the LDO output, avoiding the less efficient LDO regulator when possible. The switch-over function connects the V <sub>DD</sub> pin directly to the V <sub>OUT</sub> pin using an internal switch. When the switch-over is complete the LDO is turned off, which results in a power saving s and maximizes efficiency. If the LDO

output is used to bias the SiC401A/B, then after switch-over the device is self-powered from the switching regulator with the LDO turned off.

The switch-over starts 32 switching cycles after P  $_{GOOD}$  output goes high. The voltages at the V<sub>DD</sub> and V<sub>OUT</sub> pins are then compared; if the two voltages are within ± 300 mV of each other, the V<sub>DD</sub> pin connects to the V<sub>OUT</sub> pin using an internal switch, and the LDO is turned off. To avoid unwanted switch-over, the minimum difference between the voltag es for V<sub>OUT</sub> and V<sub>DD</sub> should be ± 500 mV.

It is not recommended to use the switch-over feature for an output voltage less than V  $_{\text{DD}}$  UVLO th reshold since the SiC401A/B is not operational below that threshold.

#### Switch-Over MOSFET Parasitic Diodes

The switch-over MOSFET contains parasitic diodes that are inherent to its construction, as sho wn in figure 12. If the voltage at the V  $_{OUT}$  pin is hig her than V  $_{DD}$ , then t he respective diode will turn on and the current will flow through this diode. This has the potential of damaging the device. Therefore, V<sub>OUT</sub> must be less than V<sub>DD</sub> to prevent damaging the device.

Figure 12 - Switch-over MOSFET Parasitic Diodes

#### **Design Procedure**

When de signing a switch mo de supp ly the input voltage range, load current, switching frequency, and inductor ripple current must be specified.

The maximum input voltage (V<sub>IN max.</sub>) is the highest specified input voltage. The min imum i nput voltage (V<sub>IN min.</sub>) is determined by the lo west input voltage after evaluating the voltage drops due to connectors, fuses, switches, and PCB traces.

The following parameters define the design:

- Nominal output voltage (V<sub>OUT</sub>)

- Static or DC output tolerance

- Transient response

- Maximum load current (I<sub>OUT</sub>)

There are two values of load current to evaluate - continuous load current and peak load current. Continuous load current relates to thermal stresses which d rive the selection of the in ductor and in put capaci tors. Peak loa d current determines instantaneous component stresses and filtering requirements such as inductor saturation, output capacitors, and design of the current limit circuit.

The following values are used in this design:

•  $V_{IN} = 12 V \pm 10 \%$

Document Number: 63835

For technical questions, contact: <a href="mailto:powerictechsupport@vishay.com">powerictechsupport@vishay.com</a> www.vishay.com

19

S12-2109-Rev. C, 03-Sep-12

This document is subject to change without notice.

19

• V<sub>OUT</sub> = 1.5 V ± 4 %

**Vishay Siliconix**

- f<sub>SW</sub> = 300 kHz

- Load = 15 A max.

#### **Frequency Selection**

Selection of the swi tching freq uency re quires making a trade-off between the size and cost of the external filter components (inductor and output capacitor) and the power conversion efficiency.

The desired switching frequency is 300 kHz which results from using component selected for optimum size and cost. A resistor ( $R_{tON}$ ) is used to program the on-time (indirectly setting the frequency) using the following equation.

$$R_{ton} = \frac{k}{25 \text{ pF x } f_{SW}}$$

To select  $R_{tON},$  use the maximum value for  $V_{IN},$  and for  $t_{ON}$  use the value associated with maximum  $V_{IN}.$

$$t_{ON} = \frac{V_{OUT}}{V_{INmax.} \times f_{SW}}$$

Substituting for R<sub>tON</sub> results in the following solution.

$R_{tON} = 133.3 \text{ k}\Omega$ , use  $R_{tON} = 130 \text{ k}\Omega$ .

#### Inductor Selection

In order to determine the inductance, the ripple current must first be defined. Low inductor values result in smaller size but create hi gher ripple current which can reduce efficien cy. Higher inductor values will reduce the ripple current/voltage and for a given DC resistance are more efficien t. However, larger inductance translates directly into larger packages and higher cost. Co st, size, output ripple, and efficiency are a ll used in the selection process.

The ripp le current will also set the boun dary for  $P_{Save}$  operation. The switching will typ ically enter  $P_{Save}$  mode when the load current decreases to 1/2 of the ripple current. For example, if ripple current is 4 A then  $P_{Save}$  operation will typically start for loads less than 2 A. If ripple current is set at 40 % of maximum bad current, then  $P_{Save}$  will start for loads less than 20 % of maximum current.

The inductor value is typically selected to provide a rippl e current that is between 25 % to 50 % of the maximum load current. This provides a n optimal trade-off betwe en cost, efficiency, and transient performance.

During the on-time, voltage across the inductor is (V\_{IN} - V\_{OUT}). The equation for determining inductance is shown next.

$$L = \frac{(V_{IN} - V_{OUT}) \times t_{ON}}{I_{RIPPLE}}$$

#### Example

In this e xample, the i nductor rip ple current is set equ al to 30 % of the maximum load current. Thus ripple current will be

30 % x 15 A or 4.5 A. To  $\,$  find the min imum ind uctance needed, use the  $\,$  V  $_{IN}$  and t  $\,_{ON}$  values that correspond to  $\,$  V  $_{INmax.}$

$$L = \frac{(13.2 - 1.5) \text{ x } 379 \text{ ns}}{4.5 \text{ A}} = 0.99 \text{ } \mu\text{H}$$

A slightly larger value of 1  $\mu H$  is selected. This will decrease the maximum I\_{RIPPLE} to 4.43 A.

Note that the inductor must be rated for the maximum DC load current plus 1/2 of the ripple current.

The ripple current under minimum V  $_{\rm IN}$  con ditions is a lso checked using the following equations.

$$t_{ON\_VINmin.} = \frac{25 \text{ pF x R}_{tON x VOUT}}{V_{INmin.}} = 451 \text{ ns}$$

$$I_{RIPPLE} = \frac{(V_{IN} - V_{OUT}) \text{ x toN}}{L}$$

$$I_{RIPPLE\_VINmin.} = \frac{(10.8 - 1.5) \text{ x 451 ns}}{1 \text{ }\mu\text{H}} = 4.19 \text{ A}$$

#### **Capacitor Selection**

The output ca pacitors are chosen ba sed upon required ESR and cap acitance. The maximum ESR requirement is controlled by the output ripple requirement and the DC tolerance. The output voltage has a DC value that is equal to the valley of the output ripple plus 1/2 of the peak-to-peak ripple.

A change in the output ripple voltage will lead to a change in DC voltage at the output.

The design goal for output voltage ripple is 3% of 1.5 V or 45 mV. The maximum ESR value allowed is shown by the following equations.

$$\text{ESR}_{\text{max.}} = \frac{\text{V}_{\text{RIPPLE}}}{\text{I}_{\text{RIPPLEmax.}}} = \frac{45 \text{ mV}}{4.43 \text{ A}}$$

$$\text{ESR}_{\text{max}} = 10.2 \text{ m}\Omega$$

The output capacitance is usually chosen to meet transient requirements. A worst-case load release, from maximum load to no load at the exact moment when inductor current is at the peak, determines the required capacitance. If the load release is i nstantaneous (load changes from maximum to zero in < 1  $\mu s$ ), the output capacitor must absorb all the inductor's stored energy. This will cause a peak voltage on the capacitor according to the following equation.

$$C_{OUT\_min.} = \frac{L (I_{OUT} + \frac{1}{2} \times I_{RIPPLEmax.})^2}{(V_{PEAK})^2 - (V_{OUT})^2}$$

Assuming a peak voltage  $V_{PEAK}$  of 1.65 V (150 mV rise upon load rele ase), and a 15 A load rele ase, the required capacitance is shown by the next equation.

www.vishay.com 20

$$C_{OUT\_min.} = \frac{1 \ \mu H \ (10 + \frac{1}{2} \times 4.43)^2}{(1.65)^2 - (1.5)^2}$$

C\_{OUT\\_min.} = 316 \ \mu F

During the load release time, the voltage cross the inductor is approximately - V<sub>OUT</sub>. This causes a down-slope or falling di/dt in the inductor. If the load dl/dt is not much faster than the dl/dt of the inductor, then the inductor current will tend to track the falling load current. This will reduce the excess inductive energy that must be ab sorbed by the o utput capacitor; therefore a smaller capacitance can be used.

The following can be used to calculate the needed capacitance for a given  $dI_{LOAD}/dt$ .

Peak inductor current is shown by the next equation.

$I_{LPK} = I_{max} + 1/2 \times I_{RIPPLEmax}$

$I_{I PK} = 10 + 1/2 \times 4.43 = 12.215 \text{ A}$

Rate of change of load current =  $\frac{dI_{LOAD}}{dt}$

I<sub>max.</sub> = maximum load release = 15 A

$$C_{OUT} = I_{LPK} \times \frac{L \times \frac{I_{LPK}}{V_{OUT}} - \frac{I_{max.}}{dI_{LOAD}} \times dt}{2 (V_{PK} - V_{OUT})}$$

Example

$$\frac{dI_{LOAD}}{dt} = \frac{2.5 \text{ A}}{1 \text{ }\mu\text{s}}$$

This would cause the output current to move from 15 A to 0 A in 4 µs, g iving the min imum o utput ca pacitance requirement shown in the following equation.

$$C_{OUT} = 12.215 \text{ x} \frac{1 \ \mu\text{H x}}{2} \frac{12.215}{1.5} - \frac{10}{2.5} \text{ x} 1 \ \mu\text{s}}{2 \ (1.65 - 1.5)}$$

Note that C  $_{OUT}$  is much small er in this exa mple, 169  $\mu$ F compared to 316 µF based on a worst case load release. To meet the two de sign criteria o f minimum 3 16 µF and maximum 10.2 m $\Omega$  ESR, select one capacitor of 330  $\mu$ F and  $9 \text{ m}\Omega \text{ ESR}.$

#### **Stability Considerations**

Unstable o peration is p ossible wi th ada ptive o n-time controllers, and usually takes the form of doub le-pulsing or ESR loop instability.

Double-pulsing occurs due to switching noise seen at the FB input or because the FB ripple voltage is too low. This causes the FB compa rator to trigger prematurely after the 250 ns minimum off-time has expired. In extreme case s the noise can cause three or more successive on -times. Do ublepulsing will result in higher ripple voltage at the output, but in

## SiC401A, SiC401BCD

### **Vishay Siliconix**

most applications it wil I not affect operation. This form of instability can usually be avoided by providing the FB pin with a smooth, clean ripple signal that is at least 10 mVp-p, which may dictate the need to increa se the ESR of the output capacitors. It is also imperative to provid e a proper PCB layout as discussed in the Layout Guidelines section.