# 2-W STEREO AUDIO POWER AMPLIFIER WITH FOUR SELECTABLE GAIN SETTINGS

#### **GENERAL DESCRIPTION**

The EMA2217 is a stereo audio power amplifier in a 20-pin TSSOP thermally enhanced package capable of driving 2W of continuous RMS power per channel into  $4\Omega$  loads. Internal gain control minimizes the number of external components needed, simplifying the design, and freeing up board space for other features. Amplifier gain is internally configured and controlled by way of two terminals (G0 and G1). Gain settings of 6 dB, 10 dB, 15.6 dB, and 21.6 dB are provided. EMP products are Pb-free and RoHS compliant.

### **FEATURES**

- Internal Gain control Which Eliminates External Gain-Setting Resistors

- Fully Differential Configuration

- Low Supply Current (6mA Typical)

- De-pop Citcuitry

### **APPLICATIONS**

Notebook Computers, PDAs, and Other Portable

Audio devices

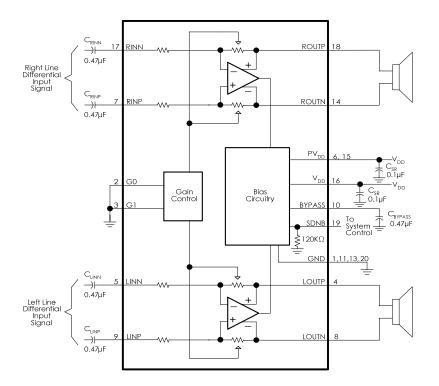

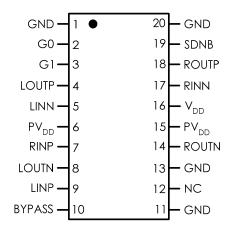

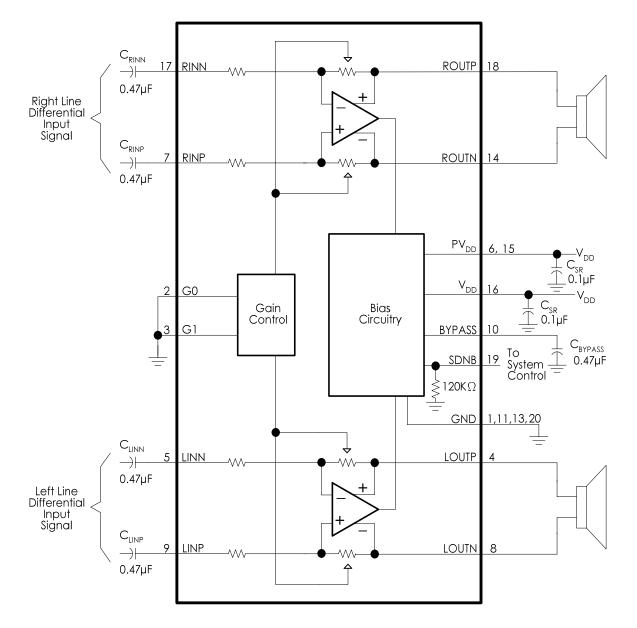

### **CONNECTION DIAGRAM**

TSSOP-20

# **ORDER INFORMATION**

EMA2217-50QE16GRR

| 50   | 5.0V Operation                    |

|------|-----------------------------------|

| QE16 | TSSOP-20FD Package                |

| G    | Lead-free Package; SnBi (Pb Free) |

| R    | Commercial Grade Temperature      |

|      | Rating: -40 to 85°C               |

| R    | Package in Tape & Reel            |

# **MARKING & PACKING INFORMATION**

| Package Type | Product ID        | Package Marking | Transport Media      |

|--------------|-------------------|-----------------|----------------------|

|              |                   | EMP             |                      |

| TSSOP-20     | EMA2217-50QE16GRR | EMA2217         | 3K units Tape & Reel |

|              |                   | DATE CODE       |                      |

### **TERMINAL FUNCTIONS**

| TERM             | TERMINAL   |     | TERMINAL I/O                                                 |  | DESCRIPTION |  |

|------------------|------------|-----|--------------------------------------------------------------|--|-------------|--|

| NAME             | NO.        | 1/0 | DESCRIPTION                                                  |  |             |  |

| BYPASS           | 10         | -   | Tap to voltage divider for internal midsupply bias generator |  |             |  |

| G0               | 2          | Ι   | Bit 0 of gain select                                         |  |             |  |

| G1               | 3          | Ι   | Bit 1 of gain select                                         |  |             |  |

| GND              | 1,11,13,20 | -   | Ground                                                       |  |             |  |

| LINN             | 5          | Ι   | Left channel negative differential input                     |  |             |  |

| LINP             | 9          | Ι   | Left channel positive differential input                     |  |             |  |

| LOUTN            | 8          | 0   | Left channel negative output                                 |  |             |  |

| LOUTP            | 4          | 0   | Left channel positive output                                 |  |             |  |

| NC               | 12         | -   | No connection                                                |  |             |  |

| PV <sub>DD</sub> | 6,15       | I   | Supply voltage terminal                                      |  |             |  |

| ROUTN           | 14 | 0 | Right channel negative output             |  |

|-----------------|----|---|-------------------------------------------|--|

| ROUTP           | 18 | 0 | Right channel positive output             |  |

| RINN            | 17 | I | Right channel negative differential input |  |

| RINP            | 7  | I | ight channel positive differential input  |  |

| SDNB            | 19 | I | laces IC in shutdown mode when held low   |  |

| V <sub>DD</sub> | 16 | I | Supply voltage terminal                   |  |

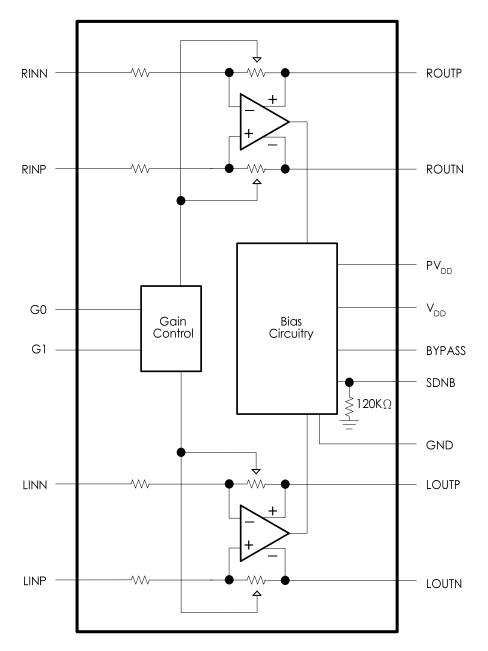

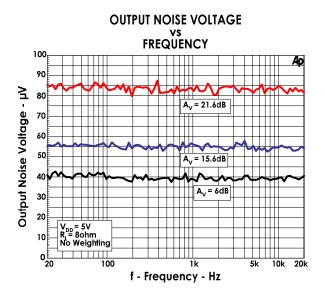

### FUNCTION BLOCK DIAGRAM

### **ABSOLUTE MAXIMUM RATINGS**

| Supply Voltage       | 6.0V               | Thermal Resistance          |                                                                   |

|----------------------|--------------------|-----------------------------|-------------------------------------------------------------------|

| Storage Temperature  | -65°C to +150°C    | $\theta_{JA}$ (TSSOP-20 FD) | 55°C/W                                                            |

| Input Voltage        | -0.3V to VDD +0.3V | <b>Operating Ratings</b>    |                                                                   |

| Power Dissipation    | Internally Limited | Temperature Range           | $\text{-40°C} \ \leq \ T_{\text{A}} \leq \ 85^{\text{o}}\text{C}$ |

| ESD Susceptibility   | HBM 2kV, MM 200V   | Supply Voltage              | $2.5V~\leq~V_{\text{DD}}\leq~5.5V$                                |

| Junction Temperature | 150°C              |                             |                                                                   |

### ELECTRICAL CHARACTERISTICS

Apply for  $V_{DD}$  = 5V,  $A_V$ =6dB,  $R_L$  = 8 $\Omega$  and  $T_A$  = 25°C (unless otherwise noted)

| Symbol | Parameter                            | Conditions                                                                                                                                 | EMA2217 |                       |     | Units |

|--------|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|---------|-----------------------|-----|-------|

| Symbol | ruidineiei                           | Conditions                                                                                                                                 | Min     | Тур                   | Max | UTIIS |

| IDD    | Quiescent Power Supply Current       | V <sub>IN</sub> = 0V, no load                                                                                                              |         | 6                     | 10  | mA    |

| lsd    | Shutdown Current                     | $V_{SDNB} = 0.4V$                                                                                                                          |         | 0.1                   | 1.0 | μA    |

| Iн     | High-level Input Current             | SDNB = 1.2V<br>G0 = G1 = 5V                                                                                                                |         | 10                    | 0.1 | μA    |

| IIL    | Low-level Input Current              | SDNB = 0.4V<br>G0 = G1 = 0V                                                                                                                |         | 3.3                   | 0.1 | μA    |

| VIH    | High-level Input Voltage             | SDNB<br>G0/G1                                                                                                                              | 1.2     | 5                     |     | V     |

| VIL    | Low-level Input Voltage              | SDNB<br>G0/G1                                                                                                                              |         | 0                     | 0.4 | V     |

| Zı     | Input Impedance                      |                                                                                                                                            | 20      | 25                    | 30  | kΩ    |

| Vos    | Output Offset Voltage                | V <sub>IN</sub> = 0V, no load, measure<br>differentially                                                                                   |         | 5                     | 25  | mV    |

| Ро     | Output Power                         | $THD + N = 1 \%, f = 1 kHz$ $R_L = 3\Omega$ $R_L = 4\Omega$ $R_L = 8\Omega$                                                                |         | 2.3<br>2<br>1.32      |     | W     |

|        |                                      | $THD + N = 10\%, f = 1kHz$ $R_L = 3\Omega$ $R_L = 4\Omega$ $R_L = 8\Omega$                                                                 |         | 2.9<br>2.45<br>1.6    |     |       |

| THD+N  | Total Harmonic<br>Distortion + Noise | f = 1  kHz<br>$R_{L} = 3\Omega, P_{O} = 1.75\text{ W}$<br>$R_{L} = 4\Omega, P_{O} = 1.5\text{ W}$<br>$R_{L} = 8\Omega, P_{O} = 1\text{ W}$ |         | 0.07<br>0.06<br>0.015 |     | %     |

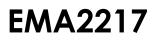

| PSRR   | Power Supply Rejection Ratio         | V <sub>RIPPLE</sub> = 200mV <sub>PP</sub> , sine wave,<br>input ac-grounded<br>f = 20 to 20kHz,                                            |         | -75                   |     | dB    |

| CMRR   | Common-mode Rejection Ratio          | $V_{I} = 1V_{PP}$ , f = 20 to 20kHz                                                                                                        |         | -62                   |     | dB    |

| C               | Devenue a la r                       |                                                                                                         | EMA2217 |                      |     | 11 11 |  |

|-----------------|--------------------------------------|---------------------------------------------------------------------------------------------------------|---------|----------------------|-----|-------|--|

| Symbol          | Parameter                            | Conditions                                                                                              | Min     | Тур                  | Max | Units |  |

| I <sub>DD</sub> | Quiescent Power Supply Current       | V <sub>IN</sub> = 0V, no load                                                                           |         | 4                    | 10  | mA    |  |

| I <sub>SD</sub> | Shutdown Current                     | $V_{SDNB} = 0.4V$                                                                                       |         | 0.1                  | 1.0 | μA    |  |

| Іін             | High-level Input Current             | SDNB = 1.2V<br>G0 = G1 = 2.6V                                                                           |         | 10                   | 0.1 | μA    |  |

| l <sub>IL</sub> | Low-level Input Current              | SDNB = 0.4V<br>G0 = G1 = 0V                                                                             |         | 3.3                  | 0.1 | μA    |  |

| VIH             | High-level Input Voltage             | SDNB<br>G0/G1                                                                                           | 1.2     | 2.6                  |     | V     |  |

| VIL             | Low-level Input Voltage              | SDNB<br>G0/G1                                                                                           |         | 0                    | 0.4 | V     |  |

| Zı              | Input Impedance                      |                                                                                                         | 20      | 25                   | 30  | kΩ    |  |

| Vos             | Output Offset Voltage                | V <sub>IN</sub> = 0V, no load, measure<br>differentially                                                |         | 5                    | 25  | mV    |  |

| Po              | Output Power                         | $THD + N = 1 \%, f = 1 kHz$ $R_L = 3\Omega$ $R_L = 4\Omega$ $R_L = 8\Omega$                             |         | 0.55<br>0.5<br>0.32  |     | W     |  |

| 10              |                                      | $THD + N = 10\%, f = 1kHz$ $R_{L} = 3\Omega$ $R_{L} = 4\Omega$ $R_{L} = 8\Omega$                        |         | 0.68<br>0.6<br>0.4   |     |       |  |

| THD+N           | Total Harmonic<br>Distortion + Noise | f = 1 kHz<br>$R_L = 3\Omega, P_O = 0.5W$<br>$R_L = 4\Omega, P_O = 0.4W$<br>$R_L = 8\Omega, P_O = 0.25W$ |         | 0.03<br>0.02<br>0.03 |     | %     |  |

| PSRR            | Power Supply Rejection Ratio         | V <sub>RIPPLE</sub> = 200mV <sub>PP</sub> , sine wave,<br>input ac-grounded<br>f = 20 to 20KHz,         |         | -62                  |     | dB    |  |

| CMRR            | Common-mode Rejection Ratio          | VI = 1 VPP, f = 20 to 20kHz                                                                             |         | -70                  |     | dB    |  |

#### Apply for $V_{DD} = 2.6V$ , $A_V = 6$ dB, $R_L = 8\Omega$ and $T_A = 25^{\circ}C$ (unless otherwise noted)

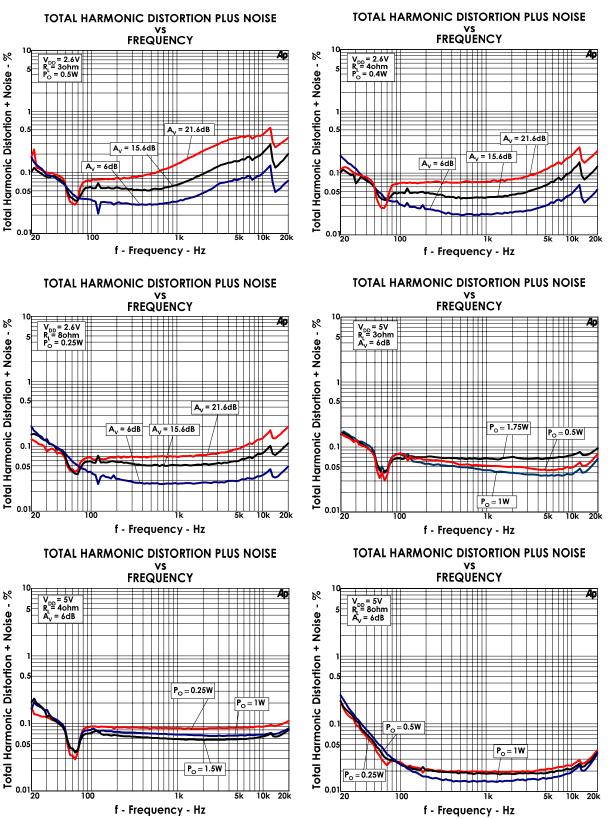

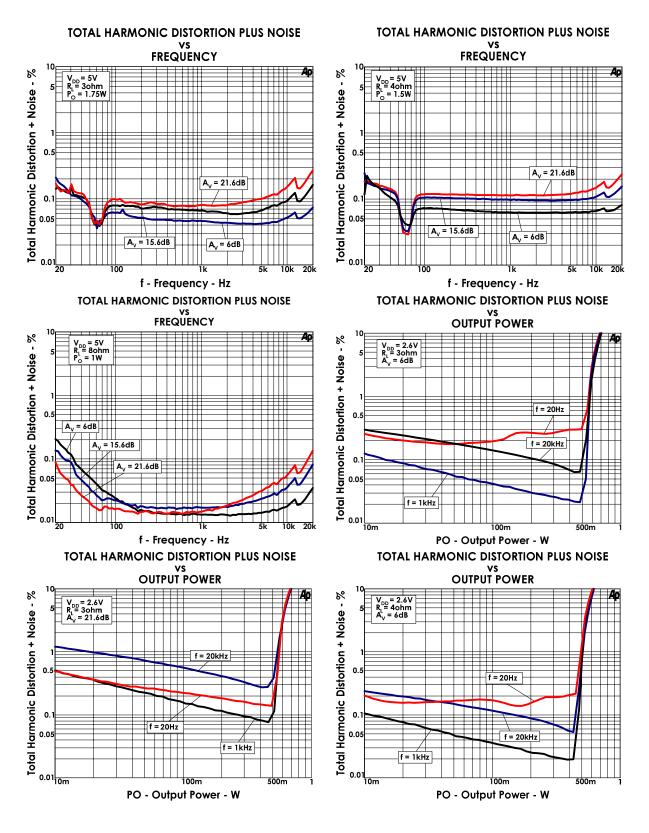

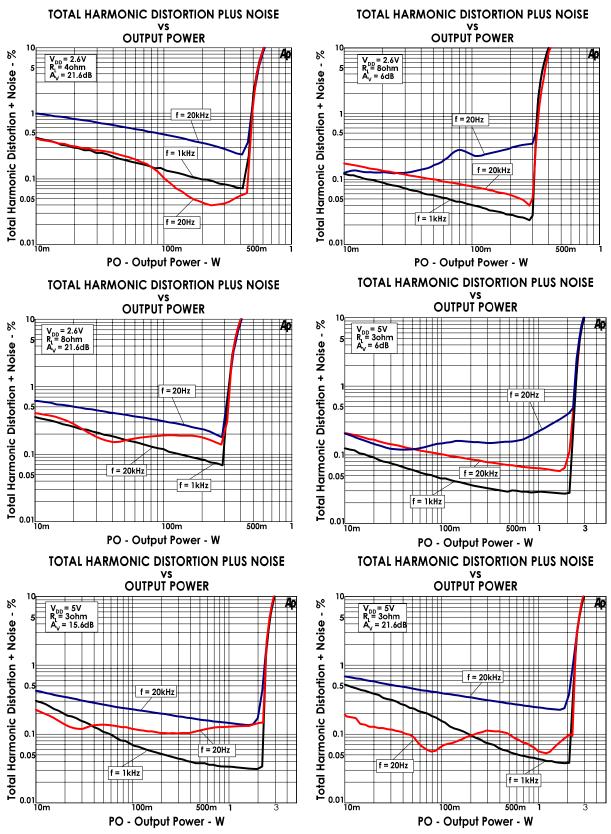

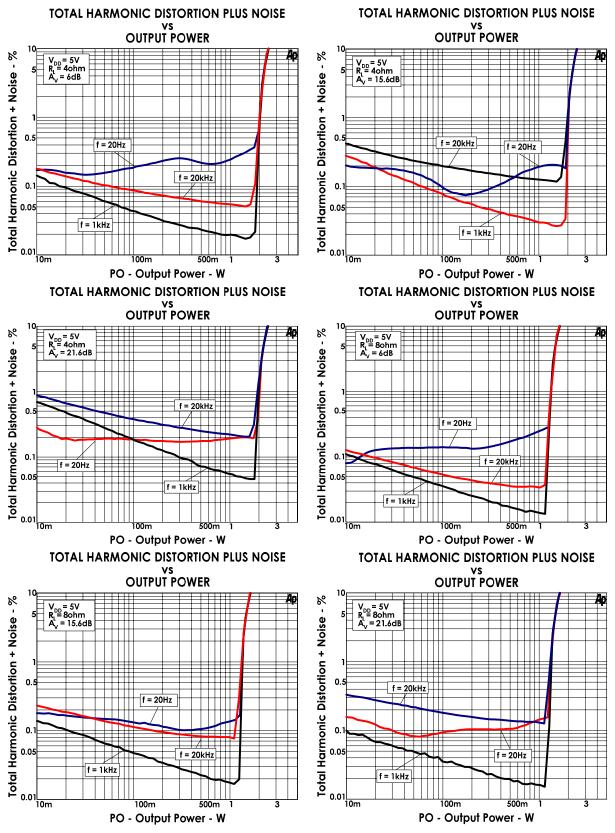

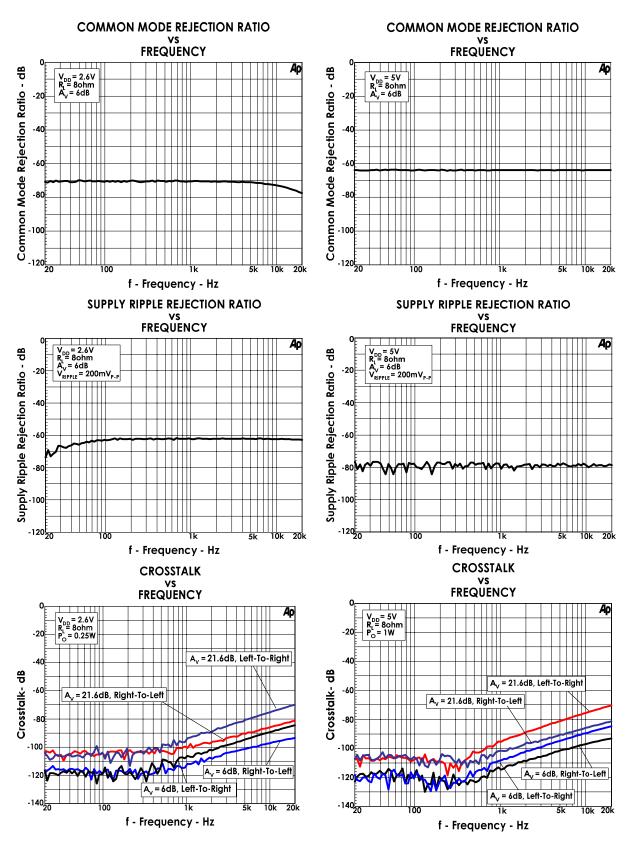

#### **TYPICAL PERFORMANCE CHARACTERISTICS**

Elite MicroPower Inc. reserves the right to make changes to improve reliability or manufacturability without notice, and customers are advised to obtain the latest version of relevant information prior to placing orders.

Elite MicroPower Inc. reserves the right to make changes to improve reliability or manufacturability without notice, and customers are advised to obtain the latest version of relevant information prior to placing orders.

# **APPLICATION INFORMATION**

### **APPLICATION INFORMATION**

Figure 2. Typical EMA2217 Application Circuit Using Differential Inputs

NOTE A: A 0.1 µF ceramic capacitor should be placed as close as possible to the IC. For filtering lower frequency noise signals, a larger electrolytic capacitor of 10 µF or greater should be placed near the audio power amplifier.

# **APPLICATION INFORMATION**

#### shutdown modes

The EMA2217 employs a shutdown mode of operation designed to reduce supply current,  $I_{DD}$ , to the absolute minimum level during periods of nonuse for battery-power conservation. The SDNB input terminal should be held high during normal operation when the amplifier is in use. Pulling SDNB low causes the outputs to mute and the amplifier to enter a low-current state,  $I_{DD} < 1 \ \mu$ A. SDNB should never be left unconnected because amplifier operation would be unpredictable.

#### gain setting via G0 and G1 inputs

The gain of the EMA2217 is set by two input terminals, G0 and G1.

#### Table 1. Gain Settings

| G0 | G1 | GAIN (dB) |

|----|----|-----------|

| 0  | 0  | 6         |

| 0  | 1  | 10        |

| 1  | 0  | 15.6      |

| 1  | 1  | 21.6      |

The gains listed in Table 1 are realized by changing the taps on the feedback resistors inside the amplifier. Input impedance, ZI (25 k $\Omega$ ), is independent on the gain setting. The actual gain settings are controlled by ratios of resistors, so the actual gain distribution from part-to-part is quite good. However, the input impedance will shift by 20% due to shifts in the actual resistance of the input impedance.

For design purposes, the input network (discussed in the next section) should be designed assuming an input impedance of 20 k $\Omega$ , which is the absolute minimum input impedance of the EMA2217.

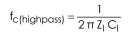

#### input capacitor, C

In the typical application an input capacitor,  $C_i$ , is required to allow the amplifier to bias the input signal to the proper dc level for optimum operation. In this case,  $C_i$  and the input impedance of the amplifier,  $Z_i$ , form a high-pass filter with the corner frequency determined in equation 1.

The value of C<sub>1</sub> is important to consider as it directly affects the bass (low frequency) performance of the circuit. Consider the example where  $Z_1$  is 20 k $\Omega$ , which is the absolute minimum input impedance of the EMA2217, and the specification calls for a flat bass response down to 40 Hz. Equation 2 is reconfigured as equation 2.

$$C_{I} = \frac{1}{2 \pi Z_{I} f_{C}}$$

<sup>(2)</sup>

In this example,  $C_1$  is  $0.2\mu$ F, so one would likely choose a value in the range of  $0.22\mu$ F to 1  $\mu$ F. A further consideration for this capacitor is the leakage path from the input source through the input network (C<sub>1</sub>) and the feedback network to the load. This leakage current creates a DC offset voltage at the input to the amplifier that reduces useful headroom, especially in high-gain applications. For this reason a low-leakage

tantalum or ceramic capacitor is the best choice. When polarized capacitors are used, the positive side of the capacitor should face the amplifier input in most applications, as the dc level there is held at  $V_{DD}/2$ , which is likely higher than the source dc level. It is important to confirm the capacitor polarity in the application.

#### power supply decoupling, CS

The EMA2217 is a high-performance CMOS audio amplifier that requires adequate power supply decoupling to ensure the output total harmonic distortion (THD) is as low as possible. Power supply decoupling also prevents oscillations for long lead lengths between the amplifier and the speaker. The optimum decoupling is achieved by using two capacitors of different types that target different types of noise on the power supply leads. For higher frequency transients, spikes, or digital hash on the line, a good low equivalent-series-resistance (ESR) ceramic capacitor, typically  $0.1\mu$ F placed as close as possible to the device VDD lead, works best. For filtering lower-frequency noise signals, a larger aluminum electrolytic capacitor of 10  $\mu$ F or greater placed near the audio power amplifier is recommended.

#### midrail bypass capacitor, CBYP

The mid-rail bypass capacitor  $C_{BYP}$ , the most critical capacitor serves several important functions. During start-up or recovery from shutdown mode,  $C_{BYP}$  determines the rate at which the amplifier starts up. The second function is to reduce noise produced by the power supply caused by coupling into the output drive signal. This noise is from the mid-rail generation circuit internal to the amplifier, which appears as degraded PSRR and THD+N.

Bypass capacitor,  $C_{BYP}$ , values of 0.47  $\mu$ F to 1  $\mu$ F ceramic or tantalum low-ESR capacitors are recommended for the best THD and noise performance.

#### using low-ESR capacitors

Low-ESR capacitors are recommended throughout this applications section. A real (as opposed to ideal) capacitor can be modeled simply as a resistor in series with an ideal capacitor. The voltage drop across this resistor minimizes the beneficial effects of the capacitor in the circuit. The lower the equivalent value of this resistance, the more the real capacitor behaves like an ideal capacitor.

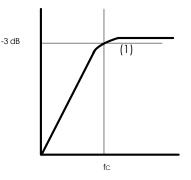

### **TSSOP-20 Exposed Pad OUTLINE DIMENSION**

|   | VARIATIONS (A | LL DINEVSION | IS SHOWN IN | MM)  |

|---|---------------|--------------|-------------|------|

|   | SYMBOLS       | MIN.         | NOM.        | MAX. |

|   | A             | -            |             | 1.20 |

| A | A1            | 0.05         | -           | 0.15 |

| 承 | A2            | 0.80         | 0.90        | 1.05 |

|   | ь             | 0.19         | -           | 0.30 |

| 承 | c             | 0.09         |             | 0.20 |

|   | Ď             | 6.40         | 6.50        | 6.60 |

|   | E1            | 4.30         | 4.40        | 4.50 |

|   | E             |              | 6.40 BSC    |      |

|   | Φ             |              | 0.65 BSC    |      |

|   | L1            |              | 1.00 REF    |      |

| 渔 | L             | 0.50         | 0.60        | 0.75 |

|   | n             | 0.20         | _           | _    |

|   | θ             | 6            | _           | 8    |

#### 3 THERMALLY ENHANCED DIMENSIONS (SHOWN IN WM)

| PAD SIZE | E2       | D1       |

|----------|----------|----------|

| 118×16E  | 2.70 REF | 3.77 REF |

© Copyright 2006 All rights reserved.

No part of this document may be reproduced or duplicated in any form or by any means without the prior permission of EMP.

The contents contained in this document are believed to be accurate at the time of publication. EMP assumes no responsibility for any error in this document, and reserves the right to change the products or specification in this document without notice.

The information contained herein is presented only as a guide or examples for the application of our products. No responsibility is assumed by EMP for any infringement of patents, copyrights, or other intellectual property rights of third parties which may result from its use. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of EMP or others.

Any semiconductor devices may have inherently a certain rate of failure. To minimize risks associated with customer's application, adequate design and operating safeguards against injury, damage, or loss from such failure, should be provided by the customer when making application designs.

EMP's products are not authorized for use in critical applications such as, but not limited to, life support devices or system, where failure or abnormal operation may directly affect human lives or cause physical injury or property damage. If products described here are to be used for such kinds of application, purchaser must do its own quality assurance testing appropriate to such applications.