# UNISONIC TECHNOLOGIES CO., LTD

83CXXX **Preliminary** CMOS IC

# 4-PIN µP VOLTAGE MONITORS WITH MANUAL RESET INPUT

#### **DESCRIPTION**

The UTC 83CXXX is a microprocessor supervisory circuit. It has an active-low RESET and push-pull outputs. The circuit can assert a reset signal as long as the V<sub>CC</sub> power supplies voltage dropping below a preset threshold and it keep the reset signal for at least 140ms when  $V_{\text{CC}}$  has risen above the reset threshold. The reset threshold can be operated with multi-supply voltages.

The UTC 83CXXX provides the circuit with perfect reliability and low cost through eliminating external components and adjustments when applied with +5V, +3.3V, +3.0V power supply The UTC 83CXXX also provide a de-bounced manual reset input.

The reset comparator can work despite of fast transients on V<sub>CC</sub>, and the outputs are guaranteed to be in the right logic state while V<sub>CC</sub> is down to 1V.

In applications, the UTC 83CXXX is suitable for computers, intelligent instruments, controllers, critical microprocessor and microcomputer power monitors, portable or battery-powered equipment, automotive.

#### **FEATURES**

- \* +3V, +3.3V, and +5V power-supply voltages

- \* Full temperature rated

- \* Supply current: 5µA

- \* Available in configuration: push-pull RESET output

- \* 140ms minimum power-on reset pulse width

- \* Guaranteed reset to V<sub>CC</sub> = +1V

- \* Power supply transient Immunity

- \* Eliminating external components

- \* Manual reset input

#### ORDERING INFORMATION

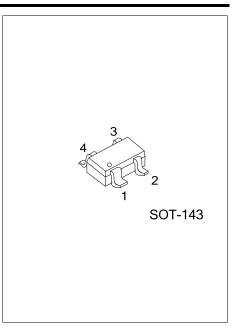

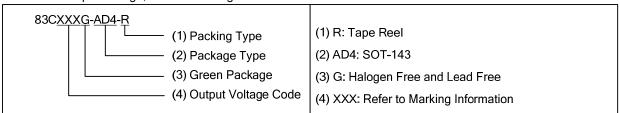

| Ordering Number | Package | Packing   |

|-----------------|---------|-----------|

| 83CXXXG-AD4-R   | SOT-143 | Tape Reel |

Note: XXX: Output Voltage, refer to Marking Information.

www.unisonic.com.tw 1 of 5

# ■ MARKING INFORMATION

| PACKAGE | VOLTAGE CODE         | MARKING                    |

|---------|----------------------|----------------------------|

| SOT-143 | B: 2.93V<br>C: 3.08V | 8XG<br>Voltage Code<br>1 2 |

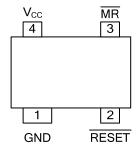

# ■ PIN CONFIGURATION

# ■ PIN DESCRIPTION

| PIN NO | PIN NAME        | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                              |

|--------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | GND             | Ground                                                                                                                                                                                                                                                                                                                                                                                   |

| 2      | RESET           | $\overline{\text{RESET}}$ output remains low while $V_{CC}$ is below the reset threshold, and for at least 140ms after $V_{CC}$ rises above the reset threshold.                                                                                                                                                                                                                         |

| 3      | MR              | Manual reset input. A logic low on $\overline{\text{MR}}$ asserts reset. Reset remains asserted as long as $\overline{\text{MR}}$ is low and for at least 140ms after $\overline{\text{MR}}$ returns high, This active-low input has an internal $20k\Omega$ pull-up resistor. It can be driven from a TTL or CMOS-logic line, or shorted to ground with a switch. Leave open if unused. |

| 4      | V <sub>CC</sub> | Supply voltage (+5V, +3.3V, +3.0V)                                                                                                                                                                                                                                                                                                                                                       |

# ABSOLUTE MAXIMUM RATING

| PARAMETER                                        |            | SYMBOL             | RATINGS                    | UNIT  |

|--------------------------------------------------|------------|--------------------|----------------------------|-------|

| Terminal Voltage (respect to GND)                |            | $V_{CC}$           | -0.3 ~ +6.0                | V     |

| RESET Voltage                                    | Push-Pull  | V <sub>RESET</sub> | $-0.3 \sim (V_{CC} + 0.3)$ | V     |

|                                                  | Open Drain | ▼RESET             | -0.3 ~ +6.0                | V     |

| Input Current                                    |            | I <sub>CC</sub>    | 20                         | mA    |

| Output Current (RESET)                           |            | I <sub>OUT</sub>   | 20                         | mA    |

| Power Dissipation (Ta =+70°C) Derated Above 70°C |            | В                  | 320                        | mW    |

|                                                  |            | P <sub>D</sub>     | 4                          | mW/°C |

| Operating Temperature                            |            | $T_{OPR}$          | -40~+105                   | ů     |

| Storage Temperature                              |            | T <sub>STG</sub>   | -65~+150                   | °C    |

Note: Absolute maximum ratings are those values beyond which the device could be permanently damaged. Absolute maximum ratings are stress ratings only and functional device operation is not implied.

# ■ ELECTRICAL CHARACTERISTICS

$(V_{CC}$  = full range,  $T_A$  =-40°C~+105°C. Typical values are at  $T_A$ =25°C, unless otherwise specified)

# 83C293 (2.93V) (V<sub>CC</sub>= 3.3V)

|                                | - /  |                 |                                                             |       |      |       |        |

|--------------------------------|------|-----------------|-------------------------------------------------------------|-------|------|-------|--------|

| PARAMETER                      |      | SYMBOL          | TEST CONDITIONS                                             | MIN   | TYP  | MAX   | UNIT   |

| V <sub>CC</sub> Range          |      | V <sub>CC</sub> | T <sub>A</sub> =0°C~+70°C                                   | 1.0   |      | 5.5   | V      |

|                                |      |                 | T <sub>A</sub> =-40°C~+105°C                                | 1.2   |      | 5.5   | V      |

| MR Input Threshold             |      | V <sub>IH</sub> | -V <sub>CC</sub> >V <sub>TH(MAX)</sub>                      | 1.98  |      |       | V      |

|                                |      | $V_{IL}$        |                                                             |       |      | 0.825 | V      |

| Reset Threshold                |      | $V_{TH}$        | T <sub>A</sub> =25°C                                        | 2.871 | 2.93 | 2.988 | V      |

| Supply Current                 |      | I <sub>CC</sub> | V <sub>CC</sub> <3.6V, T <sub>A</sub> =-40°C~+105°C         |       | 5    | 8     | μΑ     |

| RESET Output Current           | Low  | I <sub>OL</sub> | $V_{CC}=2.5V$ , $V_{\overline{RESET}}=0.5V$                 | 8     |      |       | mA     |

| (push-pull active low)         | High | I <sub>OH</sub> | $V_{CC}$ = 3.3V, $V_{\overline{RESET}}$ = 2.8V              | 3     |      |       | mA     |

| MR Pull-up Resistance          |      |                 |                                                             | 10    | 20   | 30    | kΩ     |

| Reset Threshold Tempco         |      |                 |                                                             |       | 70   |       | ppm/°C |

| V <sub>CC</sub> to Reset Delay |      |                 | V <sub>CC</sub> = V <sub>TH</sub> ~(V <sub>TH</sub> -100mV) |       | 15   |       |        |

| Reset Active Timeout Period    |      |                 | $V_{CC} = V_{TH(MAX)}$                                      | 140   | 310  | 520   | ms     |

| MR Minima Pulse Width t        |      | t <sub>MR</sub> |                                                             |       | 10   |       | μs     |

| MR Glitch Immunity (Note )     |      |                 |                                                             |       | 100  |       | ns     |

| MR to Reset Propagation Delay  |      | $t_{MD}$        |                                                             |       | 0.5  |       | μs     |

#### 83C308 (3.08V) (V<sub>CC</sub>=3.3V)

| 000000 (0.001) (1000 0.01             | · /  |                 |                                                     |       |      |       |        |

|---------------------------------------|------|-----------------|-----------------------------------------------------|-------|------|-------|--------|

| PARAMETER                             |      | SYMBOL          | TEST CONDITIONS                                     | MIN   | TYP  | MAX   | UNIT   |

| V <sub>CC</sub> Range                 |      | V <sub>CC</sub> | T <sub>A</sub> =0°C~+70°C                           | 1.0   |      | 5.5   | V      |

|                                       |      |                 | T <sub>A</sub> =-40°C~+105°C                        | 1.2   |      | 5.5   | V      |

| MR Input Threshold                    |      | $V_{IH}$        | V <sub>CC</sub> >V <sub>TH(MAX)</sub>               | 1.98  |      |       | V      |

|                                       |      | $V_{IL}$        |                                                     |       |      | 0.825 | V      |

| Reset Threshold                       |      | $V_{TH}$        | T <sub>A</sub> =25°C                                | 3.018 | 3.08 | 3.141 | V      |

| Supply Current                        |      | Icc             | V <sub>CC</sub> <3.6V, T <sub>A</sub> =-40°C~+105°C |       | 5    | 8     | μΑ     |

| RESET Output Current                  | Low  | $I_{OL}$        | $V_{CC}$ =2.5V, $V_{\overline{RESET}}$ = 0.5V       | 8     |      |       | mA     |

| (push-pull active low)                | High | I <sub>OH</sub> | $V_{CC}$ = 3.3V, $V_{\overline{RESET}}$ = 2.8V      | 3     |      |       | mA     |

| MR Pull-up Resistance                 |      |                 |                                                     | 10    | 20   | 30    | kΩ     |

| Reset Threshold Tempco                |      |                 |                                                     |       | 70   |       | ppm/°C |

| V <sub>CC</sub> to Reset Delay        |      |                 | $V_{CC} = V_{TH} \sim (V_{TH} - 100 \text{mV})$     |       | 15   |       |        |

| Reset Active Timeout Period           |      |                 | $V_{CC} = V_{TH(MAX)}$                              | 140   | 310  | 520   | ms     |

| MR Minima Pulse Width t <sub>MR</sub> |      | $t_{MR}$        |                                                     |       | 10   |       | μs     |

| MR Glitch Immunity (Note )            |      |                 |                                                     |       | 100  |       | ns     |

| MR to Reset Propagation Delay t       |      | $t_{MD}$        |                                                     |       | 0.5  |       | μs     |

Note: "Glitches" of 100ns or less typical values will not generate a reset pulse.

#### ■ DETAILED DESCRIPTION

The UTC **83CXXX** have a push-pull output stage. A microprocessor's ( $\mu$ P's) reset input initiates the microprocessor in a known state. The UTC **83CXXX** assert a reset signal as long as the V<sub>CC</sub> power supply voltage drops below a preset threshold. When V<sub>CC</sub> has risen over the reset threshold, the devices keep the signal for at least 140ms. They have a function of preventing code-execution errors during power-up, power-down, or brownout conditions by resetting.

See the manual reset input section if you want to see function that the manual reset input  $(\overline{MR})$  can initiate a reset.

#### **Manual Reset Input**

Many products based on microprocessor need manual reset characteristic, allowing them to initiate a reset. Reset keeps working while  $\overline{\text{MR}}$  is low, and when  $\overline{\text{MR}}$  returns high it is for the reset Active Timeout Period ( $t_{\text{RP}}$ ). TTL or CMOS-logic levels, or with open-drain / collector outputs both can drive  $\overline{\text{MR}}$  will be started by a logic low on manual reset .Because the input has a build-in 20k $\Omega$  pull-up resistor; it can be left open if it is not used. We can put a 0.1 $\mu$ F capacitor from  $\overline{\text{MR}}$  to ground if  $\overline{\text{MR}}$  is driven from long cables or the device is used in a noisy environment strengthening additional noise capacity. Connecting a normally open momentary switch from  $\overline{\text{MR}}$  to ground to create a manual-reset function, and external debounce circuitry is not required.

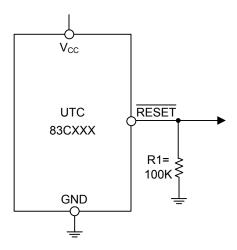

Figure 1. RESET Valid to V<sub>CC</sub> = Ground Circuit

#### APPLICATION INFORMATION

#### 1. Ensuring a Valid Reset Output Down to V<sub>CC</sub> = 0

The UTC 83CXXX  $\overline{\text{RESET}}$  output no more sinks current when  $V_{CC}$  drops below 1V—it becomes an open circuit. Therefore, high-impedance CMOS logic input connected to  $\overline{\text{RESET}}$  can drift to undetermined voltages. This presents no problem in most applications since most microprocessors and other circuitry can't be operated when  $V_{CC}$  is under 1V. In figure 1, however, in applications where  $\overline{\text{RESET}}$  must be valid down to 0V. In order to causes any stray leakage currents to flow to ground, adding a pull-down resistor to  $\overline{\text{RESET}}$ , that holding  $\overline{\text{RESET}}$  low. (R1's value is not critical and the value  $100k\Omega$  is large enough not to load  $\overline{\text{RESET}}$  and small enough to pull  $\overline{\text{RESET}}$  to ground).

#### 2. Benefits of Highly Accurate Reset Threshold

Most microprocessor supervisor ICs has reset threshold voltages between 5% and 10% below the value of nominal supply voltages. If using ICs rated at only the nominal supply ±5%, this leaves an uncertainty zone where the supply is between 5% and 10% low and where the reset may or may not be asserted.

The UTC 83C308 with high accuracy ensure that the reset is asserted closely to 5% limit and long before the supply has declined to 10% below nominal.

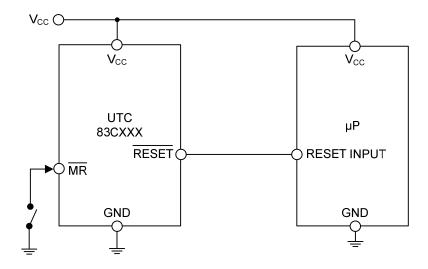

#### ■ TYPICAL APPLICATION CIRCUIT

UTC assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all UTC products described or contained herein. UTC products are not designed for use in life support appliances, devices or systems where malfunction of these products can be reasonably expected to result in personal injury. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner. The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice.