## ZVS RESONANT CONVERTER FOR CONSUMER APPLICATION USING L6598 IC

#### by Helen Ding

In this paper we study the details of the Multi-resonant Zero-current-switching converter which has smaller size and higher efficiency, and low noise operation. It will shown the design equations and demoboard results of a high-end TV power supply using ST L6598.

The small size, high efficiency, and low noise operation makes the half bridge resonant topology actrative for converters.

It will shown the design equations and demoboard test results of a high-end TV power supply using ST L6598.

## 1 CIRCUIT DESCRIPTION

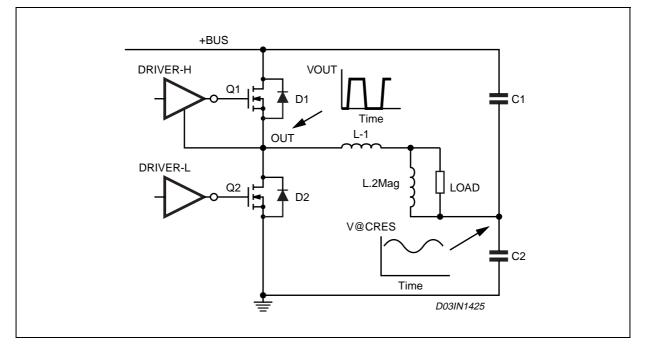

The simplified schematic and operating waveforms are shown in Fig.1 and Fig.2.

#### Figure 1. Simplified Schematic

This half-bridge converter consists of switching devices  $Q_1 \& Q_2$ , resonant inductor  $L_1$ , magnetizing inductor of transformer  $L_2$ , resonant capacitors  $C_1 \& C_2$ , transformer T, rectifier diodes  $D_1 \& D_2$ , output capacitor Cout.  $CQ_1 \& CQ_2$  are the parasitic capacitors of the  $Q_1 \& Q_2$ .  $D_{Q1} \& D_{Q2}$  are the parasitic reverse diodes of  $Q_1 \& Q_2$ .

Switching devices  $Q_1 \& Q_2$  repeat on and off alternately, and the on- and off-times are the same. 50% duty cycle.

September 2003

This circuit has three operation.

- 1. The operation of a resonant circuit between  $L_1$  and  $C_1+C_2$ . Which supplies power to the load.

- 2. The operation of a resonant circuit between  $L_1+L_2$  and  $C_1+C_2$ . Which does not supply power with the load.

- 3. The operation of a resonant circuit between  $C_{Q1} + C_{Q2}$ , L1+L2 and  $C_1+C_2$ . Which achieves the ZVS of the MOSFET.

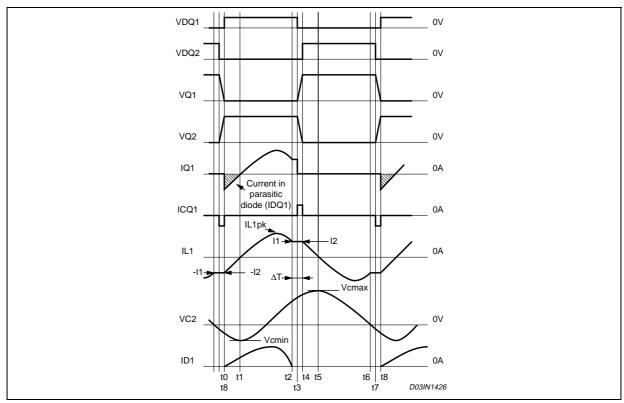

#### Figure 2. Operating Waveforms

## t0~t1:

In  $Q_1$  reverse current flows through parasitic diode  $D_{Q1}$ .  $Q_2$  is off.

The initial value of the resonant current between  $L_1$  and  $C_1+C_2$  at t0 is -l2, which coincide with the current in  $L_2$ . The current in  $L_2$  will increases at the rate of  $nV_{out}/L_2$  (n = N1/N2, N2 = N3). At t0  $C_{Q1}$  is discharged. The voltage becomes zero. ZVS is achieved. The voltage of  $C_2$  decreases further.  $C_2$  is discharging.

## t1~t2:

$Q_1$  is on and  $Q_2$  is off.

The resonant current flows through  $Q_1$  and in the opposite direction of t0~t1. The resonant current increases sinusoidally and reaches the maximum value then deceases till coincides with the current in  $L_2$  at t2. The difference between resonant current and current in  $L_2$  flows through the primary winding N1 of the transformer. Power is supplied to the load.

## t2~t3:

$Q_1$  is on and  $Q_2$  is off.

The current I1 in L<sub>1</sub> coincides with the current in L<sub>2</sub> at t2. No current flows through the secondary winding of the transformer. In this mode L<sub>1</sub>+L<sub>2</sub> and C<sub>1</sub>+C<sub>2</sub> resonate.

#### 2/13

## t3~t4:

$Q_1$  turns off at t3. Both  $Q_1$  and  $Q_2$  are off.

The charge stored in the parasitic capacitor  $C_{Q2}$  of  $Q_2$  is discharged by means of the resonant current between  $L_1+L_2$  and  $C_1+C_2$ . Whereas  $C_{Q1}$  is charged.

## t4~t5:

$Q_1$  is off. The resonant current flows through the parasitic diode  $D_{Q2}$  of  $Q_2$ . At t4  $C_{Q2}$  is discharged. The voltage becomes zero. ZVS is achieved. The voltage of  $C_2$  increases further.

## t5~t6:

Q<sub>1</sub> is off and Q<sub>2</sub> is on.

The resonant current flows through  $Q_2$  and in the opposite direction of t4~t5. The resonant current decreases sinusoidally and reaches the minimum value then increases till coincides with the current in  $L_2$  at t6. The difference between resonant current and current in  $L_2$  flows through the primary winding N1 of the transformer. Power is supplied to the load.

## t6~t7:

$Q_1$  is off and  $Q_2$  is on.

The current -I2 in L<sub>1</sub> coincides with the current in L<sub>2</sub> at t6. No current flows through the secondary winding of the transformer. In this mode L<sub>1</sub>+L<sub>2</sub> and C<sub>1</sub>+C<sub>2</sub> resonate.

## t7~t8:

$Q_2$  turns off.  $Q_1$  and  $Q_2$  are off.

The parasitic capacitor  $C_{Q2}$  of  $Q_2$  is charged by means of the resonant current between  $L_1+L_2$  and  $C_1+C_2$ . Whereas  $C_{Q1}$  is discharged.

Here the circuit returns to the first mode and the cycle is repeated.

A main advantage of this resonant converter is that there are no turn-on switching losses exist in the FET because its inverse diode carries current and the voltage across the MOSFET is zero before the MOSFET conducts forward current.

There are still turn-off switching losses. But it can be erased by placing small snubber capacitors directly across the FET devices. And no discharge resistors are needed. This was because the capacitor is not discharged by turning the FET on but rather is discharged by turning-off the opposite FET.

Also the switching losses due to Coss and Crss is eliminated by the same reason mentioned before in the lossless snubbers. The energy stored in any capacitance directly across the device is returned to the DC source by virtue of the opposite FET turning off.

## 2 L6598 DEVICE DESCRIPTION

The L6598 is an integrated circuit realised in BCD OFF-LINE technology. Able to drive POWER MOS or IGBT, in half bridge topology, the L6598 is provided with all the features (such as VCO, SOFT-START, OP-AMP and ENABLES) needed to implement and control properly a resonant SMPS with a minimum components count. Even though the device is able to withstand high voltage (up to 600V), it can operate at low voltage starting from its operative supply.

| Pin N° | Name                | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|--------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1      | C <sub>SS</sub>     | Soft Start Timing Capacitor. The capacitor CSS sets the soft start time, according to the relations: $T_{SS} = k_{SS}C_{SS}$ (typ. $k_{SS} = 0.15 \text{ s/}\mu\text{F}$ ). During $t_{SS}$ the capacitor is charged by means of a current which depends on $R_{fstart}$ value (i.e. on the difference between fstart and fmin). In this way TSS is always set at $k_{SS}C_{SS}$ (i.e. $T_{SS}$ depends only by $C_{SS}$ ). In steady state the voltage at pin 1 is 5V. |  |  |

| 2      | R <sub>fstart</sub> | Maximum Oscillation Frequency Setting. The resistance connected between this pin and ground sets the $f_{start}$ value, fixing the difference between $f_{start}$ and fmin ( $f_{start} > f_{min}$ ). The voltage at this pin is fixed at $V_{REF} = 2V$ , and so $R_{fstart}$ set the lfstart current equal to $V_{REF}/R_{fstart}$ . The minimum $R_{fstart}$ value which can be connected to this pin is 25 kOhm.                                                    |  |  |

| 3      | C <sub>f</sub>      | Oscillator Frequency Setting. The capacitor $C_F$ , along with to $R_{fstart}$ and $R_{fmin}$ , sets $f_{start}$ and fmin. In normal operation this pin shows a triangular wave.                                                                                                                                                                                                                                                                                        |  |  |

| 4      | R <sub>fmin</sub>   | Minimum Oscillation Frequency Setting. The resistance connected between this pin and ground sets the $f_{min}$ value. The voltage at this pin is fixed at $V_{REF} = 2V$ , and so $R_{fmin}$ set the lfmin current equal to $V_{REF}/R_{fmin}$ . The minimum $R_{fmin}$ value which can be connected to this pin is 25 kOhm.                                                                                                                                            |  |  |

| 5      | OP <sub>out</sub>   | Out of the operational amplifier. To implement a feedback control loop this pin can be connected to the R <sub>fmin</sub> pin by means an appropriate circuitry.                                                                                                                                                                                                                                                                                                        |  |  |

| 6      | OP <sub>on-</sub>   | Inverting Input of the operational amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 7      | OP <sub>on+</sub>   | Non Inverting Input of the operational amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| 8      | EN1                 | Enable 1. This pin (active high), forces the device in a latched shutdown state (like in the under voltage conditions). There are two ways to resume normal operation. The first is to reduce the supply voltage below the undervoltage threshold and then increase it again until the valid supply is recognized. The second is activating EN2 input. The enable 1 is especially designed for strong fault (e.g. in case of short circuit).                            |  |  |

| 9      | EN2                 | Enable 2. EN2 input (active high) restarts the start-up procedure (soft-start sequence).                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| 10     | GND                 | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| 11     | LVG                 | Low Side Driver Output. This pin must be connected to the low side power MOSFET gate of the half bridge. A resistor connected between this pin and the power MOS gate can be used to reduce the peak current.                                                                                                                                                                                                                                                           |  |  |

| 12     | Vs                  | Supply Voltage. This pin, connected to the supply filter capacitor, is internally clamped (15.6V typical).                                                                                                                                                                                                                                                                                                                                                              |  |  |

| 13     | N.C.                | Not Connected. It ensures the insulation between the high voltage section and the low voltage one.                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| 14     | OUT                 | High Side Driver Floating Reference. This pin must be connected close to the source of the high side power MOS or IGBT.                                                                                                                                                                                                                                                                                                                                                 |  |  |

| 15     | HVG                 | High Side Driver Output. This pin must be connected to the high side power MOSFET gate of the half bridge. A resistor connected between this pin and the power MOS gate can be used to reduce the peak current.                                                                                                                                                                                                                                                         |  |  |

| 16     | V <sub>boot</sub>   | Bootstrapped Supply Voltage. Between this pin and VS must be connected the bootstrap capac-<br>itor. A patented integrated circuitry replaces the high voltage external diode. This features is<br>achieved by means of a high voltage DMOS, synchronously driven with the low side power MOS-<br>FET.                                                                                                                                                                  |  |  |

57

#### Table 1. Device Pins Description

## 3 ANALYSIS AND DESIGN EQUATIONS

Following assumptions is for simplify the analysis.

1) All circuit components are ideal devices.

2) DT (Fig.2) is very short compared to the resonant time. DT = 0, and I1 = I2.

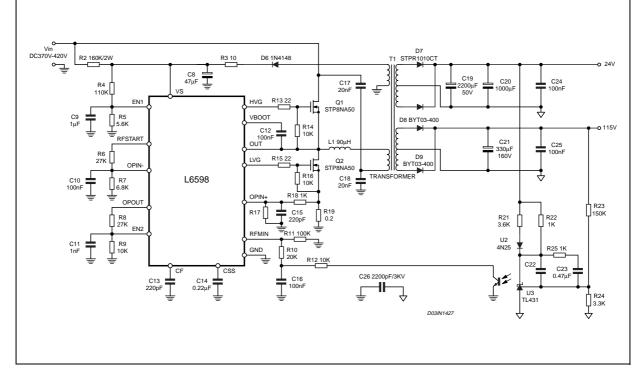

Fig.3 is the schematic of L6598 resonant converter demoboard.

## Figure 3. 180W Half-Bridge resonant with the L6598: electrical schematic

The spec. of the power supply. Input voltage: DC 370V ~ 420V (output of a PFC stage) Output voltage: 110V/1.2A , 24V/2A Output power : 180W

## 3.1 Resonant frequency and switching frequency

Before the design, we need to decide several operation frequencies of converter. That include the start switching frequency - Fstart, minimum switching frequency - Fmin and resonant frequency - Fr. In this application, we choose:

Fstart = 250KHz ( by design Rfstart of L6598) Fmin = 68KHz ( by design Rfmin of L6598) Fr = 84KHz ( by design L1, C17, C18)

To calculate Rfstart and Rfmin, using below equations:

$$Rfmin = \frac{1.41}{FminCf}$$

(1)

$$Rfstart = \frac{1.41}{(Fstart - Fmin)Cf}$$

(2)

5/13

Choose Cf = 220pF, then

Rfmin =

$$\frac{1.41}{68 \cdot 10^3 \cdot 220 \cdot 10^{-12}} = 94.2 \,\mathrm{k\Omega} \div 100 \,\mathrm{k\Omega}$$

Rfstart =  $\frac{1.41}{(250 - 68) \cdot 10^3 \cdot 220 \cdot 10^{-12}} = 32.5 \,\mathrm{k\Omega}$

Rfstart is 35.2Kohm, this is larger than the minimum value of Rfstart which is 25Kohm.

In this application, we use R6, R7 voltage divider to get a fixed voltage to Pin6 (OPin-) as the voltage of Pin2 (Rfstart) is fixed at Vref = 2V. At the same time Pin7(OPin+) connected to primary current sense resister. Voltage of Pin7 (Vopin+) will increase while output power increase. The output of the operational amplifier will be high when Vopin+ tends to be higher than Vopin-. Then another voltage divider R8, R9 will send this high voltage to Pin9 (EN2). L6598 will stop the normal operation and restart as long as EN2 is high. Thus over-current-protection is achieved.

If set R6 = 27Kohm, R7 = 6.8Kohm, then the input voltage for Pin6 is 0.4V.

Now, Rfstart = R6+R7 = 33.8Kohm

Rfmin = R11 = 100Kohm

Recalculated Fstart & Fmin. Fmin is 64KHz, Fstart is 254KHz.

The design for resonant components will be finished in the followed step.

## 3.2 Design transformer and resonant components

First select core size.

$$A_{P} = \left(\frac{11.1 \cdot Pin}{k \cdot \Delta B \cdot F}\right)^{1.31}$$

(3)

For half-bridge converter, k = 0.165 With Pout = 180W,  $\eta$  = 94%,  $\Delta B$  = 0.4T, Fmin = 64KHz, Calculated Ap = 0.402 cm<sup>4</sup>

Choose core: EC39, with Ae = 1.32cm2

Npmin =

$$\frac{\text{Vin(min)} \cdot 10^4}{2 \cdot \text{fsmin} \cdot \Delta B \cdot Ae}$$

(4)

Npmin =

$$\frac{370 \cdot 10}{2 \cdot 68 \cdot 10^3 \cdot 0.4 \cdot 1.32} = 51.5$$

n =  $\frac{N_p}{10} \ge \frac{V_{inmax}}{2}$

$$= \frac{N_{p}}{N_{s1}} \ge \frac{2}{V_{o1} + V_{F1}}$$

(5)

$$n \ge \frac{\frac{420}{2}}{110 + 1} = 1.9$$

$$Ns_2 = \frac{(V_{02} + V_{F2})N_{s1}}{V_{01} + V_{F1}}$$

We choose Np = 52T, n = 2 Then Ns<sub>110</sub> = 26T. This is 110V winding. The turns of 24V winding is 6. The turns of Vcc supply winding is 3.

Now design the resonant components. Set normalize output voltage is M = 0.95Set normalize output current is J = 0.2

$$Zo = \frac{\left(\frac{V_{inmax}}{2}\right)^2 \cdot J \cdot M}{Vo \cdot Io}$$

(6)

$$Zo = \frac{\left(\frac{420}{2}\right)^2 \cdot 0.2 \cdot 0.95}{(110 \cdot 1.2) + (24 \cdot 2)} = 46.55$$

$$Lr = \frac{Zo}{2\pi fr} = \frac{56.55}{2\pi \cdot 84 \cdot 10^3} = 88.2 \mu H$$

(7)

$$Cr = \frac{1}{2\pi fr \cdot Zo} = \frac{1}{2\pi \cdot 84 \cdot 10^3 \cdot 46.55} = 40.6nF$$

(8)

$\label{eq:cr} \begin{array}{l} Cr=C17+C18,\\ Choose\ C17=C18=20nF,\ then\ Cr=40nF\\ Recalculate\ Lr\ under\ Fr=84KHz.\ Lr=L1=90uH \end{array}$

Choose primary inductance L2 as 5 ~ 10 times the resonant inductance. L2 = 500uH

Now the resonant frequency of total circuit is

fo =

$$\frac{1}{2\pi\sqrt{(L2+L1)\cdot Cr}}$$

= 32.5kHz (9)

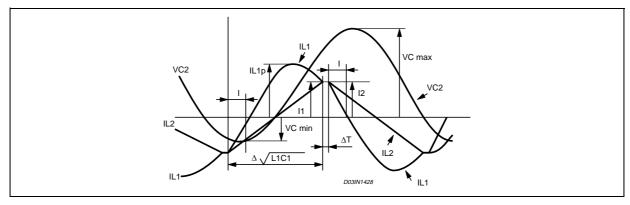

#### 3.3 conditions for resonance between L2 and resonant circuit (L1, C17+C18)

When the resonant between L2 and the resonant circuit starts, current IL2 varies from -I2 to +I1 during t2t1, and the voltage is nVout and constant. The operating waveforms are shown in Fig. 4

#### Figure 4. operating waveforms

Therefore.

$$nV_{out} = L_2 \cdot \frac{I_1 + I_2}{\frac{Tr}{2}}$$

(10)

$$T'r = \frac{Tr}{2} = \pi \sqrt{L1Cr}$$

(11)

When assumed  $I_1 = I_2$ , then

$$I_1 = \frac{nV_{out} \cdot T'r}{2L_2}$$

(12)

Calculated value of I1 is 1.32A.

#### 3.4 Maximum voltage Vcmax and minimum voltage Vcmin of resonant capacitor

The voltage of the resonant capacitor varies in accordance with the charge and discharge current in both the resonant circuits between L2 and C17+C18, and between L1+L2 and C17+C18.

The following equation shows the relation between the maximum value Vcmax and the minimum value Vcmin of the resonant capacitor voltage.

$$Vc max = Vc min + 2(Vin - nVout - Vc min) + \Delta Vc$$

(13)

nVout: primary voltage of transformer

$\Delta Vc:$  charge in value of resonant capacitor voltage in the resonant circuit between L1+L2 and C17+C18

Where

$$Vc max + Vc min = Vin$$

(14)

The Vcmax and Vcmin are derived from the relation with the output current. And the output current lout is:

$$I_{OUT} = \frac{n}{T'_r + \Delta T} \int_0^{T'r} (iL_1 - iL_2) dt$$

(15)

Where  $iL_1$  and  $iL_2$  are as follows:

$$iL_1 = (Vin - nVout - Vcmin) \sqrt{\frac{Cr}{L_1}} sin\left(\frac{t}{\sqrt{L_1Cr}} - \theta\right)$$

(16)

$$iL_{2} = \frac{I_{1} + I_{2}}{T'r}t - I_{2}$$

(17)

$\theta$  is the period of t0~t1. While assume  $\Delta T = 0$ , and I1 = I2

$$Iout = \frac{2n\sqrt{L_1Cr}}{T'r}\sqrt{(V_{in} - nVout - Vcmin)^2 \frac{Cr}{L_1} - l_1^2}$$

(18)

According to this equation, the minimum voltage Vcmin is obtained as follows:

$$Vcmin = Vin - nVout - \sqrt{\frac{\left(I_{out} \cdot \frac{T'_{r}}{2n\sqrt{L_{1} \cdot Cr}}\right)^{2} + I_{1}^{2}}{\left(\frac{Cr}{L_{1}}\right)}}$$

(19)

The Vcmax can be calculated according to equation (14). The maximum voltage applied to the resonant capacitor tends to increase as the output current increase.

Calculated Vcmax in this application is 310V at maximum output power.

#### 3.5 Peak value II1pk of resonant current

Resonant current iL1 is calculated according to equation (16). The peak value of iL1 is

$$IL_{1pk} = (Vin - nVout - Vcmin) \sqrt{\frac{Cr}{L_1}}$$

(20)

Calculated IL1pk is 1.9A in this application.

#### 3.6 Over current protection and over voltage protection

We set the over current protection point at  $I_{L1pk} = 2.1A$ . As the inverting input of operational amplifier is 0.4V, The calculated Rsense will be 0.4V/2.1A = 0.19ohm. Choose 0.2ohm/1W resistor as Rsense (R20). Then the voltage on R20 will be 0.42V at expected OCP point.

By choosing the suitable voltage divider R18 and R17, we can get the 0.4V voltage to OPin+.

In this application we choose R17 = 39Kohm , R18 = 1Kohm.

Over voltage protection is achieved by sense the supply voltage of L6598 --Vs. R4 and R5 is a voltage divider which connected to Pin8 (EN1). When the voltage of Pin8 is higher than the threshold 0.6V, it forces the device in a latched shut down state.

By choose R4 = 110Kohm and R5 = 5.6Kohm, the OVP is trigged at Vs = 12.4V. That is 10% higher than the normal operating voltage.

#### 4 EVALUATION RESULT OF DEMOBOARD

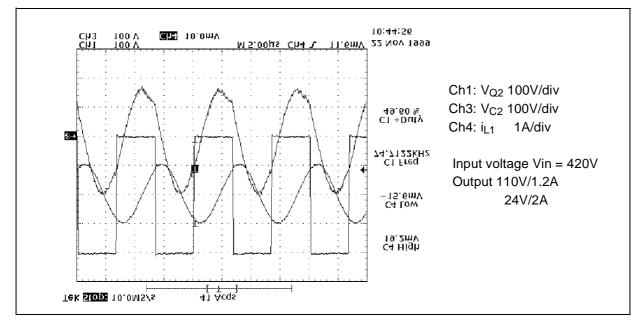

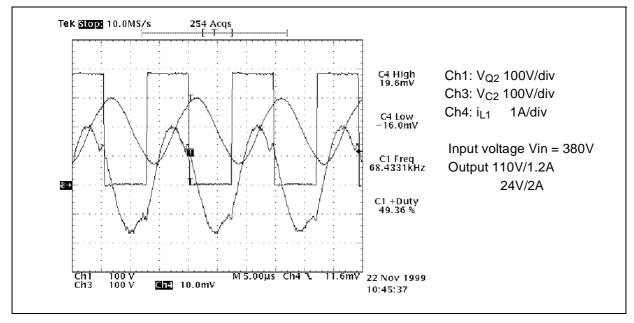

#### 4.1 Operating waveforms

See the operating waveform in Fig.5

The measured value : I1 is 1.4A, Vcmax is 300V, IL1pk is 1.9A. That is coincide with the calculated value.

## Figure 5. Operating Waveform

## Figure 6.

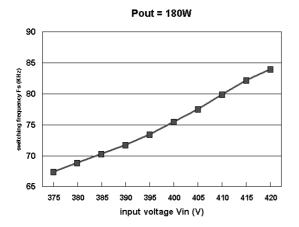

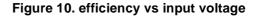

## 4.2 Switching frequency characteristics

## Figure 7. switching frequency vs input voltage

#### Figure 8. switching frequency vs output power

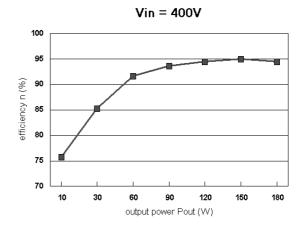

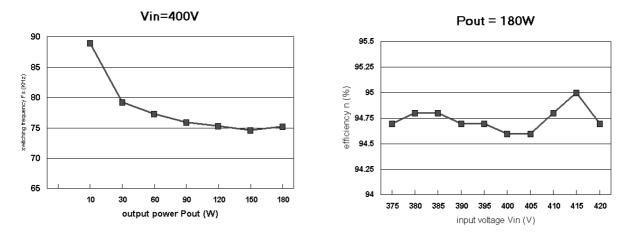

## Figure 9. efficiency vs output power

The maximum efficiency is 95% at maximum output power of 180W.

## 4.4 OCP and OVP

The power supply will automatically pass in restart procedure when the output power exceed a certain value. In experiment, set output current 1.8A to 110V & 2A to 24V, the voltage of pin 9 (EN2 of L6598) will be higher than 1V and the IC restarts the start-up sequence. Thus the OCP achieves. The maximum output power is slightly depend on the input voltage. In this demo board the maximum output power is around 240W.

The over-current-protection will be active as well when 24V or 110V is under short circuit condition.

The operating frequency tends to increase as the output load decrease. The maximum switching frequency is limited by (R10+R12)//R11. Using equation (1) we can calculate the Fmax value. It is 278KHz. When the maximum frequency is reached and the load reduced further, the output voltage will no longer be regulated and tends to increase. So does the Vs voltage of L6598. Once Vs rise to 12.2V, the over-voltage-protection will be triggered.

In the demo board, the tested value is  $V_s = 12.2V$  and  $V_{o1} = 134V$ ,  $V_{o2} = 29V$ .

So to keep the output voltage regulated, a minimum output power is request. The test result can be find in the following table.

| Input Voltage (DC)   | 370V                        | 420V                          |

|----------------------|-----------------------------|-------------------------------|

| Output minimum power | 4W<br>110V/30mA<br>24V/30mA | 9.5W<br>110V/80mA<br>24V/30mA |

| Switching frequency  | 70KHz                       | 240KHz                        |

| Input power          | 7.3W                        | 13W                           |

#### Table 2.

The maximum switching frequency can be designed to a higher value to reduce the minimum output power by reducing the value of (R10+R12). But the Fmax has a upper limitation given by L6598. It can not exceed 350KHz.

## 5 CONCLUSION

We could obtain high efficiency in this circuit. Because both ZVS, ZCS can be achieved of turn-on and ZVS can be achieved of turn-off.

The major drawback of this kind of converter is the line regulation is not good. So it is better to use the converter after a PFC circuit.

## 6 **REFERENCE**

[1] A High Efficiency 150W DC/DC Converter

Yasuhito Furukawa, Kouichi Morite, Taketoshi Yoshikawa

[2] A Comparison of Half-Bridge Resonant Converter Topologies

ROBERT L. STEIGERWALD,

IEEE Power Electronics Specialists Conference Record, 1987,135-144

- [3] L6598 datasheet and AN1673.

- [4] AN628 & AN996

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners

© 2003 STMicroelectronics - All rights reserved

#### STMicroelectronics GROUP OF COMPANIES

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States

www.st.com