# **OKI** semiconductor

# MSM6912

#### **PCM CHANNEL FILTER**

## **GENERAL DESCRIPTION**

The MSM6912 is a PCM channel filter LSI which is fabricated by OKI's low power consumption CMOS silicon gate technology.

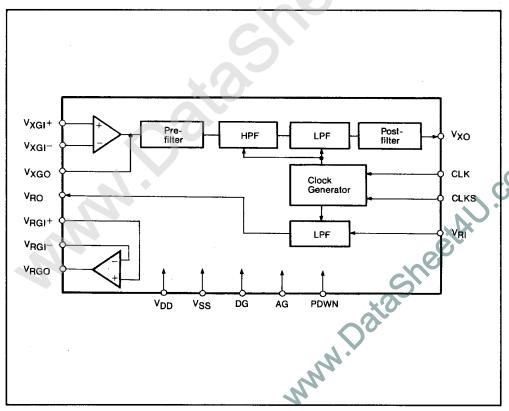

It consists of pre-filter, HPF, post filter and two LPF's.

#### **FEATURES**

- CCITT G.712 standard

- 50/60 Hz rejection filter on-chip

- SIN x/x compensation filter on-chip

- External gain adjustment, both transmit and receive filters

- Power-down mode available

- 128 KHz or 2048 KHz external clock for operation

- Power supply, ±5 V

- 16-pin ceramic DIP package

#### **BLOCK DIAGRAM**

# **PIN CONFIGURATION**

| V <sub>XGI</sub> + 1 | 16 V <sub>XO</sub> |

|----------------------|--------------------|

| V <sub>XGI</sub> - 2 | 15 AG              |

| Vxgo 3               | 14 CLKS            |

| V <sub>RO</sub> 4    | 13 PDWN            |

| V <sub>RGI</sub> + 5 | 12 CLK             |

| V <sub>RGI</sub> - 6 | 11 DG              |

| V <sub>RGO</sub> 7   | 10 V <sub>RI</sub> |

| v <sub>ss</sub> 8    | 9 V <sub>DD</sub>  |

|                      |                    |

# **PIN DESCRIPTION**

| Pin No. | Pin Name           | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |  |  |

|---------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| 1       | V <sub>XGI</sub> + | VXGI+ is the non-inverting input of the gain-setting Op Amp in the transmit filter section. The input analog signal is typically applied to this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| 2       | VxGI-              | $v_{\chi GI^-}$ is the inverting input of the gain-setting Op Amp in the transmit filter section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| 3       | VxGO               | $\begin{array}{c} V_{XGO} \text{ is connected to the output of the gain-setting Op Amp in the transmit filter section.} \\ \text{An appropriate voltage gain can be set as shown in Figure 1 below.} \\ \hline V_{XGI} + 1 \\ \hline RG \\ V_{XGI} - 2 \\ \hline W_{XGO} \\ \hline Figure 1 \\ \hline \text{As the transmit filter section has a gain of approx.} + 3 dB excluding this amplifier, a suitable level diagram has to be selected.} \\ \text{The DC offset voltage of } V_{XGO} \text{ becomes 50-Gv (mV) in the worst case.} \\ \text{The load resistance connected to } V_{XGO} \text{ should be greater than 10 K} \Omega. \\ \hline \end{array}$ |  |  |  |  |  |  |  |

| 4       | V <sub>RO</sub>    | $V_{RO}$ is the analog output of the receive filter. Because the output impedance is not so low, it is better to use the gain setting OP Amp as a output buffer. The resistive loads connected to $V_{RO}$ should be greater than 10 K $\Omega$ .                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

| 5       | V <sub>RGI</sub> + | V <sub>RGI</sub> + is the non-inverting input of the gain setting Op Amp in the receive filter section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| 6       | V <sub>RGI</sub> - | V <sub>RGI</sub> — is the inverting input of the gain setting Op Amp in the receive filter section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |  |

|         | Di- N    | Function                                                                                                                                                                                                                                                                                                                                  |

|---------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin No. | Pin Name | Function                                                                                                                                                                                                                                                                                                                                  |

| 7       | VRGO     | V <sub>RGO</sub> is the output of the gain setting Op Amp in the receive filter section. An appropriate voltage gain can be set as shown in Figure 2 and 3.                                                                                                                                                                               |

|         |          | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                     |

|         |          | $\begin{array}{c c} & V_{RGI} + \\ \hline & 5 & V_{RGI} + \\ \hline & 7 & V_{RGO} & \end{array}$ $\begin{array}{c c} & G_V = R_2/(R_1 + R_2) \\ & (R_1 + R_2), RL \geq 10 \text{ K}\Omega \end{array}$ Figure 3                                                                                                                           |

|         |          | Use Figure 2 for amplification and Figure 3 for attenuation. As the receive filter section has a gain of approx. 0 dB excluding this amplifier, a suitable level diagram has to be calculated. The DC offset voltage of VRGO becomes as follows in the worst case;  Figure 2 (200 + 50) · Gv = 250 · Gv (mV)  Figure 3 200 · Gv + 50 (mV) |

|         |          | The resistive loads connected to $V_{RGO}$ should be greater than 10 K $\Omega$ .                                                                                                                                                                                                                                                         |

| Pin No. | Pin Name        | Function                                                                                                                                                                                                                                                                                                 |                                                                                          |  |  |  |  |  |

|---------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--|--|--|--|--|

| 8       | V <sub>SS</sub> | VSS is the negative supply pin. The voltage supplied to this pin should be $-5V\pm5\%$ .                                                                                                                                                                                                                 |                                                                                          |  |  |  |  |  |

| 9       | V <sub>DD</sub> | VDD is the positive supply pin. T should be $+5V \pm 5\%$ .                                                                                                                                                                                                                                              | VDD is the positive supply pin. The voltage supplied to this pin should be $+5V\pm5\%$ . |  |  |  |  |  |

| 10      | V <sub>RI</sub> | VRI is the analog input to the receive filter. The receive signal is typically generated by the decoder section of a companding CODEC (ex. MSM6917AS). The receive filter provides the sin x/x correction over the passband.                                                                             |                                                                                          |  |  |  |  |  |

| 11      | DG              | This pin is connected to the digi                                                                                                                                                                                                                                                                        | This pin is connected to the digital system ground.                                      |  |  |  |  |  |

| 12      | CLK             | CLK is the digital clock signal input. Two clock frequency (128 KHz, 2,048 KHz) can be applied. The desired clock frequency is selected by the CLKS input. For proper operation, this clock should be tied to the receive clock of the CODEC.                                                            |                                                                                          |  |  |  |  |  |

| 13      | PDWN            | This control input enables MSM6912AS in the powerdown mode. Power down occurs when the signal of this input is pulled high.                                                                                                                                                                              |                                                                                          |  |  |  |  |  |

| 14      | CLKS            | This control pin is used to selec                                                                                                                                                                                                                                                                        | t the desired clock frequency.                                                           |  |  |  |  |  |

|         |                 | CLK (Pin 12)                                                                                                                                                                                                                                                                                             | CLKS (Pin 14)                                                                            |  |  |  |  |  |

|         |                 | 128 KHz                                                                                                                                                                                                                                                                                                  | Digital "L"                                                                              |  |  |  |  |  |

|         |                 | 2,048 KHz                                                                                                                                                                                                                                                                                                | Digital "H"                                                                              |  |  |  |  |  |

| 15      | AG              | This pin is connected to the                                                                                                                                                                                                                                                                             | analog system ground.                                                                    |  |  |  |  |  |

| 16      | Vxo             | $V_{XO}$ is the analog output of the transmit filter. The output voltage range is $\pm 2.5$ V and the output DC offset voltage is less than 200 mV. This output should be AC-coupled to the encoder section of the CODEC. The resistive load connected to $V_{XO}$ should be greater than 5 K $\Omega$ . |                                                                                          |  |  |  |  |  |

#### **ELECTRICAL CHARACTERISTICS**

## **Absolute Maximum Ratings**

| Parameter                | Symbol           | Conditions Ratings                      |                                             | Unit |

|--------------------------|------------------|-----------------------------------------|---------------------------------------------|------|

| Supply voltage           | V <sub>DD</sub>  |                                         | -0.3 ~ 7                                    | V    |

|                          | VSS              | T- 0500ith                              | +0.3 ~ -7                                   | _ v  |

| Digital input<br>voltage | V <sub>DIN</sub> | Ta=25°C with<br>respect to<br>DG and AG | −0.3 ~ V <sub>DD</sub> + 0.3                | v    |

| Analog input<br>voltage  | VAIN             |                                         | V <sub>SS</sub> −0.3 ~ V <sub>DD</sub> +0.3 | V    |

| Operating temperature    | TOP              |                                         | 0~70                                        | °C   |

| Storage<br>temperature   | TST              |                                         | <b>−55 ~ 150</b>                            | °C   |

#### **Recommended Operating Conditions**

| Parameter             | Symbol          | Conditions      | Min   | Тур | Max   | Unit |

|-----------------------|-----------------|-----------------|-------|-----|-------|------|

|                       | V <sub>DD</sub> | With respect to | 4.75  | 5   | 5.25  | ٧    |

| Supply voltage        | V <sub>SS</sub> | DG and AG       | -4.75 | -5  | -5.25 | V    |

| Operating temperature | ТОР             |                 | 0     |     | 70    | °C   |

#### **DC and Digital Interface Characteristics**

(VDD = +5V

$$\pm$$

5%, VSS = -5V  $\pm$  5%, Ta = 0  $\sim$  70°C)

|                |                  |                        |              | - 00   |     |      |

|----------------|------------------|------------------------|--------------|--------|-----|------|

| Parameter      | Symbol           | Conditions             |              | 11-3   |     |      |

| Parameter      | Зупроі           | Conditions             | Min          | Тур    | Max | Unit |

| Standby supply | IDDS             | DDWN - V               |              | 0.01   | 1   | mA   |

| current        | Isss             | PDWN = V <sub>IH</sub> | _            | · 0.01 | 1   | mA   |

| Operating      | IDDO             | PDWN = V <sub>IL</sub> | _            | 5      | 10  | mA   |

| supply current | Isso             | POWN - VIL             | _            | 5      | 10  | mA   |

| Input leakage  | I <sub>I</sub> L | V <sub>I</sub> = 0V    | <del>-</del> | -      | 10  | μΑ   |

| current        | ЧН               | V <sub>I</sub> = 5V    | _            | _      | 10  | μΑ   |

| Input voltage  | VIL              | With respect           | _            | _      | 8.0 | ν    |

|                | VIH              | to DG                  | 2.4          | _      | -   | ٧    |

# **Analog Interface, Gain Setting Amplifier and Transmit Filter**

$(V_{DD} = +5V \pm 5\%, V_{SS} = -5V \pm 5\%, Ta = 0 \sim 70^{\circ}C)$

|                        |                                            |                  |                                             | 1    | Limits |     |      |  |

|------------------------|--------------------------------------------|------------------|---------------------------------------------|------|--------|-----|------|--|

|                        | Parameter                                  | Symbol           | Conditions                                  |      |        | г   | Unit |  |

|                        |                                            |                  |                                             | Min  | Тур    | Max |      |  |

|                        | input leakage<br>current<br>VXGI+<br>VXGI- | ІВХ              | -3.2V≤V <sub>IN</sub> ≤+3.2V                | _    | _      | 10  | μΑ   |  |

|                        | Input<br>resistance<br>VXGI+<br>VXGI-      | RIX              |                                             | 2    | _      | _   | МΩ   |  |

| nplifier               | Input offset voltage                       | vosxı            | -3.2V≤V <sub>IN</sub> ≤+3.2V                | _    | _      | 50  | mV   |  |

| ttingan                | DC open loop<br>voltage gain               | Avx              |                                             | 66   | _      | _   | dB   |  |

| Gain setting amplifier | Open loop<br>unity gain<br>bandwidth       | fcx              |                                             | _    | 2      | _   | MHz  |  |

|                        | Load<br>capacitance                        | C <sub>LX1</sub> |                                             | _    | _      | 200 | PF   |  |

|                        | Load resistance                            | R <sub>LX1</sub> |                                             | 10   | _      | _   | ΚΩ   |  |

|                        | Output voltage swing                       | V <sub>OX1</sub> | RL ≥ 10KΩ                                   | ±2.5 | _      | _   | V    |  |

|                        | Output resistance                          | R <sub>OX1</sub> |                                             | _    | _      | 100 | Ω    |  |

|                        | Output offset voltage                      | Vosx             | VxGj+ = AG<br>Input OP Amp at<br>Unity gain | _    | -      | 200 | mV   |  |

| Filter                 | Load<br>capacitance                        | C <sub>LX2</sub> |                                             | _    | _      | 200 | PF   |  |

|                        | Load<br>resistance                         | R <sub>LX2</sub> |                                             | 5    | _      | _   | ΚΩ   |  |

|                        | Output voltage swing                       | V <sub>OX2</sub> | RL≥5KΩ                                      | ±2.5 | _      |     | v    |  |

# Analog Interface, Receive Filter and Gain Setting Amplifier

$(V_{DD} = +5V \pm 5\%, V_{SS} = -5V \pm 5\%, Ta = 0 \sim 70^{\circ}C)$

|                        | Davanatas                                | 0                 | 0                            |      | Limits |     |      |  |

|------------------------|------------------------------------------|-------------------|------------------------------|------|--------|-----|------|--|

|                        | Parameter                                | Symbol Conditions |                              | Min  | Тур    | Max | Unit |  |

|                        | Input leakage<br>current                 | I <sub>BR1</sub>  | -3.2V≤V <sub>IN</sub> ≤+3.2V | _    | _      | 10  | μΑ   |  |

|                        | Input<br>resistance                      | R <sub>IR1</sub>  |                              | 2    | _      | _   | МΩ   |  |

| <b>.</b>               | Output resistance                        | R <sub>OR1</sub>  |                              | -    | _      | 200 | Ω    |  |

| Filter                 | Output offset voltage                    | Vosa              | V <sub>RI</sub> = AG         | _    | _      | 200 | mV   |  |

|                        | Load<br>capacitance                      | C <sub>LR1</sub>  |                              | _    | -      | 200 | PF   |  |

|                        | Load<br>resistance                       | R <sub>LR1</sub>  |                              | 10   | _      | _   | κΩ   |  |

|                        | Output voltage swing                     | V <sub>OR1</sub>  | R <sub>L</sub> ≥10KΩ         | ±2.5 | -      | _   | ٧    |  |

|                        | Input leakage<br>current<br>VRGI+, VRGI- | l <sub>BR2</sub>  | -3.2V≤V <sub>IN</sub> ≤+3.2V |      | -      | 10  | μΑ   |  |

| plifier                | Input<br>resistance<br>VRGI+, VRGI-      | R <sub>IR2</sub>  |                              | 2    | _      | _   | МΩ   |  |

| Gain setting amplifier | Input offset voltage                     | Vosri             | -3.2V≤V <sub>IN</sub> ≤+3.2V | _    | _      | 50  | mV   |  |

| ain set                | DC open loop<br>voltage gain             | Avr               |                              | 66   | _      | _   | dВ   |  |

| Ö                      | Open loop<br>unity gain<br>bandwidth     | fCR.              |                              | _    | 2      | _   | MHz  |  |

|                        | Output resistance                        | ROR2              | At unity gain                | _    | -      | 20  | Ω    |  |

|                        | Load<br>capacitance                      | C <sub>LR2</sub>  |                              | _    | _      | 200 | PF   |  |

|                        | Load<br>resistance                       | R <sub>LR2</sub>  |                              | 10   | _      | _   | ΚΩ   |  |

|                        | Output voltage swing                     | V <sub>OR2</sub>  | RL≥10KΩ                      | ±2.5 | _      | _   | v    |  |

# **Transmit Filter Transfer Characteristics**

$(V_{DD} = +5V \pm 5\%, V_{SS} = -5V \pm 5\%, Ta = 0 \sim 70$ °C)

|                                       |                           |                  | (TDD ) OT                                   | -     | 100    |        |      |        |

|---------------------------------------|---------------------------|------------------|---------------------------------------------|-------|--------|--------|------|--------|

|                                       | Parameter Symbol          |                  | Conditions                                  |       | Limits |        |      |        |

|                                       |                           |                  |                                             | Amp   | Min    | Тур    | Max  |        |

| Absol<br>gain (9                      | ute passband<br>900 Hz)   | G <sub>AX</sub>  |                                             |       | 2.8    | 3.0    | 3.2  |        |

|                                       | Below 60 Hz               |                  | Input = 0 dBmo $-1.25$ Vrms                 | _     | _      | -20    |      |        |

| GAX)                                  | 300~3000 Hz               |                  | Output                                      |       | -0.25  | _      | +0.1 | dВ     |

| Relative gain (to GAX)                | 3300 Hz                   | G <sub>RX</sub>  | = + 3 dBmo<br>-1.77 Vrms                    |       | -0.35  | _      | +0.1 |        |

|                                       | 3400 Hz                   |                  | -1.77 Villis                                | 0 dB  | -0.85  | _      | +0.1 |        |

|                                       | 4000 Hz                   |                  |                                             |       | _      | _      | -14  | ]      |

|                                       | 4600 Hz and<br>above      |                  |                                             |       | _      | -      | -28  |        |

|                                       | variation with<br>erature | G <sub>AXT</sub> | Input = 0 dBmo<br>900 Hz                    |       | _      | 0.0005 | _    | dB/°C  |

| Gain v<br>suppli                      | variation with<br>es      | G <sub>AXS</sub> | Input = 0 dBmo<br>900 Hz<br>Supplies: ±5%   |       | _      | 0.05   | _    | dB/V   |

| Cross<br>to Trai                      | talk, Receive<br>nsmit    | CTRX             | *1                                          |       |        | -      | -60  | dB     |

| Total (                               | C message noise<br>out    | N <sub>CX1</sub> |                                             |       | -      | 8      | _    |        |

| Total (                               | C message noise<br>out    | N <sub>CX2</sub> |                                             | 20 dB | _      | 10     | -    | dBrnco |

| Differe<br>delay                      | ential envelope           | DDX              | 0.9 ~ 2.6 KHz                               | 0 dB  | _      | _      | 60   |        |

| Absolu                                | Absolute delay            |                  | 900 Hz                                      |       | _      | 200    | _    | μS     |

| Single frequency distortion products  |                           | D <sub>P</sub> X | V <sub>XO</sub> = +3 dBmo<br>900 Hz         | 20 dB | _      | -      | -45  |        |

| Positive power supply rejection ratio |                           | PSRR1            | V <sub>XO</sub> , 900 Hz<br>V <sub>DD</sub> | 0.15  | 25     | 30     |      | dB     |

|                                       | ive power<br>y rejection  | PSRR2            | V <sub>XO</sub> , 900 Hz<br>V <sub>SS</sub> | OdB   | 23     | 28     | _    |        |

<sup>\*1</sup>  $V_{RI} = 0 dBmo, 900 Hz$

#### **Receive Filter Transfer Characteristics**

$(V_{DD} = +5V \pm 5\%, V_{SS} = -5V \pm 5\%, Ta = 0 \sim 70$ °C)

|                                       |                          |                  |                                              | •    | 00     |        | -    | ,           |

|---------------------------------------|--------------------------|------------------|----------------------------------------------|------|--------|--------|------|-------------|

|                                       | Parameter                | Symbol           | Conditions                                   |      | Limits |        |      |             |

|                                       | raiametei                | Symbol           | Conditions                                   | Amp  | Min    | Тур    | Max  | Unit        |

|                                       | ute passband<br>900 Hz)  | GAR              | Input = 0 dBmo<br>= 1.25 Vrms                |      | -0.25  | -0.1   | 0    |             |

| Relative gain (to GAR)                | Below 300 Hz             |                  | Output<br>= +3dBmo                           |      | -0.25  | _      | +0.1 |             |

|                                       | 300~3000 Hz              |                  | = +3 dBmo<br>= 1.77 Vrms                     |      | -0.25  | _      | +0.1 | dB          |

|                                       | 3300 Hz                  | G <sub>RR</sub>  | With sin x/x                                 |      | -0.35  | _      | +0.1 |             |

|                                       | 3400 Hz                  |                  | correction<br>where x                        | 0 dB | -0.85  | _      | +0.1 |             |

|                                       | 4000 Hz                  |                  | $= \pi f/8000$                               |      | _      | _      | -14  | 1           |

|                                       | 4600 Hz and<br>above     |                  |                                              |      | _      | _      | -28  |             |

| Gain v<br>tempe                       | ariation with<br>rature  | G <sub>ART</sub> | Input = 0 dBmo<br>900 Hz                     |      | _      | 0.0005 | _    | dB/°C       |

| Gain v<br>suppli                      | ariation with<br>es      | G <sub>AXS</sub> | Input = 0 dBmo<br>900 Hz<br>Supplies: ±5%    |      | _      | 0.05   | -    | dB/V        |

| Cross<br>to rece                      | talk, transmit<br>elve   | CTXR             | *1                                           |      | _      | _      | -60  | dB          |

| Total (<br>at out                     | C message noise<br>out   | NCR              |                                              |      | _      | 7      | _    | dBrnco      |

| Differe<br>delay                      | ential envelope          | DDR              | 0.9 ~ 2.6 KHz                                |      | -      | -      | 120  | μS          |

| Absolute delay                        |                          | DAR              | 900 Hz                                       |      | _      | 120    | _    |             |

| Single frequency distortion products  |                          | DPR              | V <sub>RGO</sub> = +3 dBmo<br>900 Hz *2      |      | _      | _      | -50  |             |

| Positive power supply rejection ratio |                          | PSRR3            | V <sub>RGO</sub> , 900 Hz<br>V <sub>DD</sub> | †    | 30     | 35     | _    | dB          |

|                                       | ive power<br>y rejection | PSRR4            | VRGO, 900 Hz<br>VSS                          |      | 30     | 35     | -    |             |

|                                       |                          | 1                | <del></del>                                  |      | J      | 1      | L    | <del></del> |

<sup>\*1</sup>  $V_{XO} = +3 \text{ dBmo}, 900 \text{ Hz}$  $V_{RI} = AG$

<sup>\*2</sup> Removing the component of 128 KHz