19708

# 8-, 10-, 12-Bit Video Speed ANALOG O-, 10-, 12-DIL VIUCO SPECU DEVICES Current and Voltage Out, D/A Converters

**FEATURES** Current Settling Times to 15ns ±1.5V Compliance Voltage Settling Times to 100ns (MDH) Monotonicity Guaranteed Over Temperature High Output Currents - 15mA -30°C to +85°C Operating Range **Industry Standard Pin Outs** 20V, p-p Out (MDH) TTL or ECL Logic

APPLICATIONS Vector Displays Vaveform Generation Automatic Test Equipmen TV Picture Reconstruction

This broad family of digital to-analog converte resents the "state of the art" in modular, high speed, vo output devices. The family consists of a total of 11 devices i 4 series (MDS, MDSE, MDSL and MDH) that allow the user to make engineering trade-offs between resolution, speed, output and logic type. The first 3 are high compliance current output units which make possible linear output swings greater than ±1.5V. The voltage output MDH series contain a fast settling hybrid operational amplifier which provides ±10V output at ±50mA. To simplify selection these major specifications are summarized in Table 1.

| MODEL BITS |                      | FULL SCALE<br>OUTPUT                | FULL SCALE SETTLING TIME | INPUT<br>LOGIC |  |  |  |

|------------|----------------------|-------------------------------------|--------------------------|----------------|--|--|--|

|            |                      | (Fastest Settling High Current Out) |                          |                |  |  |  |

| MDS-0815   | 8                    | 15mA                                | 15ns to 0.4% FS          | TTL            |  |  |  |

| MDS-1020   | 10                   | 15mA                                | 20ns to 0.1% FS          | TTL            |  |  |  |

| MDS-1240   | 12                   | 15mA                                | 40ns to 0.025% FS        | TTL            |  |  |  |

|            | (MDS with ECL Logic) |                                     |                          |                |  |  |  |

| MDS-0815E  | 8                    | 15mA                                | 15ns to 0.4% FS          | ECL            |  |  |  |

| MDS-1020E  | 10                   | 15mA                                | 20ns to 0.1% FS          | ECL            |  |  |  |

|            |                      | (Low Cur                            | rent MDS)                |                |  |  |  |

| MDSL-0825  | 8                    | 5mA                                 | 25ns to 0.1%             | TTL            |  |  |  |

| MDSL-1035  | 10                   | 5mA                                 | 25ns to 0.1%             | TTL            |  |  |  |

| MDSL-1250  | 12                   | 5mA                                 | 50ns to 0.025%           | TTL            |  |  |  |

|            |                      | (Voltage                            | Out MDSL)                |                |  |  |  |

| MDH-0870   | 8                    | 10V/50mA                            | 150ns to 0.4%            | TTL            |  |  |  |

| MDH-1001   | 10                   | 10V/50mA                            | 200ns to 0.1%            | TTL            |  |  |  |

| MDH-1202   | 12                   | 10V/50mA                            | 500ns to 0.025%          | TTL            |  |  |  |

|            |                      |                                     |                          |                |  |  |  |

Table 1.

ultra-high speed operation. In fact, it is the fastest 12-A available, settling to 0.025% in 40ns. Hybrid construceliminates the thermal lag problem inherent in 12-bit s constructed with discrete components. This in turn ins that the accuracy is maintained over the total frequency range of operation yielding superior results for frequency do main applications

The MDS-1240 is particularly well suited for CRT display plications because of its unsurpassed speed and drive capabilities. The high output current (15mA) allows the use of low impedance loads so that settling times remain short - even with higher output voltage levels. The ability to drive load capacitance is at least 3 times that of other 12-bit D/A's thus providing capability to drive a terminated transmission line directly. The MDS-815 and MDS-1020 provide similar performance at 8 and 10 bits, while the MDS-E units provide it with ECL logic. MDSL-0825, MDSL-1035 and MDSL-1250 also utilize this reliable hybrid construction. The use of laser trimmed resistor networks within the D/A's not only eliminates thermal time lag errors but provide the linearity tempco of 2ppm/°C; guaranteeing monotonic operation over the extended temperature range of -30°C to +85°C. The power dissipation of the MDSL series is one-half that of competitive D/A's, but a full 5mA output current is maintained. This allows driving transmission lines or other low impedance loads directly.

(continued on page 195S)

### SPEED WITH PRECISION

Analog Devices' model MDS-1240 is the first D/A converter available with highly reliable, internal hybrid construction to

# **SPECIFICATIONS**

(typical @ +25°C unless otherwise specified)

|                                                                         |               | CURF            | RENT OUTPU                    | Т               | CURRENT OF                   |             |

|-------------------------------------------------------------------------|---------------|-----------------|-------------------------------|-----------------|------------------------------|-------------|

| MODEL                                                                   | UNITS         | 0815            | MDS<br>1020                   | 1240            | MDS-E (EC                    | 1020        |

| RESOLUTION                                                              | Bits          | 8               | 10                            | 12              | 8                            | 10          |

| LSB (Weight)                                                            | μA            | 58.6            | 14.6                          | 3.66            | 58.6                         | 14.6        |

| ACCURACY                                                                | μΛ            | 36.0            | 14.0                          | 3.00            | 38.0                         | 14.0        |

| Initial (Adjust to 0)                                                   | ±%FS          | 0.2             | 0.05                          | 0.012           | 0.2                          | 0.05        |

| Linearity (Integral)                                                    | LSB max       | ±1/2            | *                             | *               | *                            | *           |

| Monotonicity                                                            |               | 1               | Over Operating                | Temp Range      |                              |             |

| Zero Offset (Adjust to 0)                                               |               | 15nA max        | *                             |                 | *                            | *           |

| TEMPERATURE COEFFICIENTS                                                |               |                 |                               |                 |                              |             |

| Linearity                                                               | ppm/°C        | 5               | *                             | 2               | *                            | 2           |

| Gain                                                                    | ppm/°C        | 30              | *                             | 20              | *                            | *           |

| Offset (Bipolar)                                                        | ppm/°C        | 15              |                               |                 |                              |             |

| STABILITY WITH TIME                                                     | ±%/yr max     | 0.5             | •                             | *               | *                            | *           |

| ATA INPUTS                                                              |               |                 |                               |                 |                              |             |

| Logic Compatability Logic Voltage Levels                                |               | TTL             | -                             | •               | ECL                          | ECL         |

| Bit On Logic '1"                                                        | V             | +2 to +5.0      |                               |                 | -0.9                         | -0.9        |

| Bit Off Logic "O"                                                       | V             | 0 to +0.4       |                               |                 | -1.7                         | -1.7        |

| Logic Current (Each Bit)                                                | 7)            |                 |                               |                 |                              |             |

| Bit On Logic "1"                                                        | μA            | €50             | * -                           | *               | *                            | *           |

| Bit Off Logic "b"                                                       | mA            | 1-9             | \* \                          | -5 max          | *                            | *           |

| MSB                                                                     | mA )          | N/A             | I colon                       | -10 max         | L:                           |             |

| Coding                                                                  | ノノし           | Offset Ripers   | ary (BIN) for<br>(OBN) for Bi | Unipolar,       |                              |             |

| DUTPUT                                                                  | $\overline{}$ | Dirisct Billary | JOBA, INC. BI                 | porar           | $\mathcal{I}_{\mathcal{L}}$  |             |

| Current Range                                                           | \             | $\setminus$ /   | <i>'    </i>                  |                 | $\vdash$                     | <u>~]</u> [ |

| Unipolar                                                                | mA            | 0 to +15        | */                            | _ • / /         | 0 to -15                     | 0 to -15    |

| Bipolar                                                                 | mA            | ±7.5            | *                             | 716             | *                            | 1 * 1       |

| Impedance (See Figure 3)                                                | Ω             | 165             | *                             | 200±1%          | <u></u>                      | *           |

| Compliance (MDH V <sub>OUT</sub> )                                      | V             | +1.5, -2        | *                             |                 | J-1.5, +2                    | -1.5, +2    |

| Load Resistance for V <sub>OUT</sub> (See Figure 5)                     | 0             |                 |                               | 100             | $  \cdot  $                  | . / [       |

| 0 to +1V<br>±1V                                                         | $\Omega$      | 112<br>4.32k    |                               | 100<br>750      |                              | ·           |

| NTERNAL REFERENCE VOLTAGE OUT                                           | V             | N/A             | *                             | -6.2 ±5%        |                              |             |

| SETTLING TIME <sup>2</sup>                                              | · ·           | IN/A            |                               | -0.2 ± 3 %      |                              |             |

| Current                                                                 | ns to %.      | 15 to 0.4       | 20 to 0.10                    | 20 to 0.1       |                              | 20 to 0.10  |

|                                                                         | 113 (0 /0/    | 100,4           | 20 10 0,10                    | 40 to 0.025     |                              | 20 (0 0.10  |

| Unipolar Voltage (R <sub>L</sub> = $300\Omega \parallel 10 \text{pF}$ ) | ns to %       |                 |                               |                 |                              |             |

| Bipolar Voltage (R <sub>L</sub> = 2325 $\Omega$   10pF)                 | ns to %       |                 |                               | 2               |                              |             |

| OUTED DESCRIPTION                                                       |               |                 |                               |                 |                              |             |

| POWER REQUIREMENTS                                                      | V             | +11 +17         | *                             | +14.5           |                              |             |

| Range<br>Current at Nominal +V                                          | MA max        | ±11 to ±16      | 120                           | ±14.5 to ±16.5  | *                            | 120         |

| Current at Nominal -V                                                   | mA max        | 15              | *                             | 20              | *                            | *           |

| OWER SUPPLY REJECTION RATIO                                             | %/V           | 0.04            | *                             |                 | *                            | *           |

| +15V                                                                    | %/V           | 0.04            |                               | -0.0001         |                              |             |

| -15V (Bipolar)                                                          | %/V           |                 |                               | -0.002          |                              |             |

| -15V (Unipolar)                                                         | %/V           |                 |                               | -0.2            | 118-85, pps.55p-6-890.55pa-7 |             |

| EMPERATURE RANGE                                                        |               |                 |                               |                 |                              |             |

| Operating                                                               | °C            | -20 to +75      | •                             | -30 to +85      | •                            |             |

| Storage                                                                 | °C            | -55 to +85      | *                             | -55 to +125     | *                            | *           |

| CASE                                                                    |               | Diallyl Phtha   | late per MIL-M                | i-14 Type SDG-F | *                            | *           |

| RICE                                                                    |               |                 |                               |                 |                              |             |

| (1-4)                                                                   | \$            | 115             | 137                           | 149             | 129                          | 149         |

<sup>\*</sup>Specifications same as MDS-0815.

NOTES:

$^3$  0 to +5V Out  $^4$  0 to +10V Out  $^5$  ±5V Out  $^8$  See Figures 15 and 16 for test circuits.

Specifications subject to change without notice.

<sup>&</sup>lt;sup>1</sup> 1ppm/°C for current output. Op amp is  $50\mu V$ /°C. (See tables in Figures 15, 16 and 17, for overall TC in various configurations.)

<sup>2</sup> For Full Scale Step.

| CURF          | RENT OUTPUT   | r             |                             | VOLTAGE OUT<br>MDH        |                           |

|---------------|---------------|---------------|-----------------------------|---------------------------|---------------------------|

| 0825          | 1035          | 1250          | 0870                        | 1001                      | 1202                      |

| 3             | 10            | 12            | 8                           | 10                        | 12                        |

| 19.6          | 4.88          | 1.22          | De                          | pends on V <sub>OUT</sub> |                           |

| 0.2           | 0.05          | 0.012         | 0.2                         | 0.05                      | 0.012                     |

| *             |               | *             | *                           | *                         | *                         |

| *             | *             | *             | 10mV                        | 10mV                      | 10mV                      |

| 2             | 2             | 2             | 2                           | 2                         | 2                         |

| 20            | 20            | 20            | 20<br>See                   | 20<br>Note 1              | 20                        |

| *             | *             | *             | *                           | *                         | *                         |

|               | *             |               | *                           |                           | *                         |

| $\bigcirc$    |               | *             |                             |                           | *                         |

| *             | )* / <u> </u> |               | *                           | *                         | *                         |

|               | / · /         | ) (ر          | $\supset$                   | *                         | *                         |

| 1.6           | 1.6           | *1.6          | -1.6                        | -1.0                      | -1.6                      |

|               | <u></u>       |               | $\langle \cdot \rangle / /$ | : ) / /                   | 1 ,                       |

|               |               |               | 2)((                        |                           | 1 1                       |

| 0 to +5       | 0 to +5       | 0 to +5       | ±50 max                     | ±50 max                   | ±50 max                   |

| ±2.5          | ±2.5          | ±2.5          | ±50 max                     | ±50 max                   | ±50 max                   |

| 600 ±1%       | 600 ±1%       | 600 ±1%       | 0.1 max                     | 0.1 max<br>±10            | 0.1 max<br>±10            |

|               |               |               | ±10                         |                           |                           |

| 300<br>2.325k | 300<br>2.325k | 300<br>2.325k | N/A<br>N/A                  | N/A<br>N/A                | N/A<br>N/A                |

| -6.2 ±5%      | -6.2 ±5%      | -6.2 ±5%      | -6.2 ±5%                    | -6.2 ±5%                  | -6.2 ±5%                  |

| 25 to 0,1     | 25 to 0.1     | 50 to 0.25    | 15 to 0.2                   | 25 to 0.10                | 50 to 0.25                |

| 45 to 0.4     | 70 to 0.1     | 70 to 0.1     | 70 to 0.4 <sup>3</sup>      | 100 to 0.1 <sup>3</sup>   | 200 to 0.025 <sup>3</sup> |

| 70 to 0.1     | 80 to 0.05    | 90 to 0.025   | 150 to 0.44                 | 200 to 0.14               | 400 to 0.0254             |

| 75 to 0.4     | 100 to 0.1    | 100 to 0.1    | 100 to 0.4 <sup>5</sup>     | 130 to 0.1 <sup>5</sup>   | 250 to 0.025 <sup>5</sup> |

| 100 to 0.1    | 110 to 0.05   | 125 to 0.025  |                             |                           |                           |

| ±12 to ±15    | ±12 to ±15    | ±12 to ±15    | ±14.5 to ±16.5              | ±14 5 to ±16.5            |                           |

| 26            | 26            | 26            | 50                          | 50                        | 50                        |

| 16            | 16            | 16            | 35                          | 35                        | 35                        |

| 0.0001        | 0.0001        | 0,0001        | 0.003                       | 0.003                     | 0.003                     |

| 0.001         | 0.001         | 0.001         | 0.01                        | 0.01                      | 0.01                      |

| 0.2           | 0.15          | 0.15          | 0.15                        | 0.15                      | 0.15                      |

| -30 to +85    | -30 to +85    | -30 to +85    | -30 to +85                  | -30 to +85                | -30 to +85                |

| -55 to +125   |               | -55 to +125   | -55 to +125                 | -55 to +125               | -55 to +125               |

| *             | •             | *             | *                           | *                         | *                         |

| 112           | 119           | 129           | 204                         | 214                       | 224                       |

|               | /             |               |                             |                           |                           |

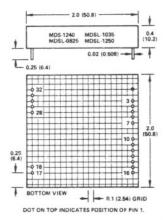

### MDS-0815, 0815E, 1020, 1020E OUTLINE DIMENSIONS

Dimensions shown in inches and (mm).

##

### MDS-1240, MDSL-0825, 1035, 1250 OUTLINE DIMENSIONS

Dimensions shown in inches and (mm).

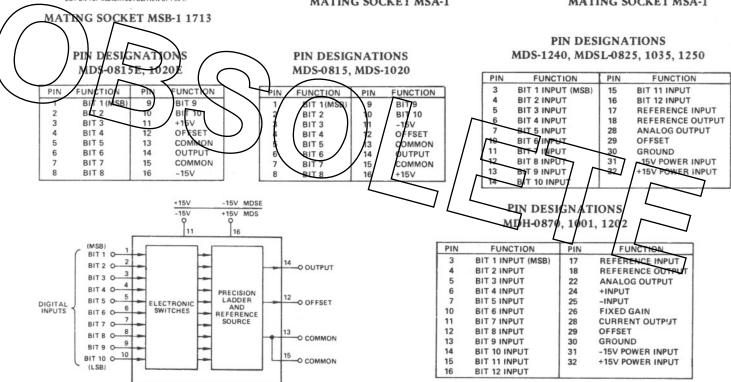

## MATING SOCKET MSA-1

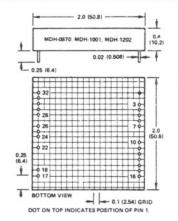

## MDH-0870, 1001, 1202 OUTLINE DIMENSIONS

Dimensions shown in inches and (mm).

### MATING SOCKET MSA-1

MDS and MDSE Block Diagram

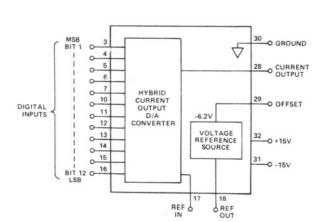

MDS-1240 and MDSL Series Block Diagram Page 4 of 8

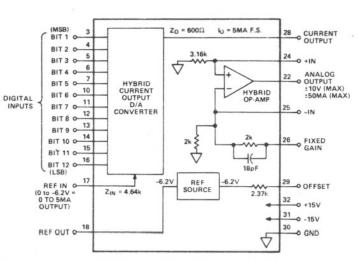

MDH Series Block Diagram

### MDH SERIES APPLICATIONS

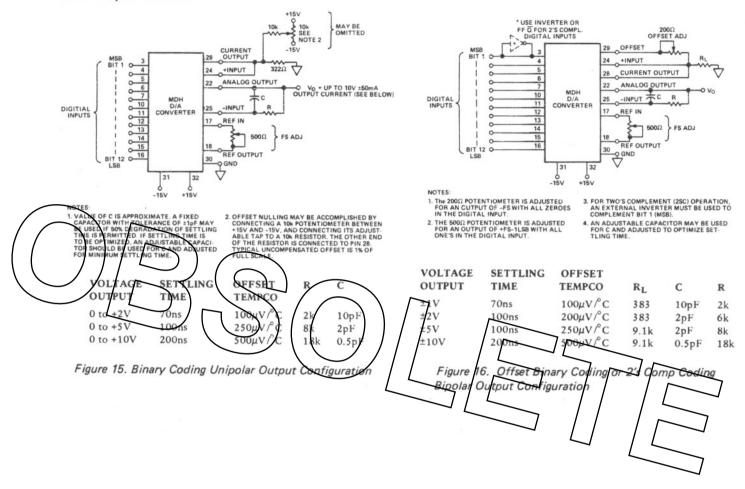

By using external feedback resistor and capacitor as shown in Figures 15 and 16, other full scale output ranges from 2V to 10V may be obtained.

MDSL (MDS-1240, MDSL-0825, 1035, 1250 continued) SEE NOTE -15V +15V 31 R1 500Ω ZERO 29 VOLTAGE OUTPUT OUTPUT ±1V FS VOUT = R1 (IN kΩ) +1 VOLTS FS UNIPOLAR ±10V (MAX) AT ±100mA 5 6 7 10 D/A CONVERTER 2.32kΩ (750Ω MDS-1240) DIGITIAL 11 12 13 R2 300Ω REF OUT 18 10 R4 1kΩ D/A CONVERTER DIGITIAL 0 11 0 12 0 13 0 14 0 15 14 100Ω TO 1kΩ GROUND 15 ADJ 18 REFOUT 16 BIT 12 O REF IN 0 15 16 -15V +15V NOTES:

1. CIRCUIT SHOWN FOR UNIPOLAR POSITIVE

OUTPUT. OUTPUT SETTLING TIME IS APPROXIMATELY 150ns. 4. FOR BIPOLAR OUTPUT CONNECT 500Ω POTENTIOMETER BETWEEN PINS 29 AND 28 AND UNGROUND PIN 29. R2 IS SE L<sub>2</sub>TO 2.32kΩ, AND V<sub>OUT</sub> (p-p) = 2 (R1 (IN kΩ) +1). C. C1 IS APPROXIMATELY 10pF AND MAY BE ADJUSTED FOR BEST TRANSIENT RESPONSE. CALIBRATION PROCEDURE CALIBRATION PROCESSING

WITH INPUT CODE 000000000000

ADJUST THE 5000 (R1) POTENTIOMETER

FOR -1,000 VOLTS OUTPUT. WITH

INPUT CODE 1111111111111ADJUST

THE 1001 (R2) POTENTIOMETER FOR

+0.99976 VSLTS OUTPUT. 2. FOR 0 TO +10V OUTPUT R2 = 300 $\Omega$ , R1 = 9k $\Omega$ . 3. R3 IS ADJUSTED FOR DESIRED OUTPUT, RANGE IS APPROXIMATELY +5%. Figure 13. Noninverting Unipolar or Bipolar Voltage Output ipolar Cur<del>rent</del> Qutput APPLICATIONS E UTPUT MDS/MDSE/815, 1040 (MSB) BIT 1 O TWO OUTPUTS UP TO 2V (p-p) BIT 2 C 220 D/A CONVERTER DIGITAL OUTPUT INPUTS HOS-050 OP AMP BIT 9 O BIT 10 O-(LSB) O +15V Figure 11. Voltage Output MDS-1240, MDSL (all) STROBE O NOTES ON DEGLITCHED D/A TTL SEE MAX UPDATE RATE = 11MHz FOR 0.01% ACCURACY CONSULT DGM DATA SHEET FOR DEGLITCH CIRCUIT DETAILS. NOTE -15V +15V 2. R1 IS VARIED TO OBTAIN DESIRED OUTPUT LEVEL: FOR 0 TO +1V OUT PUT, R1 =  $100\Omega$ . VOLTAGE OUTPUT Figure 14. Ultra High-Speed Deglitched D/A (Vout = -R1 X Io) HOS-050 OP AMP **100**Ω 10 D/A CONVERTER DIGITIAL GROUND 12 18 REF OUT 0 13 100Ω TO 1kΩ 16 REF IN FOR UNIPOLAR VOLTAGE OUTPUT CONNECT JUMPER BETWEEN PINS 29 AND 30. FOR BIPOLAR VOLTAGE OUTPUT CONNECT A 500Ω POTENTIO-METER BETWEEN PINS 28 AND 29 AND ADJUST FOR ZERO OUTPUT WITH 100000000000 INPUT.

Figure 12. Inverting Unipolar or Bipolar Voltage Output

| ANALOG OUTPUT BIPOLAR, NONINVERTING | OFFSET BINARY | ANALOG OUTPUT UNIPOLAR, NONINVERTING | STRAIGHT BINARY |

|-------------------------------------|---------------|--------------------------------------|-----------------|

| +FS, -1LSB                          | 1111          | +FS, -1LSB                           | 1111            |

| +1/2 FS                             | 1100          | +3/4 FS                              | 1100            |

| 0                                   | 1000          | +1/2 FS                              | 1000            |

| -1/2 FS                             | 0100          | +1/4 FS                              | 0100            |

| -FS                                 | 0000          | 0                                    | 0000            |

Table 2. Input Coding

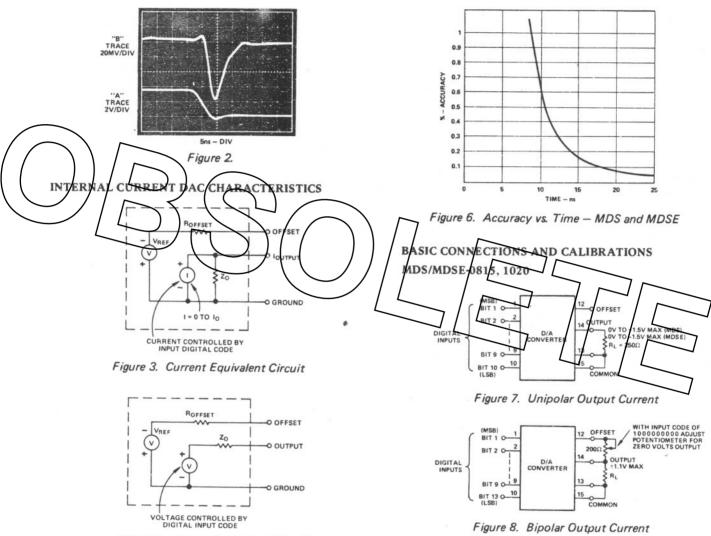

Figure 4. Voltage Equivalent Circuit

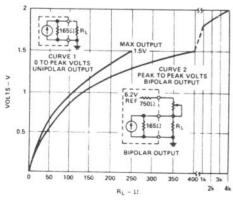

Figure 5. VOUT vs. Load Resistance MDS-0815, -1020

MDS-1240, MDSL-0825, 1035, 1250

Figure 9. Unipolar Current Output

(continued from page 191S)

Each D/A is housed in industry standard size cases, and each has an internal precision reference. Bipolar operation is achieved by external pin interconnection. In normal circumstances, no external components are required for operation into low impedance loads. Designed primarily for PCB mounting, these D/A's may also be plugged into standard DIL sockets mounted on 1.8" centers (MDS series 2" centers).

For ultra-high reliability, this D/A series is optionally available with burn-in extended beyond the Analog Devices standard of 96 hours at +25°C.

### NOTES ON FAST-SETTLING D/A CONVERTERS

Invariably, fast-settling D/A converters use current rather than voltage switching.

There are inherent advantages to current-switching converters, since it eliminates an output amplifier. If there is no output amplifier there is no slew rate limitation which slows settling. The absence of an output amplifier also means there are no overshoot and ringing problems often associated with feedback amplifiers.

The settling time of a current-switshing D/A converter, then, is based on:

- 1. The RC time constant of the converter output

- 2. The settling time of the output current change.

If the settling time of the D/A converter under consideration is determined by the RC time constant, the output capacitance and output impedance become very important.

As a typical example in the Analog Devices' D/A converters, output capacitance is 5pF, and nominal output impedance is  $165\Omega$ .

For test purposes, the output of these D/A converters are loaded with approximately  $150\Omega$ . (There is no "trick" or "gimmick" in loading the output of the converter; it is done to provide an output voltage of approximately 1.0V to 1.2V.) This loading means RC =  $80\times5\times10^{-12}$  = 0.4ns. Since settling time is approximately 7 RC, the overall settling time, if determined by the RC time constant, would be 2.8ns.

Based on this, it becomes obvious the RC time constant of such converters outputs is not the limiting factor in establishing settling time. Instead, the settling time of the converters is based primarily on the settling time of the overall (output) current change, since the effect of the RC time constant is "swamped." Expressed in another way, this means settling time for the MDS series converters is relatively independent of load resistance, unless substantial load capacitance is present. The settling time of the output current, in turn, is based on:

- 1. The settling time of each switch within the converter.

- The time skew among the digital inputs which cause the switching action.

Some manufacturers of fast-settling D/A converters spec settling time under the conditions of all digital inputs changing from "0" to "1", or vice versa. At first glance, it would appear this is the "worst case" condition for measuring settling time, since maximum current is being switched.

Unfortunately, this method of specifying neglects an important characteristic of saturated logic... the propagation delay for negative-going inputs is different from the delay for page 8 of 8

going inputs on all forms of saturated logic. The TTL or DTL driving logic, and the D/A input circuits for current-switching D/A's are subject to this same characteristic.

Thus, the time skew of the individual current switches within the converter is worse when one or more input bits are out of phase with the others. This is true even for ideal inputs in which the digital inputs arrive simultaneously; if there is time skew among the bit inputs, of course, the problem becomes more pronounced.

Note, settling times even better than those specified for the MDS series become possible if digital input bit arrivals are deskewed.

These differences among the switches cause a discontinuity or "glitch" in the output. The true "worst case" glitch always occurs at the switching point of the Most Significant Bit or the center point of the output range, because nearly equal and opposite currents are being switched within the converter.

In addition, all "0" to all "1" switching overlooks the practical aspects involved. There are relatively few times when all of the input bits will be changing from one state to the other on successive input changes; however, the MSB will switch out of phase with all other bits each time the analog output of the converter crosses the midpoint.

In considering the choice of a "fast settling" D/A converter, then, the user should look for the following points in the data sheet:

- If the settling time spec has all bits changing state identically, it neglects the phenomenor associated with saturated logic discussed earlier.

- 2. Is the settling time specified with an impractically-low-impedance load?

If the RC time constant of the converter output is the major factor in establishing settling time (because of high output capacitance and/or resistance), a low impedance load helps make settling time look better.

A low impedance load means the voltage being developed at the output is oftentimes too small to be useful.

A higher-impedance load which can develop a useable output of 1.0V or more sometimes negates the fast settling time of the spec sheet.

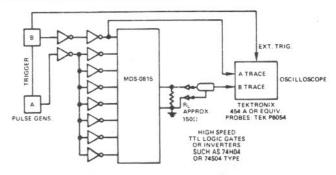

A test setup for this worst-case measurement is shown in Figure 1. Two pulse generators are used to generate the required out-of-phase pulses, and the delays are adjusted for minimum skew. Figure 2 is an unretouched photo of the oscilloscope trance of an MDS-815 under test.

Figure 1.