# ARM920T

(Rev 1)

## **Technical Reference Manual**

#### ARM920T

#### **Technical Reference Manual**

Copyright © 2000, 2001 ARM Limited. All rights reserved.

#### **Release Information**

Change history

| Date               | Issue | Change         |

|--------------------|-------|----------------|

| 31st January 2000  | A     | First release  |

| 5th September 2000 | В     | Second release |

| 18th April 2001    | С     | Third release  |

#### **Proprietary Notice**

Words and logos marked with ® or ™ are registered trademarks or trademarks owned by ARM Limited, except as otherwise stated below in this proprietary notice. Other brands and names mentioned herein may be the trademarks of their respective owners.

Neither the whole nor any part of the information contained in, or the product described in, this document may be adapted or reproduced in any material form except with the prior written permission of the copyright holder.

The product described in this document is subject to continuous developments and improvements. All particulars of the product and its use contained in this document are given by ARM in good faith. However, all warranties implied or expressed, including but not limited to implied warranties of merchantability, or fitness for purpose, are excluded.

This document is intended only to assist the reader in the use of the product. ARM Limited shall not be liable for any loss or damage arising from the use of any information in this document, or any error or omission in such information, or any incorrect use of the product.

Figure 9-5 on page 9-12 reprinted with permission IEEE Std 1149.1-1990, IEEE Standard Test Access Port and Boundary-Scan Architecture Copyright 2000, by IEEE. The IEEE disclaims any responsibility or liability resulting from the placement and use in the described manner

#### **Confidentiality Status**

This document is Open Access. This document has no restriction on distribution.

#### **Product Status**

The information in this document is final (information on a developed product).

#### **Web Address**

http://www.arm.com

# Contents

# **ARM920T Technical Reference Manual**

|           | Preface                                      |      |

|-----------|----------------------------------------------|------|

|           | About this document                          | xvi  |

|           | Further reading                              | xx   |

|           | Feedback                                     |      |

| Chapter 1 | Introduction                                 |      |

| •         | 1.1 About the ARM920T                        | 1-2  |

|           | 1.2 Processor functional block diagram       | 1-3  |

| Chapter 2 | Programmer's Model                           |      |

| •         | 2.1 About the programmer's model             | 2-2  |

|           | 2.2 About the ARM9TDMI programmer's model    |      |

|           | 2.3 CP15 register map summary                |      |

| Chapter 3 | Memory Management Unit                       |      |

| •         | 3.1 About the MMU                            | 3-2  |

|           | 3.2 MMU program accessible registers         |      |

|           | 3.3 Address translation                      |      |

|           | 3.4 MMU faults and CPU aborts                | 3-21 |

|           | 3.5 Fault address and fault status registers | 3-22 |

|           | 3.6 Domain access control                    |      |

|           | 3.7 Fault checking sequence                  |      |

|           | 3.8  | External aborts                                   | 3-28    |

|-----------|------|---------------------------------------------------|---------|

|           | 3.9  | Interaction of the MMU and caches                 | 3-29    |

| Chapter 4 | Cac  | hes, Write Buffer, and Physical Address TAG (PA T | AG) RAM |

|           | 4.1  | About the caches and write buffer                 |         |

|           | 4.2  | ICache                                            |         |

|           | 4.3  | DCache and write buffer                           |         |

|           | 4.4  | Cache coherence                                   |         |

|           | 4.5  | Cache cleaning when lockdown is in use            |         |

|           | 4.6  | Implementation notes                              |         |

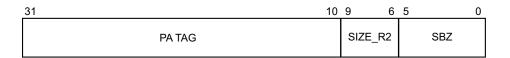

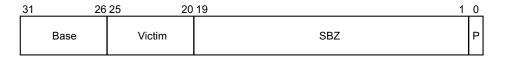

|           | 4.7  | Physical address TAG RAM                          |         |

|           | 4.8  | Drain write buffer                                |         |

|           | 4.9  | Wait for interrupt                                | 4-24    |

| Chapter 5 | Cloc | ck Modes                                          |         |

|           | 5.1  | About ARM920T clocking                            | 5-2     |

|           | 5.2  | FastBus mode                                      |         |

|           | 5.3  | Synchronous mode                                  |         |

|           | 5.4  | Asynchronous mode                                 |         |

| Chapter 6 | Rue  | Interface Unit                                    |         |

| Onapici o | 6.1  | About the ARM920T bus interface                   | 6-2     |

|           | 6.2  | Unidirectional AMBA ASB interface                 |         |

|           | 6.3  | Fully-compliant AMBA ASB interface                |         |

|           | 6.4  | AMBA AHB interface                                |         |

|           | 6.5  | Level 2 cache support and performance analysis    |         |

| Chapter 7 | Con  | rocessor Interface                                |         |

| Onapier 7 | 7.1  | About the ARM920T coprocessor interface           | 7-9     |

|           | 7.1  | LDC/STC                                           |         |

|           | 7.2  | MCR/MRC                                           |         |

|           | 7.4  | Interlocked MCR                                   |         |

|           | 7.5  | CDP                                               |         |

|           | 7.6  | Privileged instructions                           | _       |

|           | 7.7  | Busy-waiting and interrupts                       |         |

| Chapter 8 | Trac | ce Interface Port                                 |         |

|           | 8.1  | About the ETM interface                           | 8-2     |

| Chapter 9 | Deb  | ug Support                                        |         |

| •         | 9.1  | About debug                                       | 9-2     |

|           | 9.2  | Debug systems                                     |         |

|           | 9.3  | Debug interface signals                           |         |

|           | 9.4  | Scan chains and JTAG interface                    |         |

|           | 9.5  | The JTAG state machine                            |         |

|           | 9.6  | Test data registers                               |         |

|           | 0.0  |                                                   |         |

|            | 9.7<br>9.8   | ARM920T core clocks                                                     |       |

|------------|--------------|-------------------------------------------------------------------------|-------|

|            | 9.9          | Clock switching during test                                             |       |

|            | 9.10         | Determining the core state and system state                             |       |

|            | 9.11         | Exit from debug state                                                   |       |

|            | 9.12<br>9.13 | The behavior of the program counter during debug  EmbeddedICE macrocell |       |

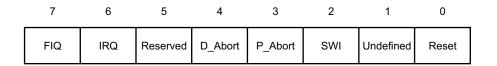

|            | 9.13<br>9.14 | Vector catching                                                         |       |

|            | 9.15         | Single-stepping                                                         |       |

|            | 9.16         | Debug communications channel                                            |       |

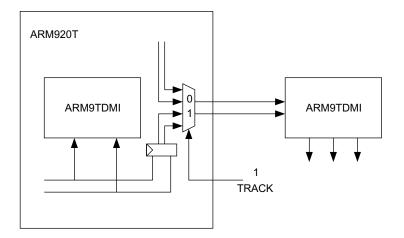

| Chapter 10 | Tracki       | ingICE                                                                  |       |

| •          | 10.1         | About TrackingICE                                                       | 10-2  |

|            | 10.2         | Timing requirements                                                     | 10-3  |

|            | 10.3         | TrackingICE outputs                                                     | 10-4  |

| Chapter 11 | AMBA         | Test Interface                                                          |       |

|            | 11.1         | About the AMBA test interface                                           |       |

|            | 11.2         | Entering and exiting AMBA Test                                          |       |

|            | 11.3         | Functional test                                                         |       |

|            | 11.4         | Burst operations                                                        |       |

|            | 11.5         | PA TAG RAM test                                                         |       |

|            | 11.6<br>11.7 | Cache test                                                              | _     |

| Chapter 12 | Instru       | ction Cycle Summary and Interlocks                                      |       |

| Chapter 12 | 12.1         | About the instruction cycle summary                                     | 12-2  |

|            | 12.2         | Instruction cycle times                                                 |       |

|            | 12.3         | Interlocks                                                              |       |

| Chapter 13 | AC Ch        | naracteristics                                                          |       |

| •          | 13.1         | ARM920T timing diagrams                                                 | 13-2  |

|            | 13.2         | ARM920T timing parameters                                               |       |

|            | 13.3         | Timing definitions for the ARM920T Trace Interface Port                 | 13-26 |

| Appendix A | Signal       | Descriptions                                                            |       |

|            | A.1          | AMBA signals                                                            |       |

|            | A.2          | Coprocessor interface signals                                           |       |

|            | A.3          | JTAG and TAP controller signals                                         |       |

|            | A.4          | Debug signals                                                           |       |

|            | A.5<br>A.6   | Miscellaneous signalsARM920T Trace Interface Port signals               |       |

| A          |              | Č                                                                       |       |

| Appendix B |              | Test Registers                                                          | _ =   |

|            | B.1          | About the test registers                                                |       |

|            | B.2          | Test state register                                                     | в-з   |

#### Contents

| B.3 | Cache test registers and operations          | B-8  |

|-----|----------------------------------------------|------|

| B.4 | MMU test registers and operations            | B-18 |

| B.5 | StrongARM backwards compatibility operations | B-30 |

## Glossary

# List of Tables

# **ARM920T Technical Reference Manual**

| Change history                               | i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| CP15 register map                            | 2-5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Address types in ARM920T                     | 2-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| CP15 abbreviations                           | 2-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Register 0, ID code                          | 2-8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Cache type register format                   | 2-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Cache size encoding (M=0)                    | 2-11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Line length encoding                         | 2-12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Control register 1 bit functions             | 2-12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Clocking modes                               | 2-14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Fault status register                        | 2-16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Function descriptions register 7             | 2-17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TLB operations register 8                    | 2-19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Accessing the cache lockdown register 9      | 2-22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Accessing the TLB lockdown register 10       | 2-23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Interpreting level one descriptor bits [1:0] | 3-10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                              | Change history ARM9TDMI implementation options CP15 register map Address types in ARM920T CP15 abbreviations Register 0, ID code Cache type register format Cache size encoding (M=0) Cache associativity encoding (M=0) Line length encoding Control register 1 bit functions Clocking modes Register 2, translation table base Register 3, domain access control Fault status register Function descriptions register 7 Cache operations register 8 Accessing the cache lockdown register 9 Accessing the TLB lockdown register 10 CP15 register functions Level one descriptor bits Interpreting level one descriptor bits [1:0] |

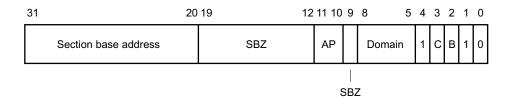

| Table 3-4  | Section descriptor bits                                              | 3-11    |

|------------|----------------------------------------------------------------------|---------|

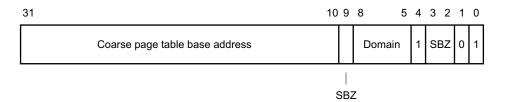

| Table 3-5  | Coarse page table descriptor bits                                    | 3-12    |

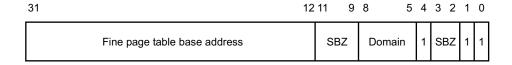

| Table 3-6  | Fine page table descriptor bits                                      | 3-13    |

| Table 3-7  | Level two descriptor bits                                            | 3-16    |

| Table 3-8  | Interpreting page table entry bits [1:0]                             | 3-16    |

| Table 3-9  | Priority encoding of fault status                                    | 3-22    |

| Table 3-10 | Interpreting access control bits in domain access control register   | 3-23    |

| Table 3-11 | Interpreting access permission (AP) bits                             |         |

| Table 4-1  | DCache and write buffer configuration                                |         |

| Table 5-1  | Clock selection for external memory accesses                         |         |

| Table 6-1  | Relationship between bidirectional and unidirectional ASB interface  |         |

| Table 6-2  | ARM920T input/output timing                                          | 6-4     |

| Table 6-3  | AMBA ASB transfer types                                              | 6-6     |

| Table 6-4  | Burst transfers                                                      | 6-7     |

| Table 6-5  | Use of WRITEOUT signal                                               |         |

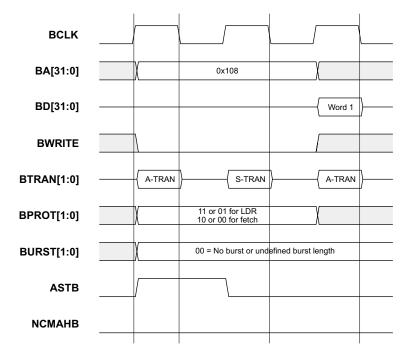

| Table 6-6  | Noncached LDR and fetch                                              | 6-12    |

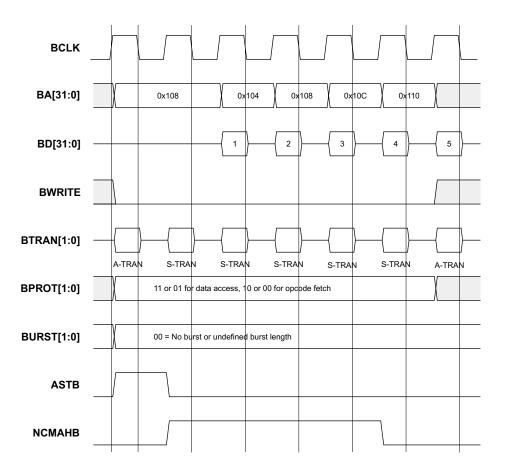

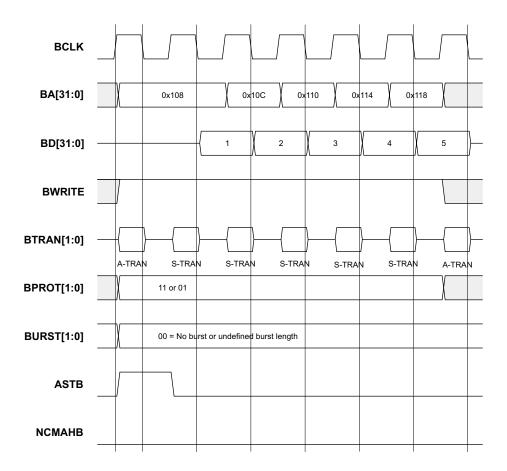

| Table 6-7  | Data eviction of 4 or 8 words                                        |         |

| Table 6-8  | ARM920T supported bus access types                                   |         |

| Table 7-1  | Handshake encoding                                                   |         |

| Table 9-1  | Public instructions                                                  | 9-14    |

| Table 9-2  | ID code register                                                     |         |

| Table 9-3  | Scan chain number allocation                                         |         |

| Table 9-4  | Scan chain 0 bit order                                               |         |

| Table 9-5  | Scan chain 1 bit function                                            |         |

| Table 9-6  | Scan chain 2 bit function                                            |         |

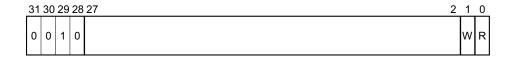

| Table 9-7  | Scan chain 15 format and access modes                                |         |

| Table 9-8  | Scan chain 15 physical access mode bit format                        |         |

| Table 9-9  | Physical access mapping to CP15 registers                            |         |

| Table 9-10 | Scan chain 15 interpreted access mode bit format                     |         |

| Table 9-11 | Interpreted access mapping to CP15 registers                         | 9-35    |

| Table 9-12 | Interpreted access mapping to the MMU                                |         |

| Table 9-13 | Interpreted access mapping to the caches                             |         |

| Table 9-14 | Scan chain 4 format                                                  |         |

| Table 9-15 | ARM9TDMI EmbeddedICE macrocell register map                          |         |

| Table 9-16 | Watchpoint control register, data comparison bit functions           |         |

| Table 9-17 | Watchpoint control register for instruction comparison bit functions |         |

| Table 9-18 | Debug status register bit functions                                  |         |

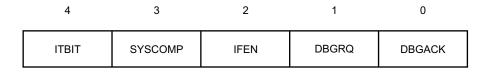

| Table 9-19 | Debug comms control register bit functions                           |         |

| Table 10-1 | ARM920T in TrackingICE mode                                          |         |

| Table 11-1 | AMBA test modes                                                      |         |

| Table 11-2 | AMBA functional test locations                                       |         |

| Table 11-3 | Construction of A920Inputs location                                  |         |

| Table 11-4 | Construction of A920Status1 location                                 |         |

| Table 11-5 | Construction of A920Status2 location                                 |         |

| Table 11-6 | Burst locations                                                      |         |

| Table 11-7 | PA TAG RAM locations                                                 |         |

| Table 11-8 | Construction of data pattern write data                              | . 11-12 |

| Table 11-9  | Cache test locations                            | 11-15 |

|-------------|-------------------------------------------------|-------|

| Table 11-10 | CAM write data                                  | 11-15 |

| Table 11-11 | CAM match write data                            | 11-16 |

| Table 11-12 | CAM match read data                             | 11-16 |

| Table 11-13 | Invalidate by VA write data                     | 11-16 |

| Table 11-14 | Lockdown victim and base data                   | 11-17 |

| Table 11-15 | MMU test locations                              | 11-19 |

| Table 11-16 | Invalidate by VA data                           | 11-19 |

| Table 11-17 | Match write data                                | 11-20 |

| Table 11-18 | CAM data                                        |       |

| Table 11-19 | CAM data Size_C encoding                        | 11-20 |

| Table 11-20 | RAM1 data                                       |       |

| Table 11-21 | RAM1 data access permission bits                | 11-21 |

| Table 11-22 | RAM2 data                                       | 11-22 |

| Table 11-23 | RAM2 data Size_R2 encoding                      | 11-22 |

| Table 12-1  | Symbols used in tables                          | 12-3  |

| Table 12-2  | Instruction cycle bus times                     | 12-3  |

| Table 12-3  | Data bus instruction times                      |       |

| Table 13-1  | ARM920T timing parameters                       |       |

| Table 13-2  | ARM920T Trace Interface Port timing definitions |       |

| Table A-1   | AMBA signals                                    |       |

| Table A-2   | Coprocessor interface signals                   |       |

| Table A-3   | JTAG and TAP controller signals                 |       |

| Table A-4   | Debug signals                                   |       |

| Table A-5   | Miscellaneous signals                           |       |

| Table A-6   | Trace signals                                   | A-13  |

| Table B-1   | Test state register                             |       |

| Table B-2   | Clocking mode selection                         |       |

| Table B-3   | Register 7 operations                           |       |

| Table B-4   | Register 9 operations                           |       |

| Table B-5   | Register 15 operations                          |       |

| Table B-6   | CP15 MCR and MRC instructions                   |       |

| Table B-7   | Register 7, 9, and 15 operations                |       |

| Table B-8   | Write cache victim and lockdown operations      |       |

| Table B-9   | TTB register operations                         |       |

| Table B-10  | DAC register operations                         |       |

| Table B-11  | FSR register operations                         |       |

| Table B-12  | FAR register operations                         |       |

| Table B-13  | Register 8 operations                           |       |

| Table B-14  | Register 10 operations                          |       |

| Table B-15  | CAM, RAM1, and RAM2 register 15 operations      |       |

| Table B-16  | Register 2, 3, 5, 6, 8, 10, and 15 operations   |       |

| Table B-17  | CAM memory region size                          |       |

| Table B-18  | Access permission bit setting                   |       |

| Table B-19  | Miss and fault encoding                         |       |

| Table B-20  | RAM2 memory region size                         |       |

| Table B-21  | Write TLB lockdown operations                   | B-27  |

List of Tables

# List of Figures

# **ARM920T Technical Reference Manual**

| Figure P-1  | Key to timing diagram conventions                 | XIX  |

|-------------|---------------------------------------------------|------|

| Figure 1-1  | ARM920T functional block diagram                  | 1-3  |

| Figure 2-1  | CP15 MRC and MCR bit pattern                      | 2-7  |

| Figure 2-2  | Cache type register format                        | 2-9  |

| Figure 2-3  | Dsize and Isize field format                      | 2-9  |

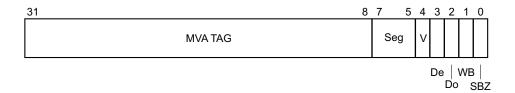

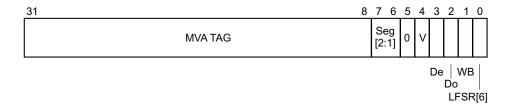

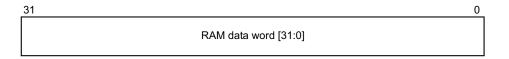

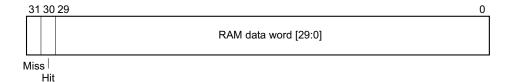

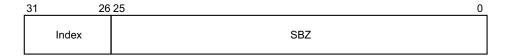

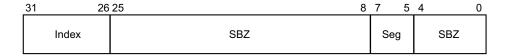

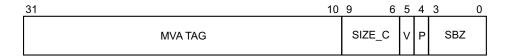

| Figure 2-4  | Register 7 MVA format                             | 2-19 |

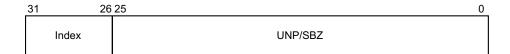

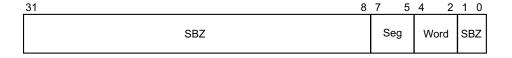

| Figure 2-5  | Register 7 index format                           | 2-19 |

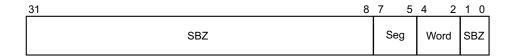

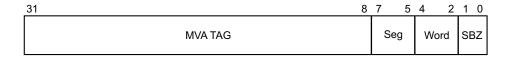

| Figure 2-6  | Register 8 MVA format                             | 2-20 |

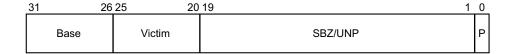

| Figure 2-7  | Register 9                                        | 2-22 |

| Figure 2-8  | Register 10                                       | 2-23 |

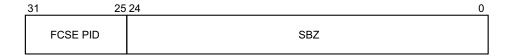

| Figure 2-9  | Register 13                                       | 2-24 |

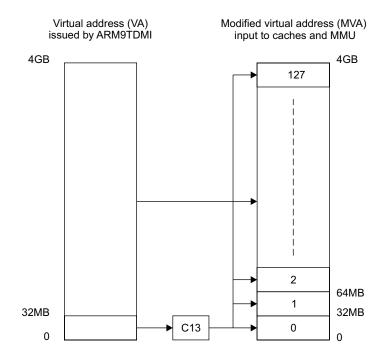

| Figure 2-10 | Address mapping using CP15 Register 13            | 2-25 |

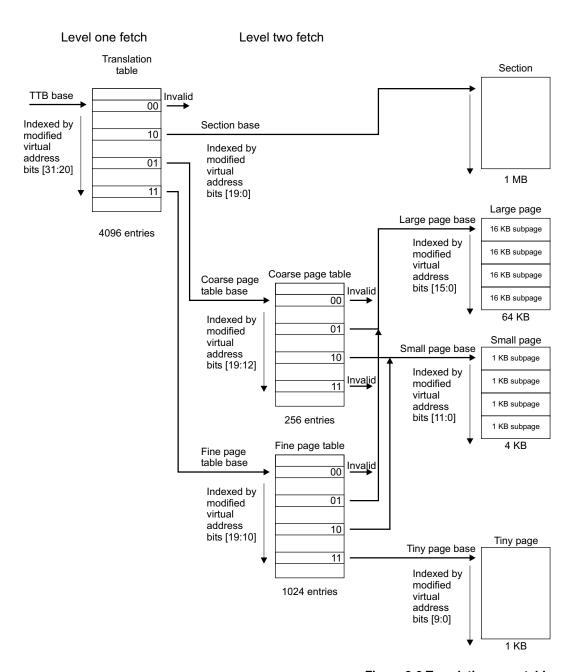

| Figure 3-1  | Translation table base register                   | 3-6  |

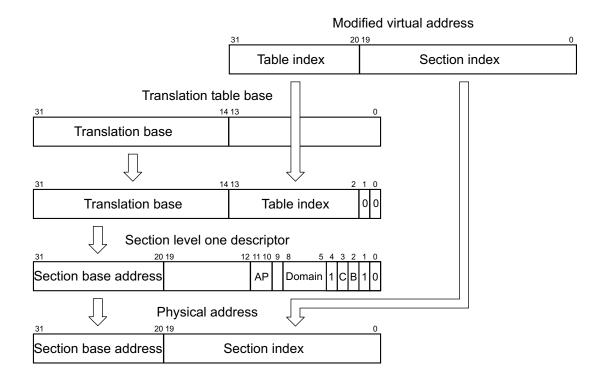

| Figure 3-2  | Translating page tables                           | 3-7  |

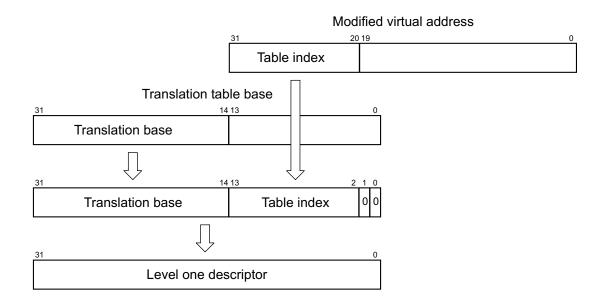

| Figure 3-3  | Accessing translation table level one descriptors | 3-8  |

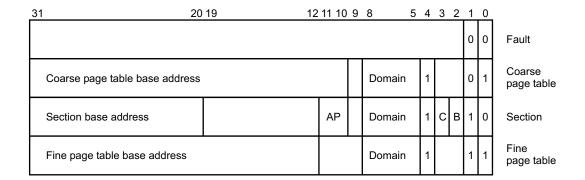

| Figure 3-4  | Level one descriptor                              | 3-9  |

| Figure 3-5  | Section descriptor                                | 3-10 |

| Figure 3-6  | Coarse page table descriptor                      | 3-11 |

| Figure 3-7  | Fine page table descriptor                        | 3-12 |

| Figure 3-8  | Section translation                               | 3-14 |

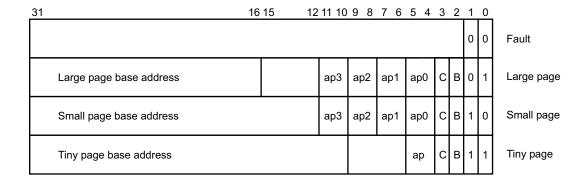

| Figure 3-9  | Level two descriptor                              | 3-15 |

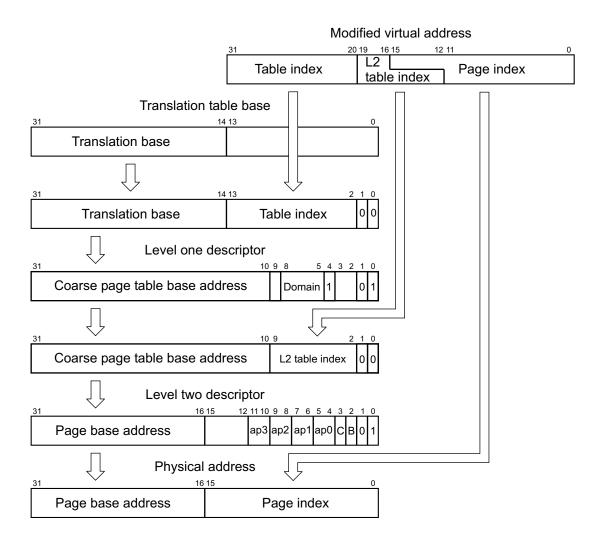

| Figure 3-10 | Large page translation from a coarse page table   |      |

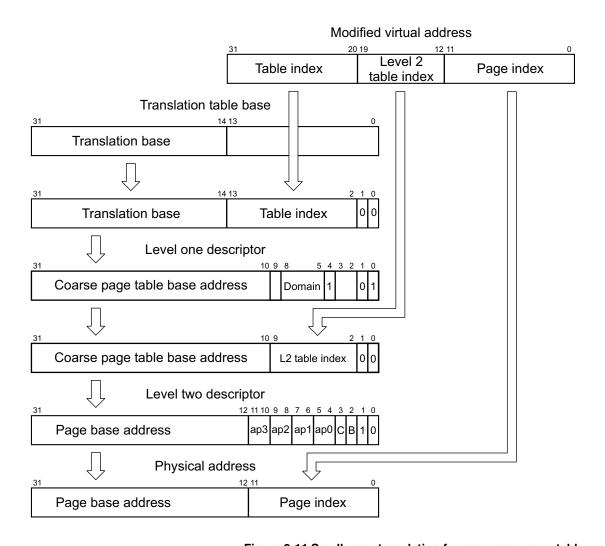

| Figure 3-11 | Small page translation from a coarse page table   | 3-18 |

|             |                                                   |      |

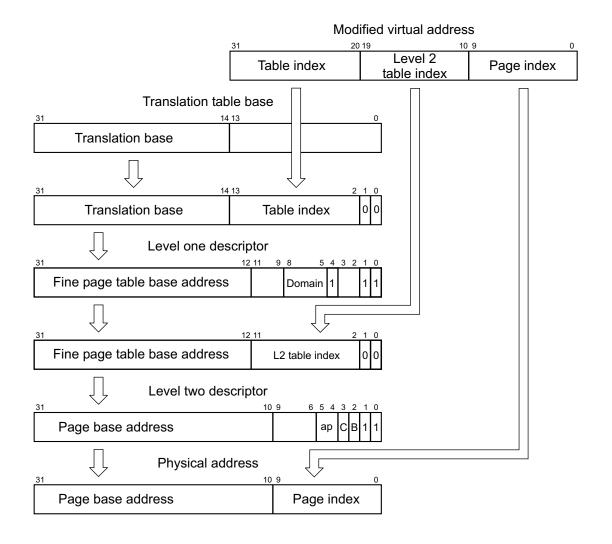

| Figure 3-12 | Tiny page translation from a fine page table           | 3-19 |

|-------------|--------------------------------------------------------|------|

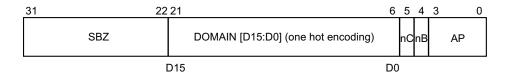

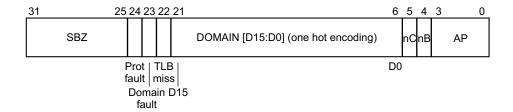

| Figure 3-13 | Domain access control register format                  |      |

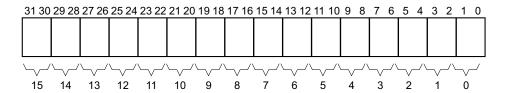

| Figure 3-14 | Sequence for checking faults                           | 3-25 |

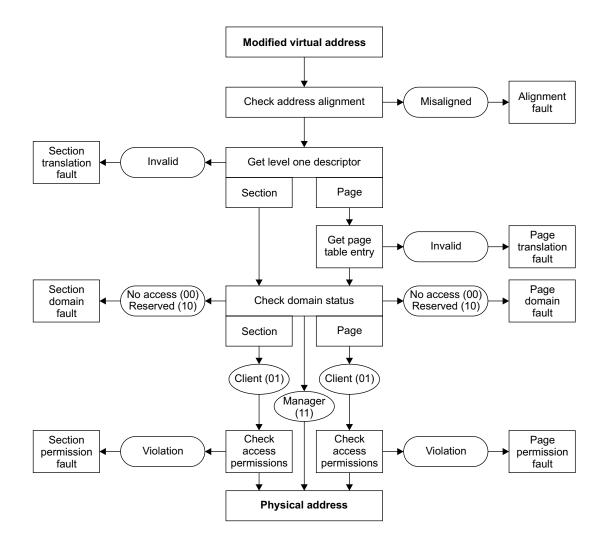

| Figure 4-1  | Addressing the 16KB ICache                             | 4-5  |

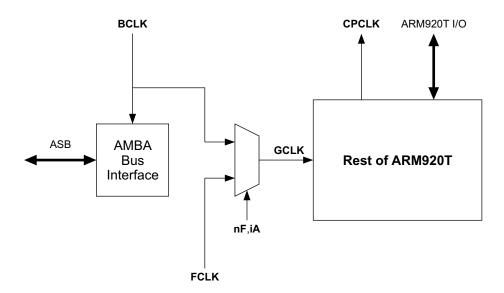

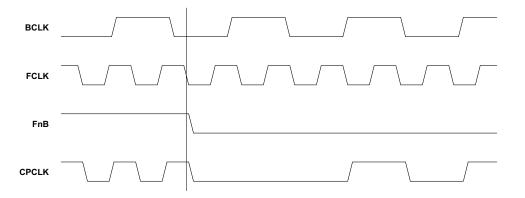

| Figure 5-1  | ARM920T clocking                                       | 5-2  |

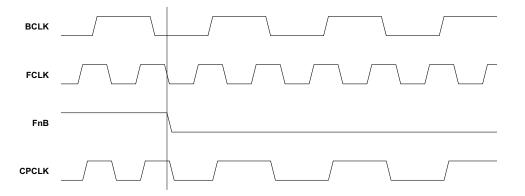

| Figure 5-2  | Synchronous mode FCLK to BCLK zero phase delay         | 5-5  |

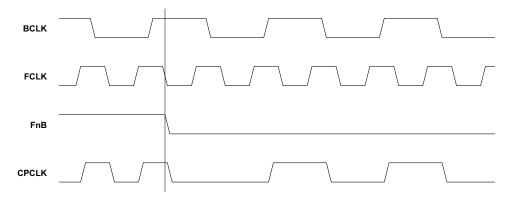

| Figure 5-3  | Synchronous mode FCLK to BCLK one phase delay          | 5-5  |

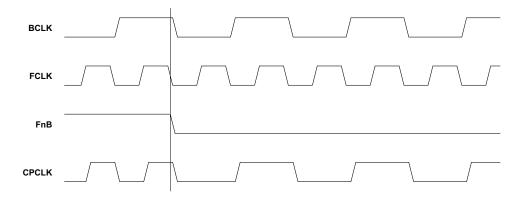

| Figure 5-4  | Asynchronous mode FCLK to BCLK zero cycle delay        | 5-6  |

| Figure 5-5  | Asynchronous mode FCLK to BCLK one cycle delay         | 5-7  |

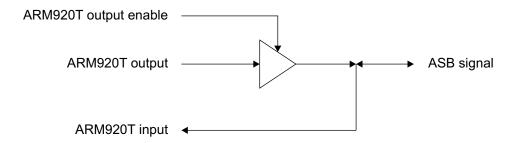

| Figure 6-1  | Output buffer for bidirectional signals                | 6-5  |

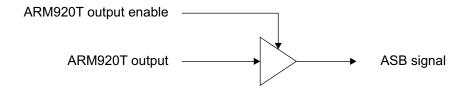

| Figure 6-2  | Output buffer for unidirectional signals               | 6-6  |

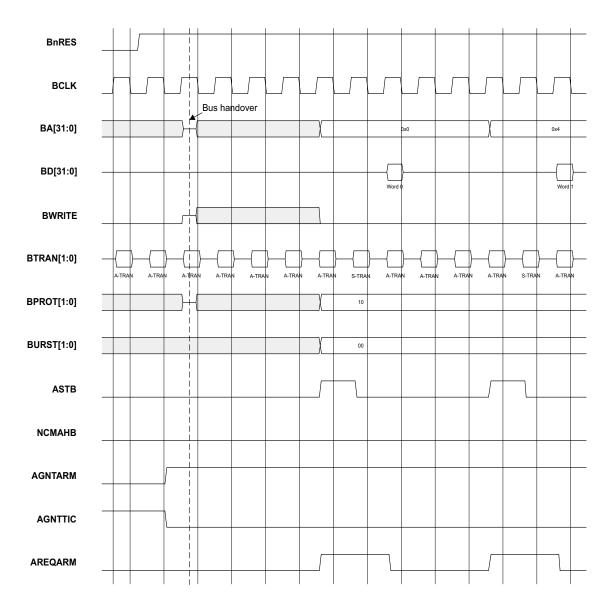

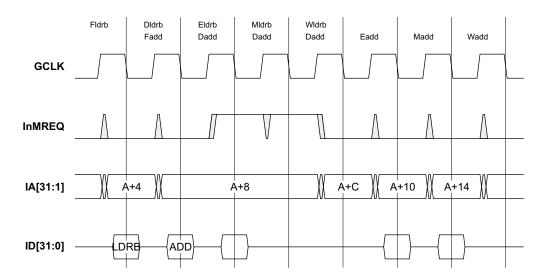

| Figure 6-3  | Instruction fetch after reset                          | 6-11 |

| Figure 6-4  | Example LDR from address 0x108                         | 6-12 |

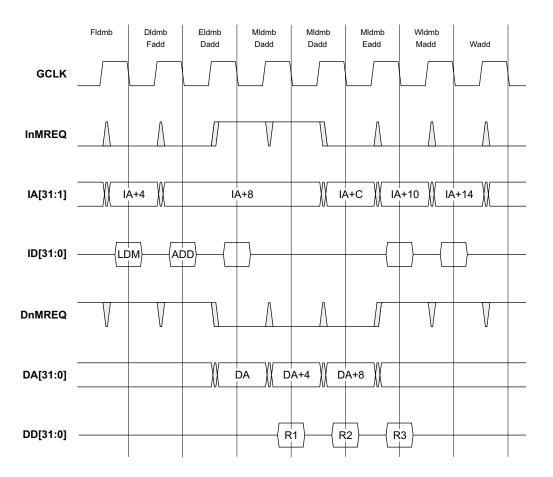

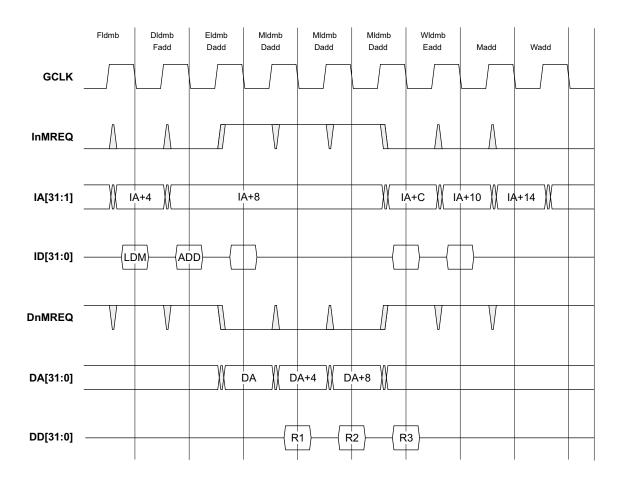

| Figure 6-5  | Example LDM of 5 words from 0x108                      | 6-13 |

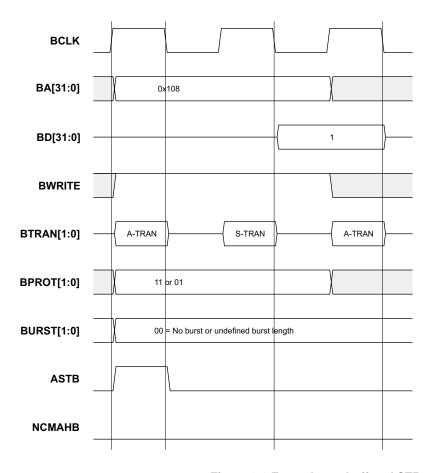

| Figure 6-6  | Example nonbuffered STR                                | 6-14 |

| Figure 6-7  | Example nonbuffered STM                                | 6-15 |

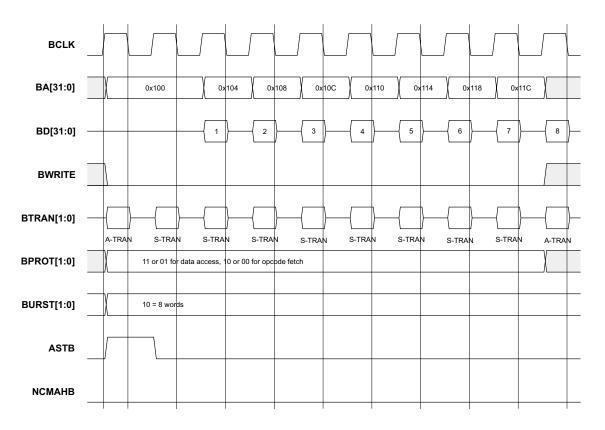

| Figure 6-8  | Example linefill from 0x100                            | 6-16 |

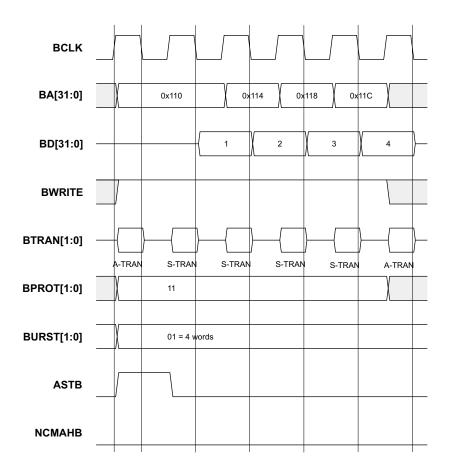

| Figure 6-9  | Example 4-word data eviction                           | 6-17 |

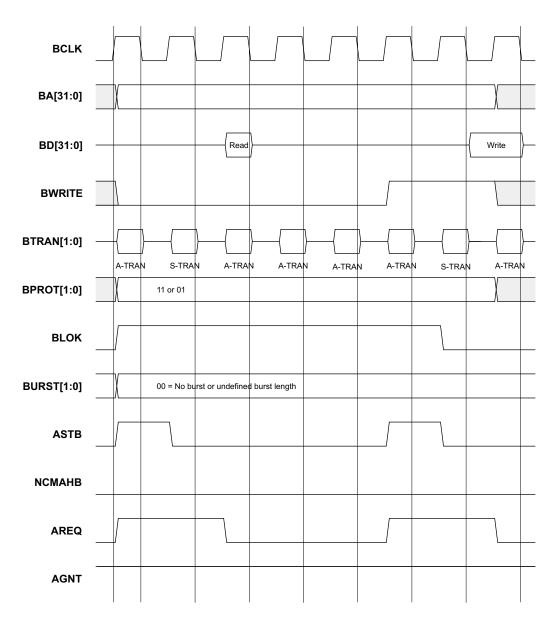

| Figure 6-10 | Example swap operation                                 | 6-19 |

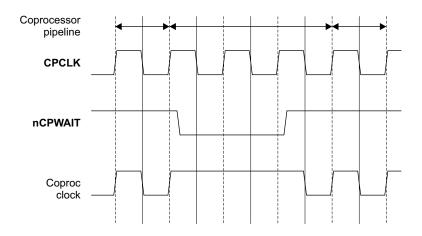

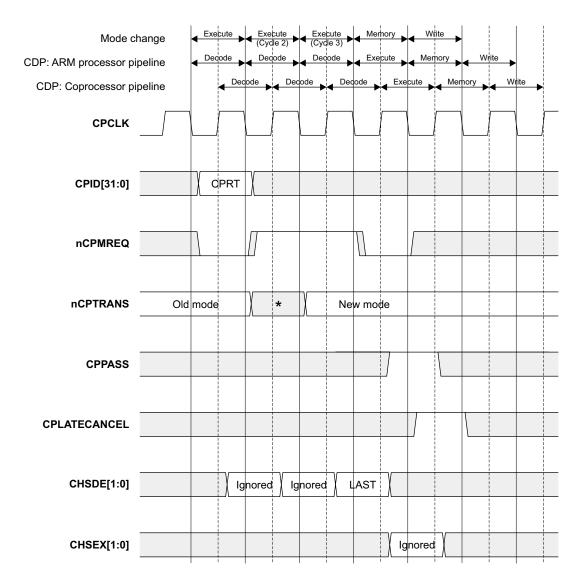

| Figure 7-1  | ARM920T coprocessor clocking                           | 7-3  |

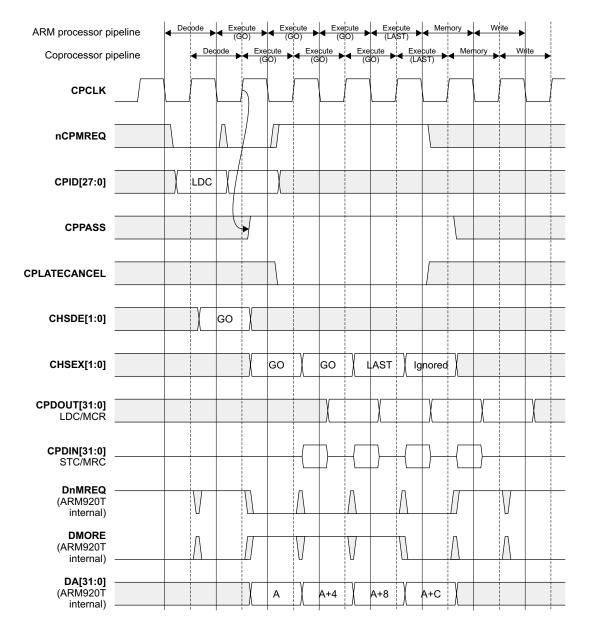

| Figure 7-2  | ARM920T LDC/STC cycle timing                           | 7-5  |

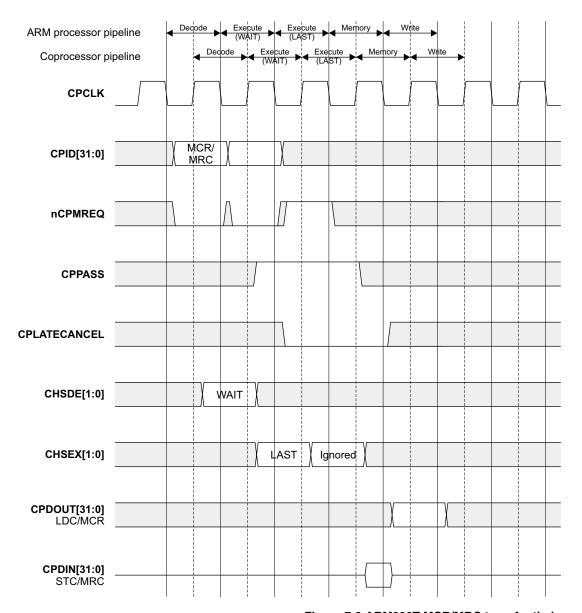

| Figure 7-3  | ARM920T MCR/MRC transfer timing                        | 7-9  |

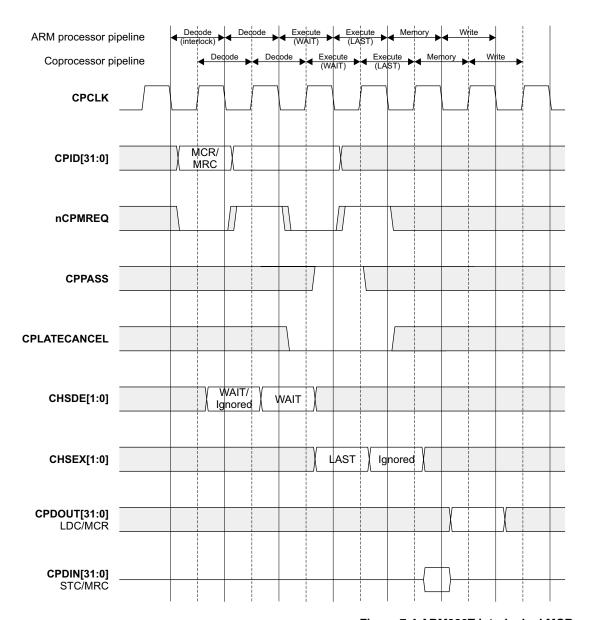

| Figure 7-4  | ARM920T interlocked MCR                                | 7-12 |

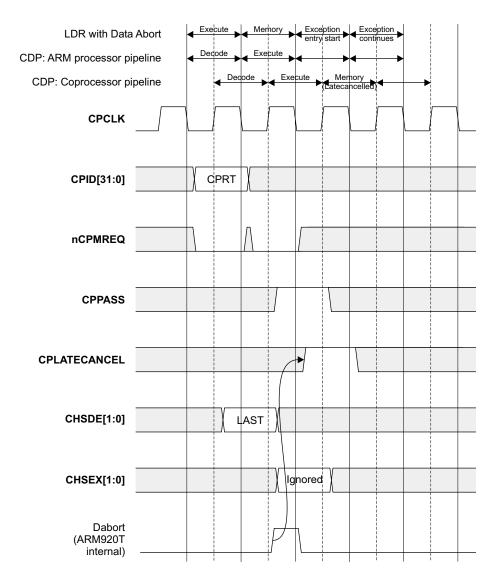

| Figure 7-5  | ARM920T late canceled CDP                              |      |

| Figure 7-6  | ARM920T privileged instructions                        |      |

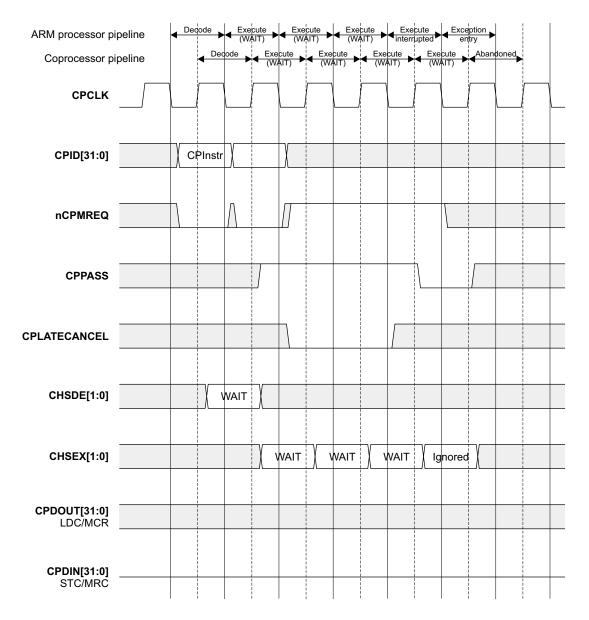

| Figure 7-7  | ARM920T busy waiting and interrupts                    |      |

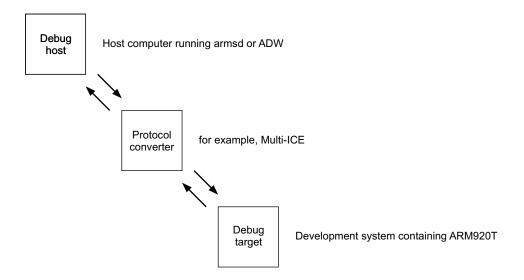

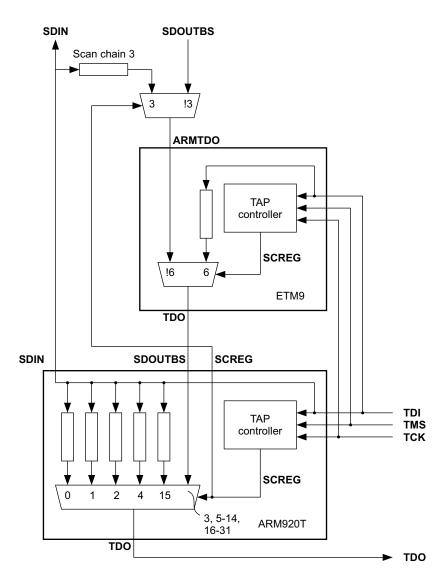

| Figure 9-1  | Typical debug system                                   | 9-3  |

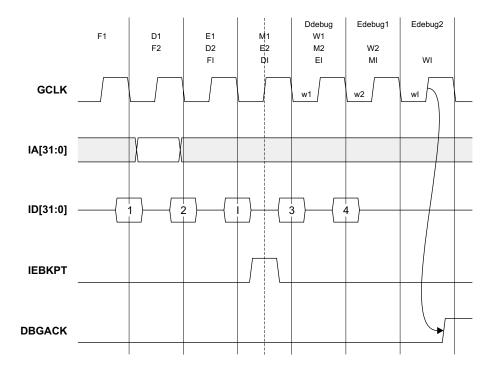

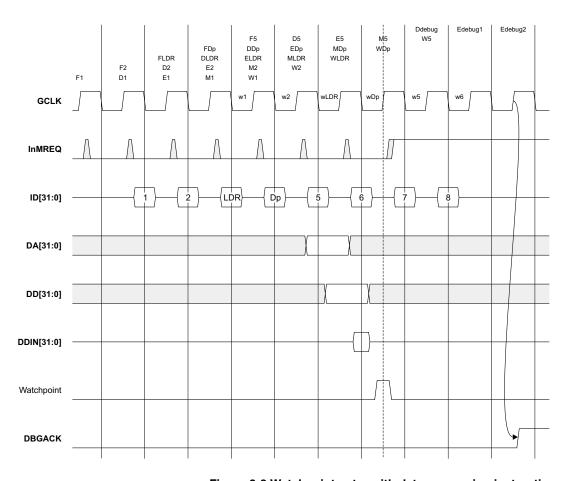

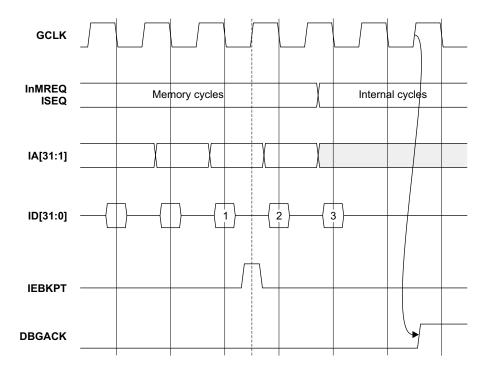

| Figure 9-2  | Breakpoint timing                                      |      |

| Figure 9-3  | Watchpoint entry with data processing instruction      |      |

| Figure 9-4  | Watchpoint entry with branch                           |      |

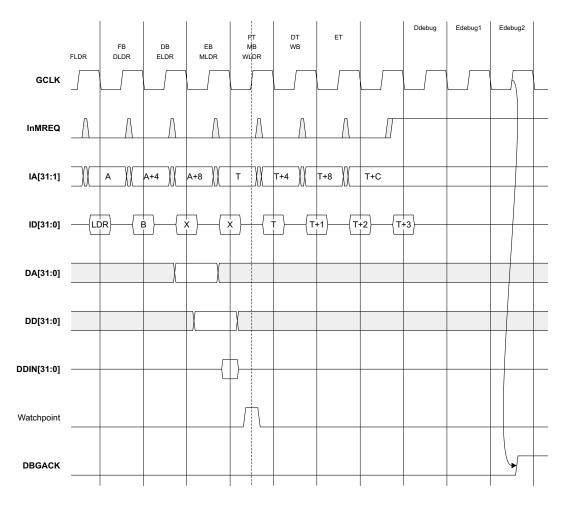

| Figure 9-5  | Test access port (TAP) controller state transitions    |      |

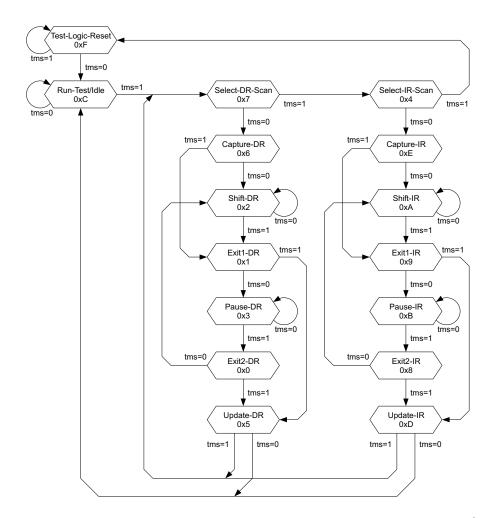

| Figure 9-6  | External scan chain multiplexor                        |      |

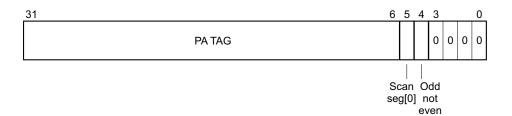

| Figure 9-7  | Write back physical address format                     |      |

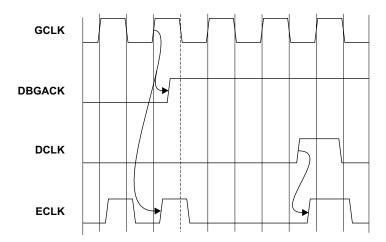

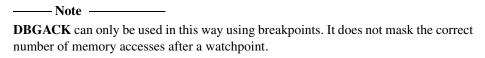

| Figure 9-8  | Clock switching on entry to debug state                |      |

| Figure 9-9  | Debug exit sequence                                    |      |

| Figure 9-10 | Debug state entry                                      |      |

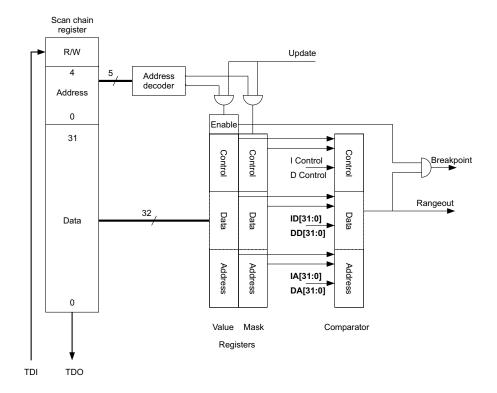

| Figure 9-11 | ARM9TDMI EmbeddedICE macrocell overview                |      |

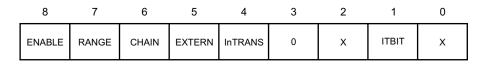

| Figure 9-12 | Watchpoint control register for data comparison        |      |

| Figure 9-13 | Watchpoint control register for instruction comparison |      |

| Figure 9-14 | Debug control register                                 |      |

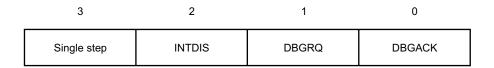

| Figure 9-15 | Debug status register                                  |      |

| Figure 9-16 | Vector catch register                                  |      |

| Figure 9-17 | Debug comms control register                           |      |

| Figure 10-1 | Using TrackingICE                                      |      |

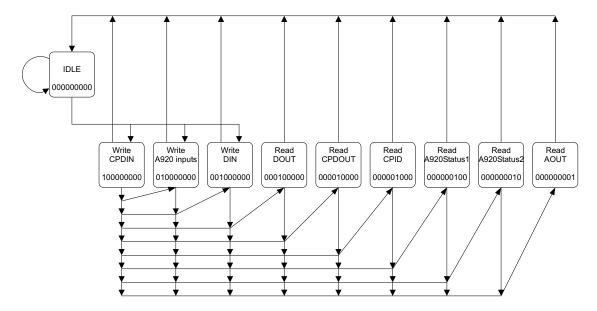

| Figure 11-1 | AMBA functional test state machine                     |      |

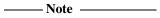

| Figure 11-2 | Write data format                                      |      |

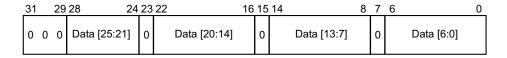

| Figure 12-1 | Single load interlock timing                           | 12-6 |

| Figure 12-2  | Two cycle load interlock                               | 12-7  |

|--------------|--------------------------------------------------------|-------|

| Figure 12-3  | LDM interlock                                          |       |

| Figure 12-4  | LDM dependent interlock                                | 12-10 |

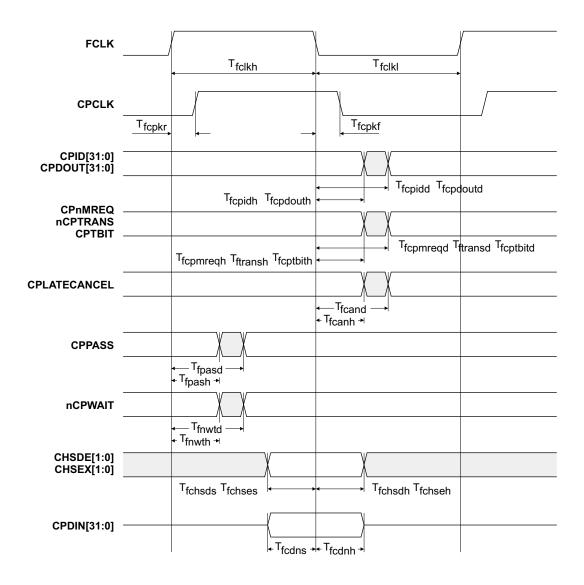

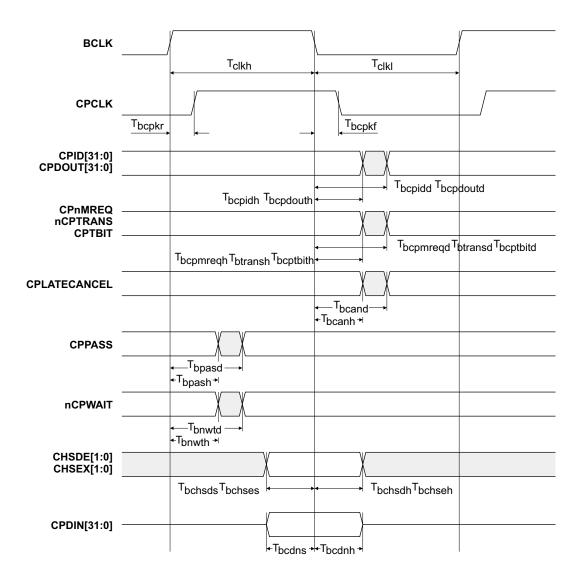

| Figure 13-1  | ARM920T FCLK timed coprocessor interface               | 13-2  |

| Figure 13-2  | ARM920T BCLK timed coprocessor interface               | 13-3  |

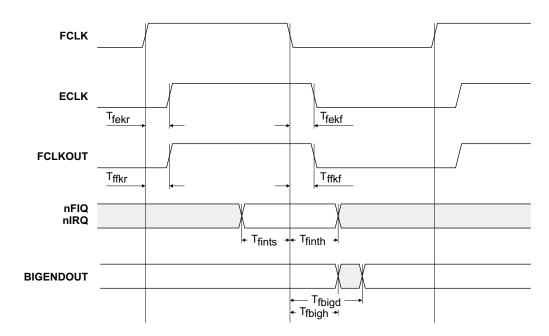

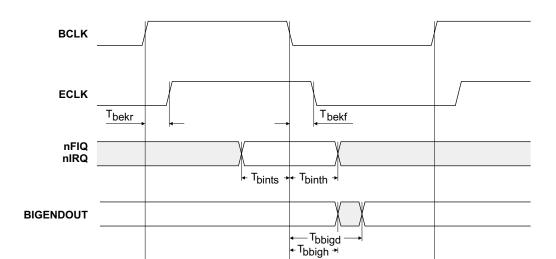

| Figure 13-3  | ARM920T FCLK related signal timing                     | 13-4  |

| Figure 13-4  | ARM920T BCLK related signal timing                     | 13-5  |

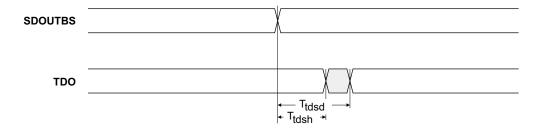

| Figure 13-5  | ARM920T SDOUTBS to TDO relationship                    | 13-5  |

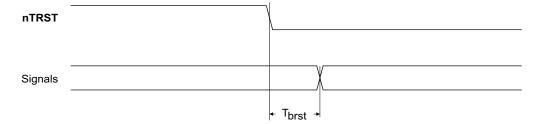

| Figure 13-6  | ARM920T nTRST to other signals relationship            | 13-6  |

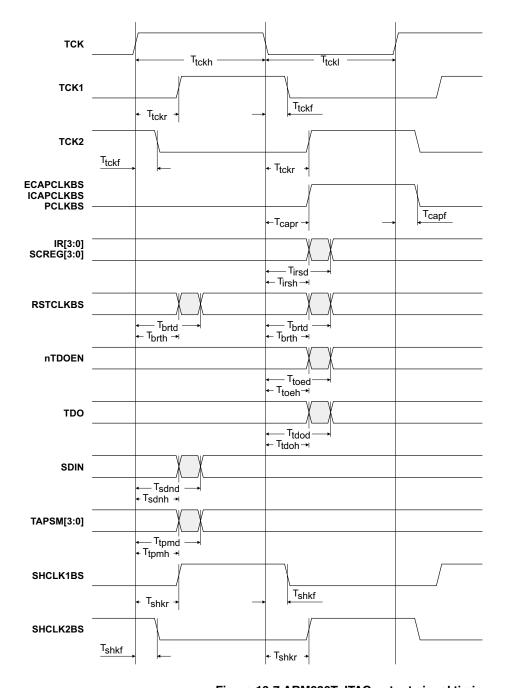

| Figure 13-7  | ARM920T JTAG output signal timing                      | 13-7  |

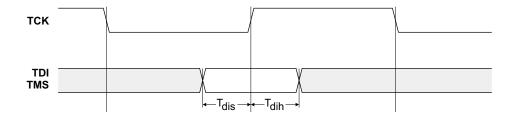

| Figure 13-8  | ARM920T JTAG input signal timing                       | 13-8  |

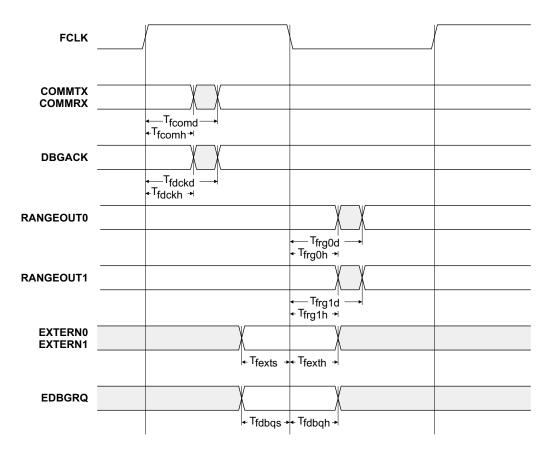

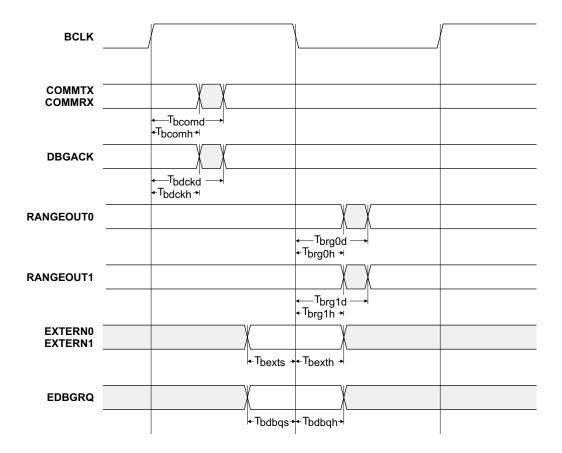

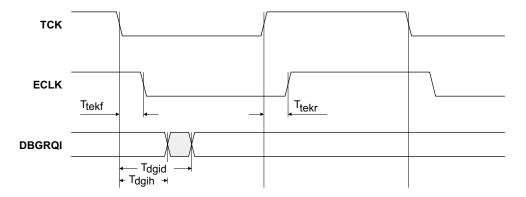

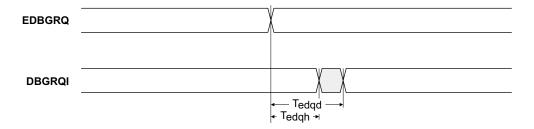

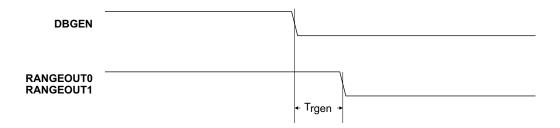

| Figure 13-9  | ARM920T FCLK related debug output timing               | 13-8  |

| Figure 13-10 | ARM920T BCLK related debug output timing               | 13-9  |

| Figure 13-11 | ARM920T TCK related debug output timing                | 13-10 |

| Figure 13-12 | ARM920T EDBGRQ to DBGRQI relationship                  | 13-10 |

| Figure 13-13 | ARM920T DBGEN to output relationship                   | 13-11 |

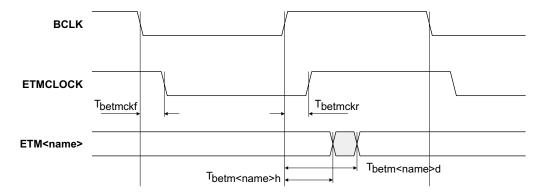

| Figure 13-14 | ARM920T BCLK related Trace Interface Port timing       | 13-11 |

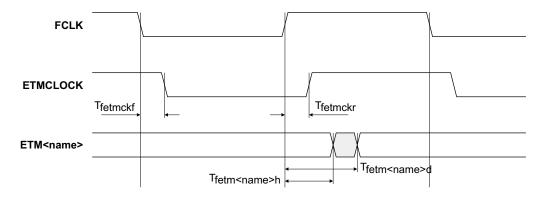

| Figure 13-15 | ARM920T FCLK related Trace Interface Port timing       | 13-12 |

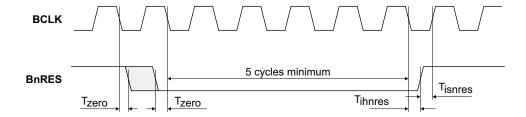

| Figure 13-16 | ARM920T BnRES timing                                   | 13-12 |

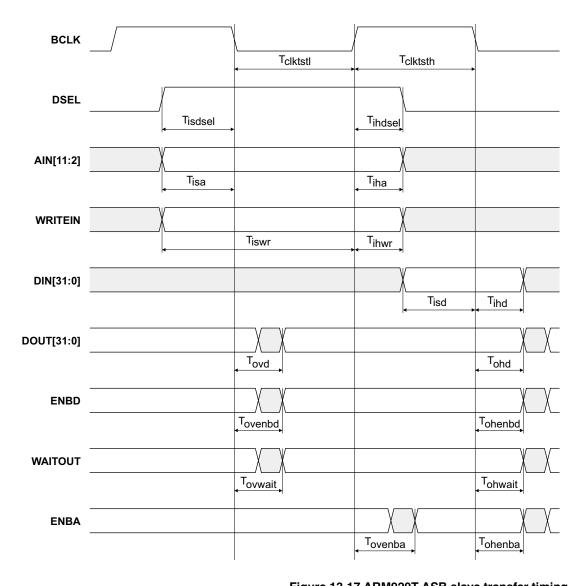

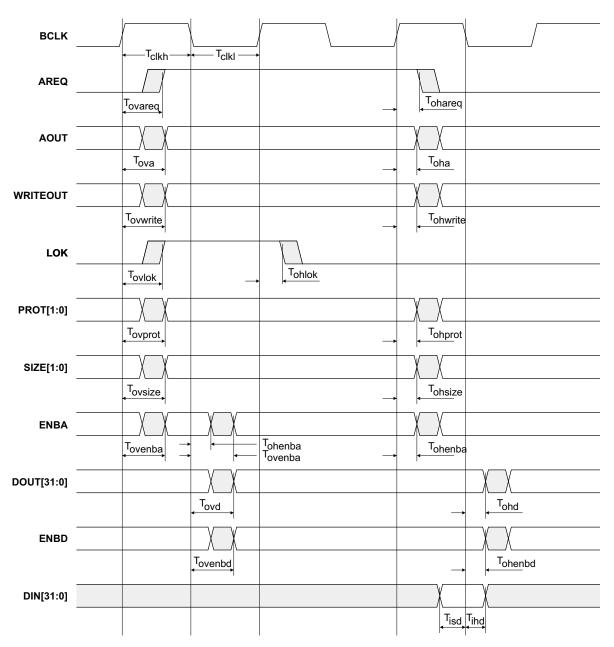

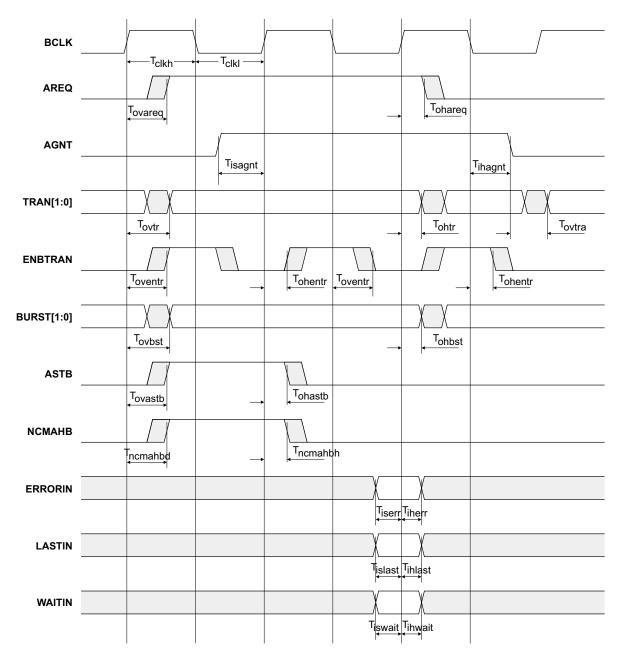

| Figure 13-17 | ARM920T ASB slave transfer timing                      | 13-13 |

| Figure 13-18 | ARM920T ASB master transfer timing                     | 13-14 |

| Figure 13-19 | ARM920T ASB master transfer timing                     | 13-15 |

| Figure B-1   | CP15 MRC and MCR bit pattern                           | B-2   |

| Figure B-2   | Rd format, CAM read                                    | B-12  |

| Figure B-3   | Rd format, CAM write                                   | B-12  |

| Figure B-4   | Rd format, RAM read                                    | B-12  |

| Figure B-5   | Rd format, RAM write                                   | B-13  |

| Figure B-6   | Rd format, CAM match RAM read                          | B-13  |

| Figure B-7   | Data format, CAM read                                  | B-13  |

| Figure B-8   | Data format, RAM read                                  | B-13  |

| Figure B-9   | Data format, CAM match RAM read                        | B-14  |

| Figure B-10  | Rd format, write I or D cache victim and lockdown base | B-15  |

| Figure B-11  | Rd format, write I or D cache victim                   | B-15  |

| Figure B-12  | Rd format, CAM write and data format, CAM read         | B-24  |

| Figure B-13  | Rd format, RAM1 write                                  | B-24  |

| Figure B-14  | Data format, RAM1 read                                 | B-25  |

| Figure B-15  | Rd format, RAM2 write and data format, RAM2 read       |       |

| Figure R-16  | Rd format, write Lor D.TLB lockdown                    | B-27  |

List of Figures

## **Preface**

This preface introduces the ARM920T processor and its reference documentation. It contains the following sections:

- About this document on page xvi

- Further reading on page xx

- Feedback on page xxi.

#### About this document

This document is the technical reference manual for the ARM920T processor.

#### Intended audience

This document has been written for hardware and software engineers who want to design or develop products based upon the ARM920T processor. It assumes no prior knowledge of ARM products.

#### **Using this manual**

This document is organized into the following chapters:

#### Chapter 1 Introduction

Read this chapter for an introduction to the ARM920T.

#### Chapter 2 Programmer's Model

Read this chapter for a description of the programmer's model for the ARM920T.

#### Chapter 3 Memory Management Unit

Read this chapter for a description of the memory management unit and the memory interface, including descriptions of the instruction and data interfaces.

#### Chapter 4 Caches, Write Buffer, and Physical Address TAG (PA TAG) RAM

Read this chapter for descriptions of cache, write buffer, and PA TAG RAM operation.

#### **Chapter 5 Clock Modes**

Read this chapter for a description of the processor clock modes.

#### Chapter 6 Bus Interface Unit

Read this chapter for a description of the bus interface unit and the AMBA ASB and AHB interface.

#### Chapter 7 Coprocessor Interface

Read this chapter for a description of the ARM920T coprocessor interface.

#### Chapter 8 Trace Interface Port

Read this chapter for a description of the Trace Interface Port of the ARM920T.

#### Chapter 9 Debug Support

Read this chapter for a description of the debug interface.

#### Chapter 10 TrackingICE

Read this chapter for a description of how the ARM920T uses TrackingICE mode.

#### Chapter 11 AMBA Test Interface

Read this chapter for a description of the AMBA test interface.

#### Chapter 12 Instruction Cycle Summary and Interlocks

Read this chapter for details of instruction cycle times. This chapter contains timing diagrams for interlock timing.

#### Chapter 13 AC Characteristics

Read this chapter for a description of the timing parameters used in the ARM920T.

#### Appendix A Signal Descriptions

Read this chapter for a detailed description of the signals used in the ARM920T.

#### Appendix B CP15 Test Registers

Read this chapter for a detailed description of the CP15 test register used in the ARM920T.

#### Typographical conventions

The following typographical conventions are used in this book:

**bold** Highlights ARM processor signal names, and interface elements, such as

menu names and buttons. Also used for terms in descriptive lists, where

appropriate.

*italic* Highlights special terminology, cross-references, and citations.

typewriter Denotes text that can be entered at the keyboard, such as commands, file

and program names, and source code.

<u>typewriter</u> Denotes a permitted abbreviation for a command or option. The

underlined text may be entered instead of the full command or option

name.

typewriter italic

Denotes arguments to commands or functions, where the argument is to

be replaced by a specific value.

typewriter bold

Denotes language keywords when used outside example code.

#### **Timing diagram conventions**

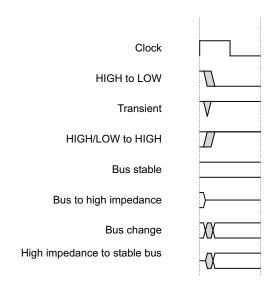

This manual contains a number of timing diagrams. Figure P-1 explains the components used in these diagrams. Any variations are clearly labeled when they occur. Therefore, you must not attach any additional meaning unless specifically stated.

Figure P-1 Key to timing diagram conventions

Shaded bus and signal areas are undefined, so the bus or signal can assume any value within the shaded area at that time. The actual level is unimportant and does not affect normal operation.

## **Further reading**

This section lists publications by ARM Limited, and by third parties.

If you would like further information on ARM products, or if you have questions not answered by this document, please contact info@arm.com or visit our web site at http://www.arm.com.

#### **ARM publications**

This document contains information that is specific to the ARM920T processor. Refer to the following documents for other relevant information:

- ARM Architecture Reference Manual (ARM DDI 0100)

- *ARM9TDMI Data Sheet* (ARM DDI 0029).

#### Other publications

This section lists relevant documents published by third parties.

IEEE Std. 1149.1- 1990, Standard Test Access Port and Boundary-Scan Architecture.

#### **Feedback**

ARM Limited welcomes feedback both on the ARM920T processor, and on the documentation.

#### Feedback on the ARM920T

If you have any comments or suggestions about this product, please contact your supplier giving:

- the product name

- a concise explanation of your comments.

#### Feedback on the ARM920T Technical Reference Manual

If you have any comments about this document, please send email to errata@arm.com giving:

- the document title

- the document number

- the page number(s) to which your comments refer

- a concise explanation of your comments.

General suggestions for additions and improvements are also welcome.

Preface

# Chapter 1 Introduction

This chapter introduces the ARM920T processor. It contains the following sections:

- About the ARM920T on page 1-2

- Processor functional block diagram on page 1-3.

#### 1.1 About the ARM920T

The ARM920T processor is a member of the ARM9TDMI family of general-purpose microprocessors, which includes:

- ARM9TDMI (core)

- ARM940T (core plus cache and protection unit)

- ARM920T (core plus cache and MMU).

The ARM9TDMI processor core is a Harvard architecture device implemented using a five-stage pipeline consisting of Fetch, Decode, Execute, Memory, and Write stages. It can be provided as a standalone core that can be embedded into more complex devices. The standalone core has a simple bus interface that allows you to design your own caches and memory systems around it.

The ARM9TDMI family of microprocessors supports both the 32-bit ARM and 16-bit Thumb instruction sets, allowing you to trade off between high performance and high code density.

The ARM920T processor is a Harvard cache architecture processor that is targeted at multiprogrammer applications where full memory management, high performance, and low power are all-important. The separate instruction and data caches in this design are 16KB each in size, with an 8-word line length. The ARM920T processor implements an enhanced ARM architecture v4 MMU to provide translation and access permission checks for instruction and data addresses.

The ARM920T processor supports the ARM debug architecture and includes logic to assist in both hardware and software debug. The ARM920T processor also includes support for coprocessors, exporting the instruction and data buses along with simple handshaking signals.

The ARM920T interface to the rest of the system is over unified address and data buses. This interface enables implementation of either an *Advanced Microcontroller Bus Architecture* (AMBA) *Advanced System Bus* (ASB) or *Advanced High-performance Bus* (AHB) bus scheme either as a fully-compliant AMBA bus master, or as a slave for production test. The ARM920T processor also has a *Tracking ICE* mode which allows an approach similar to a conventional ICE mode of operation.

The ARM920T processor supports the addition of an *Embedded Trace Macrocell* (ETM) for real-time tracing of instructions and data.

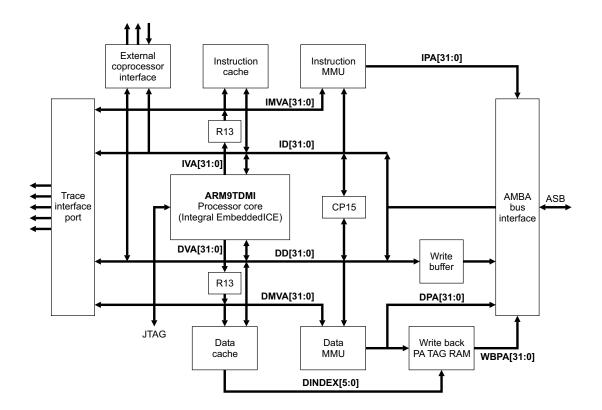

## 1.2 Processor functional block diagram

Figure 1-1 shows the functional block diagram of the ARM920T processor.

Figure 1-1 ARM920T functional block diagram

The blocks shown in Figure 1-1 are described as follows:

- The ARM9TDMI core is described in the ARM9TDMI Technical Reference Manual.

- Register 13 and coprocessor 15 are described in Chapter 2 *Programmer's Model*.

- The instruction and data MMUs are described in Chapter 3 *Memory Management Unit*.

- The instruction and data caches, the write buffer, and the write-back PA TAG RAM are described in Chapter 4 *Caches*, *Write Buffer*, and *Physical Address TAG* (*PA TAG*) *RAM*.

- The AMBA bus interface is described in Chapter 6 Bus Interface Unit.

- The external coprocessor interface is described in Chapter 7 *Coprocessor Interface*.

- The trace interface port is described in Chapter 8 *Trace Interface Port*.

# Chapter 2 **Programmer's Model**

This chapter describes the ARM920T registers and provides details required when programming the microprocessor. It contains the following sections:

- About the programmer's model on page 2-2

- About the ARM9TDMI programmer's model on page 2-3

- *CP15 register map summary* on page 2-5.

## 2.1 About the programmer's model

The ARM920T processor incorporates the ARM9TDMI integer core, which implements the ARM architecture v4T. It executes the ARM and Thumb instruction sets, and includes EmbeddedICE JTAG software debug features.

The programmer's model of the ARM920T processor consists of the programmer's model of the ARM9TDMI core (see *About the ARM9TDMI programmer's model* on page 2-3) with the following additions and modifications:

- The ARM920T processor incorporates two coprocessors:

- CP14, which allows software access to the debug communications channel.

You can access the registers defined in CP14 using MCR and MRC instructions.

These are described in *Debug communications channel* on page 9-64.

- The system control coprocessor, CP15, which provides additional registers that are used to configure and control the caches, MMU, protection system, the clocking mode, and other system options of the ARM920T, such as big or little-endian operation. You can access the registers defined in CP15 using MCR and MRC instructions. These are described in CP15 register map summary on page 2-5.

- The ARM920T processor also features an external coprocessor interface that

allows the attachment of a closely-coupled coprocessor on the same chip, for

example, a floating-point unit. You can access registers and operations provided

by any coprocessors attached to the external coprocessor interface using

appropriate coprocessor instructions.

- Memory accesses for instruction fetches and data loads and stores can be cached

or buffered. Cache and write buffer configuration and operation is described in

detail in Chapter 4 Caches, Write Buffer, and Physical Address TAG (PA TAG)

RAM.

- The MMU page tables that reside in main memory describe the virtual to physical

address mapping, access permissions, and cache and write buffer configuration.

These are created by the operating system software and accessed automatically by

the ARM920T MMU hardware whenever an access causes a TLB miss.

- The ARM920T has a Trace Interface Port that allows the use of Trace hardware and tools for real-time tracing of instructions and data.

## 2.2 About the ARM9TDMI programmer's model

The ARM9TDMI processor core implements ARM architecture v4T, and executes the ARM 32-bit instruction set and the compressed Thumb 16-bit instruction set. The programmer's model is fully described in the *ARM Architecture Reference Manual*. The *ARM9TDMI Technical Reference Manual* gives implementation details, including instruction execution cycle times.

ARMv4T specifies a small number of implementation options. The options selected in the ARM9TDMI implementation are listed in Table 2-1. For comparison, the options selected for the ARM7TDMI implementation are also shown.

Processor<br/>coreArchitectureData Abort<br/>modelValue stored by direct STR,<br/>STRT, and STM of PCARM7TDMIARMv4TBase updatedAddress of instruction + 12ARM9TDMIARMv4TBase restoredAddress of instruction + 12

Table 2-1 ARM9TDMI implementation options

The ARM9TDMI is code-compatible with the ARM7TDMI, with two exceptions:

- The ARM9TDMI core implements the base restored Data Abort model. This significantly simplifies the software Data Abort handler.

- The ARM9TDMI fully implements the instruction set extension spaces added to the ARM (32-bit) instruction set in ARMv4 and ARMv4T.

These differences are explained in more detail in the following sections:

- Data Abort model on page 2-3

- *Instruction set extension spaces* on page 2-4.

#### 2.2.1 Data Abort model

The base restored Data Abort model differs from the base updated Data Abort model implemented by ARM7TDMI.

The difference in the Data Abort models affects only a very small section of operating system code, the Data Abort handler. It does not affect user code. With the base restored Data Abort model, when a Data Abort exception occurs during the execution of a memory access instruction, the base register is always restored by the processor hardware to the value the register contained before the instruction was executed. This removes the requirement for the Data Abort handler to unwind any base register update that might have been specified by the aborted instruction.

#### 2.2.2 Instruction set extension spaces

All ARM processors implement the undefined instruction space as one of the entry mechanisms for the undefined instruction exception. That is, ARM instructions with opcode[27:25] = 0b011 and opcode[4] = 0b1 are undefined on all ARM processors including the ARM9TDMI and ARM7TDMI.

ARMv4 and ARMv4T also introduce a number of instruction set extension spaces to the ARM instruction set. These are:

- arithmetic instruction extension space

- control instruction extension space

- coprocessor instruction extension space

- load/store instruction extension space.

Instructions in these spaces are undefined, and cause an undefined instruction exception. The ARM9TDMI core fully implements all the instruction set extension spaces defined in ARMv4T as undefined instructions, allowing emulation of future instruction set additions.

## 2.3 CP15 register map summary

CP15 defines 16 registers. The register map for CP15 is shown in Table 2-2.

Table 2-2 CP15 register map

| Register | Read                      | Write                     |

|----------|---------------------------|---------------------------|

| 0        | ID code <sup>a</sup>      | Unpredictable             |

| 0        | Cache type <sup>a</sup>   | Unpredictable             |

| 1        | Control                   | Control                   |

| 2        | Translation table base    | Translation table base    |

| 3        | Domain access control     | Domain access control     |

| 4        | Unpredictable             | Unpredictable             |

| 5        | Fault status <sup>b</sup> | Fault status <sup>b</sup> |

| 6        | Fault address             | Fault address             |

| 7        | Unpredictable             | Cache operations          |

| 8        | Unpredictable             | TLB operations            |

| 9        | Cache lockdown b          | Cache lockdown b          |

| 10       | TLB lockdown b            | TLB lockdown b            |

| 11       | Unpredictable             | Unpredictable             |

| 12       | Unpredictable             | Unpredictable             |

| 13       | FCSE PID                  | FCSE PID                  |

| 14       | Unpredictable             | Unpredictable             |

| 15       | Test configuration        | Test configuration        |

Register location 0 provides access to more than one register. The register accessed depends on the value of the opcode\_2 field. See the register description for details.

Separate registers for instruction and data. See the register description for details.

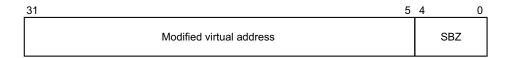

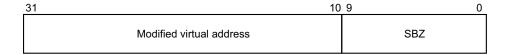

#### 2.3.1 Addresses in ARM920T

Three distinct types of address exist in an ARM920T system:

- Virtual Address (VA)

- Modified Virtual Address (MVA)

- Physical Address (PA).

Below is an example of the address manipulation when the ARM9TDMI core requests an instruction (see Figure 2-10 on page 2-25).

- 1. The *Instruction VA* (IVA) is issued by the ARM9TDMI core.

- 2. This is translated by the ProcID to the *Instruction MVA* (IMVA). It is the IMVA that the *Instruction Cache* (ICache) and MMU see.

- 3. If the protection check carried out by the IMMU on the IMVA does not abort, and the IMVA tag is in the ICache, the instruction data is returned to the ARM9TDMI core.

- 4. If the ICache misses (the IMVA tag is not in the ICache), then the IMMU performs a translation to produce the *Instruction PA* (IPA). This address is given to the AMBA bus interface to perform an external access.

Table 2-3 Address types in ARM920T

| Domain  | ARM9TDMI     | Caches and TLBs        | AMBA bus      |

|---------|--------------|------------------------|---------------|

| Address | Virtual (VA) | Modified Virtual (MVA) | Physical (PA) |

### 2.3.2 Accessing CP15 registers

The terms and abbreviations shown in Table 2-4 are used throughout this section.

Table 2-4 CP15 abbreviations

| Term           | Abbreviation | Description                                                                                                                                                                                                                   |

|----------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Unpredictable  | UNP          | For reads, the data returned when reading from this location is unpredictable. It can have any value. For writes, writing to this location causes unpredictable behavior, or an unpredictable change in device configuration. |

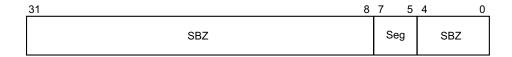

| Should be zero | SBZ          | When writing to this location, all bits of this field should be 0.                                                                                                                                                            |

In all cases, reading from, or writing any data values to any CP15 registers, including those fields specified as *unpredictable* or *should be zero*, does not cause any permanent damage.

All CP15 register bits that are defined and contain state, are set to zero by **BnRES** except the V bit in register 1, which takes the value of macrocell input **VINITHI** when **BnRES** is asserted.

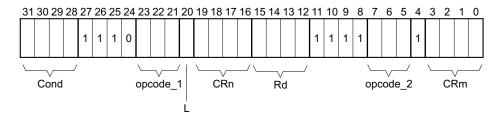

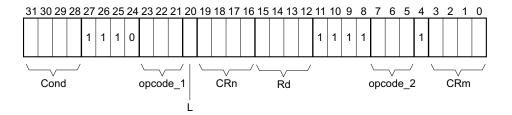

You can only access CP15 registers with MRC and MCR instructions in a privileged mode. The instruction bit pattern of the MCR and MRC instructions is shown in Figure 2-1. The assembler for these instructions is:

MCR/MRC{cond} P15,opcode\_1,Rd,CRn,CRm,opcode\_2

Figure 2-1 CP15 MRC and MCR bit pattern

Instructions CDP, LDC, and STC, together with unprivileged MRC and MCR instructions to CP15, cause the undefined instruction trap to be taken. The CRn field of MRC and MCR instructions specifies the coprocessor register to access. The CRm field and opcode\_2 fields specify a particular action when addressing registers. The L bit distinguishes between an MRC (L=1) and an MCR (L=0).

Attempting to read from a nonreadable register, or to write to a nonwritable register causes unpredictable results.

The opcode\_1, opcode\_2, and CRm fields should be zero, except when the values specified are used to select the desired operations, in all instructions that access CP15. Using other values results in unpredictable behavior.

#### 2.3.3 Register 0, ID code register

This is a read-only register that returns a 32-bit device ID code.

You can access the ID code register by reading CP15 register 0 with the opcode\_2 field set to any value other than 1 (the CRm field should be zero when reading). For example:

MRC p15,0,Rd,c0,c0,0 ; returns ID register

The contents of the ID code are shown in Table 2-5.

Table 2-5 Register 0, ID code

| Register bits | Function               | Value    |

|---------------|------------------------|----------|

| 31:24         | Implementer            | 0x41     |

| 23:20         | Specification revision | 0x1      |

| 19:16         | Architecture (ARMv4T)  | 0x2      |

| 15:4          | Part number            | 0x920    |

| 3:0           | Layout revision        | Revision |

### 2.3.4 Register 0, cache type register

This is a read-only register that contains information about the size and architecture of the caches, allowing operating systems to establish how to perform such operations as cache cleaning and lockdown. All ARMv4T and later cached processors contain this register, allowing RTOS vendors to produce future-proof versions of their operating systems.

You can access the cache type register by reading CP15 register 0 with the opcode\_2 field set to 1. For example:

MRC p15,0,Rd,c0,c0,1; returns cache details

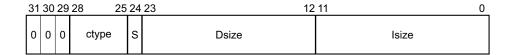

The format of the cache type register is shown in Figure 2-2.

Figure 2-2 Cache type register format

**ctype** The ctype field determines the cache type.

**S bit** Specifies whether the cache is a unified cache or separate instruction and

data caches.

**Dsize** Specifies the size, line length, and associativity of the data cache.

**Isize** Specifies the size, line length, and associativity of the instruction cache.

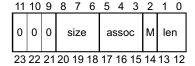

The Dsize and Isize fields in the cache type register have the same format. This is shown in Figure 2-3.

Figure 2-3 Dsize and Isize field format

**size** The size field determines the cache size in conjunction with the M bit.

**assoc** The assoc field determines the cache associativity in conjunction with the

M bit.

**M bit** The multiplier bit. Determines the cache size and cache associativity

values in conjunction with the size and assoc fields.

**len** The len field determines the line length of the cache.

The register values for the ARM920T cache type register are listed in Table 2-6.

**Table 2-6 Cache type register format**

| Function |          | Register bits | Value                              |

|----------|----------|---------------|------------------------------------|

| Reserved | l        | 31:29         | 0b000                              |

| ctype    |          | 28:25         | 0b0110                             |

| S        |          | 24            | 0b1 = Harvard cache                |

| Dsize    | Reserved | 23:21         | 0b000                              |

|          | size     | 20:18         | 0b101 = 16KB                       |

|          | assoc    | 17:15         | 0b110 = 64-way                     |

|          | M        | 14            | 0b0                                |

|          | len      | 13:12         | 0b10 = 8 words per line (32 bytes) |

| Isize    | Reserved | 11:9          | 0b000                              |

|          | size     | 8:6           | 0b101 = 16KB                       |

|          | assoc    | 5:3           | 0b110 = 64-way                     |

|          | M        | 2             | 0b0                                |

|          | len      | 1:0           | 0b10 = 8 words per line (32 bytes) |

Bits [28:25] indicate which major cache class the implementation falls into. 0x6 means that the cache provides:

- cache-clean-step operation

- cache-flush-step operation

- lockdown facilities.

The size of the cache is determined by the size field and the M bit. The M bit is 0 for the data and instruction caches. Bits [20:18] for the *Data Cache* (DCache) and bits [8:6] for the *Instruction Cache* (ICache) are the size field. Table 2-7 shows the cache size encoding.

Table 2-7 Cache size encoding (M=0)

| size field | Cache size |

|------------|------------|

| 0b000      | 512B       |

| 0b001      | 1KB        |

| 0b010      | 2KB        |

| 0b011      | 4KB        |

| 0b100      | 8KB        |

| 0b101      | 16KB       |

| 0b110      | 32KB       |

| 0b111      | 64KB       |

The associativity of the cache is determined by the assoc field and the M bit. The M bit is 0 for the data and instruction caches. Bits [17:15] for the DCache and bits [5:3] for the ICache are the assoc field. Table 2-8 shows the cache associativity encoding.

Table 2-8 Cache associativity encoding (M=0)

| assoc field | Associativity |

|-------------|---------------|

| 0b000       | Direct mapped |

| 0b001       | 2-way         |

| 0b010       | 4-way         |

| 0b011       | 8-way         |

| 0b100       | 16-way        |

| 0b101       | 32-way        |

| 0b110       | 64-way        |

| 0b111       | 128-way       |

|             | <u> </u>      |

The line length of the cache is determined by the len field. Bits [13:12] for the DCache and bits [1:0] for the ICache are the len field. Table 2-9 shows the line length encoding.

Table 2-9 Line length encoding

| len field | Cache line length   |  |

|-----------|---------------------|--|

| 00        | 2 words (8 bytes)   |  |

| 01        | 4 words (16 bytes)  |  |

| 10        | 8 words (32 bytes)  |  |

| 11        | 16 words (64 bytes) |  |

#### 2.3.5 Register 1, control register

This register contains the control bits of the ARM920T. All reserved bits must either be written with 0 or 1, as indicated, or written using read-modify-write. The reserved bits have an unpredictable value when read. Use the following instructions to read and write this register:

```

MRC p15, 0, Rd, c1, c0, 0 ; read control register MCR p15, 0, Rd, c1, c0, 0 ; write control register

```

All defined control bits are set to 0 on reset, except the V bit. The V bit is set to 0 at reset if the **VINITHI** pin is LOW, or 1 if the **VINITHI** pin is HIGH. The functions of the control bits are shown in Table 2-10.

Table 2-10 Control register 1 bit functions

| Register<br>bits | Name   | Function                             | Value                                                               |

|------------------|--------|--------------------------------------|---------------------------------------------------------------------|

| 31               | iA bit | Asynchronous clock select            | See Table 2-11 on page 2-14.                                        |

| 30               | nF bit | notFastBus select                    | See Table 2-11 on page 2-14.                                        |

| 29:15            | -      | Reserved                             | Read = Unpredictable. Write = Should be zero.                       |

| 14               | RR bit | Round robin replacement              | 0 = Random replacement.<br>1 = Round-robin replacement.             |

| 13               | V bit  | Base location of exception registers | 0 = Low addresses = 0x00000000.<br>1 = High addresses = 0xFFFF0000. |

Table 2-10 Control register 1 bit functions (continued)

| Register<br>bits | Name  | Function               | Value                                                                                             |

|------------------|-------|------------------------|---------------------------------------------------------------------------------------------------|

| 12               | I bit | ICache enable          | 0 = ICache disabled.<br>1 = ICache enabled.                                                       |

| 11:10            | -     | Reserved               | Read = 00.<br>Write = 00.                                                                         |

| 9                | R bit | ROM protection         | This bit modifies the MMU protection system. See <i>Domain access control</i> on page 3-23.       |

| 8                | S bit | System protection      | This bit modifies the MMU protection system. See <i>Domain access control</i> on page 3-23.       |

| 7                | B bit | Endianness             | 0 = Little-endian operation.<br>1 = Big-endian operation.                                         |

| 6:3              | -     | Reserved               | Read = 1111.<br>Write = 1111.                                                                     |

| 2                | C bit | DCache enable          | 0 = DCache disabled.<br>1 = DCache enabled.                                                       |

| 1                | A bit | Alignment fault enable | Data address alignment fault checking.  0 = Fault checking disabled.  1 = Fault checking enabled. |

| 0                | M bit | MMU enable             | 0 = MMU disabled.<br>1 = MMU enabled.                                                             |

Register 1 bits [31:30] select the clocking mode of the ARM920T, as shown in Table 2-11.

Table 2-11 Clocking modes

| Clocking mode | iA | nF |

|---------------|----|----|

| FastBus mode  | 0  | 0  |

| Synchronous   | 0  | 1  |

| Reserved      | 1  | 0  |

| Asynchronous  | 1  | 1  |

#### **Enabling the MMU**

You must take care with the address mapping of the code sequence used to enable the MMU (see *Enabling the MMU* on page 3-29).

See *Enabling and disabling the ICache* on page 4-6 and *Enabling and disabling the DCache and write buffer* on page 4-10 for the restrictions and the effects of having caches enabled with the MMU disabled.

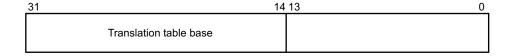

# 2.3.6 Register 2, translation table base (TTB) register

This is the *Translation Table Base* (TTB) register, for the currently active first-level translation table. The contents of register 2 are shown in Table 2-12.

Table 2-12 Register 2, translation table base

| Register<br>bits | Function                                                   |

|------------------|------------------------------------------------------------|

| 31:14            | Pointer to first-level translation table base. Read/write. |

| 13:0             | Reserved: Read = Unpredictable. Write = Should be zero.    |

Reading from register 2 returns the pointer to the currently active first-level translation table in bits [31:14]. Writing to register 2 updates the pointer to the first-level translation table from bits [31:14] of the written value.

Bits [13:0] should be zero when written, and are unpredictable when read.

You can use the following instructions to access the TTB:

MRC p15, 0, Rd, c2, c0, 0 ; read TTB register MCR p15, 0, Rd, c2, c0, 0 ; write TTB register

#### 2.3.7 Register 3, domain access control register

Register 3 is the read and write domain access control register, consisting of 16 2-bit fields. Each of these 2-bit fields defines the access permissions for the domains shown in Table 2-13.

Table 2-13 Register 3, domain access control

| Register<br>bits | Domain |

|------------------|--------|

| 31:30            | D15    |

| 29:28            | D14    |

| 27:26            | D13    |

| 25:24            | D12    |

| 23:22            | D11    |

| 21:20            | D10    |

| 19:18            | D9     |

| 17:16            | D8     |

| 15:14            | D7     |

| 13:12            | D6     |

| 11:10            | D5     |