Semiconductor Inc.

1,048,576 x 32 CMOS High Speed Dynamic RAM

#### **Features**

Row Access Times of 80/100/120 ns

Onboard Address Latching

Onboard Address Multiplexing

Byte Write Facility

CAS Before RAS Refresh

RAS Only Refresh

Directly TTL Compatible

MemConfig Option for Transputer Applications

1024 Cycle Refresh in 16 ms (max)

#### **Block Diagram**

# 1M x 32 DRAM

# MD321000FKX-80/10/12

Issue 1.0 July 1990

# ADVANCE PRODUCT INFORMATION

| Absolute Maximum Ratings (1)    |                            |          |  |

|---------------------------------|----------------------------|----------|--|

| Voltage Range on any pin        | -1 to V <sub>cc</sub> +0.3 | V        |  |

| Voltage Range on V <sub>∞</sub> | 0 to 7                     | V        |  |

| Short Circuit Output Current    | 50                         | mA       |  |

| Power Dissipation               | 8                          | W        |  |

| Storage Temperature             | -65 to +150                | <b>℃</b> |  |

Notes: (1) Stresses above those listed may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| <b>Recommended Operati</b> | ng Cond         | itions |     |                      |                 |

|----------------------------|-----------------|--------|-----|----------------------|-----------------|

|                            |                 | min    | typ | max                  |                 |

| Supply Voltage             | $V_{\infty}$    | 4.5    | 5.0 | 5.5                  | V               |

| Input High Voltage         | VIH             | 2.4    | -   | V <sub>CC</sub> +0.3 | V               |

| Input Low Voltage          | V <sub>IL</sub> | -1     | -   | 8.0                  | V               |

| Output High Voltage        | V <sub>IL</sub> | 2.4    | -   | V <sub>CC</sub> +0.3 | V               |

| Output Low Voltage         | Vol             | -1     | -   | 8.0                  | · <b>V</b>      |

| Operating Temperature      | T,              | 0      | -   | 70                   | °C              |

|                            | Tai             | -40    | -   | 85                   | °C (321000FKXI) |

| DC Electrical Characteristics (V        | . Ellisant E ann - Eanni |

|-----------------------------------------|--------------------------|

| III : Floctrical i maractorietice /\/   | / _6\/+10%   _0% +6 ,70% |

| DO LICCII IVAI DI IAI ACICII SI ICS ( V |                          |

|                          |                  |                      |       | -80 | -1    | 0   | -:    | 12  |      |

|--------------------------|------------------|----------------------|-------|-----|-------|-----|-------|-----|------|

| Parameter                | Symbol           | Test Condition       | min   | max | min   | max | min   | max | Unit |

| Input Leakage Current    | -                |                      |       |     |       |     |       |     |      |

| CAS, RAS, MemWrB0-3, OE  | l <sub>n</sub> , |                      | -80   | +80 | -80   | +80 | -80   | +80 | μА   |

| AD2 - A <u>D19</u>       | الع              | ٠                    | -600  | +20 | -600  | +20 | -600  | +20 | μA   |

| ALE                      | l <sub>Lt3</sub> |                      | -1200 | +40 | -1200 | +40 | -1200 | +40 | μΑ   |

| AMUX                     | LH               |                      | -1800 | +60 | -1800 | +60 | -1800 | +60 | μΑ   |

| I/O Leakage Current      | l <sub>lvo</sub> |                      | -80   | +80 | -80   | +80 | -80   | +80 | μΑ   |

| Read/Write Cycle Current | l <sub>cc1</sub> |                      | -     | 805 | -     | 725 | -     | 645 | mΑ   |

| Standby Current          | l <sub>cc2</sub> | V <sub>H</sub> =5.5V | -     | 110 | -     | 110 | -     | 110 | mΑ   |

| Average Refresh Current  | I <sub>CC3</sub> | ••                   | -     | 805 | -     | 725 | -     | 645 | mΑ   |

# Capacitance (V<sub>cc</sub>=5V±10%,T<sub>A</sub>=25°C)

| Parameter       |              | Symbol           | Test Condition                     | typ | max | Unit |

|-----------------|--------------|------------------|------------------------------------|-----|-----|------|

| I/P Capacitance | CAS, RAS, OE | C <sub>IN1</sub> | V <sub>IN1</sub> = 0V              |     | 56  | pF   |

|                 | MemWrB0-3    | C <sub>IN2</sub> | $V_{iN2} = 0V$                     | -   | 14  | pF   |

|                 | ALE          | Civis            | $V_{\text{INS}}^{\text{INS}} = 0V$ | -   | 10  | pF   |

|                 | AMUX         | C <sub>IN4</sub> | $V_{\rm IN4}^{\rm ISS} = 0V$       | -   | 15  | pF   |

| I/O Capacitance | AD0 - AD31   | C <sub>M</sub>   | $V_{VO} = 0V$                      | -   | 17  | pF   |

# **AC Test Conditions**

- \* Input pulse levels: Gnd to 3.0V

- \* Input rise and fall times: 5ns

- \* Input and Output timing reference levels: 1.5V

\* Output load: 1 TTL gate + 100pF

- \* Vc=5V±10%

# **Electrical Characteristics & Recommended AC Operating Conditions**

|                                                                              |                                        |          | 30    |            | -10   | -12     |       |      |        |

|------------------------------------------------------------------------------|----------------------------------------|----------|-------|------------|-------|---------|-------|------|--------|

| Parameter                                                                    | Symbol                                 | min      | max   | min        | max   | min     | max   | Unit | Note   |

| Read Cycle Time                                                              | t <sub>RC</sub>                        | 160      | -     | 190        | -     | 220     | •     | ns   | _ 2    |

| Transition Time                                                              | t <sub>T</sub>                         | 3        | 50    | 3          | 50    | 3       | 50    | ns   |        |

| Non-static Column Decode Mode                                                | •                                      |          |       |            |       |         |       |      |        |

| Pulse Duration, RAS Low                                                      | t <sub>ras</sub>                       | 80       | 10000 | 100        | 10000 | 120     | 10000 | กร   |        |

| Delay Time, RAS Low to CAS Low                                               | tRCD                                   | 22       | 55    | 25         | 75    | 25      | 90    | ns   | 8,1    |

| Delay Time, CAS Low to RAS High                                              | t <sub>RSH</sub>                       | 25       | -     | 25         | -     | 25      | -     | ns   | 8      |

| Pulse Duration, RAS High (Precharge)                                         | t <sub>RP</sub>                        | 70       | -     | 80         | -     | 90      | •     | ns   |        |

| Delay Time, RAS Low to CAS High                                              | t <sub>CSH</sub>                       | 80       | -     | 100        | -     | 120     | -     | ns   |        |

| Pelay Time, CAS High to RAS Low                                              | tCRP                                   | 10       | -     | 10         | -     | 10      | •     | ns   |        |

| Pulse Duration, CAS Low                                                      | tcas                                   | 25       | 10000 | 25         | 10000 | 30      | 10000 | ns   |        |

| Column Address Setup Time Before                                             | CAS                                    |          |       |            |       |         |       |      |        |

| CAS Low                                                                      | tasc                                   | 20       | -     | 20         | -     | 20      | -     | ns   |        |

| Pulse Duration, CAS High                                                     | t <sub>CP</sub>                        | 10       | -     | 10         | •     | 10      | •     | ns   |        |

| Row Address Hold Time After RAS Low                                          | t <sub>rah</sub>                       | 12       | -     | 15         | •     | 15      |       | ns   |        |

| Row Address Setup Time Before RAS Low                                        | t t                                    | 10       | -     | 10         | -     | 10      | _     | ns   |        |

| Delay Time, Column Address to RAS High                                       |                                        | 60       | -     | 65         | -     | 75      | -     | ns   |        |

| Column Address Hold Time After RAS Low                                       |                                        | 75       | -     | 85         | -     | 110     | -     | ns   | 7      |

| Read Hold Time After RAS High                                                | t <sub>RRH</sub>                       | 10       | -     | 10         | -     | 10      | •     | ns   | •      |

| Read Setup Time Before CAS Low                                               | 4                                      | 0        | -     | 0          | -     | 0       | •     | ns   |        |

| Column Address Hold Time After CAS Low                                       | t <sub>rcs</sub><br>/ t <sub>cah</sub> | 15       | -     | 20         | •     | 25      |       | ns   |        |

| Read Hold Time After CAS High                                                | OAN                                    | 0        |       | 0          | -     | 0       | -     | ns   |        |

| ccess Time From CAS Low                                                      | t <sub>RCH</sub>                       |          | 25    | -          | 25    | -       | 30    | ns   |        |

| Output Disable Time After CAS High                                           | CAC                                    | 0        | 20    | 0          | 25    | 0       | 30    | ns   | 1      |

| Access Time From RAS Low                                                     | t<br>t                                 | -        | 80    |            | 100   | -       | 120   | ns   | •      |

| Access Time From OE Low_                                                     | t <sub>rac</sub>                       | _        | 25    | _          | 25    | _       | 30    | ns   |        |

| Output Disable Time After OE High                                            | t GAC                                  | 0        | 20    | 0          | 25    | 0       | 30    | ns   | 1      |

| Vrite Cycle Time                                                             | GOFF                                   | 160      | -     | 190        | -     | 220     | -     |      | •      |

| Vrite Cycle Tillie<br>Vrite Pulse Duration                                   | <sup>t</sup> wc                        | 15       | -     | 20         | -     | 25      | _     | ns   |        |

| Vrite Hold Time After RAS Low                                                | <sup>T</sup> WP                        | 70       |       | <b>8</b> 5 | -     | 110     | -     | ns   |        |

| MemWr Low Setup Time Before CAS High                                         | WCR                                    | 25       | -     | 25         | -     | 30      | -     | ns   | 6      |

| NemWr Low Setup Time Before CAS Ingri<br>NemWr Low Setup Time Before CAS Low | OHL                                    | 25<br>0  |       | 25<br>0    | -     |         | -     | ns   |        |

| Vrite Hold Time After CAS Low                                                | twcs                                   | 15       | -     | 20         |       | 0<br>25 | •     | ns   | 6      |

|                                                                              | twcH                                   |          |       |            | •     |         | •     | ns   |        |

| MemWr Low Setup Time <u>Befo</u> re RAS High                                 | 1144                                   | 25       | -     | 25         | •     | 30      | -     | กร   | _      |

| Data Setup Time Before CAS Low                                               | tosc                                   | 0        | •     | 0          | •     | 0       | •     | ns   | 5      |

| Data Hold Time After CAS Low                                                 | DHC                                    | 15<br>75 | -     | 20         | •     | 25      | •     | ns   | 5      |

| Data Hold Time After RAS Low                                                 | DHR                                    | 75       | -     | 90         | -     | 120     | -     | ns   | 7<br>5 |

| Oata Setup Time Before MemWr Low                                             | t <sub>DSW</sub>                       | 0        | -     | 0          | •     | 0       | -     | ns   | •      |

| Data Hold Time After MemWr Low                                               | DHW                                    | 15       | -     | 20         | -     | 25      | •     | ns   | 5      |

| Delay Time, OE High Before Data valid                                        | tapp                                   | 25       | •     | 25         | •     | 30      | -     | ns   | _      |

| Delay Time RAS high to CAS low                                               | t <sub>RPC</sub>                       | 10       | -     | 10         | •     | 10      | •     | ns   | 3      |

| Delay Time CAS low to RAS low                                                | CSR                                    | 10       | -     | 10         | -     | 10      | •     | ns   | 3      |

| Delay Time RAS low to CAS high                                               | t <sub>CHR</sub>                       | 20       | •     | 20         | -     | 25      | •     | ns   | 3      |

| Delay Time Address valid to ALE low                                          | t <sub>lal</sub>                       | 10       | -     | 10         | •     | 10      | -     | ns   |        |

| Delay Time ALE low to Address not valid                                      | t <sub>LHL</sub>                       | 13       | •     | 13         | •     | 13      | -     | ns   |        |

| Delay Time ALE high to Address valid                                         | t <sub>LHH</sub>                       | 13       | •     | 13         | •     | 13      | •     | ns   |        |

| ALE Pulse Duration, High                                                     | t <sub>P</sub>                         | 4        | -     | 4          | •     | 4       | -     | ns   |        |

| Address Latch Setup Time                                                     |                                        | 13       |       | 13         |       | 13      |       |      |        |

- 1. t<sub>off</sub> and t<sub>aoff</sub> are specified when the output is no longer driven.

2. All cycle times assume t<sub>r</sub>=5ns.

3. CAS before RAS refresh only.

5. Later of CAS or MemWr in write operation.

6. Early write operation only.

7. The minimum value is measured when t<sub>RAD</sub> is set to t<sub>RAD</sub> min as a reference.

8. Read cycle only.

- 8. Read cycle only.

9. Write cycle only.

10. Maximum value specified only to guarantee access time.

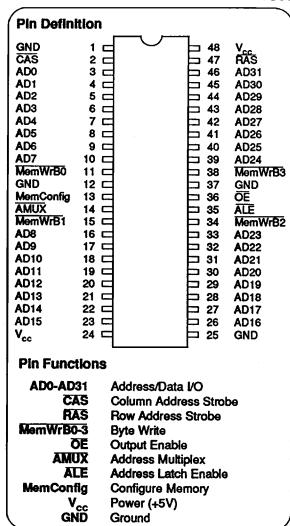

#### DESCRIPTION

The MD321000FKX is a high speed 33,554,432 bit Dynamic Random Access Memory organised as 1,048,576 words of 32 bits each. Although designed primarily for use with Transputers, it can be used with any system which supports Dynamic Memory and a 32 bit Multiplexed Address / Data Bus. Information on interfacing this part with both Transputers and other systems is given below.

### TRANSPUTER OPERATION

Four different Memory Configuration options are provided via the MemConfig pin. This pin is connected, at the manufacturing stage, to one of the Address / Data pins AD4, AD5, AD6, AD7, the particular option specified by the customer when ordering. This allows for a wide range of memory speed and Transputer speed configurations to be used, depending on the application, as shown in the table below.

|        |         | TRANSPUTER SPEED MHz |   |                 |   |   |    |   |         |   |   |   |

|--------|---------|----------------------|---|-----------------|---|---|----|---|---------|---|---|---|

| MEMORY | 20      |                      |   | 25              |   |   | 30 |   |         |   |   |   |

| SPEED  | AD LINK |                      |   | AD LINK AD LINK |   |   |    | K | AD LINK |   |   | K |

| (ns)   | 4       | 5                    | 6 | 7               | 4 | 5 | 6  | 7 | 4       | 5 | 6 | 7 |

| 80     | •       | •                    | • | •               | • | • | •  | • |         |   |   | • |

| 100    | •       | •                    | • | •               |   |   |    | • |         |   |   | • |

| 120    |         |                      |   | •               |   |   |    | • |         |   |   | • |

Indicates allowable combination.

Connections to the Transputer are as follows:

| Transputer Pin | MD321000 Pin |

|----------------|--------------|

| MemnotWrD0     | AD0          |

| MemnotRfD1     | AD1          |

| MemAD2-MemAD31 | AD2-AD31     |

| notMemS0       | ALE          |

| notMemS1       | RAS          |

| notMemS2       | <b>AMUX</b>  |

| notMemS3       | CAS          |

| MemConfig      | MemConfig    |

| notMemRd       | ŌĒ           |

| notMemWrB0-3   | MemWrB0-3    |

#### **GENERAL OPERATION**

The MD321000 is a 1M x 32 bit Dynamic Memory with a multiplexed Address / Data bus. This device has on board address latches and address multiplexing, which reduces the complexity of external circuitry. This data sheet descibes the use of this memory in normal READ and WRITE modes and EARLY WRITE mode, as well as two types of REFRESH.

#### Address AD2 - AD21

20 Address bits are required to decode 1 of 1M locations. This 20 bit address is converted by the on board circuitry to two 10 bit addresses for use by the 1M x 4 DRAMS used, and strobed into the DRAMS by using the RAS and CAS control inputs.

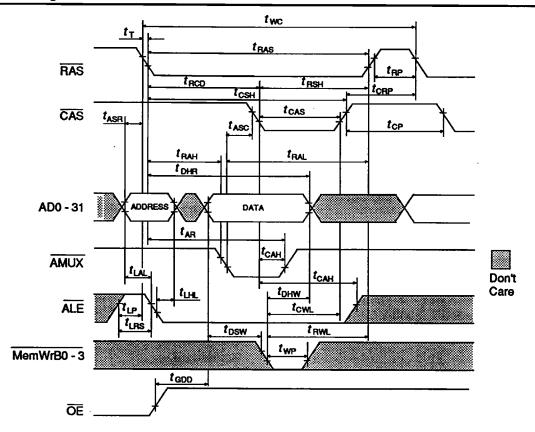

#### MemWrB0 - MemWrB3

The READ or WRITE mode is selected by these inputs, a separate input provided for each byte, the least significant byte controlled by MemWrB0. A logic high on these inputs selects the READ mode and a logic low selects the WRITE mode. The data input is disabled when READ mode is selected. When MemWrB0-3 go low prior to CAS (early write), data out will remain in the high impedance state for the entire cycle, permitting a WRITE operation with  $\overline{OE}$  grounded.

#### Data IN ADO - AD31

Data is written during a WRITE or EARLY WRITE cycle. In an EARLY WRITE cycle, MemWrB0-3 are brought low before CAS and the data is strobed by CAS. In a WRITE cycle, CAS is already low so the data is strobed in by MemWrB0-3; note that OE must be high to put the output buffers into a high impedance state before placing data onto AD0 - AD31.

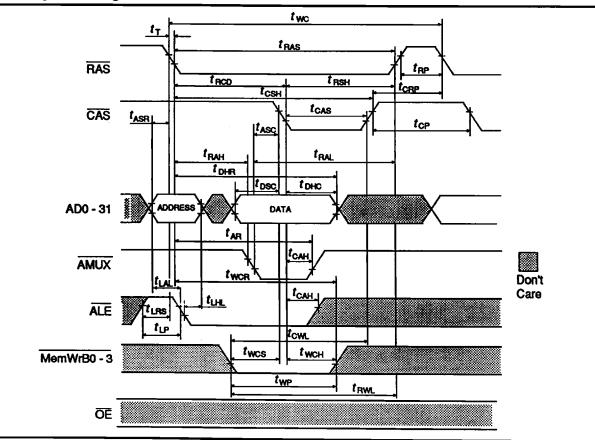

See diagrams showing WRITE and EARLY WRITE-waveforms for detailed timing.

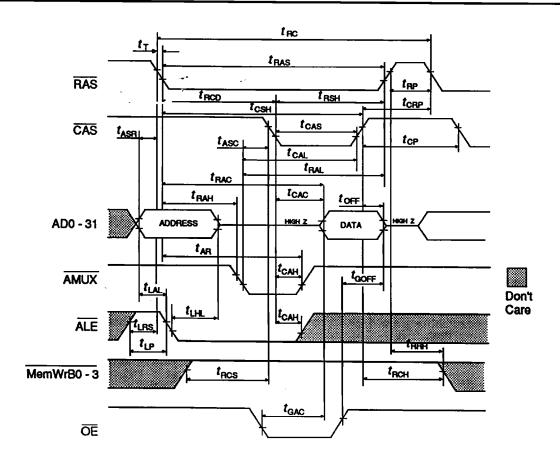

#### Data OUT AD0 - AD31

The three state output buffer is in the high impedance state until both  $\overline{CAS}$  and  $\overline{RAS}$  are brought low. In a READ cycle the output becomes valid after the access time interval  $t_{CAC}$ , and remains valid while  $\overline{CAS}$  and  $\overline{OE}$  are low. Either  $\overline{CAS}$  or  $\overline{OE}$  going high returns it to the high impedance state.

See diagram showing READ waveform for detailed timing.

## Output Enable OE

When  $\overline{OE}$  is high the output buffers are in the high impedance state. Bringing  $\overline{OE}$  low during a normal cycle will place the output buffers in the low impedance state, as long as  $\overline{RAS}$  and  $\overline{CAS}$  are low as well. If either  $\overline{OE}$  or  $\overline{CAS}$  are brought high the buffers will return to the high impedance state.

## Address Latch Enable ALE

On the high to low transition of ALE the address on the lines AD2 - AD21 is latched, and remains latched until ALE goes high. With ALE high these latches operate transparently i.e. the data on the outputs follows the inputs.

## Address Latch Multiplex AMUX

When AMUX is high the address on AD2 - AD11 (row address) is presented to the DRAMS and is latched onto them when RAS goes low. When AMUX is low the address on AD12 - AD21 is used, and latched onto the DRAMS when CAS goes low.

## Refresh RAS Only

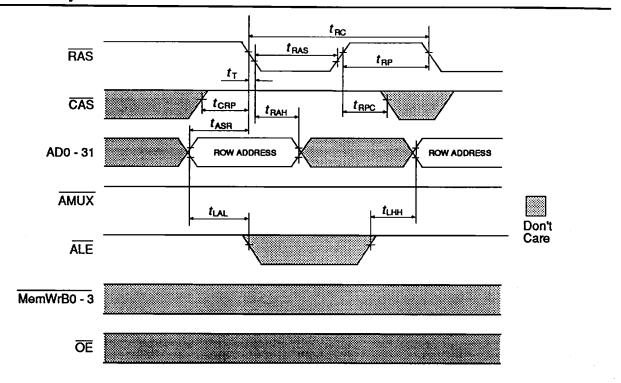

A refresh operation must be performed once every 16ms to retain stored data, achieved by strobing one of the 1024 rows. A normal READ or WRITE cycle will refresh all of the bits in each row that is selected. For RAS only refresh, CAS is held high and an externally generated row address must be supplied on AD2 - AD11.

See diagram showing  $\overline{\text{RAS}}$  only refresh for detailed timing.

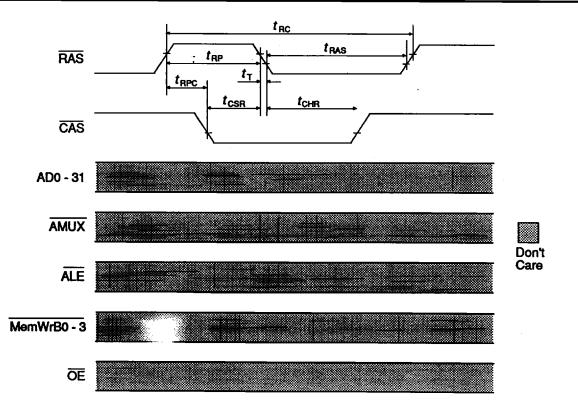

### Refresh CAS Before RAS

The refresh address can be generated automatically by bringing CAS low earlier than RAS and holding it low while cycling RAS. In this mode the external address is ignored.

# **Power Up**

To achieve correct device operation, after  $V_{\rm cc}$  has reached its full level a delay of 200 $\mu$ s is required followed by eight initialisation cycles (READ, WRITE or REFRESH).

# **Read Cycle Timing Waveform**

# Write Cycle Timing Waveform

# **Early Write Cycle Timing Waveform**

# Refresh RAS Only

# Refresh CAS Before RAS

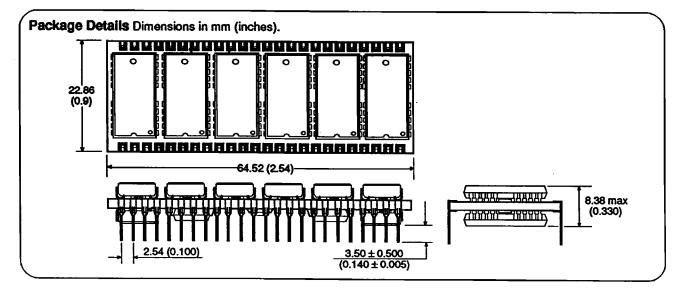

# Ordering Information

#### MD321000FKXI-12/AD4 **Transputer Option** AD4 = Link to MemAD4 AD5 = Link to MemAD5 AD6 = Link to MemAD6 AD7 = Link to MemAD7 Module Speed 80 = 80 ns 10 = 100 ns12 = 120 nsTemp. range/screening Blank = Commercial Temp. = Industrial Temp. **Package FKX** = Plastic DIL **Memory Arrangement** $321000 = 1M \times 32 bit$