# **Product Specification**

# 10Gb/s, 10km XFP Optical Transceiver

# FTLX1413M3BCL

### **PRODUCT FEATURES**

- Supports 8.5Gb/s to 11.32Gb/s bit rates

- Power dissipation <1.5W

- Commercial temperature range: -5°C to 75°C

- RoHS-6 Compliant (lead-free)

- Hot-pluggable XFP footprint

- Single Power supply: 3.3V

- Maximum link length of 10km

- Uncooled 1310nm DFB laser

- No Reference Clock required

- Built-in digital diagnostic functions

### **APPLICATIONS**

- SONET/SDH OC-192 SR-1 ITU G.693, VSR2000-2R1

- 10GBASE-LR /LW 10G Ethernet

- 1200-SM-LL-L 10G Fibre Channel and 800-SM-LC-L 8G Fibre Channel

- ITU G.709 OTN/FEC OTU1e, OTU2, OTU2e

- 10G CPRI

Finisar's FTLX1413M3BCL Small Form Factor 10Gb/s (XFP) transceivers are compliant with the current XFP Multi-Source Agreement (MSA) Specification<sup>1</sup>. They are a true multi-protocol transceiver complying with SONET OC-192 SR-1, SDH STM I-64.1, 10-Gigabit Ethernet 10GBASE-LR /LW per IEEE 802.3ae, 10G Fibre Channel 1200-SM-LL-L, 8G Fibre Channel 800-SM-LC-L, 10G CPRI, and ITU-T. G709 OTN/FEC protocols OTU1e, OTU2, and OTU2e. Digital diagnostics functions are available via a 2-wire serial interface, as specified in the XFP MSA. The transceiver is RoHS compliant and lead free per Directive 2002/95/EC<sup>3</sup>, and Finisar Application Note AN-2038<sup>4</sup>.

### PRODUCT SELECTION

# FTLX1413M3BCL

# I. Pin Descriptions

| Pin | Logic   | Symbol     | Name/Description                                              | Ref. |

|-----|---------|------------|---------------------------------------------------------------|------|

| 1   |         | GND        | Module Ground                                                 | 1    |

| 2   |         | VEE5       | Optional –5.2 Power Supply – <b>Not required</b>              |      |

| 3   | LVTTL-I | Mod-Desel  | Module De-select; When held low allows the module to          |      |

|     |         |            | respond to 2-wire serial interface commands                   |      |

| 4   | LVTTL-O | Inda amand | Interrupt (bar); Indicates presence of an important condition | 2    |

|     |         | Interrupt  | which can be read over the serial 2-wire interface            |      |

| 5   | LVTTL-I | TX_DIS     | Transmitter Disable; Transmitter laser source turned off      |      |

| 6   |         | VCC5       | +5 Power Supply– <b>Not required</b>                          |      |

| 7   |         | GND        | Module Ground                                                 | 1    |

| 8   |         | VCC3       | +3.3V Power Supply                                            |      |

| 9   |         | VCC3       | +3.3V Power Supply                                            |      |

| 10  | LVTTL-I | SCL        | Serial 2-wire interface clock                                 | 2    |

| 11  | LVTTL-  | SDA        | Serial 2-wire interface data line                             | 2    |

|     | I/O     |            |                                                               |      |

| 12  | LVTTL-O | Mod_Abs    | Module Absent; Indicates module is not present. Grounded      | 2    |

|     |         |            | in the module.                                                |      |

| 13  | LVTTL-O | Mod_NR     | Module Not Ready; Finisar defines it as a logical OR          | 2    |

|     |         |            | between RX_LOS and Loss of Lock in TX/RX.                     |      |

| 14  | LVTTL-O | RX_LOS     | Receiver Loss of Signal indicator                             | 2    |

| 15  |         | GND        | Module Ground                                                 | 1    |

| 16  |         | GND        | Module Ground                                                 | 1    |

| 17  | CML-O   | RD-        | Receiver inverted data output                                 |      |

| 18  | CML-O   | RD+        | Receiver non-inverted data output                             |      |

| 19  |         | GND        | Module Ground                                                 | 1    |

| 20  |         | VCC2       | +1.8V Power Supply – <b>Not required</b>                      |      |

| 21  | LVTTL-I | P_Down/RST | Power Down; When high, places the module in the low           |      |

|     |         |            | power stand-by mode and on the falling edge of P_Down         |      |

|     |         |            | initiates a module reset                                      |      |

|     |         |            | Reset; The falling edge initiates a complete reset of the     |      |

|     |         |            | module including the 2-wire serial interface, equivalent to a |      |

|     |         |            | power cycle.                                                  |      |

| 22  |         | VCC2       | +1.8V Power Supply – <b>Not required</b>                      |      |

| 23  |         | GND        | Module Ground                                                 | 1    |

| 24  | PECL-I  | RefCLK+    | Reference Clock non-inverted input, AC coupled on the         | 3    |

|     |         |            | host board – <b>Not required</b>                              |      |

| 25  | PECL-I  | RefCLK-    | Reference Clock inverted input, AC coupled on the host        | 3    |

|     |         |            | board – Not required                                          |      |

| 26  |         | GND        | Module Ground                                                 | 1    |

| 27  |         | GND        | Module Ground                                                 | 1    |

| 28  | CML-I   | TD-        | Transmitter inverted data input                               |      |

| 29  | CML-I   | TD+        | Transmitter non-inverted data input                           |      |

| 30  |         | GND        | Module Ground                                                 | 1    |

# Notes:

- 1. Module circuit ground is isolated from module chassis ground within the module.

- 2. Open collector; should be pulled up with 4.7k 10kohms on host board to a voltage between 3.15V and 3.6V.

- 3. A Reference Clock input is not required by the FTLX1413M3BCL. If present, it will be ignored.

Diagram of Host Board Connector Block Pin Numbers and Name

# II. Absolute Maximum Ratings

| Parameter                  | Symbol   | Min  | Тур | Max | Unit | Ref. |

|----------------------------|----------|------|-----|-----|------|------|

| Maximum Supply Voltage     | Vcc3     | -0.5 |     | 4.0 | V    |      |

| Storage Temperature        | $T_{S}$  | -40  |     | 85  | °C   |      |

| Case Operating Temperature | $T_{OP}$ | -5   |     | 75  | °C   |      |

## III. Electrical Characteristics ( $T_{OP} = -5 \text{ to } 75 \text{ °C}$ , $V_{CC3} = 3.13 \text{ to } 3.45 \text{ Volts}$ )

| Parameter                      | Symbol                 | Min     | Тур      | Max                 | Unit | Ref. |

|--------------------------------|------------------------|---------|----------|---------------------|------|------|

| Supply Voltage                 | Vcc3                   | 3.13    |          | 3.45                | V    |      |

| Supply Current                 | Icc3                   |         |          | 600                 | mA   |      |

| Module total power             | P                      |         |          | 1.5                 | W    | 1    |

| Transmitter                    |                        |         |          |                     |      |      |

| Input differential impedance   | R <sub>in</sub>        |         | 100      |                     | Ω    | 2    |

| Differential data input swing  | Vin,pp                 | 120     |          | 820                 | mV   | 3    |

| Transmit Disable Voltage       | $V_{\mathrm{D}}$       | 2.0     |          | Vcc                 | V    | 4    |

| Transmit Enable Voltage        | $V_{\mathrm{EN}}$      | GND     |          | GND+ 0.8            | V    |      |

| Transmit Disable Assert Time   |                        |         |          | 10                  | us   |      |

| Receiver                       |                        |         |          |                     |      |      |

| Differential data output swing | Vout,pp                | 340     | 650      | 850                 | mV   | 5    |

| Data output rise time          | $t_{\rm r}$            |         |          | 38                  | ps   | 6    |

| Data output fall time          | $t_{\mathrm{f}}$       |         |          | 38                  | ps   | 6    |

| LOS Fault                      | V <sub>LOS fault</sub> | Vcc-0.5 |          | Vcc <sub>HOST</sub> | V    | 7    |

| LOS Normal                     | $V_{LOS\ norm}$        | GND     |          | GND+0.5             | V    | 7    |

| Power Supply Rejection         | PSR                    |         | See Note | e 8 below           |      | 8    |

### Notes:

- 1. Maximum total power value is specified across the full temperature and voltage range.

- 2. After internal AC coupling.

- 3. SONET/SDH jitter generation requirements are guaranteed with a minimum differential data input swing of 500mV peak-to-peak.

- 4. Or open circuit.

- 5. Into 100 ohms differential termination.

- 6. 20 80 %

- 7. Loss Of Signal is open collector to be pulled up with a 4.7k 10kohm resistor to 3.15 3.6V. Logic 0 indicates normal operation; logic 1 indicates no signal detected.

- 8. Per Section 2.7.1. in the XFP MSA Specification<sup>1</sup>.

## IV. Optical Characteristics ( $T_{OP} = -5 \text{ to } 75^{\circ}\text{C}$ , $V_{CC3} = 3.13 \text{ to } 3.45 \text{ Volts}$ )

| Parameter                       | Symbol             | Min  | Тур | Max   | Unit  | Ref. |  |

|---------------------------------|--------------------|------|-----|-------|-------|------|--|

| Transmitter                     |                    |      |     |       |       |      |  |

| Output Opt. Pwr: 9/125 SMF      | P <sub>OUT</sub>   | -6   |     | -1    | dBm   | 1    |  |

| Optical Wavelength              | λ                  | 1290 |     | 1330  | nm    |      |  |

| Optical Extinction Ratio        | ER                 | 6    |     |       | dB    | 1    |  |

| Sidemode Supression ratio       | $SSR_{min}$        | 30   |     |       | dB    |      |  |

| Tx Jitter (SONET/SDH)           | $Tx_{j1}$          |      |     | 0.3   | UI    |      |  |

| 20kHz-80MHz                     | -                  |      |     |       |       |      |  |

| Tx Jitter (SONET/SDH)           | $Tx_{j2}$          |      |     | 0.1   | UI    |      |  |

| 4MHz - 80MHz                    | _                  |      |     |       |       |      |  |

| Relative Intensity Noise        | RIN                |      |     | -130  | dB/Hz |      |  |

| Receiver                        |                    |      |     |       |       |      |  |

| Receiver Sensitivity @ 9.95Gb/s | R <sub>SENS1</sub> |      |     | -14.4 | dBm   |      |  |

| Receiver Sensitivity @ 10.5Gb/s | R <sub>SENS2</sub> |      |     | -14.4 | dBm   | 2    |  |

| Receiver Sensitivity @ 11.3Gb/s | R <sub>SENS3</sub> |      |     | -13.4 | dBm   | 2    |  |

| Stressed Receiver Sensitivity   | $R_{SENS4}$        |      |     | -10.3 | dBm   | 3    |  |

| (OMA) @ 10.5Gb/s                |                    |      |     |       |       |      |  |

| Maximum Input Power             | $P_{MAX}$          | +0.5 |     |       | dBm   |      |  |

| Optical Center Wavelength       | $\lambda_{ m C}$   | 1260 |     | 1600  | nm    |      |  |

| Receiver Reflectance            | $R_{rx}$           |      |     | -14   | dB    |      |  |

| LOS De-Assert                   | $LOS_D$            |      |     | -18   | dBm   |      |  |

| LOS Assert                      | $LOS_A$            | -32  |     |       | dBm   |      |  |

| LOS Hysteresis                  |                    | 0.5  |     |       | dB    |      |  |

#### Notes:

- 1. Having ER = 6 dB guarantees that the -6 dBm minimum output power meets IEEE 802.3ae requirement of OMA=-5.2dBm.

- 2. Measured with worst ER; BER $<10^{-12}$ ;  $2^{31} 1$  PRBS. Complies with -12.6 dBm OMA at ER = 6 dB.

- 3. Per IEEE 802.3ae. Equivalent to -13.3 dBm average power at Infinite ER, -11.08 dBm at ER = 6 dB.

### 8.5Gb/s Fibre-Channel:

To operate the FTLX1413D3BCL at 8.5Gb/s Fibre-Channel, the EEPROM-Table 0, Byte 117, Bit 0 must be set as follows; .

- EEPROM Byte 117, Bit 0, value "1" for 8GFC:

- EEPROM Byte 117, Bit 0 value "0" for 10Gb/s rates:

- o (It is also possible to bypass the CDRs with, Byte 111, Bit 0.)

By default, a power cycling the transceiver will return the transceiver to normal 10Gb/s operation with the CDRs active.

#### V. **General Specifications**

| Parameter                  | Symbol    | Min | Тур | Max        | Units | Ref. |

|----------------------------|-----------|-----|-----|------------|-------|------|

| Bit Rate                   | BR        | 8.5 |     | 11.3       | Gb/s  | 1    |

| Bit Error Ratio            | BER       |     |     | $10^{-12}$ |       | 2    |

| Max. Supported Link Length | $L_{MAX}$ |     | 10  |            | km    | 1    |

### Notes:

- 1. SONET OC-192 SR-1, SDH STM I-64.1, 10GBASE-LR/LW, 1200-SM-LL-L, 800-SM-LC-L, SONET OC-192 with FEC, 10GBASE-LR/LW with FEC, 1200-SM-LL-L with FEC. 2. Tested with a  $2^{31} - 1$  PRBS

#### VI. **Environmental Specifications**

Finisar FTLX1413M3BCL transceivers have a commercial operating case temperature range of  $-5^{\circ}$ C to  $+75^{\circ}$ C.

| Parameter                  | Symbol    | Min | Тур | Max | Units | Ref. |

|----------------------------|-----------|-----|-----|-----|-------|------|

| Case Operating Temperature | $T_{op}$  | -5  |     | 75  | °C    |      |

| Storage Temperature        | $T_{sto}$ | -40 |     | 85  | °C    |      |

#### VII. **Regulatory Compliance**

Finisar XFP transceivers are Class 1 Laser Products. They are certified per the following standards:

| Feature    | Agency   | Standard                                    | Certificate |

|------------|----------|---------------------------------------------|-------------|

|            |          |                                             | Number      |

| Laser Eye  | FDA/CDRH | CDRH 21 CFR 1040 and Laser Notice 50        | 9210176-77  |

| Safety     |          |                                             |             |

| Laser Eye  | TÜV      | EN 60825-1: 2007, EN60825-2:2004+A1         | R72101686   |

| Safety     |          | IEC 60825-1: 2007 (2 <sup>nd</sup> Edition) |             |

|            |          | IEC 60825-2: 2010 (3 <sup>rd</sup> Edition) |             |

| Electrical | TÜV      | EN 60950:2006+A11                           | R72101686   |

| Safety     |          |                                             |             |

| Electrical | UL/CSA   | CLASS 3862.07                               | 2283290     |

| Safety     |          | CLASS 3862.87                               |             |

|            |          |                                             |             |

Copies of the referenced certificates are available at Finisar Corporation upon request.

### VIII. Digital Diagnostic Functions

As defined by the XFP MSA<sup>1</sup>, Finisar XFP transceivers provide digital diagnostic functions via a 2-wire serial interface, which allows real-time access to the following operating parameters:

- Transceiver temperature

- Laser bias current

- Transmitted optical power

- Received optical power

- Transceiver supply voltage

It also provides a sophisticated system of alarm and warning flags, which may be used to alert end-users when particular operating parameters are outside of a factory-set normal range.

The operating and diagnostics information is monitored and reported by a Digital Diagnostics Transceiver Controller (DDTC) inside the transceiver, which is accessed through the 2-wire serial interface. When the serial protocol is activated, the serial clock signal (SCL pin) is generated by the host. The positive edge clocks data into the XFP transceiver into those segments of its memory map that are not write-protected. The negative edge clocks data from the XFP transceiver. The serial data signal (SDA pin) is bi-directional for serial data transfer. The host uses SDA in conjunction with SCL to mark the start and end of serial protocol activation. The memories are organized as a series of 8-bit data words that can be addressed individually or sequentially. The 2-wire serial interface provides sequential or random access to the 8 bit parameters, addressed from 000h to the maximum address of the memory.

For more detailed information including memory map definitions, please see Finisar Application Note AN-2035 "Digital Diagnostic Monitoring Interface for XFP Optical Transceivers", or the XFP MSA Specification<sup>1</sup>.

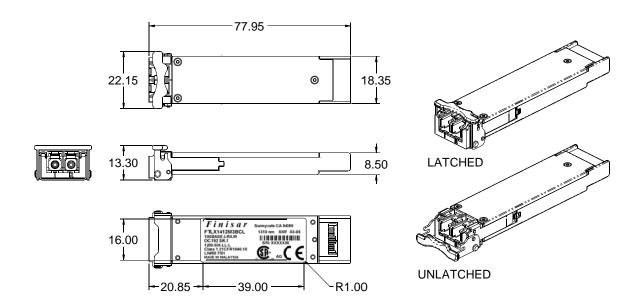

# IX. Mechanical Specifications

Finisar's XFP transceivers are compliant with the dimensions defined by the XFP Multi-Sourcing Agreement (MSA).

XFP Transceiver (dimensions are in mm)

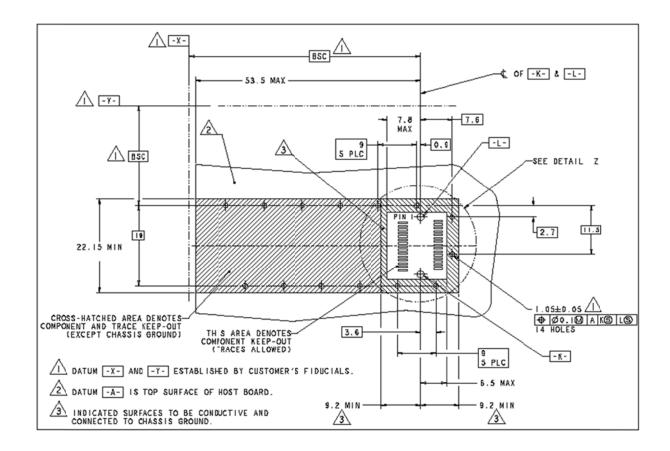

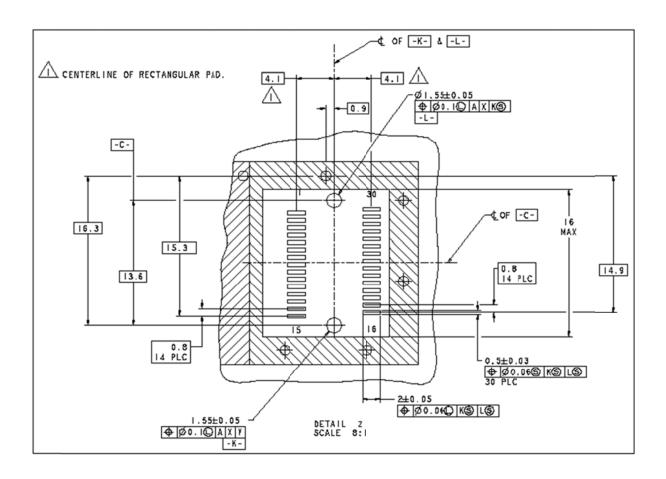

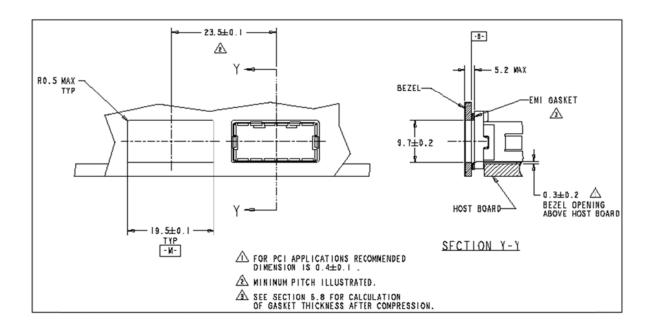

# X. PCB Layout and Bezel Recommendations

XFP Host Board Mechanical Layout (dimensions are in mm)

XFP Detail Host Board Mechanical Layout (dimensions are in mm)

XFP Recommended Bezel Design (dimensions are in mm)

### **XI.** References

- 1. 10 Gigabit Small Form Factor Pluggable Module (XFP) Multi-Source Agreement (MSA), Rev 4.5 August 2005. Documentation is currently available at <a href="http://www.xfpmsa.org/">http://www.xfpmsa.org/</a>

- 2. Application Note AN-2035: "Digital Diagnostic Monitoring Interface for XFP Optical Transceivers" Finisar Corporation, December 2003

- 3. Directive 2002/95/EC of the European Council Parliament and of the Council, "on the restriction of the use of certain hazardous substances in electrical and electronic equipment". January 27, 2003.

- 4. "Application Note AN-2038: Finisar Implementation Of RoHS Compliant Transceivers", Finisar Corporation, January 21, 2005.

### **XII.** For More Information

Finisar Corporation 1389 Moffett Park Drive Sunnyvale, CA 94089-1133 Tel. 1-408-548-1000 Fax 1-408-541-6138 sales@finisar.com www.finisar.com