SCV64<sup>TM</sup> User Manual

http://www.tundra.com

The information in this document is subject to change without notice and should not be construed as a commitment by Tundra Semiconductor Corporation. While reasonable precautions have been taken, Tundra Semiconductor Corporation assumes no responsibility for any errors that may appear in this document.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Tundra Semiconductor Corporation.

Tundra® products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Tundra product could create a situation where personal injury or death may occur. Should Buyer purchase or use Tundra products for any such unintended or unauthorized application, Buyer shall indemnify and hold Tundra and its officers, employees, subsidiaries, affiliates and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Tundra was negligent regarding the design or manufacture of the part.

The acceptance of this document will be construed as an acceptance of the foregoing conditions.

SCV64TM User Manual

Copyright 2001, Tundra Semiconductor Corporation All rights reserved.

Document: 8091078\_MA001\_01

Printed in Canada

Tundra and Tundra logo are registered trademarks of Tundra Semiconductor Corporation. SCV64 is a trademark of Tundra Semiconductor Corporation. BI-Mode is is a registered trademark of DY-4 Systems, Inc.

# **Table of Contents**

| 1 | Gener | al Informa  | tion 1-1                                      |

|---|-------|-------------|-----------------------------------------------|

|   | 1.1   | Introduc    | tion 1-1                                      |

|   | 1.2   | Product     | Overview 1-1                                  |

|   |       | 1.2.1       | Flexibility and Features1-1                   |

|   | 1.3   | Using Th    | nis Document 1-4                              |

|   | 1.4   | Convent     | ions 1-5                                      |

|   |       | 1.4.1       | Signals1-5                                    |

|   |       | 1.4.2       | Symbols1-5                                    |

|   |       | 1.4.3       | Mathematical Notation1-5                      |

| 2 | Funct | ional Descr | iption 2-1                                    |

|   | 2.1   | Introduc    | tion                                          |

|   |       | 2.1.1       | Organization of the Functional Description    |

|   |       | 2.1.2       | Functional Overview2-2                        |

|   |       | 2.1.2.1     | Data Path 2-2                                 |

|   |       | 2.1.2.2     | VMEbus Interface 2-5                          |

|   |       | 2.1.2.3     | Local Bus Interface 2-6                       |

|   | 2.2   | VMEbus      | Requester 2-8                                 |

|   |       | 2.2.1       | Function2-8                                   |

|   |       | 2.2.2       | Bus Request Modes2-9                          |

|   |       | 2.2.2.1     | Fair and Demand Modes 2-9                     |

|   |       | 2.2.2.2     | VMEbus Request Levels 2-9                     |

|   |       | 2.2.3       | Bus Release Modes 2-10                        |

|   |       | 2.2.3.1     | Bus Clear Enabling 2-10                       |

|   |       | 2.2.3.2     | Release On Request and Release When Done 2-10 |

|   |       | 2.2.3.3     | Ownership Timer 2-11                          |

|   |       | 2.2.4       | Other Bus Release Mechanisms2-11              |

|   |       | 2.2.4.1     | Local Memory Interrupt 2-11                   |

|   |       | 2.2.4.2     | BI-Mode                                       |

|     | 2.2.4.3   | Local and System Reset            | . 2-12 |

|-----|-----------|-----------------------------------|--------|

| 2.3 | Interrupt | er                                | . 2-13 |

|     | 2.3.1     | VMEbus Interrupts                 | 2-13   |

|     | 2.3.1.1   | Interrupt Generation              | . 2-13 |

|     | 2.3.1.2   | BI-mode Effects                   | . 2-14 |

|     | 2.3.1.3   | Reset Effects                     | . 2-14 |

|     | 2.3.2     | Local Bus Interrupts              | 2-15   |

| 2.4 | Interrupt | Handler                           | . 2-18 |

|     | 2.4.1     | Interrupt Enabling and Status     | 2-20   |

|     | 2.4.1.1   | Local Interrupt Level Mapping     | . 2-21 |

|     | 2.4.2     | Interrupt Acknowledge Cycles      | 2-22   |

|     | 2.4.2.1   | Auto-Vectored Interrupts          | . 2-25 |

|     | 2.4.2.2   | Vectored Interrupts               | . 2-26 |

|     | 2.4.2.3   | BI-Mode Effects                   | . 2-29 |

|     | 2.4.2.4   | Reset Effects                     | . 2-29 |

| 2.5 | System C  | Controller Functions              | . 2-30 |

|     | 2.5.1     | Syscon Determination              | 2-30   |

|     | 2.5.2     | IACK Daisy Chain Driver           | 2-31   |

|     | 2.5.3     | VMEbus Arbiter                    | 2-31   |

|     | 2.5.3.1   | Arbitration Modes                 | . 2-31 |

|     | 2.5.3.2   | Arbitration Time-out              | . 2-33 |

|     | 2.5.3.3   | Reset Effects                     | . 2-33 |

|     | 2.5.4     | Bus Timer                         | 2-34   |

|     | 2.5.5     | System Clock Driver               | 2-34   |

|     | 2.5.6     | External Inputs                   | 2-34   |

|     | 2.5.6.1   | External Status                   | . 2-34 |

|     | 2.5.6.2   | Off-Board Reset Input             | . 2-35 |

|     | 2.5.7     | Reset Effects on Syscon Functions | 2-35   |

| 2.6 | Data Pat  | h                                 | . 2-36 |

|     | 2.6.1     | SCV64 as VME Slave                | 2-39   |

|     | 2.6.1.1   | Coupled Mode                      | . 2-39 |

|     | 2.6.1.2   | Decoupled Mode 2-39                            |

|-----|-----------|------------------------------------------------|

|     | 2.6.2     | SCV64 as VME Master 2-41                       |

|     | 2.6.2.1   | Coupled Mode 2-41                              |

|     | 2.6.2.2   | Decoupled Mode 2-42                            |

|     | 2.6.2.3   | DMA Transfers 2-43                             |

| 2.7 | Memory N  | Mapping 2-45                                   |

|     | 2.7.1     | CPU Memory Map 2-45                            |

|     | 2.7.2     | VME Slave Memory Map 2-49                      |

|     | 2.7.2.1   | Automatic Base Address Programming 2-51        |

|     | 2.7.2.2   | Access Protection 2-52                         |

| 2.8 | VMEbus    | Interface 2-53                                 |

|     | 2.8.1     | SCV64 as VME Master                            |

|     | 2.8.1.1   | Address Translation 2-53                       |

|     | 2.8.1.2   | Byte Lane Translation 2-54                     |

|     | 2.8.1.3   | VMEbus Mastership 2-56                         |

|     | 2.8.1.4   | RMW Cycles 2-57                                |

|     | 2.8.1.5   | Termination of a Master Cycle with RETRY* 2-58 |

|     | 2.8.2     | SCV64 as VME Slave 2-58                        |

|     | 2.8.2.1   | Address Translation 2-58                       |

|     | 2.8.2.2   | Byte Lane Translation 2-59                     |

|     | 2.8.2.3   | Local Bus Mastership 2-60                      |

|     | 2.8.3     | DMA Transfers 2-61                             |

|     | 2.8.4     | Master/Slave Deadlock Resolution 2-61          |

|     | 2.8.5     | Location Monitor Access                        |

|     | 2.8.6     | Bus Busy Glitch                                |

|     | 2.8.7     | BI-Mode Effects                                |

|     | 2.8.8     | Bus Error Handling 2-64                        |

| 2.9 | Local Bus | s Interface 2-66                               |

|     | 2.9.1     | Local Bus Arbitration2-66                      |

|     | 2.9.1.1   | Local Arbiter Bypassed 2-66                    |

|     | 2.9.1.2   | Local Arbiter Active 2-67                      |

|      | 2.9.2     | Local Cycles – Overview               | 2-73  |

|------|-----------|---------------------------------------|-------|

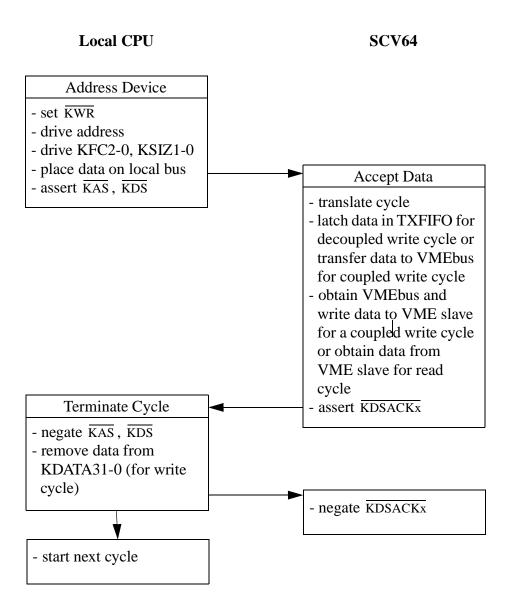

|      | 2.9.2.1   | Cycle Initiation                      | 2-73  |

|      | 2.9.2.2   | Data Transfer                         | 2-74  |

|      | 2.9.2.3   | Cycle Termination Signals             |       |

|      | 2.9.2.4   | Bus Error Handling                    | 2-77  |

|      | 2.9.3     | SCV64 as Local Slave                  | 2-78  |

|      | 2.9.4     | SCV64 as Local Master                 | 2-83  |

|      | 2.9.5     | Register Access                       | 2-87  |

|      | 2.9.6     | Burst Cycles                          | 2-89  |

|      | 2.9.6.1   | Burst Reads                           |       |

|      | 2.9.6.2   | Burst Writes                          | 2-90  |

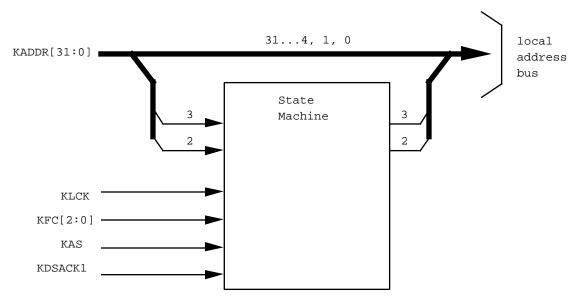

|      | 2.9.6.3   | Local Address Incrementation          |       |

|      | 2.9.7     | Read-Modify-Write Cycles              | 2-97  |

|      | 2.9.8     | Master/Slave Deadlock Resolution      | 2-98  |

|      | 2.9.8.1   | Deadlock Resolution in Decoupled Mode |       |

|      | 2.9.9     | Location Monitor Access               | 2-99  |

|      | 2.9.10    | Reflected Cycles                      | 2-99  |

|      | 2.9.11    | VSBbus Access                         | 2-100 |

|      | 2.9.12    | BI-Mode                               | 2-100 |

| 2.10 | Location  | Monitor and LMFIFO                    | 2-101 |

| 2.11 | DMA Co    | ntroller                              | 2-102 |

|      | 2.11.1    | DMA Initialization                    | 2-102 |

|      | 2.11.2    | Addressing and Data Transfer Modes    | 2-104 |

|      | 2.11.3    | Data Transfer Counts                  | 2-107 |

|      | 2.11.4    | FILL Option                           | 2-107 |

|      | 2.11.5    | No Release Option                     | 2-108 |

|      | 2.11.6    | DMA Completion and Error Checking     | 2-108 |

| 2.12 | Resets, C | locks and Timers                      | 2-110 |

|      | 2.12.1    | Resets                                | 2-110 |

|      | 2.12.1.1  | Local Reset                           | 2-110 |

|      | 2.12.1.2  | System Reset                          | 2-111 |

|        | 2.12.1.3   | Power-up Reset                            |       |

|--------|------------|-------------------------------------------|-------|

|        | 2.12.1.4   | Reset Effects on SCV64 Internal Resources |       |

|        | 2.12.2     | Clocks                                    |       |

|        | 2.12.2.1   | Clocks Required                           |       |

|        | 2.12.2.2   | Clocks Generated                          | 2-114 |

|        | 2.12.3     | Timers                                    |       |

|        | 2.12.3.1   | Local Bus Timer                           |       |

|        | 2.12.3.2   | Tick Timer                                | 2-115 |

|        | 2.12.3.3   | Watchdog Timer                            | 2-116 |

|        | 2.12.3.4   | VMEbus Timers                             | 2-116 |

| 2.13   | Power-up   | Modes                                     | 2-117 |

|        | 2.13.1     | Local IACK Cycle Decoding                 |       |

|        | 2.13.2     | Auto SYSCON select                        |       |

|        | 2.13.3     | Local Arbiter Bypass                      |       |

|        | 2.13.4     | Automatic Base Address Programming        |       |

| 2.14   | BI-Mode    |                                           | 2-119 |

| 2.15   | Auto-ID.   |                                           | 2-121 |

|        | 2.15.1     | The Auto-ID Cycle                         |       |

|        | 2.15.2     | Auto-ID Self Test                         |       |

| 2.16   | Internal D | Delay Line Calibration                    |       |

| 2.17   | Test and I | Diagnostic Modes                          |       |

|        | 2.17.1     | Decoupled Write Diagnostics               |       |

|        | 2.17.2     | Loopback Diagnostics                      |       |

|        | 2.17.2.1   | Loopback Mode                             | 2-126 |

|        | 2.17.2.2   | DMA Loopback                              |       |

|        | 2.17.2.3   | Interrupt Loopback                        |       |

|        | 2.17.2.4   | JTAG Support                              |       |

| Descri |            | V64 Signals                               |       |

| 3.1    | VMEbus     | Signals                                   |       |

| 3.2    | Local Sig  | nals                                      |       |

3

| 4     | Signals and DC Characteristics 4-1 |                   |                      |          |

|-------|------------------------------------|-------------------|----------------------|----------|

|       | 4.1                                | Termino           | ology                |          |

|       | 4.2                                | DC Cha            | racteristics         |          |

|       | 4.3                                | Capaciti          | ve Loading           |          |

|       | 4.4                                | Pin Con           | 4-11                 |          |

| App-A | Regist                             | ers               |                      | App A-1  |

|       | A.1                                | Control           | and Status Registers | App A-1  |

| App-B | SCV64                              | 4 Timing (        | Characteristics      | App B-1  |

|       | B.1                                | Timing            | Parameters           | App B-1  |

|       | B.2                                | Capaciti          | ve Loading           | App B-13 |

|       | B.3                                | Timing            | Diagrams             | App B-14 |

| App-C | Perfor                             | mance             |                      | App C-1  |

|       | C.1                                | Coupled           | Cycles               | App C-1  |

|       |                                    | C.1.1             | SCV64 as VME Master  | App C-2  |

|       |                                    | C.1.2             | SCV64 as VME Slave   | App C-5  |

|       | C.2                                | Decoup            | led Cycles           | App C-7  |

|       |                                    | C.2.1             | SCV64 as VME Master  | App C-7  |

|       |                                    | C.2.2             | SCV64 as VME Slave   | App C-7  |

|       | C.3                                | Daisy C           | hains                | App C-8  |

|       | C.4                                | Arbiter Functions |                      | App C-8  |

|       | C.5                                | Summar            | ·y                   | App C-9  |

| App-D | VMEb                               | ous-Local l       | Bus Cycle Mapping    | App D-1  |

|       | D.1                                | Cycle T           | ranslation           | App D-1  |

|       | D.2                                | Address           | Space Mapping        | App D-12 |

| App-E | Applic                             | cations           |                      | App E-1  |

|       | E.1                                | VMEbu             | s Interface          | App E-1  |

|       |                                    | E.1.1             | Buffered Signals     | App E-1  |

|       |                                    | E.1.2             | Layout Issues        | App E-1  |

|       |           | E.1.3          | Decoupling VDD and VSS                                              | App E-3            |

|-------|-----------|----------------|---------------------------------------------------------------------|--------------------|

|       |           | E.1.4          | BGxIN*[3:0] Signals                                                 | App E-3            |

|       |           | E.1.5          | RETRY*/ VRMC Pin                                                    | App E-6            |

|       |           | E.1.6          | BI-Mode and IRQ1*                                                   | App E-7            |

|       | E.2       | Local Bu       | s Interface for Slave Only Applications                             | App E-8            |

|       |           | E.2.1          | Initialization                                                      | App E-8            |

|       |           | E.2.2          | VMEbus Programming                                                  | App E-8            |

|       | E.3       | Local Bu       | s Interface for MC68030 Application                                 | App E-11           |

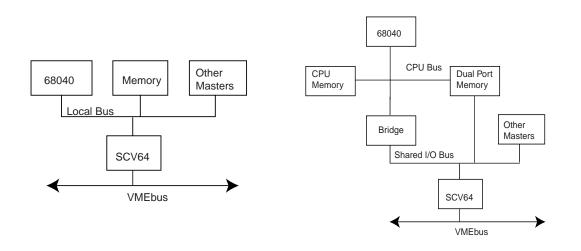

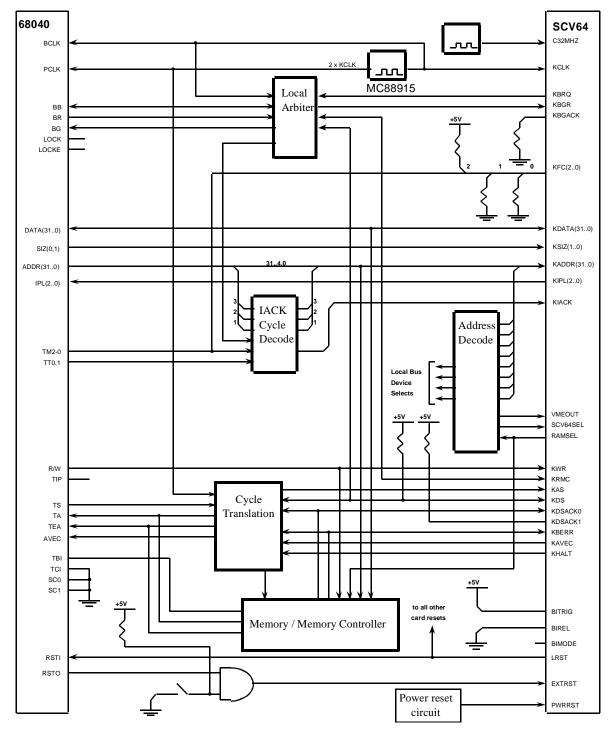

|       | E.4       | Local Bu       | s Interface for MC68040 Application                                 | App E-12           |

|       |           | E.4.1          | Design Philosophy                                                   | App E-12           |

|       |           | E.4.2          | Design Overview                                                     | App E-13           |

|       |           | E.4.3          | Bus Adapter Operation                                               | App E-16           |

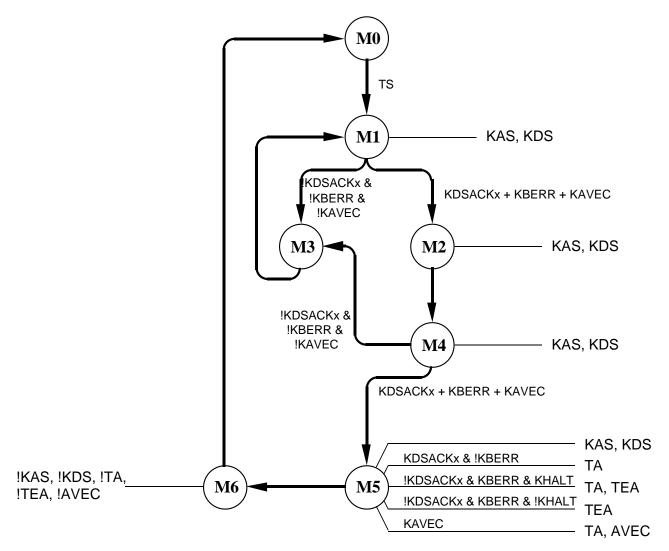

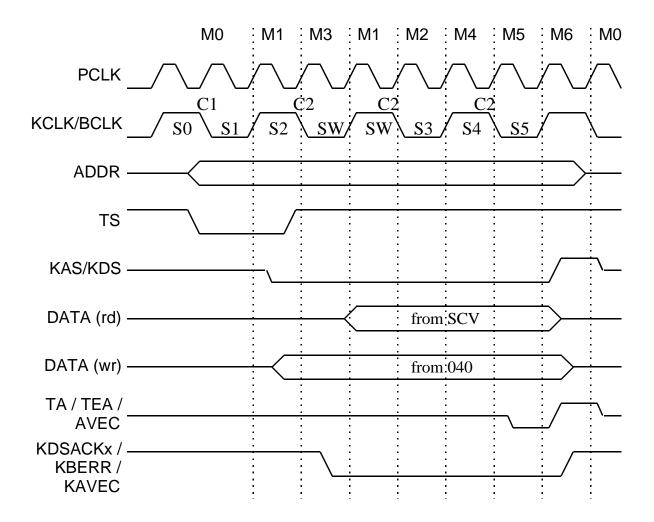

|       |           | E.4.4          | Cycle Translation State Machine                                     | App E-17           |

|       |           | E.4.5          | Dynamic Bus Sizing                                                  | App E-20           |

|       |           | E.4.6          | Transfer Attributes                                                 | App E-21           |

|       |           | E.4.7          | Interrupts                                                          | App E-24           |

| App-F | Initializ | zation         |                                                                     | App F-1            |

|       | F.1       | Hardware       | e Configuration                                                     | App F-1            |

|       |           | F.1.1          | Power-Up Modes                                                      | App F-1            |

|       |           | F.1.2          | Test Mode Pins                                                      | App F-2            |

|       |           | F.1.3          | BI-Mode                                                             | App F-2            |

|       |           | F.1.4          | JTAG                                                                | App F-2            |

|       |           | F.1.5          | Clocks                                                              | App F-2            |

|       |           | F.1.6          | Resets                                                              | App F-3            |

|       |           | F.1.7          | RETRY*/VRMC                                                         | App F-3            |

|       | F.2       | Software       |                                                                     | App F-4            |

|       |           | F.2.1          | Delay Line Initialization                                           | App F-5            |

|       |           | 1.11.1         |                                                                     |                    |

|       |           | F.2.2          | Byte Lane Mapping and Cycle Conversion                              | App F-6            |

|       |           |                | Byte Lane Mapping and Cycle Conversion<br>Slave Address Programming |                    |

|       |           | F.2.2          |                                                                     | App F-6            |

|       |           | F.2.2<br>F.2.3 | Slave Address Programming                                           | App F-6<br>App F-7 |

|       |          | F.2.6       | RETRY*/VRMC Configuration | App F-7 |

|-------|----------|-------------|---------------------------|---------|

|       |          | F.2.7       | Other Local Options       | App F-8 |

|       |          | F.2.8       | Local Bursts              | App F-8 |

|       |          | F.2.9       | Local Arbiter             | App F-8 |

|       |          | F.2.10      | Interrupts                | App F-8 |

|       |          | F.2.11      | Local Timer Functions     | App F-9 |

|       |          | F.2.12      | SYSFAIL*                  | App F-9 |

|       |          | F.2.13      | VME Requester             | App F-9 |

|       |          | F.2.14      | VME Arbiter               | App F-9 |

| App-G | Reliabil | ity predict | ion                       | App G-1 |

|       | G.1      | Device De   | escription                | App G-1 |

|       |          | G.1.1       | Physical characteristics  | App G-1 |

|       |          | G.1.2       | Thermal characteristics   | App G-1 |

|       |          | G.1.3       | Latch-up current          | App G-2 |

|       | G.2      | Parameter   | rs                        | App G-2 |

| Арр-Н | Environ  | imental an  | d Operating Parameters    | Арр Н-1 |

| App-I | Revisio  | n History   |                           | App I-1 |

| App-J | Mechan   | ical and O  | Ordering Information      | App J-1 |

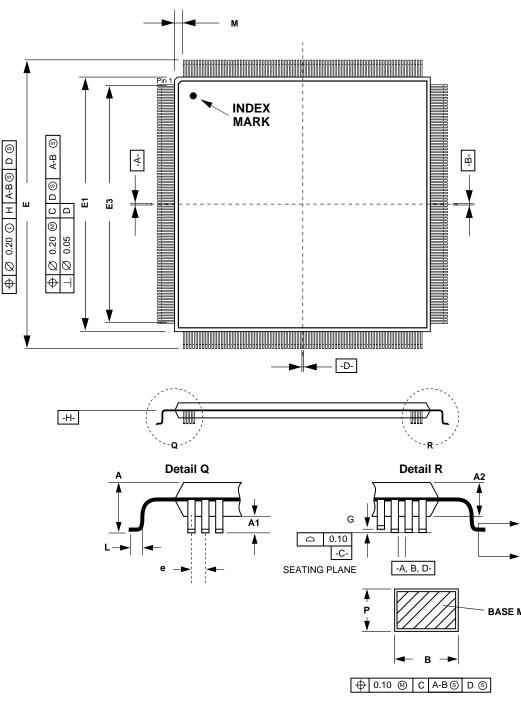

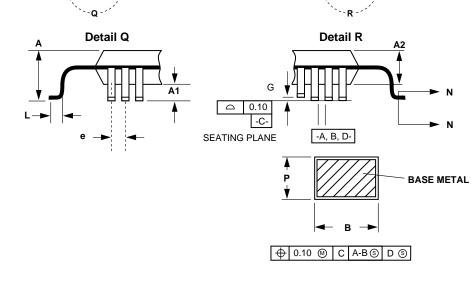

|       | J.1      | Mechanic    | al Information            | App J-1 |

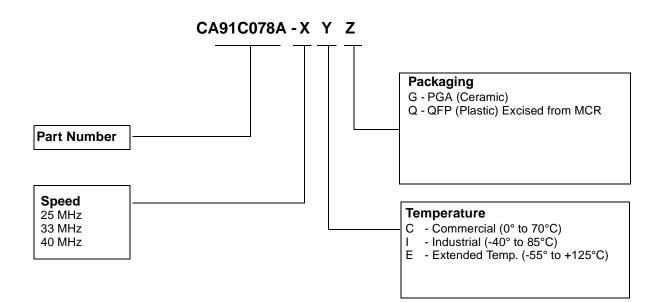

|       | J.2      | Ordering    | Information               | App J-3 |

| Index | •••••    | •••••       |                           | Index-1 |

# **List of Figures**

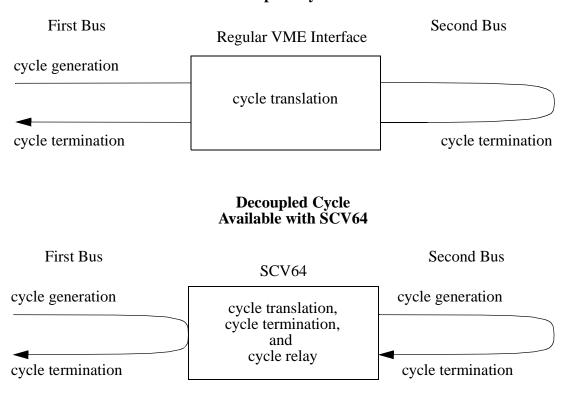

| Figure 1.1 :  | Coupled versus Decoupled Cycles                                   | . 1-2 |

|---------------|-------------------------------------------------------------------|-------|

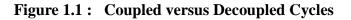

| Figure 2.1 :  | Functional Block Diagram                                          | . 2-3 |

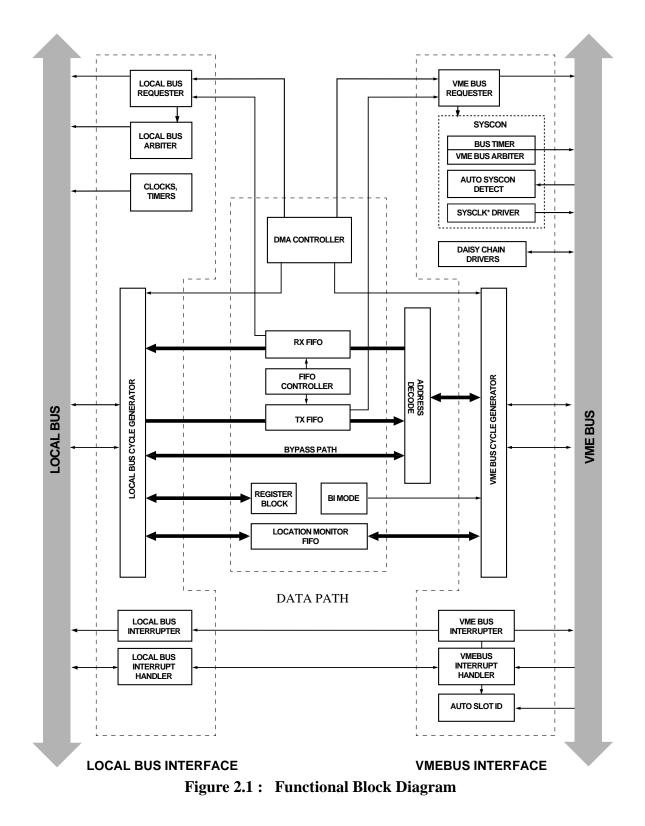

| Figure 2.2 :  | Interrupt Handler Block Diagram                                   | 2-19  |

| Figure 2.3 :  | Connections Resulting from Changing Local IACK Decoding           | 2-24  |

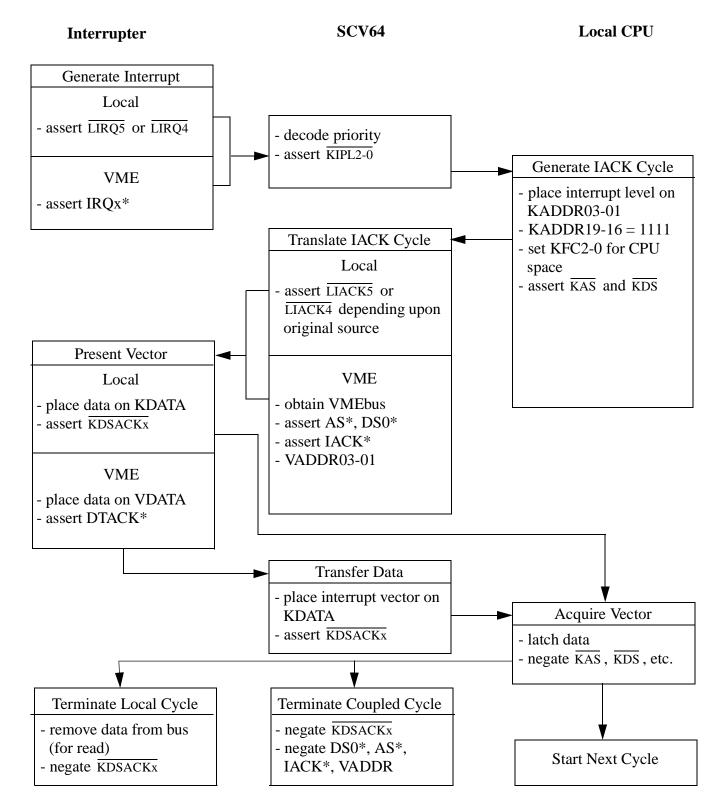

| Figure 2.4 :  | Local Interrupt Cycle - Auto-Vectored                             | 2-26  |

| Figure 2.5 :  | Timing for Local Interrupts                                       | 2-27  |

| Figure 2.6 :  | Vectored Interrupt Cycle - with Local and VME Interrupter         | 2-28  |

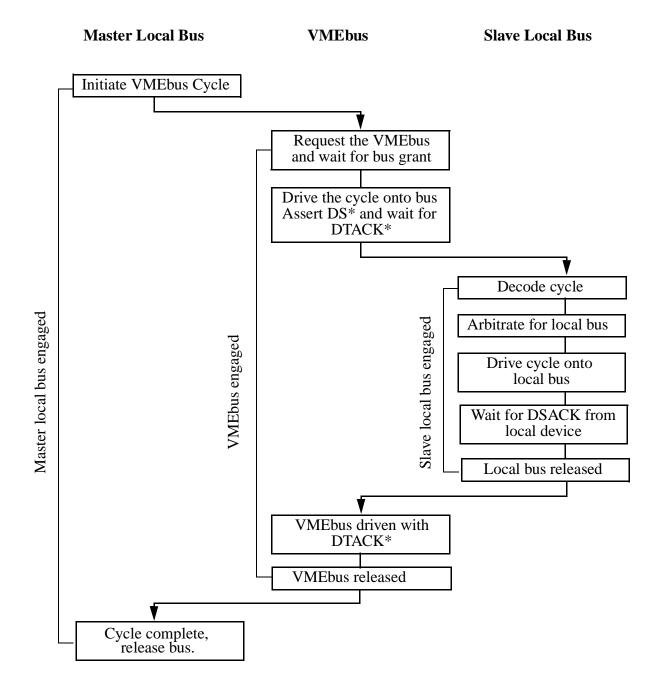

| Figure 2.7 :  | Coupled Cycles on the VMEbus                                      | 2-37  |

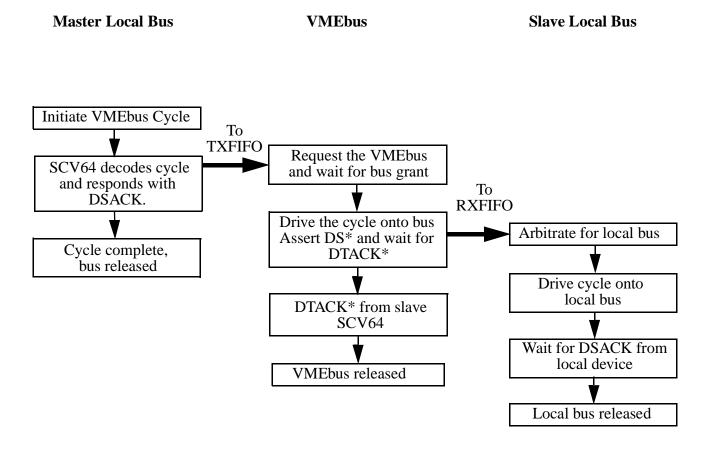

| Figure 2.8 :  | Decoupled Cycles on the VMEbus                                    | 2-38  |

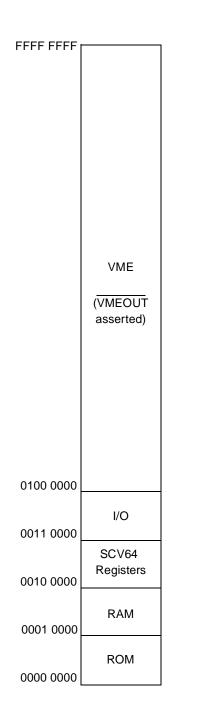

| Figure 2.9 :  | Sample CPU Memory Map as Determined by<br>Local Address Decoder   | 2-46  |

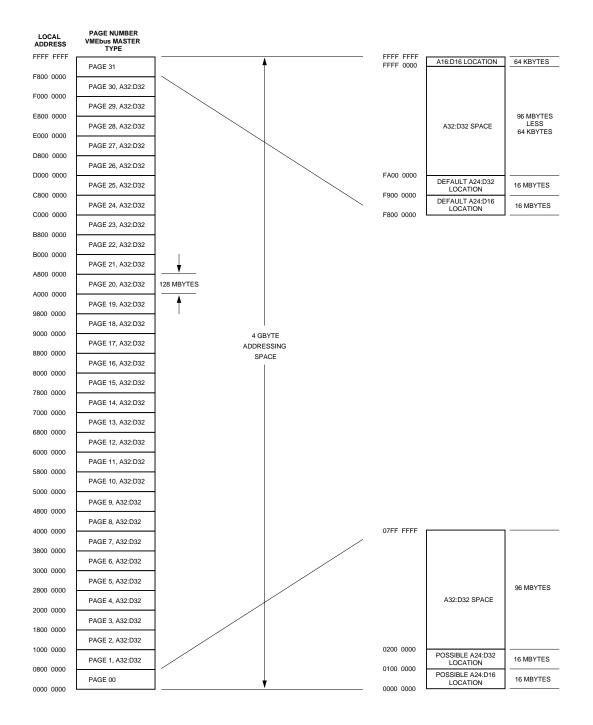

| Figure 2.10 : | SCV64 VME Access Overlay for the CPU Memory Map                   | 2-47  |

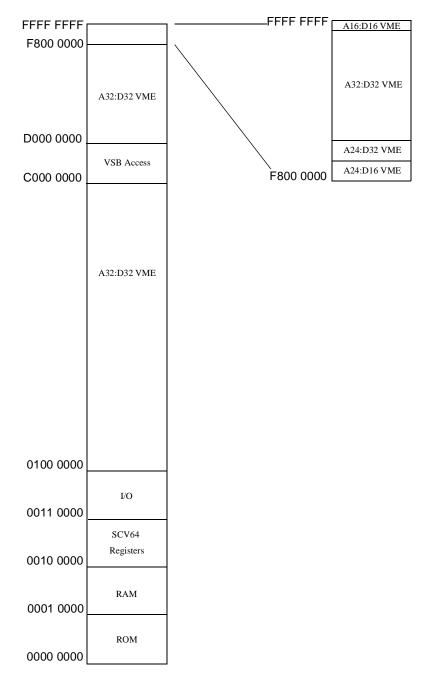

| Figure 2.11 : | Sample CPU Memory Map with SCV64 VME and VSB Space Overlay        | 2-48  |

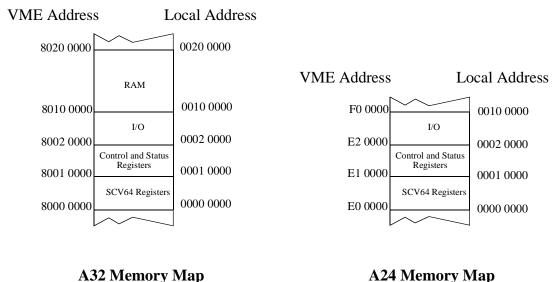

| Figure 2.12 : | Sample VME Slave Memory Map (Accessed as A32 and A24)             | 2-51  |

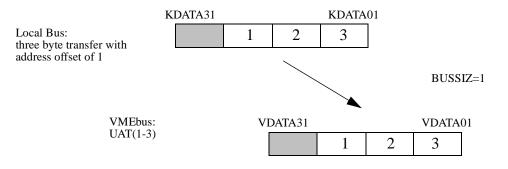

| Figure 2.13 : | Local to VME Byte Lane Translation with BUSSIZ=1                  | 2-55  |

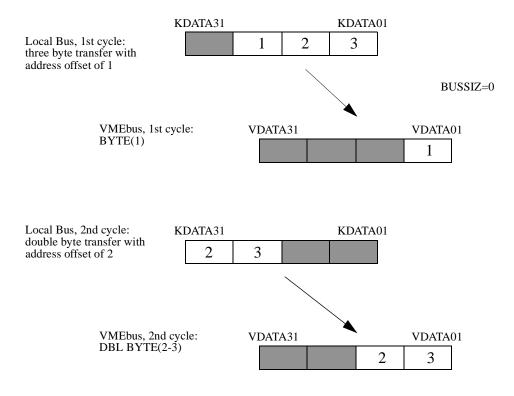

| Figure 2.14 : | Local to VME Byte Lane Translation with BUSSIZ=0                  | 2-56  |

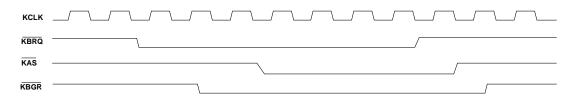

| Figure 2.15 : | Local Bus Arbitration with Local Arbiter Bypass                   | 2-67  |

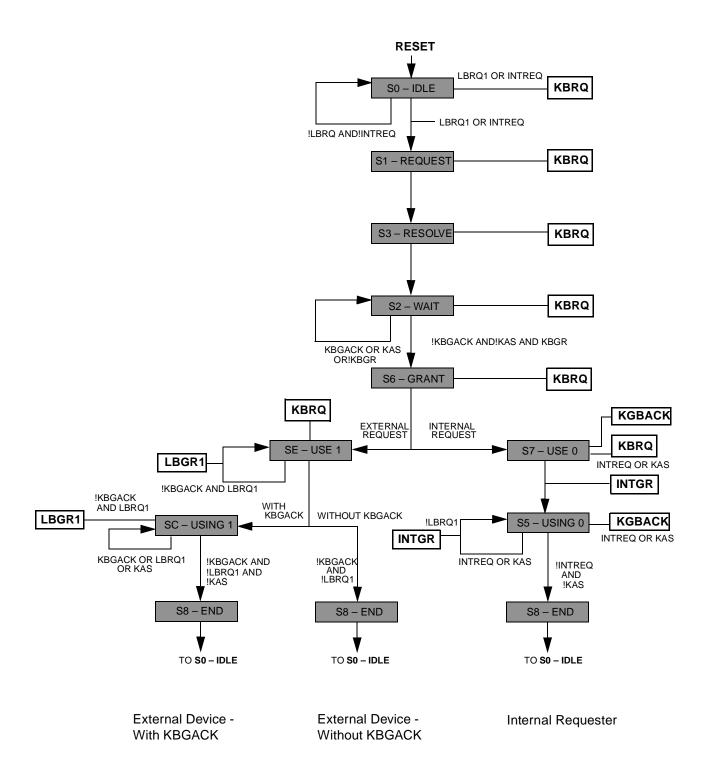

| Figure 2.16 : | Local Bus Arbiter State Machine                                   | 2-68  |

| Figure 2.17 : | Local Arbitration for Internal Requester                          | 2-70  |

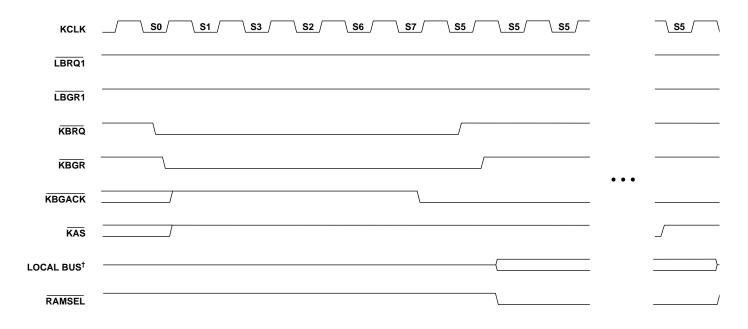

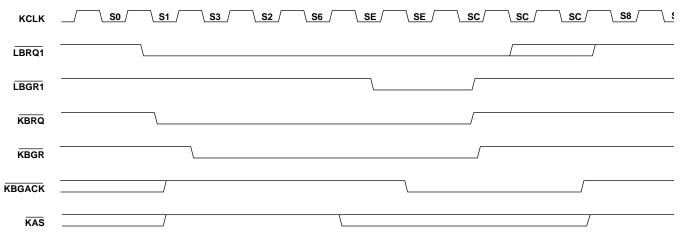

| Figure 2.18 : | Local Arbitration for External Device - With Acknowledgment       | 2-72  |

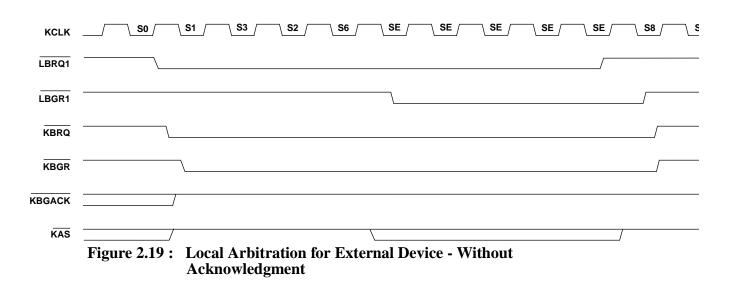

| Figure 2.19 : | Local Arbitration for External Device - Without<br>Acknowledgment | 2-72  |

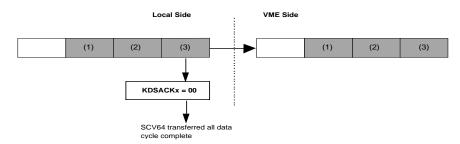

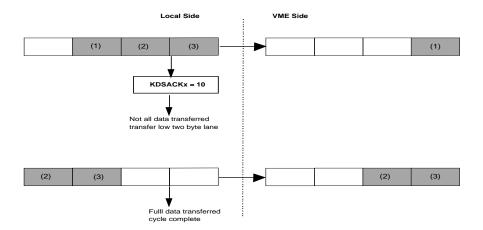

| Figure 2.20 : | Example of Longword Transfer to a 16-Bit Port                     | 2-76  |

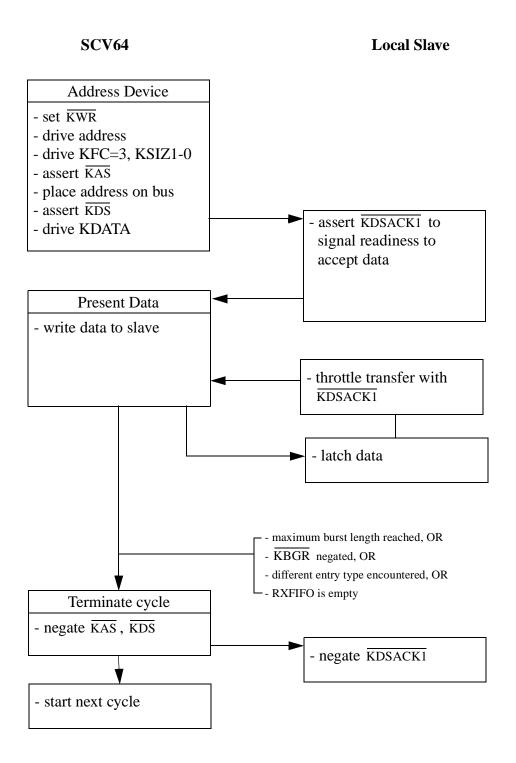

| Figure 2.21 : | Flowchart for a Local Cycle with SCV64 as Local Slave             | 2-79  |

| Figure 2.22 : | Decoupled Write Cycle – SCV64 as Local Slave                      | 2-82  |

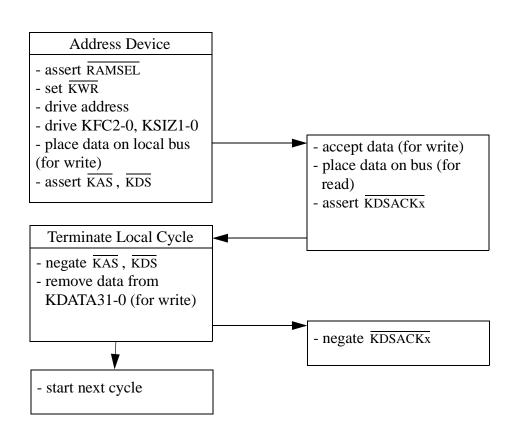

| Figure 2.23 : | Flowchart for a Local Cycle with SCV64 as Local Master            | 2-84  |

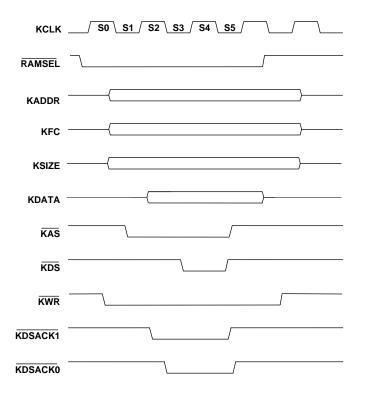

| Figure 2.24 : | Write Cycle – SCV64 as Local Master                               | 2-85  |

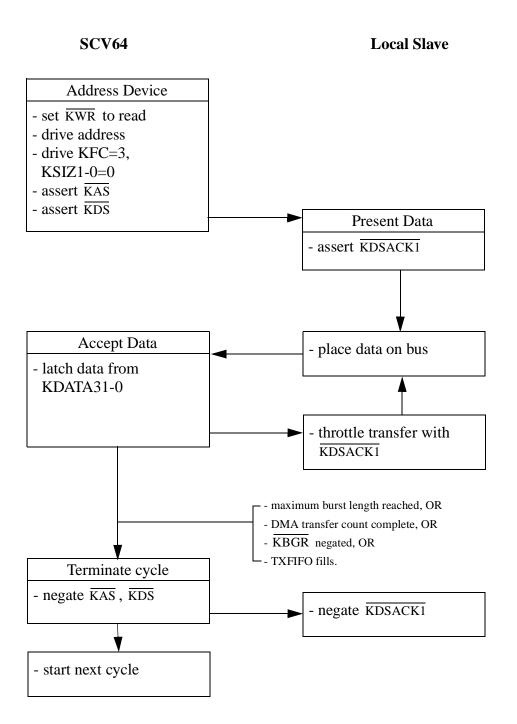

| Figure 2.25 :  | Flowchart for a Burst Read Cycle - SCV64 as Local Maste                         | r 2-91   |

|----------------|---------------------------------------------------------------------------------|----------|

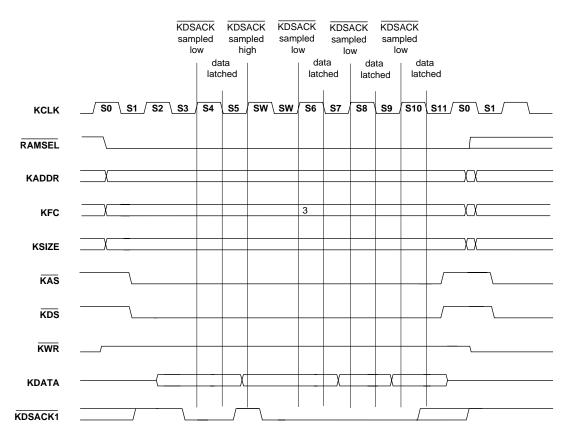

| Figure 2.26 :  | Burst Read Cycle                                                                | 2-92     |

| Figure 2.27 :  | Flowchart for a Burst Write Cycle - SCV64 as Local Master                       | er 2-94  |

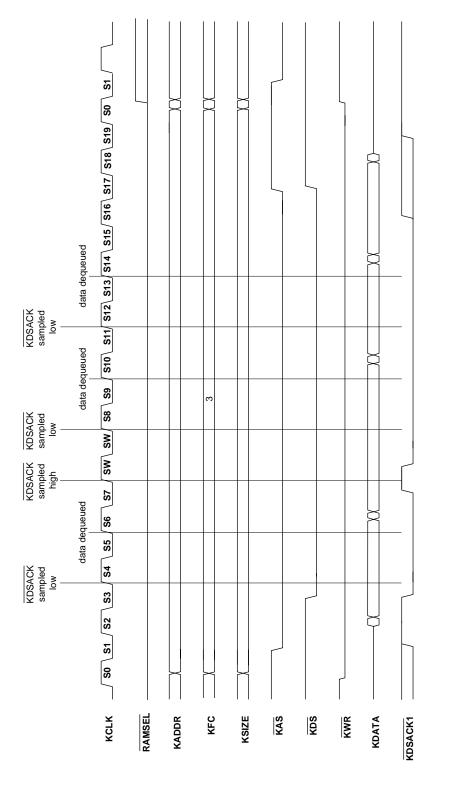

| Figure 2.28 :  | Burst Write Cycle                                                               | 2-95     |

| Figure 2.29 :  | Local interface for maximum burst length of 4 longwords                         | 2-96     |

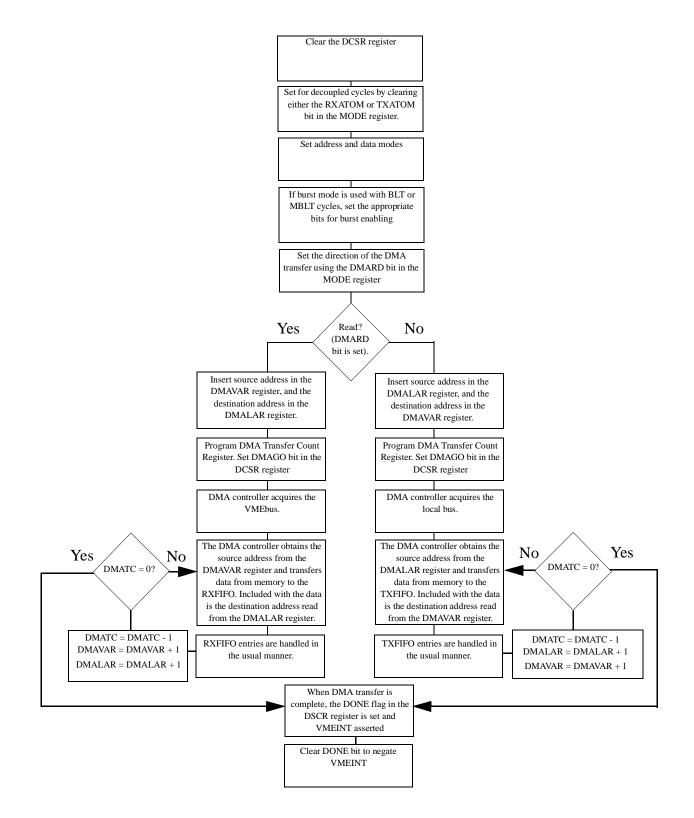

| Figure 2.30 :  | Procedural Steps in Normal DMA Reads and Writes                                 | 2-103    |

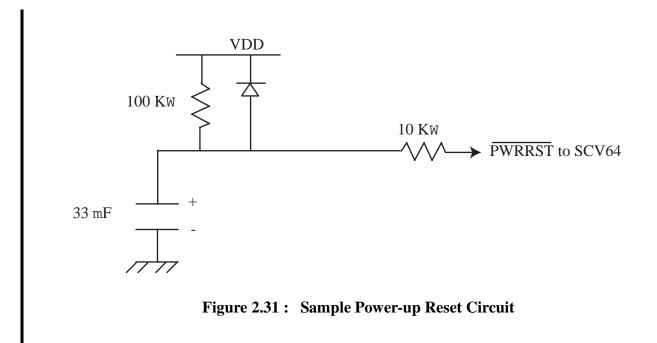

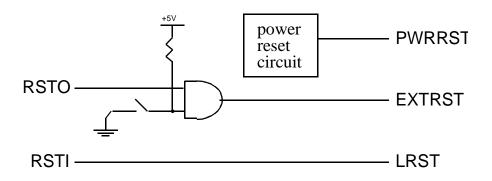

| Figure 2.31 :  | Sample Power-up Reset Circuit                                                   | 2-112    |

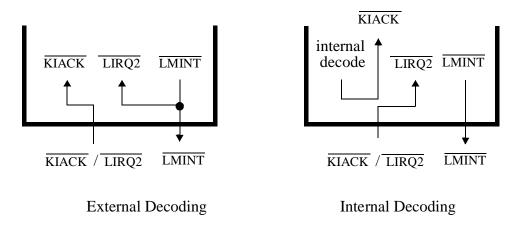

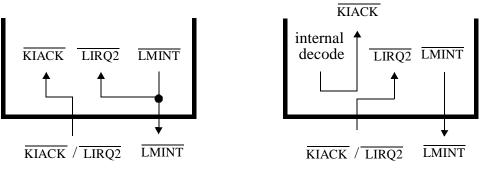

| Figure 2.32 :  | Connections with Different Local IACK Decoding                                  | 2-117    |

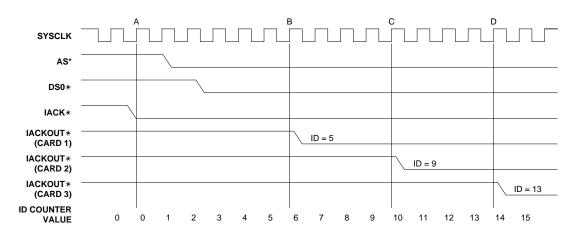

| Figure 2.33 :  | Timing for Auto-ID Cycle                                                        | 2-122    |

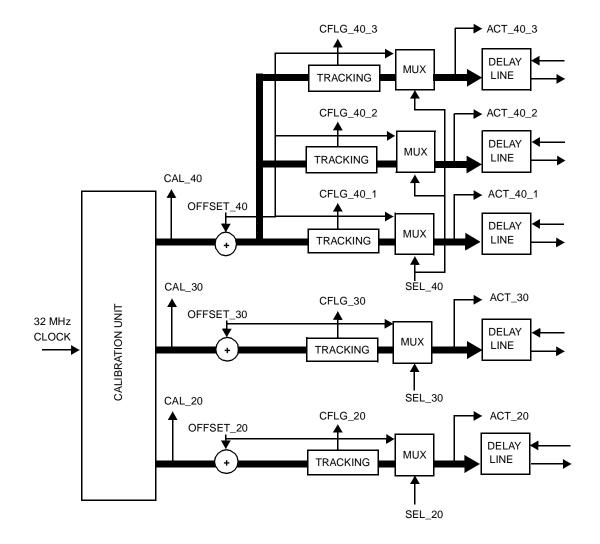

| Figure 2.34 :  | Functional Block Diagram for Delay Lines                                        | 2-125    |

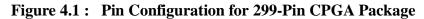

| Figure 4.1 :   | Pin Configuration for 299-Pin CPGA Package                                      | 4-11     |

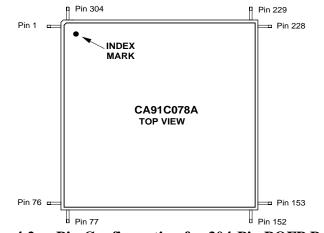

| Figure 4.2 :   | Pin Configuration for 304-Pin PQFP Package                                      | 4-12     |

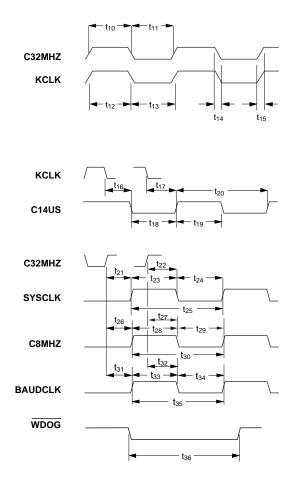

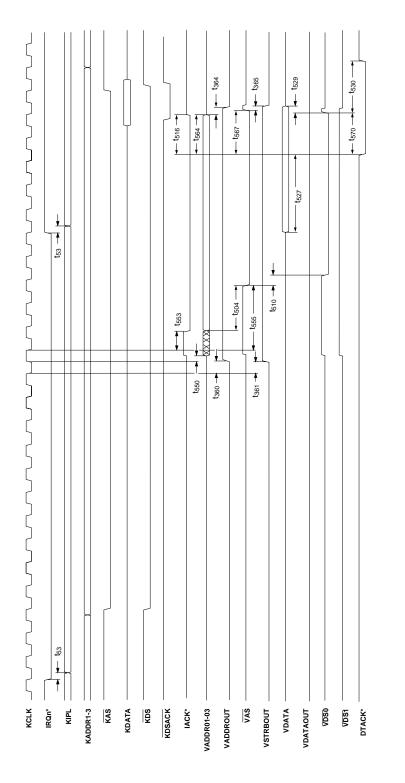

| Figure B.1 :   | Clocks and Timers                                                               | App B-14 |

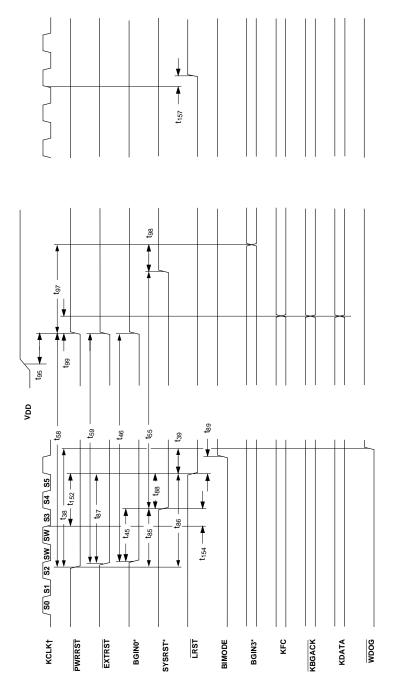

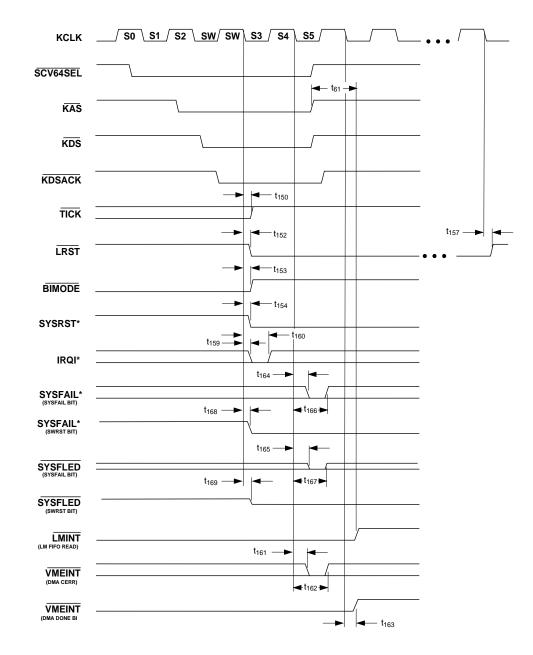

| Figure B.2 :   | Reset Timing                                                                    | App B-15 |

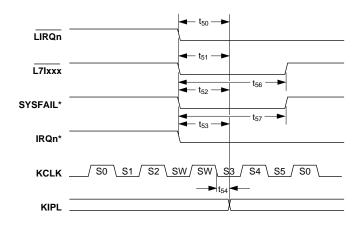

| Figure B.3 :   | Local Interrupts - Generation                                                   | App B-16 |

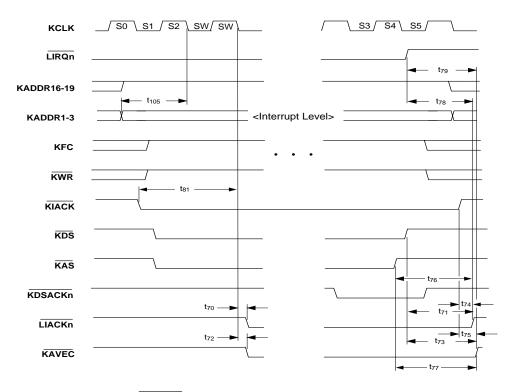

| Figure B.4 :   | Local Interrupts-Acknowledgment                                                 | App B-17 |

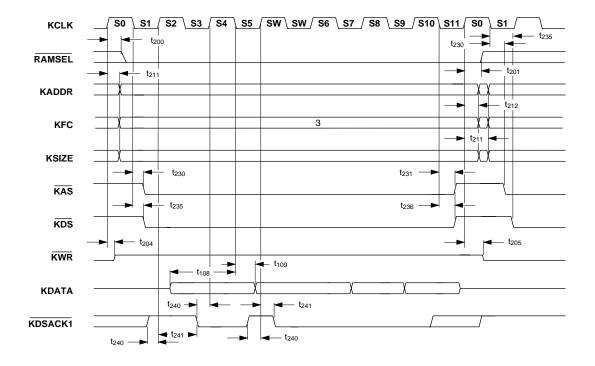

| Figure B.5 :   | Register Access                                                                 | App B-18 |

| Figure B.6 :   | Register Access Effects                                                         | App B-19 |

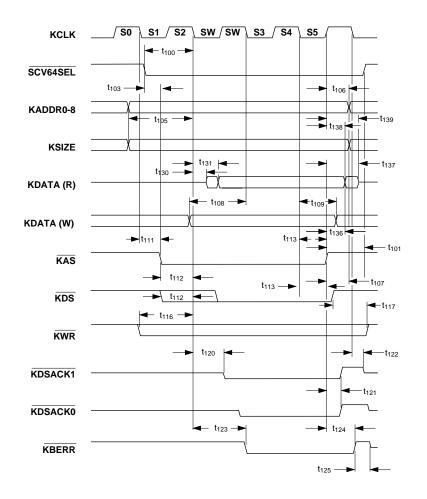

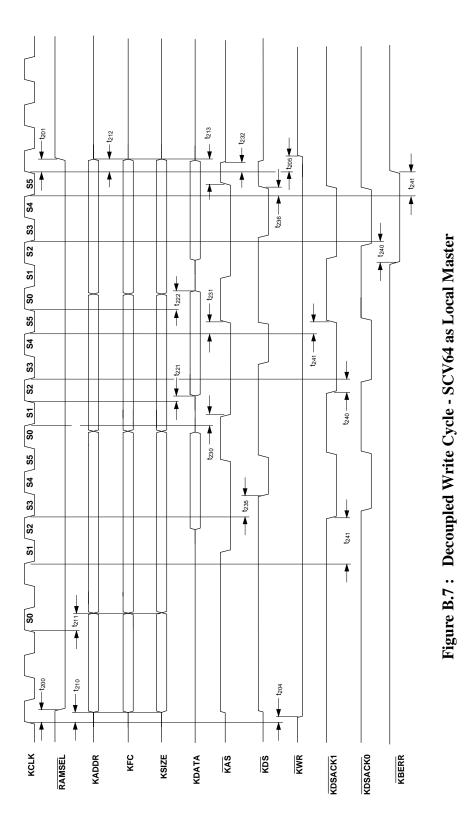

| Figure B.7 :   | Decoupled Write Cycle - SCV64 as Local Master                                   | App B-20 |

| Figure B.8 :   | Decoupled Write Cycle - SCV64 as Local Slave                                    | App B-21 |

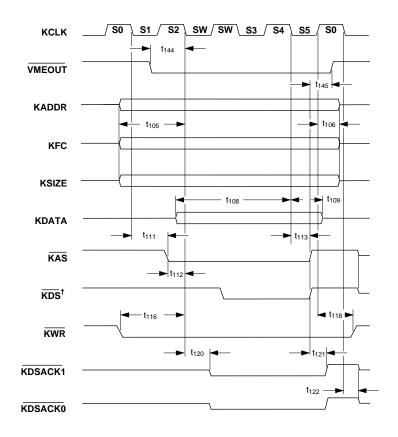

| Figure B.9 :   | Coupled Cycle - SCV64 as Local Master                                           | App B-22 |

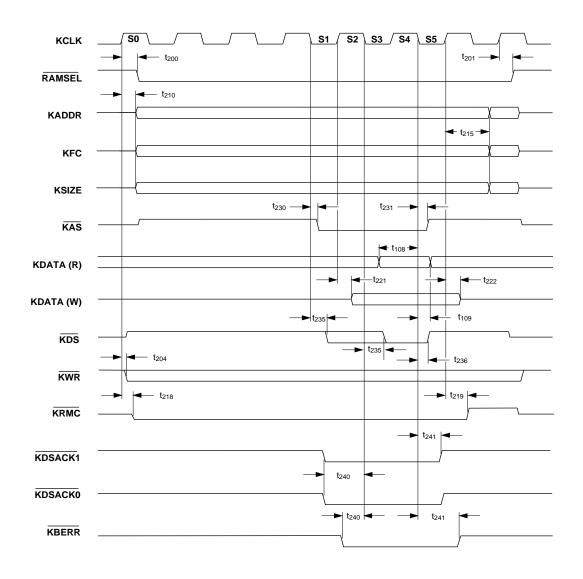

| Figure B.10 :  | Coupled Cycle - SCV64 as Local Slave                                            | App B-23 |

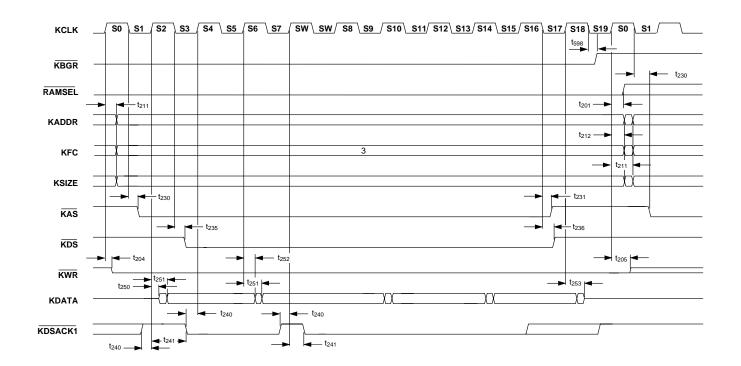

| Figure B.11 :  | Burst Write Cycle - SCV64 as Local Master                                       | App B-24 |

| Figure B.12 :  | Burst Read Cycle - SCV64 as Local Master                                        | App B-25 |

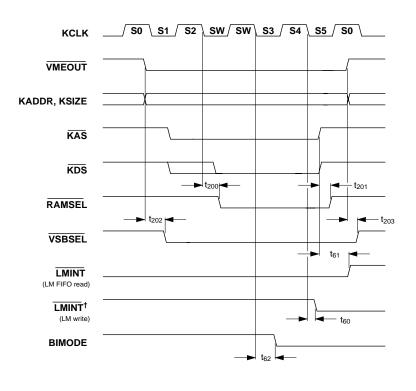

| Figure B.13 :  | Slave Image/VSB/Location Monitor Access                                         | App B-26 |

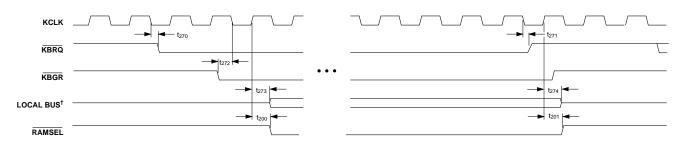

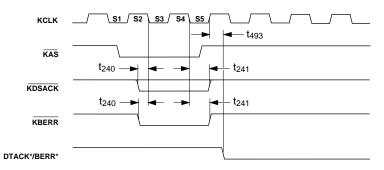

| Figure B.14a : | Local Requester – Arbiter Bypassed                                              | App B-27 |

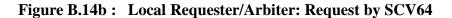

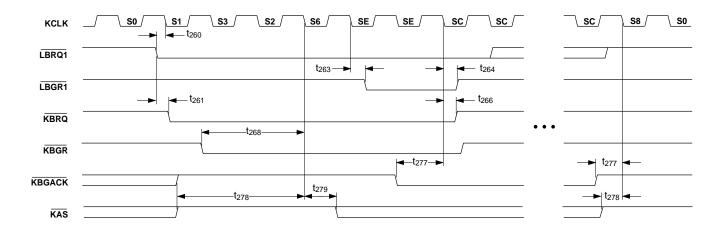

| Figure B.14b : | Local Requester/Arbiter: Request by SCV64                                       | App B-27 |

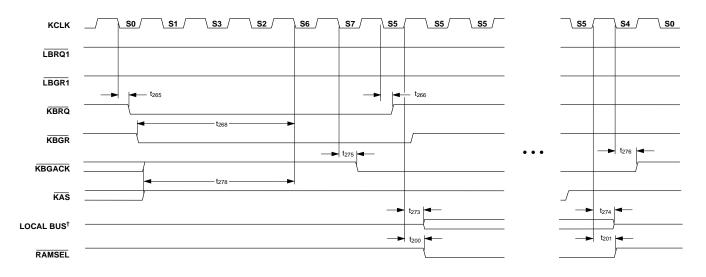

| Figure B.14c : | Local Requester/Arbiter: Request by an External Device<br>– with Acknowledge    | App B-28 |

| Figure B.14d : | Local Requester/Arbiter: Request by an External Device<br>– without Acknowledge | App B-28 |

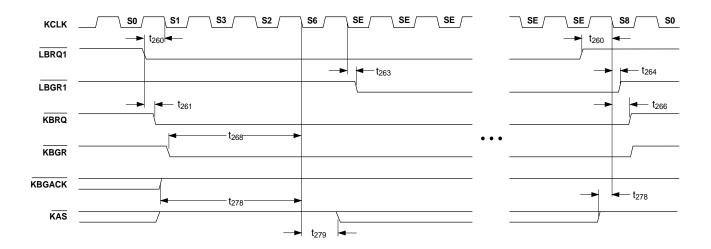

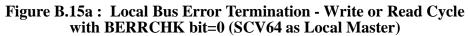

| Figure B.15a : | Local Bus Error Termination - Write or Read Cycle                               |          |

|                | with BERRCHK bit=0 (SCV64 as Local Master)App B-29                                              |

|----------------|-------------------------------------------------------------------------------------------------|

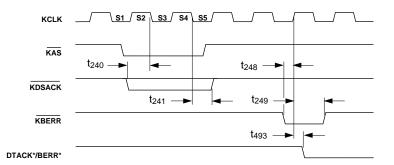

| Figure B.15b : | Local Bus Error Termination - Read Cycle with BERRCHK<br>bit=1 (SCV64 as Local Master) App B-29 |

| Figure B.15c : | Deadlock Retry Termination (SCV64 as Local Slave) App B-29                                      |

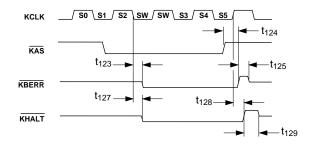

| Figure B.16 :  | Daisy Chain Driver Timing App B-30                                                              |

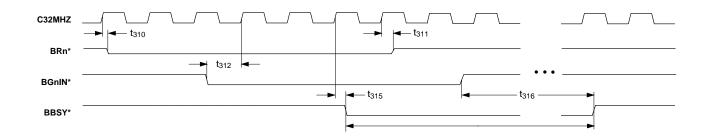

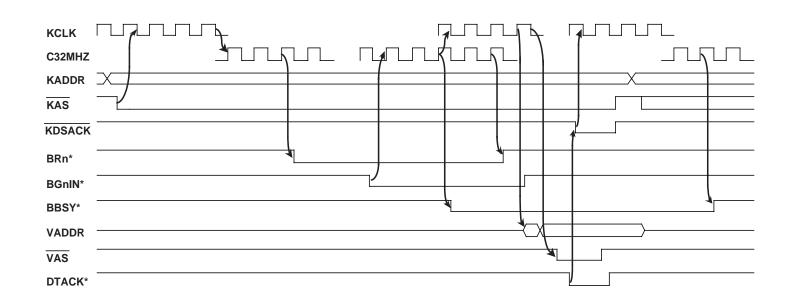

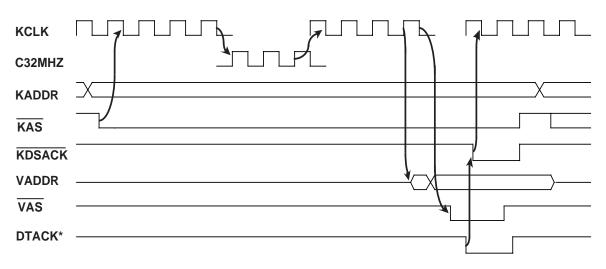

| Figure B.17a : | VMEbus Requester - Normal ReleaseApp B-31                                                       |

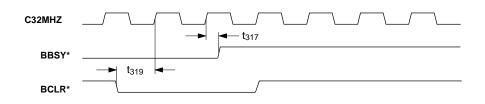

| Figure B.17b : | VMEbus Requester - Release with BCLR* App B-31                                                  |

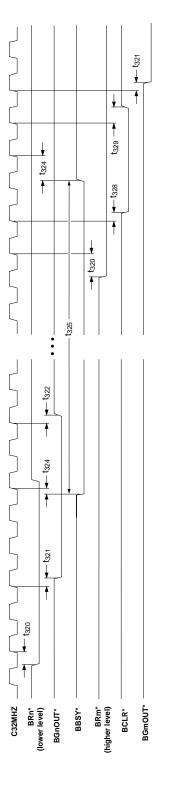

| Figure B.18 :  | VMEbus Arbiter Timing App B-32                                                                  |

| Figure B.19 :  | VMEbus Interrupter Timing App B-33                                                              |

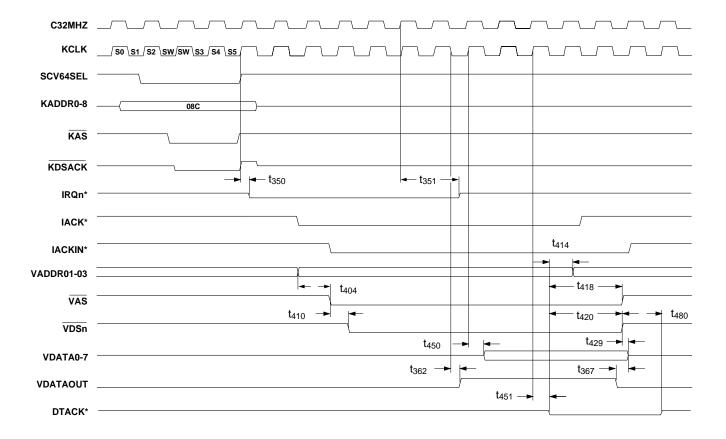

| Figure B.20 :  | VMEbus Interrupt Handler App B-34                                                               |

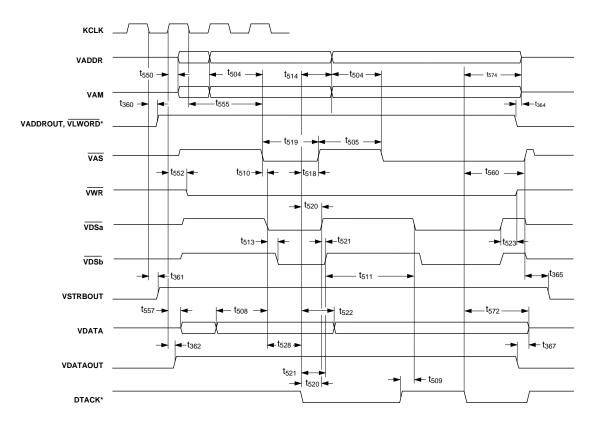

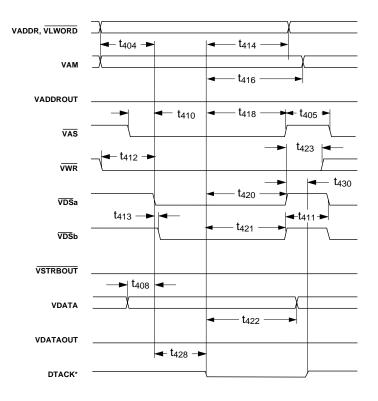

| Figure B.21 :  | Decoupled Write Cycle - SCV64 as VME Master App B-35                                            |

| Figure B.22 :  | Decoupled Write Cycle - SCV64 as VME Slave App B-36                                             |

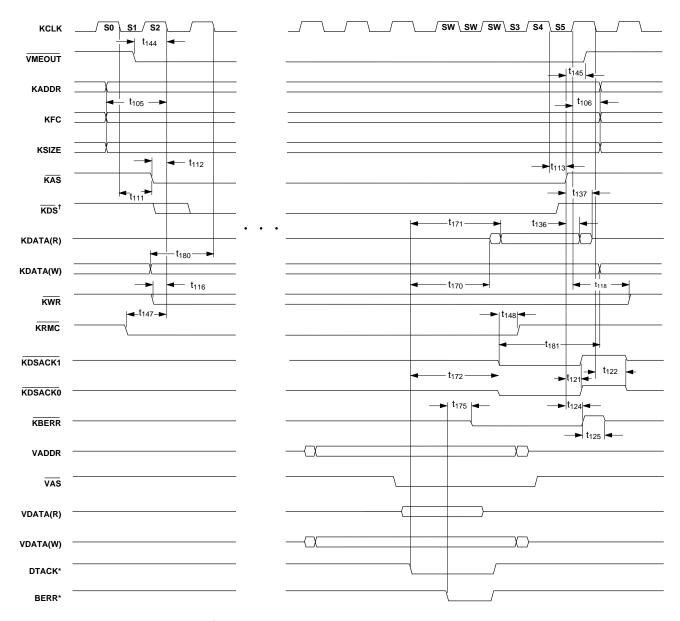

| Figure B.23 :  | Coupled Cycle - SCV64 as VME Master App B-37                                                    |

| Figure B.24 :  | Coupled Cycle - SCV64 as VME Slave App B-38                                                     |

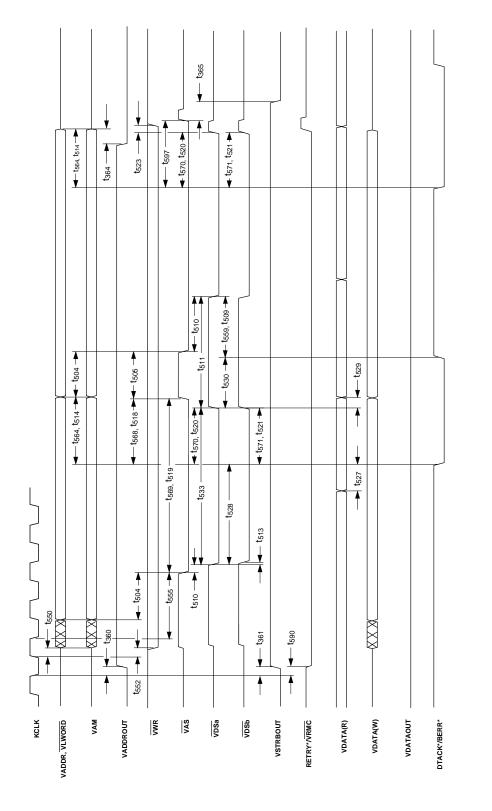

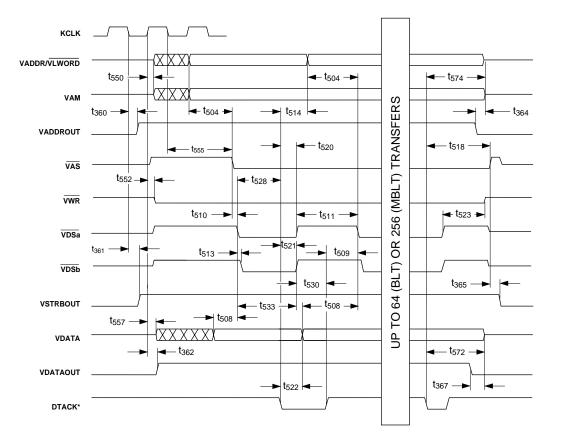

| Figure B.25 :  | BLT/MBLT Writes - SCV64 as VME Master App B-39                                                  |

| Figure B.26 :  | BLT/MBLT Writes - SCV64 as VME Slave App B-40                                                   |

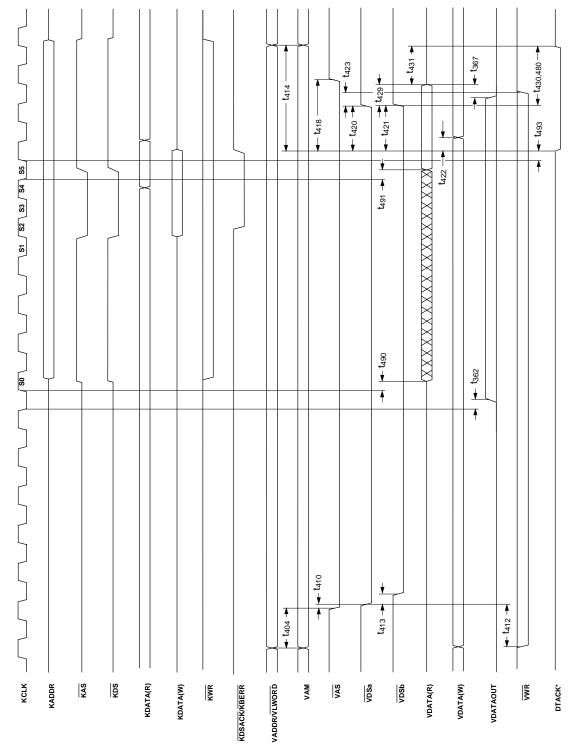

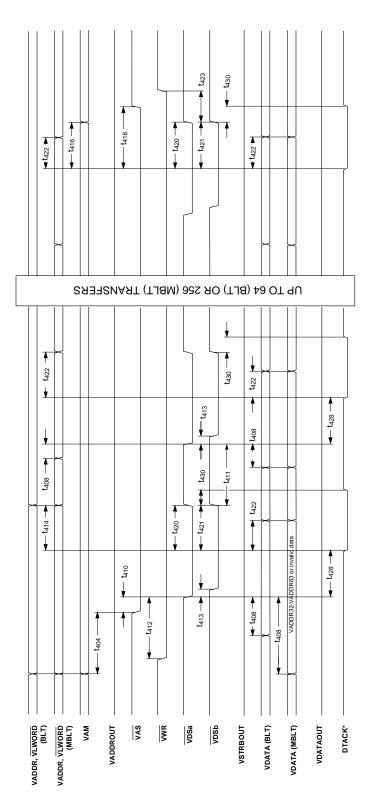

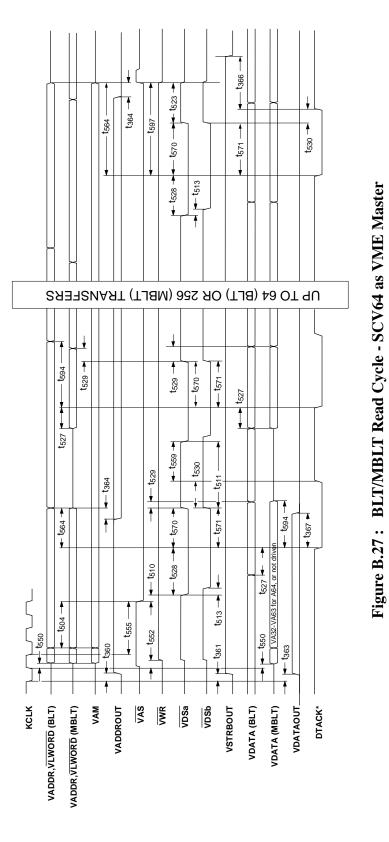

| Figure B.27 :  | BLT/MBLT Read Cycle - SCV64 as VME Master App B-41                                              |

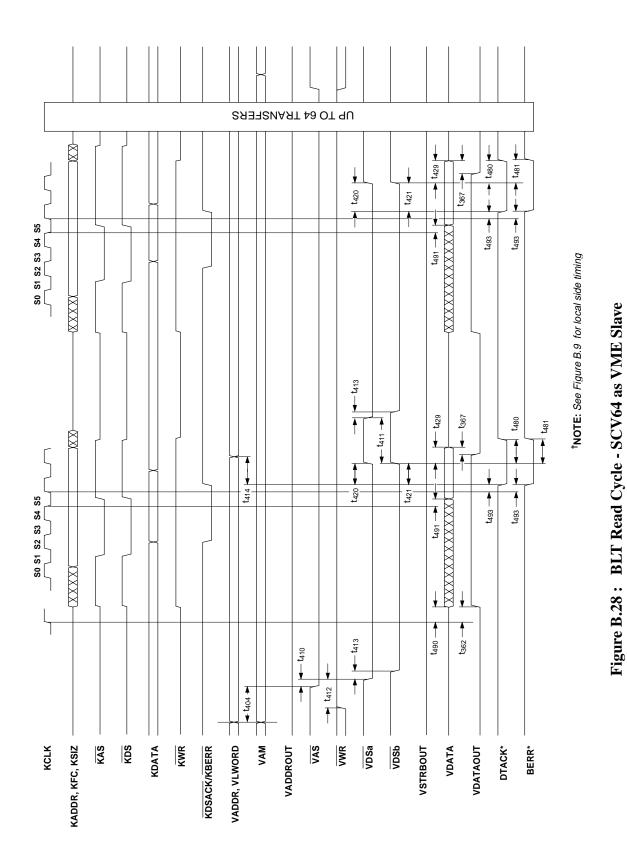

| Figure B.28 :  | BLT Read Cycle - SCV64 as VME Slave App B-42                                                    |

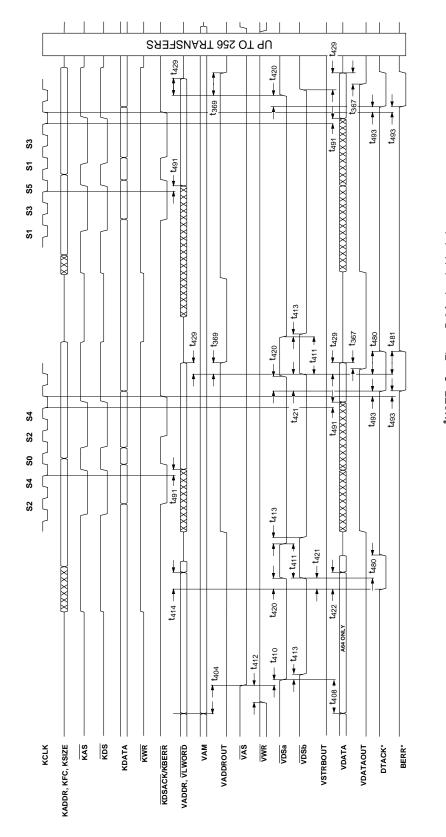

| Figure B.29 :  | MBLT Read Cycle - SCV64 as VME Slave App B-43                                                   |

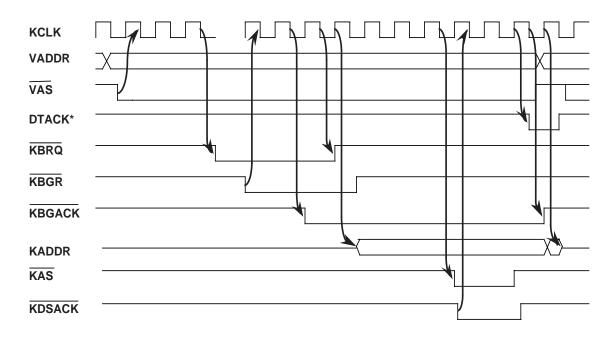

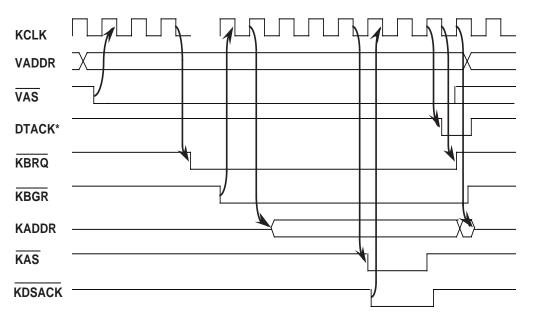

| Figure C.1 :   | SCV64 as VME master - RWD mode App C-3                                                          |

| Figure C.2 :   | SCV64 as VME master - ROR mode App C-4                                                          |

| Figure C.3 :   | Coupled Cycle - SCV64 as VME Slave (local arbiter active) App C-6                               |

| Figure C.4 :   | Coupled Cycle-SCV64 as VME Slave (local arbiter bypassed) App C-6                               |

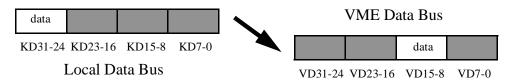

| Figure D.1 :   | Single Longword Aligned Byte Transfer with $SWAP = 0$ App D-2                                   |

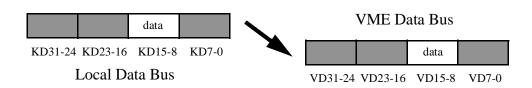

| Figure D.2 :   | Single Longword Aligned Byte Transfer with SWAP = 1 App D-2                                     |

| Figure D.3 :   | Tri-byte Transfer with BUSSIZ = 1 App D-4                                                       |

| Figure D.4 :   | Tri-byte Transfer with BUSSIZ = 0 App D-4                                                       |

| Figure E.1 :   | Orientation of the SCV64 (CPGA and PQFP) to Minimize Distance to the Connector                  |

| Figure E.2 :   | SCV64 Interface to VMEbus App E-5                                                               |

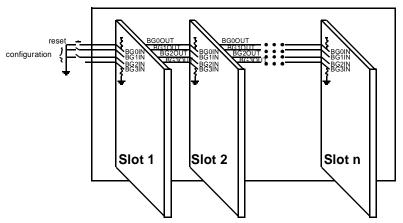

| Figure E.3 :   | Bus Grant Daisy Chain Usage in System App E-6                                                   |

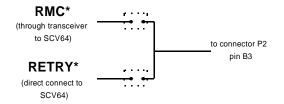

| Figure E.4 :   | Implementation of VRMC and RETRY* App E-7                                                       |

| Figure E.5 :  | Connections for Slave Only Design App E-10          |

|---------------|-----------------------------------------------------|

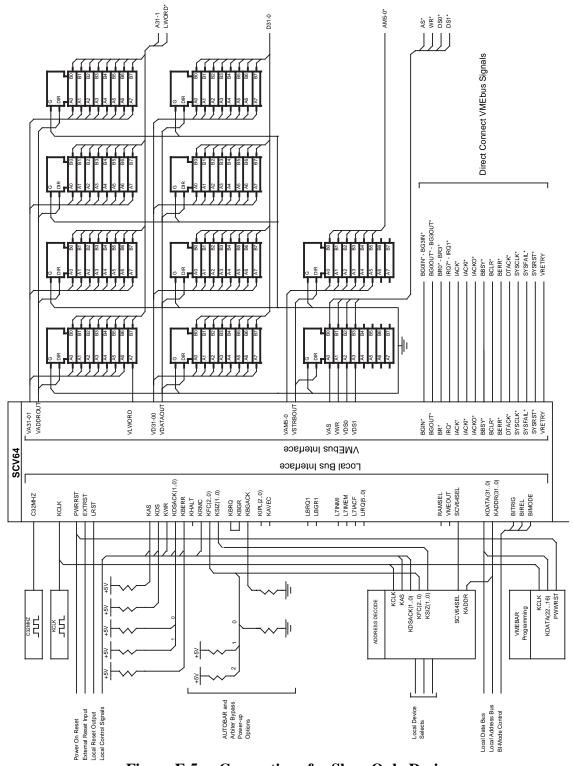

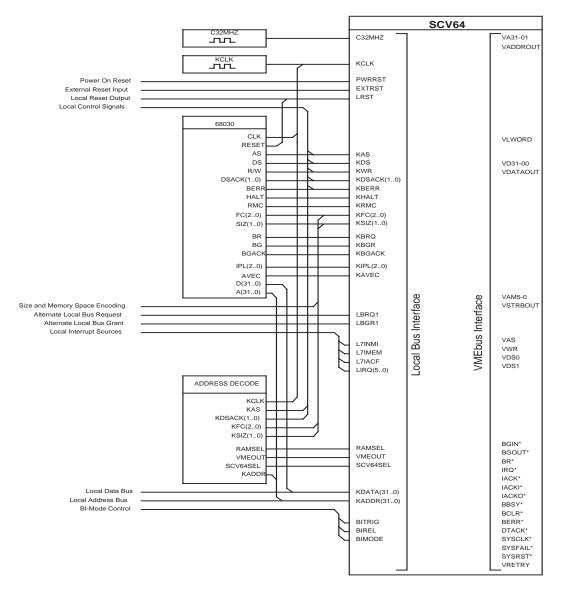

| Figure E.6 :  | Connections for 68030 Design App E-11               |

| Figure E.7 :  | Shared Local Bus Structure App E-13                 |

| Figure E.8 :  | Hierarchical Local Bus Structure App E-13           |

| Figure E.9 :  | MC68040 to SCV64 Bus Adapter Block Diagram App E-15 |

| Figure E.10 : | MC68040 Bus Transfer Control App E-16               |

| Figure E.11 : | SCV64 Bus Transfer Control App E-17                 |

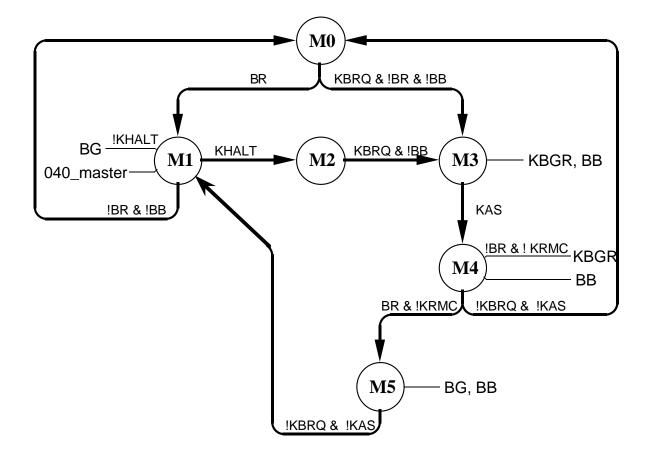

| Figure E.12 : | Cycle Translation Unit State Machine App E-19       |

| Figure E.13 : | Cycle Translation Timing Diagram App E-20           |

| Figure E.14 : | Local Bus Arbiter State Machine App E-24            |

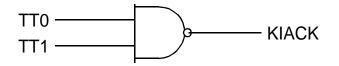

| Figure E.15 : | KIACK Generation App E-25                           |

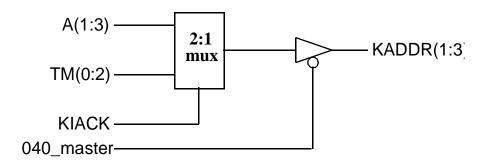

| Figure E.16 : | IACK Cycle Interrupt Level Generation App E-25      |

| Figure E.17 : | Reset Circuit App E-26                              |

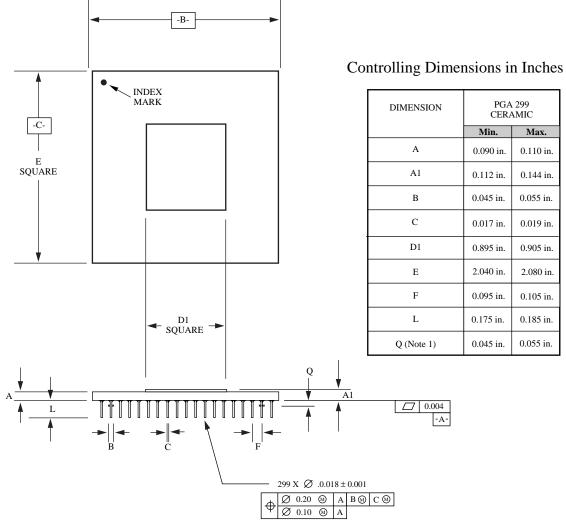

| Figure J.1 :  | 299-pin Cavity-down CPGA Package App J-1            |

| Figure J.2 :  | Mechanical Drawing for 304-Pin PQFP Package App J-2 |

# **List of Tables**

| Table 1.1 :  | Signals Used in this Manual                                          |      |

|--------------|----------------------------------------------------------------------|------|

| Table 1.2 :  | Technical Support Documentation References                           | 1-6  |

| Table 2.1 :  | VMEbus Request and Release Modes                                     |      |

| Table 2.2 :  | Setting VMEbus Request Levels                                        |      |

| Table 2.3 :  | Setting the VMEbus Ownership Timer                                   |      |

| Table 2.4 :  | Encoding for VMEbus Interrupt Levels                                 | 2-13 |

| Table 2.5 :  | KIPL2-KIPL0 Encoding for CPU Interrupt Levels                        |      |

| Table 2.6 :  | Mapping Bits for General Local Interrupts                            | 2-16 |

| Table 2.7 :  | Encoding for General Local Interrupt Level Mapping                   | 2-16 |

| Table 2.8 :  | Properties of Interrupt Sources                                      | 2-18 |

| Table 2.9 :  | Control Bits for Interrupt Sources                                   |      |

| Table 2.10 : | Status Bits for Interrupt Sources                                    | 2-21 |

| Table 2.11 : | Mapping Bits for General Local Interrupts                            | 2-22 |

| Table 2.12 : | Encoding for General Local Interrupt Level Mapping                   |      |

| Table 2.13 : | KADDR3-1 Encoding for CPU Interrupt Levels                           | 2-24 |

| Table 2.14 : | Correlation Between KFC1 and Local IACK Decoding                     |      |

| Table 2.15 : | Setting VMEbus Arbitration Modes                                     |      |

| Table 2.16 : | Setting VMEbus Time-out Period                                       |      |

| Table 2.17 : | Functions for Different Settings of KFC2 and KFC0                    |      |

| Table 2.18 : | TXCTL Register Bits Description                                      |      |

| Table 2.19 : | KFC Encodings for Transfer Type                                      |      |

| Table 2.20 : | Transfer Size Encoding                                               |      |

| Table 2.21 : | Port Size as Indicated by BUSSIZ and Cycle Termination               | 2-74 |

| Table 2.22 : | Byte Lanes for Different Port Sizes on the Local Bus                 |      |

| Table 2.23 : | Encoding for Address Offset on the Local Bus                         |      |

| Table 2.24 : | A Summary of SCV64 Register Accesses                                 |      |

| Table 2.25 : | SCV64 Register Map                                                   |      |

| Table 2.26 : | Local Bus Frequency and Allowable Wait States During<br>Burst Writes | 2-93 |

| Table 2.27 : | Bit Settings for DMA Transfer Modes                                   | 2-105    |

|--------------|-----------------------------------------------------------------------|----------|

| Table 2.28 : | Setting the Tick Timer Interval                                       | 2-116    |

| Table 2.29 : | VMEbus Signal Behavior in BI-mode                                     | 2-120    |

| Table 4.1 :  | DC Electrical Characteristics                                         |          |

| Table 4.2 :  | Pin List and DC Characteristics for SCV64 Signals<br>(-55°C to 125°C) |          |

| Table 4.3 :  | VMEbus Address and Data Input and Output Signal Bits                  | 4-7      |

| Table 4.4 :  | Local Bus Address and Data Input and Output Signal Bits               | 4-8      |

| Table 4.6 :  | Pin Assignments for Power                                             | 4-9      |

| Table 4.5 :  | Pin Assignments for Ground                                            | 4-9      |

| Table 4.7 :  | Input Capacitive Loading                                              | 4-10     |

| Table A.1 :  | A Summary of SCV64 Register Accesses                                  | App A-1  |

| Table A.2 :  | SCV64 Register Map                                                    | App A-2  |

| Table A.3 :  | DMA Local Address Register (DMALAR)                                   | App A-4  |

| Table A.4 :  | DMA VMEbus Address Register (DMAVAR)                                  | App A-4  |

| Table A.5 :  | DMA Transfer Count Register (DMATC)                                   | App A-5  |

| Table A.6 :  | Control and Status Register (DCSR)                                    | App A-6  |

| Table A.7 :  | VMEbus Slave Base Address Register (VMEBAR)                           | App A-9  |

| Table A.8 :  | A24 Slave Image Programming                                           | App A-10 |

| Table A.9 :  | A32 Slave Image Size (4 Bit Field)                                    | App A-12 |

| Table A.10 : | A32 Slave Image Base Address (5 Bit Field)                            | App A-12 |

| Table A.11 : | RXFIFO Data Register (RXDATA)                                         | App A-13 |

| Table A.12 : | RXFIFO Address Register (RXADDR)                                      | App A-13 |

| Table A.13 : | RXFIFO Control Register (RXCTL)                                       | App A-14 |

| Table A.14 : | VMEbus/VSB Bus Select (BUSSEL)                                        | App A-15 |

| Table A.15 : | VMEbus Interrupter Vector (IVECT)                                     | App A-16 |

| Table A.16 : | Access Protect Boundary Register (APBR)                               | App A-17 |

| Table A.17 : | TXFIFO Data Output Latch Register (TXDATA)                            | App A-18 |

| Table A.18 : | TXFIFO Address Output Latch Register (TXADDR)                         | App A-18 |

| Table A.19 : | Transmit FIFO AM Code and Control Bit Latch (TXCTL)                   | App A-19 |

| Table A.20 : | Location Monitor FIFO Read Port (LMFIFO)                              | App A-20 |

| Table A.22 :Slave A64 Base Address Register (SA64BAR)App A-25Table A.23 :Master A64 Base Address Register (MA64BAR)App A-26Table A.24 :Local Address Generator (LAG)App A-26Table A.25 :DMA VMEbus Transfer Count (DMAVTC)App A-27Table A.25 :Status Register 0 (STAT0)App A-28Table A.26 :Status Register 1 (STAT1)App A-29Table A.27 :Status Register 1 (STAT1)App A-29Table A.28 :General Control Register (GENCTL)App A-30Table A.29 :VMEbus Interrupter Requester (VINT)App A-31Table A.30 :VMEbus Reguester Register (VREQ)App A-32Table A.31 :VMEbus Arbiter Register (VREQ)App A-33Table A.32 :ID Register (ID)App A-34Table A.33 :Control and Status Register (CTL2)App A-35Table A.33 :Local Interrupt Status Register (TIS)App A-36Table A.35 :Local Interrupt Enable Register (ILS)App A-39Table A.36 :Level 7 Interrupt Enable Register (VIE)App A-39Table A.37 :Local Interrupt Enable Register (VIE)App A-40Table A.38 :VMEbus Interrupt Enable Register (IC10)App A-41Table A.41 :Local Interrupt S and 2 Control Register (IC32)App A-41Table A.42 :Miscellaneous Control Register (IDCT)App A-43Table A.43 :Delay Line Control Register (IDLST1)App A-44Table A.44 :Delay Line Status Register 2 (DLST2)App A-44Table A.45 :Delay Line Status Register 3 (D | Table A.21 : | Mode Control (MODE) App A-21                              |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------------------------------------------------------|

| Table A.24 :Local Address Generator (LAG)App A-26Table A.25 :DMA VMEbus Transfer Count (DMAVTC)App A-27Table A.26 :Status Register 0 (STAT0)App A-28Table A.27 :Status Register 1 (STAT1)App A-29Table A.28 :General Control Register (GENCTL)App A-30Table A.29 :VMEbus Interrupter Requester (VINT)App A-31Table A.30 :VMEbus Register (VREQ)App A-32Table A.31 :VMEbus Arbiter Register (VARB)App A-33Table A.32 :ID Register (ID)App A-34Table A.33 :Control and Status Register (CTL2)App A-34Table A.33 :Control and Status Register (TIS)App A-36Table A.35 :Local Interrupt Status Register (TIS)App A-37Table A.36 :Level 7 Interrupt Enable Register (ILE)App A-39Table A.36 :Level 7 Interrupt Enable Register (VIE)App A-40Table A.38 :VMEbus Interrupt Enable Register (VIE)App A-41Table A.39 :Local Interrupt S and 2 Control Register (IC32)App A-41Table A.41 :Local Interrupt S and 4 Control Register (IC54)App A-43Table A.42 :Miscellaneous Control Register (DLCT)App A-44Table A.45 :Delay Line Status Register 3 (DLST3)App A-44Table A.46 :Delay Line Status Register 3 (DLST3)App A-48Table A.47 :Mailbox Register 1 (MBOX1)App A-48Table A.48 :Mailbox Register 1 (MBOX3)App A-48                                                                  | Table A.22 : | Slave A64 Base Address Register (SA64BAR) App A-25        |

| Table A.25 :DMA VMEbus Transfer Count (DMAVTC)App A-27Table A.26 :Status Register 0 (STAT0)App A-28Table A.27 :Status Register 1 (STAT1)App A-29Table A.28 :General Control Register (GENCTL)App A-30Table A.29 :VMEbus Interrupter Requester (VINT)App A-31Table A.30 :VMEbus Requester Register (VREQ)App A-32Table A.31 :VMEbus Requester Register (VARB)App A-33Table A.32 :ID Register (ID)App A-34Table A.33 :Control and Status Register (CTL2)App A-35Table A.33 :Control and Status Register (TIS)App A-36Table A.35 :Local Interrupt Status Register (IIS)App A-37Table A.36 :Level 7 Interrupt Enable Register (IE)App A-39Table A.37 :Local Interrupt Enable Register (VIE)App A-40Table A.38 :VMEbus Interrupt Enable Register (VIE)App A-40Table A.39 :Local Interrupt S and 2 Control Register (IC32)App A-41Table A.41 :Local Interrupts 5 and 4 Control Register (IC54)App A-43Table A.42 :Miscellaneous Control Register (MISC)App A-43Table A.43 :Delay Line Control Register (DLCT)App A-44Table A.45 :Delay Line Status Register 2 (DLST2)App A-44Table A.46 :Delay Line Status Register 3 (DLST3)App A-48Table A.47 :Mailbox Register 0 (MBOX0)App A-48Table A.48 :Mailbox Register 1 (MBOX1)App A-48                                                   | Table A.23 : | Master A64 Base Address Register (MA64BAR) App A-26       |

| Table A.26 :Status Register 0 (STAT0)App A-28Table A.27 :Status Register 1 (STAT1)App A-29Table A.28 :General Control Register (GENCTL)App A-30Table A.29 :VMEbus Interrupter Requester (VINT)App A-31Table A.30 :VMEbus Requester Register (VREQ)App A-32Table A.31 :VMEbus Arbiter Register (VARB)App A-33Table A.32 :ID Register (ID)App A-34Table A.33 :Control and Status Register (CTL2)App A-35Table A.33 :Control and Status Register (CTL2)App A-36Table A.35 :Local Interrupt Status Register (IIS)App A-37Table A.36 :Level 7 Interrupt Enable Register (IE)App A-38Table A.37 :Local Interrupt Enable Register (VIE)App A-40Table A.38 :VMEbus Interrupt Enable Register (VIE)App A-40Table A.39 :Local Interrupt S and 2 Control Register (IC32)App A-41Table A.41 :Local Interrupts 5 and 4 Control Register (IC54)App A-43Table A.42 :Miscellaneous Control Register (MISC)App A-43Table A.43 :Delay Line Control Register (DLCT)App A-44Table A.44 :Delay Line Status Register 2 (DLST2)App A-48Table A.45 :Delay Line Status Register 3 (DLST3)App A-48Table A.48 :Mailbox Register 1 (MBOX1)App A-48Table A.49 :Mailbox Register 2 (MBOX2)App A-48                                                                                                          | Table A.24 : | Local Address Generator (LAG) App A-26                    |

| Table A.27 :Status Register 1 (STAT1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Table A.25 : | DMA VMEbus Transfer Count (DMAVTC) App A-27               |

| Table A.28 :General Control Register (GENCTL)App A-30Table A.29 :VMEbus Interrupter Requester (VINT)App A-31Table A.30 :VMEbus Requester Register (VREQ)App A-32Table A.31 :VMEbus Arbiter Register (VARB)App A-33Table A.32 :ID Register (ID)App A-34Table A.33 :Control and Status Register (CTL2)App A-35Table A.33 :Control and Status Register (TIS)App A-36Table A.34 :Level 7 Interrupt Status Register (TIS)App A-37Table A.35 :Local Interrupt Status Register (ID)App A-38Table A.36 :Level 7 Interrupt Enable Register (VIE)App A-39Table A.37 :Local Interrupt Enable Register (VIE)App A-39Table A.38 :VMEbus Interrupt Enable Register (VIE)App A-40Table A.39 :Local Interrupt S and 2 Control Register (IC10)App A-41Table A.41 :Local Interrupt 5 and 4 Control Register (IC54)App A-42Table A.42 :Miscellaneous Control Register (MISC)App A-44Table A.43 :Delay Line Control Register 1 (DLST1)App A-45Table A.45 :Delay Line Status Register 3 (DLST3))App A-47Table A.48 :Mailbox Register 0 (MBOX0)App A-48Table A.49 :Mailbox Register 1 (MBOX1)App A-48                                                                                                                                                                                               | Table A.26 : | Status Register 0 (STAT0) App A-28                        |

| Table A.29 :VMEbus Interrupter Requester (VINT).App A-31Table A.30 :VMEbus Requester Register (VREQ)App A-32Table A.31 :VMEbus Arbiter Register (VARB)App A-33Table A.32 :ID Register (ID)App A-34Table A.32 :ID Register (ID)App A-34Table A.33 :Control and Status Register (CTL2)App A-35Table A.34 :Level 7 Interrupt Status Register (7IS)App A-36Table A.35 :Local Interrupt Status Register (7IE)App A-37Table A.36 :Level 7 Interrupt Enable Register (7IE)App A-38Table A.37 :Local Interrupt Enable Register (VIE)App A-39Table A.38 :VMEbus Interrupt Enable Register (VIE)App A-40Table A.39 :Local Interrupt S and 2 Control Register (IC10)App A-41Table A.41 :Local Interrupts 5 and 4 Control Register (IC54)App A-42Table A.42 :Miscellaneous Control Register (MISC)App A-44Table A.43 :Delay Line Control Register (DLCT)App A-45Table A.44 :Delay Line Status Register 2 (DLST2)App A-46Table A.45 :Delay Line Status Register 3 (DLST3))App A-48Table A.48 :Mailbox Register 0 (MBOX0)App A-48Table A.49 :Mailbox Register 2 (MBOX2)App A-48                                                                                                                                                                                                             | Table A.27 : | Status Register 1 (STAT1) App A-29                        |

| Table A.30 :VMEbus Requester Register (VREQ)App A-32Table A.31 :VMEbus Arbiter Register (VARB)App A-33Table A.32 :ID Register (ID)App A-34Table A.33 :Control and Status Register (CTL2)App A-35Table A.34 :Level 7 Interrupt Status Register (TIS)App A-36Table A.35 :Local Interrupt Status Register (IIS)App A-37Table A.36 :Level 7 Interrupt Enable Register (IE)App A-38Table A.37 :Local Interrupt Enable Register (IE)App A-39Table A.38 :VMEbus Interrupt Enable Register (VIE)App A-40Table A.39 :Local Interrupts 1 and 0 Control Register (IC32)App A-41Table A.40 :Local Interrupts 5 and 2 Control Register (IC54)App A-42Table A.41 :Local Interrupts 5 and 4 Control Register (IC54)App A-44Table A.43 :Delay Line Control Register (DLCT)App A-44Table A.44 :Delay Line Status Register 1 (DLST1)App A-44Table A.45 :Delay Line Status Register 3 (DLST3))App A-48Table A.47 :Mailbox Register 0 (MBOX0)App A-48Table A.48 :Mailbox Register 1 (MBOX1)App A-48Table A.49 :Mailbox Register 3 (MBOX3)App A-48                                                                                                                                                                                                                                                 | Table A.28 : | General Control Register (GENCTL) App A-30                |

| Table A.31 :VMEbus Arbiter Register (VARB)App A-33Table A.32 :ID Register (ID)App A-34Table A.32 :ID Register (ID)App A-34Table A.33 :Control and Status Register (CTL2)App A-35Table A.34 :Level 7 Interrupt Status Register (7IS)App A-36Table A.35 :Local Interrupt Status Register (LIS)App A-37Table A.36 :Level 7 Interrupt Enable Register (7IE)App A-38Table A.37 :Local Interrupt Enable Register (VIE)App A-39Table A.38 :VMEbus Interrupt Enable Register (VIE)App A-40Table A.39 :Local Interrupts 1 and 0 Control Register (IC10)App A-41Table A.40 :Local Interrupts 3 and 2 Control Register (IC32)App A-41Table A.41 :Local Interrupts 5 and 4 Control Register (IC54)App A-43Table A.42 :Miscellaneous Control Register (MISC)App A-44Table A.43 :Delay Line Control Register 1 (DLST1)App A-45Table A.45 :Delay Line Status Register 3 (DLST3))App A-48Table A.47 :Mailbox Register 0 (MBOX0)App A-48Table A.49 :Mailbox Register 1 (MBOX1)App A-48Table A.49 :Mailbox Register 3 (MBOX3)App A-48                                                                                                                                                                                                                                                           | Table A.29 : | VMEbus Interrupter Requester (VINT) App A-31              |

| Table A.32 :ID Register (ID)App A-34Table A.33 :Control and Status Register (CTL2)App A-35Table A.34 :Level 7 Interrupt Status Register (7IS)App A-36Table A.35 :Local Interrupt Status Register (LIS)App A-37Table A.36 :Level 7 Interrupt Enable Register (7IE)App A-38Table A.37 :Local Interrupt Enable Register (VIE)App A-39Table A.38 :VMEbus Interrupt Enable Register (VIE)App A-40Table A.39 :Local Interrupts 1 and 0 Control Register (IC10)App A-41Table A.40 :Local Interrupts 3 and 2 Control Register (IC32)App A-41Table A.41 :Local Interrupts 5 and 4 Control Register (IC54)App A-42Table A.42 :Miscellaneous Control Register (MISC)App A-44Table A.43 :Delay Line Control Register 1 (DLST1)App A-45Table A.45 :Delay Line Status Register 3 (DLST2)App A-48Table A.47 :Mailbox Register 0 (MBOX0)App A-48Table A.49 :Mailbox Register 1 (MBOX1)App A-48Table A.49 :Mailbox Register 3 (MBOX3)App A-48                                                                                                                                                                                                                                                                                                                                                  | Table A.30 : | VMEbus Requester Register (VREQ) App A-32                 |

| Table A.33 :Control and Status Register (CTL2)App A-35Table A.34 :Level 7 Interrupt Status Register (7IS)App A-36Table A.35 :Local Interrupt Status Register (LIS)App A-37Table A.36 :Level 7 Interrupt Enable Register (7IE)App A-38Table A.36 :Level 7 Interrupt Enable Register (7IE)App A-39Table A.37 :Local Interrupt Enable Register (VIE)App A-40Table A.38 :VMEbus Interrupt Enable Register (VIE)App A-40Table A.39 :Local Interrupts 1 and 0 Control Register (IC10)App A-41Table A.40 :Local Interrupts 3 and 2 Control Register (IC32)App A-41Table A.41 :Local Interrupts 5 and 4 Control Register (IC54)App A-42Table A.42 :Miscellaneous Control Register (MISC)App A-44Table A.43 :Delay Line Control Register 1 (DLST1)App A-45Table A.45 :Delay Line Status Register 3 (DLST3))App A-47Table A.47 :Mailbox Register 0 (MBOX0)App A-48Table A.48 :Mailbox Register 1 (MBOX1)App A-48Table A.49 :Mailbox Register 3 (MBOX3)App A-48                                                                                                                                                                                                                                                                                                                          | Table A.31 : | VMEbus Arbiter Register (VARB) App A-33                   |

| Table A.34 :Level 7 Interrupt Status Register (7IS)App A-36Table A.35 :Local Interrupt Status Register (LIS)App A-37Table A.36 :Level 7 Interrupt Enable Register (7IE)App A-38Table A.36 :Local Interrupt Enable Register (7IE)App A-39Table A.37 :Local Interrupt Enable Register (LIE)App A-39Table A.38 :VMEbus Interrupt Enable Register (VIE)App A-40Table A.39 :Local Interrupts 1 and 0 Control Register (IC10)App A-41Table A.40 :Local Interrupts 3 and 2 Control Register (IC32)App A-41Table A.41 :Local Interrupts 5 and 4 Control Register (IC54)App A-42Table A.42 :Miscellaneous Control Register (MISC)App A-44Table A.43 :Delay Line Control Register (DLCT)App A-45Table A.44 :Delay Line Status Register 2 (DLST2)App A-46Table A.45 :Delay Line Status Register 3 (DLST3))App A-48Table A.47 :Mailbox Register 1 (MBOX1)App A-48Table A.49 :Mailbox Register 2 (MBOX2)App A-48                                                                                                                                                                                                                                                                                                                                                                           | Table A.32 : | ID Register (ID) App A-34                                 |

| Table A.35 :Local Interrupt Status Register (LIS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Table A.33 : | Control and Status Register (CTL2) App A-35               |

| Table A.36 :Level 7 Interrupt Enable Register (7IE)App A-38Table A.37 :Local Interrupt Enable Register (LIE)App A-39Table A.38 :VMEbus Interrupt Enable Register (VIE)App A-40Table A.39 :Local Interrupt S 1 and 0 Control Register (IC10)App A-41Table A.40 :Local Interrupts 3 and 2 Control Register (IC32)App A-41Table A.41 :Local Interrupts 5 and 4 Control Register (IC54)App A-42Table A.42 :Miscellaneous Control Register (MISC)App A-43Table A.43 :Delay Line Control Register (DLCT)App A-44Table A.44 :Delay Line Status Register 1 (DLST1)App A-46Table A.45 :Delay Line Status Register 3 (DLST3))App A-47Table A.47 :Mailbox Register 0 (MBOX0)App A-48Table A.49 :Mailbox Register 2 (MBOX2)App A-48Table A.49 :Mailbox Register 3 (MBOX3)App A-48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Table A.34 : | Level 7 Interrupt Status Register (7IS) App A-36          |

| Table A.37 :Local Interrupt Enable Register (LIE)App A-39Table A.38 :VMEbus Interrupt Enable Register (VIE)App A-40Table A.39 :Local Interrupts 1 and 0 Control Register (IC10)App A-41Table A.40 :Local Interrupts 3 and 2 Control Register (IC32)App A-41Table A.41 :Local Interrupts 5 and 4 Control Register (IC54)App A-42Table A.42 :Miscellaneous Control Register (MISC)App A-43Table A.43 :Delay Line Control Register (DLCT)App A-44Table A.44 :Delay Line Status Register 2 (DLST2)App A-46Table A.45 :Delay Line Status Register 3 (DLST3))App A-47Table A.48 :Mailbox Register 1 (MBOX1)App A-48Table A.49 :Mailbox Register 2 (MBOX2)App A-48Table A.50 :Mailbox Register 3 (MBOX3)App A-48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Table A.35 : | Local Interrupt Status Register (LIS) App A-37            |

| Table A.38 :VMEbus Interrupt Enable Register (VIE)App A-40Table A.39 :Local Interrupts 1 and 0 Control Register (IC10)App A-41Table A.40 :Local Interrupts 3 and 2 Control Register (IC32)App A-41Table A.41 :Local Interrupts 5 and 4 Control Register (IC54)App A-42Table A.42 :Miscellaneous Control Register (MISC)App A-43Table A.43 :Delay Line Control Register (DLCT)App A-44Table A.44 :Delay Line Status Register 1 (DLST1)App A-45Table A.45 :Delay Line Status Register 3 (DLST2)App A-46Table A.46 :Delay Line Status Register 3 (DLST3))App A-47Table A.47 :Mailbox Register 1 (MBOX1)App A-48Table A.49 :Mailbox Register 2 (MBOX2)App A-48Table A.50 :Mailbox Register 3 (MBOX3)App A-48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Table A.36 : | Level 7 Interrupt Enable Register (7IE) App A-38          |

| Table A.39 :Local Interrupts 1 and 0 Control Register (IC10)App A-41Table A.40 :Local Interrupts 3 and 2 Control Register (IC32)App A-41Table A.41 :Local Interrupts 5 and 4 Control Register (IC54)App A-42Table A.42 :Miscellaneous Control Register (MISC)App A-43Table A.43 :Delay Line Control Register (DLCT)App A-44Table A.44 :Delay Line Status Register 1 (DLST1)App A-45Table A.45 :Delay Line Status Register 2 (DLST2)App A-46Table A.46 :Delay Line Status Register 3 (DLST3))App A-47Table A.47 :Mailbox Register 1 (MBOX1)App A-48Table A.49 :Mailbox Register 2 (MBOX2)App A-48Table A.50 :Mailbox Register 3 (MBOX3)App A-48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Table A.37 : | Local Interrupt Enable Register (LIE) App A-39            |

| Table A.40 :Local Interrupts 3 and 2 Control Register (IC32)App A-41Table A.41 :Local Interrupts 5 and 4 Control Register (IC54)App A-42Table A.42 :Miscellaneous Control Register (MISC)App A-43Table A.43 :Delay Line Control Register (DLCT)App A-44Table A.43 :Delay Line Status Register 1 (DLST1)App A-45Table A.45 :Delay Line Status Register 2 (DLST2)App A-46Table A.46 :Delay Line Status Register 3 (DLST3))App A-47Table A.47 :Mailbox Register 0 (MBOX0)App A-48Table A.48 :Mailbox Register 1 (MBOX1)App A-48Table A.49 :Mailbox Register 3 (MBOX3)App A-48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Table A.38 : | VMEbus Interrupt Enable Register (VIE) App A-40           |

| Table A.41 :Local Interrupts 5 and 4 Control Register (IC54)App A-42Table A.42 :Miscellaneous Control Register (MISC)App A-43Table A.43 :Delay Line Control Register (DLCT)App A-44Table A.44 :Delay Line Status Register 1 (DLST1)App A-45Table A.45 :Delay Line Status Register 2 (DLST2)App A-46Table A.46 :Delay Line Status Register 3 (DLST3))App A-47Table A.47 :Mailbox Register 0 (MBOX0)App A-48Table A.48 :Mailbox Register 1 (MBOX1)App A-48Table A.49 :Mailbox Register 3 (MBOX3)App A-48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Table A.39 : | Local Interrupts 1 and 0 Control Register (IC10) App A-41 |

| Table A.42 :Miscellaneous Control Register (MISC)App A-43Table A.43 :Delay Line Control Register (DLCT)App A-44Table A.44 :Delay Line Status Register 1 (DLST1)App A-45Table A.45 :Delay Line Status Register 2 (DLST2)App A-46Table A.46 :Delay Line Status Register 3 (DLST3))App A-47Table A.47 :Mailbox Register 0 (MBOX0)App A-48Table A.48 :Mailbox Register 1 (MBOX1)App A-48Table A.49 :Mailbox Register 2 (MBOX2)App A-48Table A.50 :Mailbox Register 3 (MBOX3)App A-48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Table A.40 : | Local Interrupts 3 and 2 Control Register (IC32) App A-41 |

| Table A.43 :Delay Line Control Register (DLCT)App A-44Table A.44 :Delay Line Status Register 1 (DLST1)App A-45Table A.45 :Delay Line Status Register 2 (DLST2)App A-46Table A.46 :Delay Line Status Register 3 (DLST3))App A-47Table A.47 :Mailbox Register 0 (MBOX0)App A-48Table A.48 :Mailbox Register 1 (MBOX1)App A-48Table A.49 :Mailbox Register 2 (MBOX2)App A-48Table A.50 :Mailbox Register 3 (MBOX3)App A-48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Table A.41 : | Local Interrupts 5 and 4 Control Register (IC54) App A-42 |

| Table A.44 :Delay Line Status Register 1 (DLST1)App A-45Table A.45 :Delay Line Status Register 2 (DLST2)App A-46Table A.46 :Delay Line Status Register 3 (DLST3))App A-47Table A.47 :Mailbox Register 0 (MBOX0)App A-48Table A.48 :Mailbox Register 1 (MBOX1)App A-48Table A.49 :Mailbox Register 2 (MBOX2)App A-48Table A.50 :Mailbox Register 3 (MBOX3)App A-48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Table A.42 : | Miscellaneous Control Register (MISC) App A-43            |

| Table A.45 :Delay Line Status Register 2 (DLST2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Table A.43 : | Delay Line Control Register (DLCT) App A-44               |

| Table A.46 :Delay Line Status Register 3 (DLST3))App A-47Table A.47 :Mailbox Register 0 (MBOX0)App A-48Table A.48 :Mailbox Register 1 (MBOX1)App A-48Table A.49 :Mailbox Register 2 (MBOX2)App A-48Table A.50 :Mailbox Register 3 (MBOX3)App A-48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Table A.44 : | Delay Line Status Register 1 (DLST1) App A-45             |

| Table A.47 :Mailbox Register 0 (MBOX0)App A-48Table A.48 :Mailbox Register 1 (MBOX1)App A-48Table A.49 :Mailbox Register 2 (MBOX2)App A-48Table A.50 :Mailbox Register 3 (MBOX3)App A-48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Table A.45 : | Delay Line Status Register 2 (DLST2) App A-46             |

| Table A.48 :Mailbox Register 1 (MBOX1)App A-48Table A.49 :Mailbox Register 2 (MBOX2)App A-48Table A.50 :Mailbox Register 3 (MBOX3)App A-48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Table A.46 : | Delay Line Status Register 3 (DLST3)) App A-47            |

| Table A.49 :Mailbox Register 2 (MBOX2)App A-48Table A.50 :Mailbox Register 3 (MBOX3)App A-48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Table A.47 : | Mailbox Register 0 (MBOX0) App A-48                       |

| Table A.50 :Mailbox Register 3 (MBOX3)App A-48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Table A.48 : | Mailbox Register 1 (MBOX1) App A-48                       |