# **General Features**

The ATVaultIC400 is an ASSP designed to secure various systems against counterfeiting, cloning or identity theft. It is a hardware security module that can be used in many applications such as anti-cloning, access control or hardware protection.

|  | R |

|--|---|

| Cryptographic Services                                                                                                                                                                                                                                                                                                       | Cryptographic Algorithms                                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Public Key Pair Generation</li> </ul>                                                                                                                                                                                                                                                                               |                                                                                                                                                        |

| Digital Signature                                                                                                                                                                                                                                                                                                            | • DES / 3DES                                                                                                                                           |

| <ul> <li>Encryption / Decryption</li> </ul>                                                                                                                                                                                                                                                                                  | • AES 128/192/256 bits                                                                                                                                 |

| Message Digest                                                                                                                                                                                                                                                                                                               | <ul> <li>RSA up to 4096 bits<sup>(1)</sup></li> </ul>                                                                                                  |

| <ul> <li>Key Wrapping / Unwrapping</li> </ul>                                                                                                                                                                                                                                                                                | DSA up to 2048 bits                                                                                                                                    |

| HOTP One-Time Password Generation                                                                                                                                                                                                                                                                                            | ECC up to 384 bits                                                                                                                                     |

| True Random Number Generation                                                                                                                                                                                                                                                                                                |                                                                                                                                                        |

| Software Features                                                                                                                                                                                                                                                                                                            | Memory                                                                                                                                                 |

| <ul> <li>FIPS 140-2 Identity-based authentication<br/>using password, Secure Channel<br/>Protocol (SCP02 / SCP03) or Microsoft<sup>®</sup><br/>Minicard Driver strong authentication</li> <li>Rights Management (Administrator,<br/>Approved User, Non-approved User)</li> <li>Embedded Dynamic FAT12 File System</li> </ul> | <ul> <li>EEPROM 16 Kbytes (for user)</li> <li>Write Endurance 100 Kcycles</li> <li>Data Retention 10 Years</li> <li>2ms Program + 2ms Erase</li> </ul> |

| Communication                                                                                                                                                                                                                                                                                                                | Packages                                                                                                                                               |

| <ul> <li>Slave SPI Serial Interface, ATMEL<br/>Proprietary Protocol</li> <li>I<sup>2</sup>C (Two Wire Interface), ATMEL<br/>Proprietary Protocol</li> <li>ISO7816 UART using T=0 or T=1<br/>Protocols</li> </ul>                                                                                                             | <ul> <li>20-QFN (RoHS compliant)</li> <li>8-SOIC (RoHS compliant)</li> </ul>                                                                           |

| Hardware Platform                                                                                                                                                                                                                                                                                                            | Certifications                                                                                                                                         |

| <ul> <li>SecureAVR<sup>®</sup> 8-/16-bit RISC CPU</li> </ul>                                                                                                                                                                                                                                                                 |                                                                                                                                                        |

| <ul> <li>Hardware Random Number Generator</li> <li>Hardware 3DES Crypto Accelerator (112-<br/>bits keys)</li> <li>Hardware 32-bit Public Key Crypto<br/>Accelerator</li> </ul>                                                                                                                                               | <ul> <li>EAL4+ Certification</li> <li>FIPS 140-2 Security Level 3</li> <li>Microsoft CSP minidriver compliant</li> </ul>                               |

VaultIC<sup>™</sup> Family

# ATVaultIC400 Technical Datasheet

Notes: 1. Key sizes supported:

- Linear key size up to 2888 bits for CRT format only (2240 bits otherwise)

- 4096 bits for: CRT only Private exponent, Public exponent, CRT key generation

For more details about the alogrithms supported please refer to Table 2-1, "Supported Algorithms table", on page 8.

# Preliminary

This document is the complement to the "AT98SO Generic Datasheet" [1](TPR0395X- Available under Non-Disclosure Agreement only) for the ATVaultIC400. It only documents the values and set of features specific to this product.

# 1. Overview

### 1.1 Tampering resistance

The proven technology used in ATVaultIC400 security modules is already widespread and used in national ID/health cards, e-passports, bank cards (storing user Personal Identification Number, account numbers and authentication keys among others), pay-TV access control and cell phone SIM cards (allowing the storage of subscribers' unique ID, PIN code, and authentication to the network), where cloning must definitely be prevented. More than one billion of Secure Microcontrollers addressing all these applications have been already sold by Atmel and successfully implemented in many secure systems.

Atmel's security modules will advantageously replace complex and expensive proprietary antitampering protection system. Their advantages include low cost, ease of integration, higher security and proven technology.

They are designed to keep contents secure and avoid leaking information during code execution. While on regular microcontrollers, measuring current consumption, radio emissions and other side channels attacks may give precious information on the processed data or allow the manipulation of the data. Atmel's secure microcontrollers' security features include voltage, frequency and temperature detectors, illegal code execution prevention, tampering monitors and protection against side channel attacks and probing. The chips can detect tampering attempts and destroy sensitive data on such events, thus avoiding data confidentiality being compromised.

These features make cryptographic computations secure in comparison with regular microcontrollers whose memories can be easily duplicated. It is much safer to delegate cryptographic operations and storage of secret data (keys, identifiers, etc.) to an Atmel secure microcontroller.

### 1.2 Authentication capability

The methods to authenticate humans are generally classified into three cases: physical attribute (e.g. fingerprint, retinal pattern, facial scan, etc.), security device (e.g. ID card, security token, software token or cell phone) and something the user knows (e.g. a password/passphrase or a personal identification number).

To fight against identity theft, the multi-factor authentication is a stronger alternative to the classical login/password authentication (called weak authentication). It combines two or more authentication methods (often a password combined with a security token). Two-factor systems greatly reduce the likelihood of fraud by requiring the presence of a physical device used together with a password. If the physical device is lost or the password is compromised, security is still intact. NIST's authentication guideline [1] can be referred to for further details.

Multi-factor authentication requires a strong authentication. Anticloning is safely implemented through one-way or mutual strong authentication. Various authentication protocols exist (as specified in ISO9798-2 [3] or FIPS196 [4]), but the main method is the **challenge response authentication**:

- 1. The authenticator sends a challenge (e.g. a random number) to the equipment that must be authenticated ("the claimant").

- 2. The claimant computes a digital signature of the combination of this challenge with an optional identifier, using a private or secret key. The requested signature is then returned to the authenticator.

3. The authenticator checks the signature using either the same secret key or the public key associated to the claimant's private key and decides whether the claimant is authorized or not based on the signature verification result.

This strong authentication method requires storing secret data. Pure software multi-factor solutions are thus not reliable.

Numerous companies are now providing authentication solutions based on USB tokens. Tokens connected through USB are a convenient solution since they require no additional hardware. Atmel's turnkey USB Secure Microcontroller Solutions can help providers focus on their security model and their application without loosing too much time on tamper protection and other complex hardware security concerns.

### 1.3 Secure storage

If sensitive data is stored in files on a hard disk, even if those files are encrypted, the files can be stolen, cloned and subjected to various kinds of attacks (e.g. brute force or dictionary attack on passwords). Therefore secure microcontrollers-based hardware tokens are a must. Placing secrets outside the computer avoids risking exposure to malicious software, security breaches in web browsers, files stealing, etc.

### 1.4 Flexibility

The ATVaultIC400 product features:

- Various **communication interfaces** including SPI (Serial Protocol Interface), I<sup>2</sup>C (Twisted Wire Interface), USB (Universal Serial Bus) and ISO7816 SmartCard interface.

- Low pin count (Reset, Vcc, GND, and communication interface specific pins) making integration into an existing board simple. ATVaultIC400 modules are available in small packages (SOIC8 or QFN20) to fit into the most size-constrained devices.

- Low power consumption, in order to extend battery life in portable devices and low-power systems. ATVaultIC400 devices consume less than 400µA in standby mode, and only 10 to 20 mA during CPU-intensive operations depending on the required action.

- Embedded firmware that provides advanced functions:

- Secure storage: a fully user-defined non-volatile storage of sensitive or secret data.

- Identity-based authentication with user, administrator and manufacturer roles supported.

- Administration mode to manage user authentication data and security features

- Manufacturer mode to initialize the file system content and module parameters.

- Cryptographic command set to perform cryptographic operations using keys and data from the file system including: authentication, digital signature, encryption/decryption, hash, one-time password generation, random generation and public key pair generation.

- Public domain cryptographic algorithms such as DES, 3DES, AES, RSA<sup>®</sup> PKCS#1 v2.1, DSA, EC-DSA, MAC using DES, 3DES or AES

- Cryptographic protocols such as secret-key unilateral or mutual authentication [3] and public key based unilateral or mutual authentication [4].

- Secure Channel Protocol using 3DES or AES.

- Robust communication protocol stacked over the physical communication interfaces.

- Starter Kit with RSA<sup>®</sup> PKCS#11 [5] and Microsoft<sup>®</sup> MS-CAPI [6] libraries.

Atmel's application note [7] presents examples of efficient and cost effective IP protection applications utilizing secure chips in various embedded systems.

### 1.5 Typical application

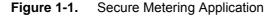

The ATVaultIC400 is a turnkey solution that combines powerful cryptographic capabilities and secure data storage. Ink Cartridge, Access Control or Smart meters are some examples of use of the ATVaultIC400.

Below is described an example of an ATVaultIC400 product used in a typical application : smart meters.

Metering (e.g. smart electric counters) involves a lot of know-how from the manufacturer and stakes financial transactions (billing). How to implement an electric meter that prevents tampering with electric consumption measurements, secures the transmissions to the servers, and protects itself against reverse engineering? The architecture exposed below can answer these concerns.

For more details about the architecture, please refer to the Application Note "How to secure Smart Meters using ATVaultIC products"[7].

### 1.6 Ordering Information

### 1.6.1 Legal

A Non-Disclosure Agreement must be signed with ATMEL.

An Export License for cryptographic hardware/software must be granted.

### 1.6.2 Quotation and Volume

For the minimum order of quantity and the annual volume, please contact your local ATMEL sales office.

### 1.6.3 Part Number

| Reference            | Description                                   |

|----------------------|-----------------------------------------------|

| ATVaultIC400-Z       | ATVaultIC400 chip in QFN20 package            |

| ATVaultIC400-R       | ATVaultIC400 chip in SOIC8 package            |

| ATVaultIC-STK02-400Z | Starter Kit for ATVaultIC400 in QFN20 package |

| ATVaultIC-STK02-400R | Starter Kit for ATVaultIC400 in SOIC8 package |

### 1.6.4 Starter Kit

The ATVaultIC Starter Kit provides an easy path to master the cryptographic and secure data storage features of the ATVaultIC secure modules. The content is :

- ATVaultIC400 samples with 1 dedicated test socket

- 1 generic USB to SPI / I<sup>2</sup>C / ISO7816 adapter

- 1 CD-ROM containing a support documentation set (getting started, application notes, reference design), some demo applications to get an insight into the ATVaultIC features, the "AT98 Manager" tool to design the file system and to personalize samples, a hardware independent cryptographic API with source code.

### 1.6.5 Demo Kit

TBD

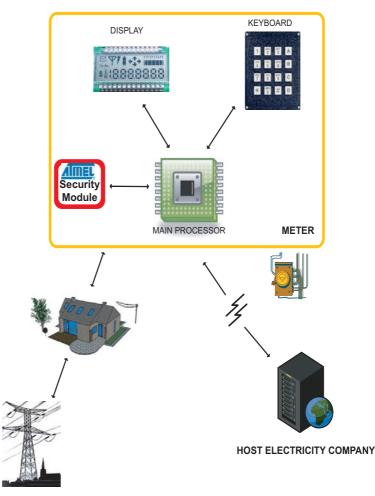

### 1.7 Software and Hardware Architecture

The ATVaultIC400 software architecture is as exposed on the diagram below.

# 2. Detailed Features

### 2.1 Communication Interfaces

The ATVaultIC400 embeds the following communication interfaces:

- SPI : up to 4 Mbps

- I<sup>2</sup>C : up to 400 kbps

- ISO7816 : up to 625 kbps

### 2.2 Security Mechanisms

The table below summarizes the cryptographic algorithms, and their identifiers, supported by the ATVaultIC400.

**Table 2-1.**Supported Algorithms table

| Cryptographic Services                                 | Supported Algorithms                                                                                                                                                                                 | Algo Identifier                                                                                                |

|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| Strong Authentication                                  | <ul> <li>Generic:<br/>ISO/IEC 9798-2 / FIPS 196 unilateral<br/>authentication protocol<br/>ISO/IEC 9798-2 mutual authentication<br/>protocol</li> <li>Password authentication</li> </ul>             | -                                                                                                              |

|                                                        | <ul> <li>Global Platform v2.2 Secure Channel 02<br/>(SCP02) using 3DES</li> <li>Global Platform v2.2 Secure Channel 03<br/>(SCP03) using AES</li> </ul>                                              | -                                                                                                              |

|                                                        | Microsoft Card Minidriver                                                                                                                                                                            | -                                                                                                              |

| Public Key-Pair Generation                             | <ul> <li>RSA key-pair generation</li> <li>Elliptic Curves key-pair generation</li> <li>DSA key-pair generation</li> </ul>                                                                            | • KGEN_RSA<br>• KGEN_ECDSA<br>• KGEN_DSA                                                                       |

| CMAC<br>(Cipher-based Message<br>Authentication Codes) | <ul> <li>ISO/IEC 9797-1 CBC-MAC algorithm 1<br/>using 3DES with 112-bit keys</li> <li>ISO/IEC 9797-1 CBC-MAC algorithm 3<br/>using DES with 56-bit keys</li> <li>NIST SP 800-38B AES CMAC</li> </ul> | <ul> <li>ALG_MAC_ISO9797_ALG1_3DES_<br/>EDE</li> <li>ALG_MAC_ISO9797_ALG3_DES</li> <li>ALG_CMAC_AES</li> </ul> |

| HMAC<br>(Hash-based Message Authen-<br>tication Codes) | • FIPS 198 HMAC with SHA-1 or SHA-256                                                                                                                                                                | • ALG_HMAC                                                                                                     |

| Message Signature                                      | <ul> <li>PKCS#1 v2.1 RSASSA PSS</li> <li>PKCS#1 v2.1 RSASSA-PKCS1-v1_5</li> <li>FIPS 186-2 ECDSA</li> <li>FIPS 186-2 DSA</li> </ul>                                                                  | • ALG_RSASSA_PKCS_PSS<br>• ALG_RSASSA_PKCS<br>• ALG_ECDSA<br>• ALG_DSA                                         |

| Cryptographic Services   | Supported Algorithms                                                                                                                                                                                                                                                           | Algo Identifier                                                                                                                                                                                                                                                                                                                             |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Message Encryption       | Block Ciphering:<br>• DES<br>• 3DES-EDE<br>• 3DES-EEE<br>• AES<br>Block chaining modes:<br>• ECB<br>• CBC<br>• OFB<br>• CFB<br>Padding methods:<br>• No padding<br>• Method 1<br>• Method 2<br>• PKCS 5<br>• PKCS 7<br>Encryption:<br>• PKCS#1 v2.1 RSAES-OAEP<br>• PKCS1-v1.5 | <ul> <li>ALG_DES</li> <li>ALG_3DES_EDE</li> <li>ALG_3DES_EEE</li> <li>ALG_3DES_EEE</li> <li>ALG_AES</li> <li>CHA_ECB</li> <li>CHA_CBC</li> <li>CHA_OFB</li> <li>CHA_CFB</li> <li>PAD_NONE</li> <li>PAD_METHOD_1</li> <li>PAD_METHOD_2</li> <li>PAD_PKCS5</li> <li>PAD_PKCS7</li> <li>ALG_RSAES_PKCS_OAEP</li> <li>ALG_RSAES_PKCS</li> </ul> |

| HOTP - One-Time Password | <ul> <li>Raw RSA X509 with no padding</li> <li>FIPS 198 HMAC algorithm with SHA1</li> </ul>                                                                                                                                                                                    | • ALG_RSAES_X509                                                                                                                                                                                                                                                                                                                            |

| Generation               | digest                                                                                                                                                                                                                                                                         | • ALG_HOTP                                                                                                                                                                                                                                                                                                                                  |

| Message Digest           | • SHA-1<br>• SHA-224<br>• SHA-256                                                                                                                                                                                                                                              | • ALG_SHA1<br>• ALG_SHA224<br>• ALG_SHA256                                                                                                                                                                                                                                                                                                  |

| Random Number Generation | FIPS 140-2 LVL3 using 3DES                                                                                                                                                                                                                                                     | -                                                                                                                                                                                                                                                                                                                                           |

# 3. Product Characteristics

## 3.1 Command Timings (T=25°C)

The table below includes only the ATVaultIC400 internal process. Communication protocol overhead and device-side process are excluded.

Table 3-1.

Command Timings table

| Command                  | Context                                                         | Min.    | Tun  | Max. | Unit |

|--------------------------|-----------------------------------------------------------------|---------|------|------|------|

| (or batch of commands)   | Context                                                         | IVIIII. | Тур. | Wax. | Unit |

| Encryption / Decryption  | DES-ECB, 258 bytes data                                         |         | TBD  |      | ms   |

| Encryption / Decryption  | 3DES-ECB, 258 bytes data                                        |         | TBD  |      | ms   |

| Encryption / Decryption  | AES                                                             |         | TBD  |      | ms   |

| Encryption               | RSAES-OAEP 1024-bit RSA key, public exp 2 <sup>16+1</sup>       |         | TBD  |      | ms   |

| Encryption               | RSAES-OAEP 2048-bit RSA key, public exp 2 <sup>16+1</sup>       |         | TBD  |      | ms   |

| Encryption               | RSAES-OAEP 4096-bit RSA key, public exp 2 <sup>16+1</sup>       |         | TBD  |      | ms   |

| Decryption               | RSAES-OAEP 1024-bit RSA key, public exp 2 <sup>16+1</sup>       |         | TBD  |      | ms   |

| Decryption               | RSAES-OAEP 2048-bit RSA key, public exp 2 <sup>16+1</sup>       |         | TBD  |      | ms   |

| Decryption               | RSAES-OAEP 4096-bit RSA key, public exp 2 <sup>16+1</sup>       |         | TBD  |      | ms   |

| Decryption               | RSAES-OAEP 4096-bit RSA CRT key, public exp 2 <sup>16+1</sup>   |         | TBD  |      | ms   |

| Signature / Verification | MAC DES algo 3 padding M2, 258 bytes data                       |         | TBD  |      | ms   |

| Signature / Verification | MAC DES algo 1 padding M2, 258 bytes data                       |         | TBD  |      | ms   |

| Signature / Verification | RSASSA-PSS 1024-bit RSA key, public exp 2 <sup>16+1</sup>       |         | TBD  |      | ms   |

| Signature / Verification | RSASSA-PSS 2048-bit RSA key, public exp 2 <sup>16+1</sup>       |         | TBD  |      | ms   |

| Signature / Verification | RSASSA-PSS 4096-bit RSA key, public exp 2 <sup>16+1</sup>       |         | TBD  |      | ms   |

| Signature / Verification | RSASSA-PKCS-v1_5 1024-bit RSA key, public exp 2 <sup>16+1</sup> |         | TBD  |      | ms   |

| Signature / Verification | RSASSA-PKCS-v1_5 2048-bit RSA key, public exp 2 <sup>16+1</sup> |         | TBD  |      | ms   |

| Signature / Verification | RSASSA-PKCS-v1_5 4096-bit RSA key, public exp 2 <sup>16+1</sup> |         | TBD  |      | ms   |

| Signature / Verification | DSA                                                             |         | TBD  |      | ms   |

| Signature / Verification | ECDSA                                                           |         | TBD  |      | ms   |

| Signature / Generation   | MAC DES algo 3 padding M2, 258 bytes data                       |         | TBD  |      | ms   |

| Signature / Generation   | MAC DES algo 1 padding M2, 258 bytes data                       |         | TBD  |      | ms   |

| Signature / Generation   | RSASSA-PSS 1024-bit RSA key, public exp 2 <sup>16+1</sup>       |         | TBD  |      | ms   |

| Signature / Generation   | RSASSA-PSS 2048-bit RSA key, public exp 2 <sup>16+1</sup>       |         | TBD  |      | ms   |

| Signature / Generation   | RSASSA-PSS 4096-bit RSA key, public exp 2 <sup>16+1</sup>       |         | TBD  |      | ms   |

| Signature / Generation   | RSASSA-PKCS-v1_5 1024-bit RSA key, public exp 2 <sup>16+1</sup> |         | TBD  |      | ms   |

| Signature / Generation   | RSASSA-PKCS-v1_5 2048-bit RSA key, public exp 2 <sup>16+1</sup> |         | TBD  |      | ms   |

| Command                | Context                                                         | Min. | Тур. | Max. | Unit |

|------------------------|-----------------------------------------------------------------|------|------|------|------|

| (or batch of commands) | Context                                                         |      | Typ: | maxi | onit |

| Signature / Generation | RSASSA-PKCS-v1_5 4096-bit RSA key, public exp 2 <sup>16+1</sup> |      | TBD  |      | ms   |

| Signature / Generation | DSA                                                             |      | TBD  |      | ms   |

| Signature / Generation | ECDSA                                                           |      | TBD  |      | ms   |

| Key Generation         | ECC                                                             |      | TBD  |      | ms   |

| Key Generation         | RSA 1024-bits, public exp 2 <sup>16+1</sup>                     | TBD  | TBD  | TBD  | ms   |

| Key Generation         | RSA 2048-bits, public exp 2 <sup>16+1</sup>                     | TBD  | TBD  | TBD  | ms   |

| Key Generation         | RSA 4096-bits, public exp 2 <sup>16+1</sup>                     | TBD  | TBD  | TBD  | ms   |

| Key Generation         | DSA                                                             | TBD  | TBD  | TBD  | ms   |

### 3.2 Maximum Ratings

Table 3-2.

Absolute Maximum Ratings<sup>(1)</sup>

| Operating Temperature            | 25°C to +85°C                                  |

|----------------------------------|------------------------------------------------|

| Supply Voltage V <sub>cc</sub>   | -0.3V to +7.5V                                 |

| Input Voltage V <sub>in</sub>    | V <sub>ss</sub> -0.3V to V <sub>cc</sub> +0.3V |

| Maximum Operating Voltage        |                                                |

| DC Current $V_{CC}$ and GND Pins | TBD                                            |

Notes: 1. Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### 3.3 AC/DC Characteristics (1.62V - 5.5V range; T= -25°C to +85°C)

| Table 3-3. | AC/DC Characteristics ( | 1.62V - 5.50V range | ; T= -25°C to +85°C) |

|------------|-------------------------|---------------------|----------------------|

|            |                         | noet oloot lange    | , 0 0 10 00 0        |

| Symbol           | Parameter                                                                    | Condition                         | Min.                 | Тур. | Max.                                         | Unit |

|------------------|------------------------------------------------------------------------------|-----------------------------------|----------------------|------|----------------------------------------------|------|

| $V_{CC}$         | Supply Voltage                                                               |                                   | 1.62                 |      | 5.5                                          | V    |

| V <sub>SS</sub>  | Ground                                                                       |                                   |                      |      |                                              |      |

| V <sub>MAX</sub> | Voltage Monitor: high level detection                                        |                                   | 7                    |      |                                              | V    |

| V <sub>MIN</sub> | Voltage Monitor: low level detection                                         | 3V, 5V<br>1.8V, 3V, 5V            |                      |      | 2.4<br>1.5                                   | V    |

| T <sub>MAX</sub> | Temperature Monitor: high level detection                                    |                                   | 85                   |      |                                              | °C   |

| T <sub>MIN</sub> | Temperature Monitor: low level detection                                     |                                   |                      |      | -25                                          | °C   |

| V <sub>IH</sub>  | Input High Voltage - I/O0,CLK,RST,<br>MISO,MOSI,SCK, SPI_SEL, SS,A04         |                                   | 0.7*V <sub>CC</sub>  |      | V <sub>CC</sub> +0.3                         | V    |

| V <sub>IL</sub>  | Input Low Voltage I/O0,CLK,RST,<br>MISO,MOSI,SCK, SPI_SEL, SS,A04            |                                   | V <sub>SS</sub> -0.3 |      | 0.2*V <sub>CC</sub>                          | V    |

| I <sub>IH</sub>  | Leakage High Current- I/O0,CLK,RST,<br>MISO,MOSI,SCK, SPI_SEL, SS,A04        | V <sub>IN</sub> = V <sub>IH</sub> | -10                  |      | 10                                           | μA   |

| I <sub>IL</sub>  | Leakage Low Current - I/O0,CLK,RST,<br>MISO,MOSI,SCK, SPI_SEL, SS,A04        | V <sub>IN</sub> = V <sub>IL</sub> | -40                  |      | 10                                           | μA   |

| V <sub>OL</sub>  | Output Low Voltage - I/O 0,SS<br>Output Low Voltage - A04,MISO,<br>MOSI, SCK | I <sub>OL</sub> =1mA              | 0                    |      | 0.08*V <sub>CC</sub><br>0.15*V <sub>CC</sub> | V    |

| V <sub>OH</sub>  | Output High Voltage - I/O 0,SS, A04,<br>MISO, MOSI, SCK                      | I <sub>OH</sub> = 1mA             | 0.7*V <sub>CC</sub>  |      | V <sub>cc</sub>                              | V    |

| Symbol           | Parameter                        | Condition                                                                                                                                                                                                                                                                                                             | Min.                                                                                                                                                                                                                                  | Тур.                                                                                              | Max.                                                                           | Unit                      |

|------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|---------------------------|

| R <sub>I/O</sub> | Pin Pull-up I/O0, RST,SPI_SEL,SS |                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                       | 220                                                                                               |                                                                                | KOhm                      |

| f <sub>scк</sub> | SPI Clock (Input)                | Duty<br>cycle=40% to<br>60%                                                                                                                                                                                                                                                                                           | 0.1                                                                                                                                                                                                                                   |                                                                                                   | 4                                                                              | MHz                       |

| T <sub>r</sub>   | I/O Output Rise Time (HRD Mode)  | C <sub>out</sub> =30pF<br>R <sub>pullup</sub> =20kOhm                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                       |                                                                                                   | 1                                                                              | μs                        |

| T <sub>f</sub>   | I/O Output Fall Time             | C <sub>out</sub> =30pF<br>R <sub>pullup</sub> =20kOhm                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                       |                                                                                                   | 1                                                                              | μs                        |

| I <sub>cc</sub>  | Typical Current at 25°C          | <ul> <li>Chip in low pov</li> <li>400µA when</li> <li>400µA when signal in high</li> <li>Chip awaken, r</li> <li>6mA when ex</li> <li>10mA when ex</li> <li>10mA when ex</li> <li>20mA when ex</li> <li>20mA when ex</li> <li>4mA when ex</li> <li>4mA when ex</li> <li>10mA when ex</li> <li>10mA when ex</li> </ul> | external clo<br>no external<br>no crypto rur<br>xternal clock<br>no external clock | clock is<br>nning:<br>supplie<br>clock is<br>tion d<br>supplie<br>clock is<br>ring DEs<br>supplie | supplied (C<br>supplied (C<br>uring RS<br>ed<br>supplied (C<br>S computationed | LK<br>A/ECC<br>LK<br>ons: |

### 3.4 Timings

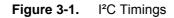

### 3.4.1 I<sup>2</sup>C Timings

The table below describes the requirements for devices connected to the  $I^2C$  Bus. The ATVaultIC400 I<sup>2</sup>C Interface meets or exceeds these requirements under the noted conditions.

Timing symbols refer to Figure 3-1.

Table 3-4.I<sup>2</sup>C Requirements

| Symbol              | Parameter                                        | Condition | Min | Max | Unit |

|---------------------|--------------------------------------------------|-----------|-----|-----|------|

| t <sub>r</sub>      | Rise Time for both SDA and SCL                   |           | TBD | TBD | ns   |

| t <sub>of</sub>     | Output Fall Time from $V_{IHmin}$ to $V_{ILmax}$ |           | TBD | TBD | ns   |

| f <sub>SCL</sub>    | SCL Clock Frequency                              |           | TBD | 100 | kHz  |

| t <sub>HD;STA</sub> | Hold Time (repeated) START Condition             |           | TBD | TBD | μs   |

| t <sub>LOW</sub>    | Low Period of the SCL Clock                      |           | TBD | TBD | μs   |

| t <sub>HIGH</sub>   | High period of the SCL clock                     |           | TBD | TBD | μs   |

| t <sub>SU;STA</sub> | Set-up time for a repeated START condition       |           | TBD | TBD | μs   |

| t <sub>HD;DAT</sub> | Data hold time                                   |           | TBD | TBD | μs   |

| t <sub>SU;DAT</sub> | Data setup time                                  |           | TBD | TBD | ns   |

| t <sub>su;sto</sub> | Setup time for STOP condition                    |           | TBD | TBD | μs   |

| t <sub>BUF</sub>    | Bus free time between a STOP and START condition |           | TBD | TBD | μs   |

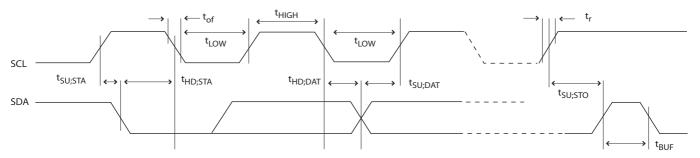

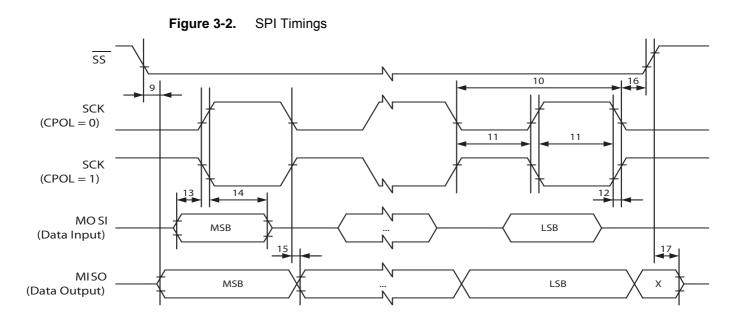

### 3.4.2 SPI Timings

The table below describes the requirements for devices connected to the SPI. The ATVaultIC400 SPI meets or exceeds these requirements under the noted conditions.

See Figure 3-2 for details.

| See figure | Description          | Condition | Min | Тур | Max | Unit |

|------------|----------------------|-----------|-----|-----|-----|------|

| 9          | SS low to out        |           |     | TBD |     | ns   |

| 10         | SCK period           |           |     | TBD |     | ns   |

| 11         | SCK high/low         |           |     | TBD |     | ns   |

| 12         | Rise/Fall time       |           |     | TBD |     | ns   |

| 13         | Setup                |           |     | TBD |     | ns   |

| 14         | Hold                 |           |     | TBD |     | ns   |

| 15         | SCK to out           |           |     | TBD |     | ns   |

| 16         | SCK to SS high       |           |     | TBD |     | ns   |

| 17         | SS high to tri-state |           |     | TBD |     | ns   |

| 18         | SS low to SCK        |           |     | TBD |     | ns   |

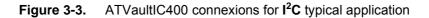

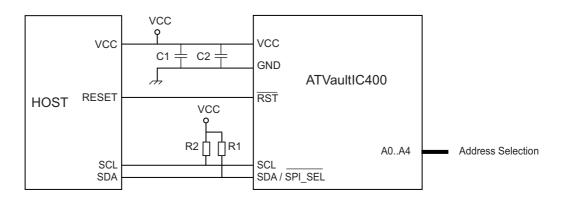

### 3.5 Connexions for Typical Application

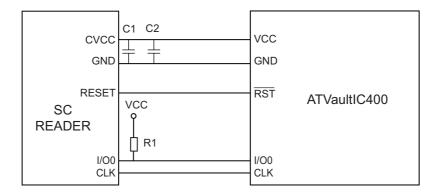

Figure 3-5. ATVaultIC400 connexions for ISO7816 typical application

| Configuration    | Reference | Description                        | Typ.Value | Comment                |

|------------------|-----------|------------------------------------|-----------|------------------------|

|                  | R1, R2    | Pull-Up Resistors                  | 2.2 kΩ    | Recommended            |

| l <sup>2</sup> C | C1        | Power Supply Decoupling Capacitors | 4.7 µF    | Recommended            |

|                  | C2        | Power Supply Decoupling Capacitors | 10 nF     | Recommended            |

| SPI              | C1        | Power Supply Decoupling Capacitors | 4.7 µF    | Recommended            |

|                  | C2        | Power Supply Decoupling Capacitors | 10 nF     | Recommended            |

|                  | R1        | Pull-Up Resistor                   | 20 kΩ     | usually on reader side |

| ISO7816          | C1        | Power Supply Decoupling Capacitors | 4.7 µF    | usually on reader side |

|                  | C2        | Power Supply Decoupling Capacitors | 10 nF     | usually on reader side |

Table 3-6. External components, Bill of Materials

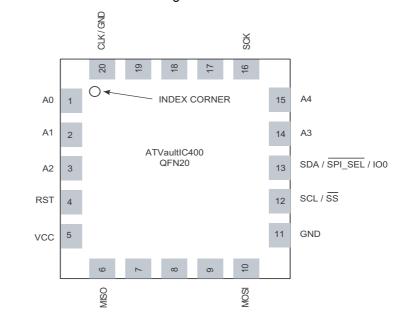

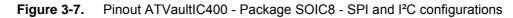

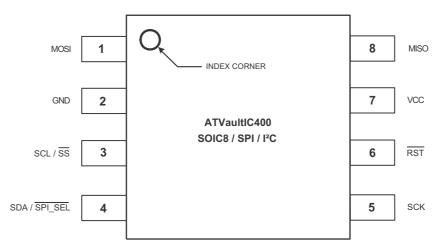

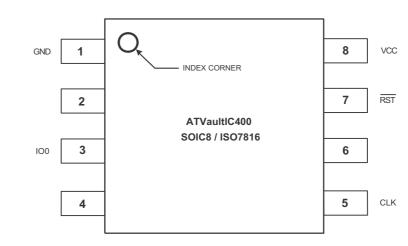

### 3.6 Pin & Package Configuration

### 3.6.1 Pin Configuration

Table 3-7. Pi

Pin List Configuration

|               | Pin #  |           |           |                                                           |  |

|---------------|--------|-----------|-----------|-----------------------------------------------------------|--|

| Designation   | QFN 20 | SOIC8/SPI | SOIC8/ISO | Description                                               |  |

| A0            | 1      | -         | -         | I <sup>2</sup> C address selection line A0                |  |

| A1            | 2      | -         | -         | I <sup>2</sup> C address selection line A1                |  |

| A2            | 3      | -         | -         | I <sup>2</sup> C address selection line A2                |  |

| RST           | 4      | 6         | 7         | CPU reset                                                 |  |

| VCC           | 5      | 7         | 8         | Power supply                                              |  |

| MISO          | 6      | 8         | -         | SPI Master Input Slave Output                             |  |

| MOSI          | 10     | 1         | -         | SPI Master Output Slave Input                             |  |

| GND           | 11     | 2         | 1         | Ground (reference voltage)                                |  |

| SCL/SS        | 12     | 3         | -         | I²C SCL / SPI Slave Select                                |  |

| SDA / SPI_SEL | 13     | 4         | -         | I <sup>2</sup> C SDA / SPI/I <sup>2</sup> C selection PIN |  |

| 100           | 13     | -         | 3         | ISO7816 I/O 0                                             |  |

| A3            | 14     | -         | -         | I <sup>2</sup> C address selection line A3                |  |

| A4            | 15     | -         | -         | I <sup>2</sup> C address selection line A4                |  |

| SCK           | 16     | 5         | -         | SPI Master clock                                          |  |

| CLK / GND     | 20     | -         | 5         | ISO7816 CLK / Ground                                      |  |

Others pins are not connected (do not connect to GND).

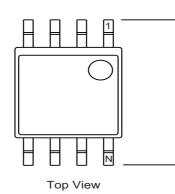

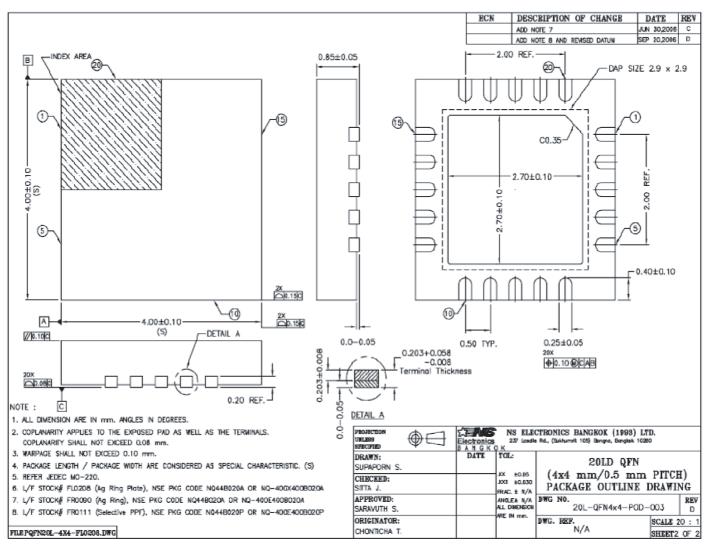

### 3.6.2 Pinouts for packages QFN20 and SOIC8

### Figure 3-6. Pinout ATVaultIC400 - Package QFN20

Note: The exposed pad is connected to GND pin internally. So it is recommended to connect it to GND.

Figure 3-8. Pinout ATVaultIC400 - Package SOIC8 - ISO configuration

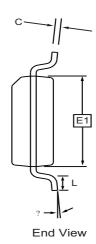

#### 3.6.3 **Packages characteristics**

#### Figure 3-9. SOIC-8 package characteristics

е Δ1

Side View

COMMON DIMENSIONS (Unit of Measure = mm)

| SYMBOL | MIN  | NOM      | MAX  | NOTE |

|--------|------|----------|------|------|

| А      | 1.70 |          | 2.16 |      |

| A1     | 0.05 |          | 0.25 |      |

| b      | 0.35 |          | 0.48 | 5    |

| С      | 0.15 |          | 0.35 | 5    |

| D      | 5.13 |          | 5.35 |      |

| E1     | 5.18 |          | 5.40 | 2, 3 |

| E      | 7.70 |          | 8.26 |      |

| L      | 0.51 |          | 0.85 |      |

| ?      | 0°   |          | 8°   |      |

| е      |      | 1.27 BSC |      | 4    |

Notes: 1. This drawing is for general information only; refer to EIAJ Drawing EDR-7320 for additional information.

Е

This drawing is for general information only; refer to EIAJ Drawing EDK-7320 for additional information.

Mismatch of the upper and lower dies and resin burns are not included.

It is recommended that upper and lower cavities be equal. If they are different, the larger dimension shall be regarded.

Determines the true geometric position.

Values b and C apply to pb/Sn solder plated terminal. The standard thickness of the solder layer shall be 0.010 +0.010/-0.005 mm.

# ATVaultIC400

TPR0433BX-SMS-09/09

# **Definitions and abbreviations**

| 3DES / TDES       | Triple DES algorithm                                                                                                                                                                                                                                                                                                                      |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AES               | Advanced Encryption Standard algorithm as defined in FIPS PUB 197                                                                                                                                                                                                                                                                         |

| APDU              | Application Protocol Data Unit as defined in ISO7816-3                                                                                                                                                                                                                                                                                    |

| Authentication    | An identification or entity authentication technique assures one party (the verifier), through acquisi-<br>tion of corroborative evidence, of both the identity of a second party involved, and that the second<br>(the claimant) was active at the time the evidence was created or acquired. (From Handbook of<br>Applied Cryptography) |

| ASSP              | Application Specific Standard Product                                                                                                                                                                                                                                                                                                     |

| CBC               | Cipher Block Chaining method applied to block ciphers                                                                                                                                                                                                                                                                                     |

| CFB               | Cipher Feedback Register chaining method applied to block ciphers                                                                                                                                                                                                                                                                         |

| CMAC              | Cipher-based Message Authentication Code                                                                                                                                                                                                                                                                                                  |

| CPU               | Central Processing Unit                                                                                                                                                                                                                                                                                                                   |

| Cryptographic key | A bit string used as a secret parameter by a cryptographic algorithm. To prevent a key from being guessed, keys need to be generated truly randomly and contain sufficient entropy.                                                                                                                                                       |

| DES               | Data Encryption Standard algorithm as defined in FIPS PUB 46-3                                                                                                                                                                                                                                                                            |

| Device            | Any CPU with master or slave capability                                                                                                                                                                                                                                                                                                   |

| DSA               | Digital Signature Algorithm as defined in FIPS PUB 186-2                                                                                                                                                                                                                                                                                  |

| ECB               | Electronic Code Book chaining method applied to block ciphers                                                                                                                                                                                                                                                                             |

| ECDSA             | Elliptic Curves DSA as defined in FIPS PUB 186-2                                                                                                                                                                                                                                                                                          |

| EEPROM            | Electrically Erasable Programmable Read-Only Memory                                                                                                                                                                                                                                                                                       |

| FAT               | File Allocation Table - file system from Microsoft®                                                                                                                                                                                                                                                                                       |

| FIPS              | Federal Information Processing Standards                                                                                                                                                                                                                                                                                                  |

| FIPS-approved     | An algorithm or technique that is specified or adopted in FIPS                                                                                                                                                                                                                                                                            |

| HMAC              | Hash-based Message Authentication Code as defined in FIPS PUB 198                                                                                                                                                                                                                                                                         |

| Host              | Entity that communicates (directly or not) with the device                                                                                                                                                                                                                                                                                |

| HOTP              | HMAC-based One Time Password algorithm as defined in RFC 4226                                                                                                                                                                                                                                                                             |

| ISO7816           | Smart Card interface                                                                                                                                                                                                                                                                                                                      |

| MAC               | Message Authentication Code - A bit string of fixed length, computed by a MAC generation algo-<br>rithm, that is used to establish the authenticity and, hence, the integrity of a message.                                                                                                                                               |

| Master            | The device that initiates and terminates a transmission. The Master also generates the clock for syn-<br>chronous interface.                                                                                                                                                                                                              |

| NIST              | National Institute of Standards and Technology                                                                                                                                                                                                                                                                                            |

| NVM               | Non Volatile Memory (EEPROM, flash, …)                                                                                                                                                                                                                                                                                                    |

| OFB               | Output Feedback Register chaining method applied to block ciphers                                                                                                                                                                                                                                                                         |

| RSA                    | Rivest Shamir Adleman algorithm                                                                                                                      |

|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCP                    | Secure Channel Protocol as defined by GlobalPlatform                                                                                                 |

| SHA                    | Secure Hash Algorithm                                                                                                                                |

| Slave                  | The device addressed by a master                                                                                                                     |

| SPI                    | Serial Protocol Interface                                                                                                                            |

| Strong Authenticatior  | n Exchange of messages during which a claimant proves its identity to a verifier by demonstrating its knowledge of a secret but without revealing it |

| TWI / I <sup>2</sup> C | Two Wire Interface and Inter Integrated Circuit Bus respectively                                                                                     |

### **Referenced Documents**

- [1] ATMEL Corporation. AT98SO Generic Datasheet. TPR0395AX-July2009 (Availbale under Non-Disclosure Agreement signed with ATMEL).

- [2] NIST SP 800-63 Electronic Authentication Guideline April 2006

- [3] ISO9798 2 Entity Authentication Part 2 : Mechanisms using symmetric encipherment algorithms. July 1999

- [4] FIPS PUB 196. Entity Authenticationusing public key cryptography. Feb 1997.

- [5] RSA Laboratories. PKCS #11 v2.20: Cyrptograhic Token Interface Standard. June 2004.

- [6] Microsoft Smart Card Minidriver Specification for Windows Base Cryptographic Service Provider (Base CSP) and Smart Card Key Storage Provider (KSP) version 5.07 -September 2007

- [7] Atmel Corporation. How to secure Smart Meters using ATVaultIC Products. xxxx-2009

# **Datasheet Revision History**

Rev AX - 15 July 2009 : Initial Version

Rev BX - 29 September 2009 : Update Product Name

| 1 | Overvi  | Overview                                                      |    |  |  |  |

|---|---------|---------------------------------------------------------------|----|--|--|--|

|   | 1.1     | Tampering resistance                                          | 3  |  |  |  |

|   | 1.2     | Authentication capability                                     | 3  |  |  |  |

|   | 1.3     | Secure storage                                                | 4  |  |  |  |

|   | 1.4     | Flexibility                                                   | 4  |  |  |  |

|   | 1.5     | Typical application                                           | 5  |  |  |  |

|   | 1.6     | Ordering Information                                          | 6  |  |  |  |

|   |         | 1.6.1 Legal                                                   | 6  |  |  |  |

|   |         | 1.6.2 Quotation and Volume                                    | 6  |  |  |  |

|   |         | 1.6.3 Part Number                                             | 6  |  |  |  |

|   |         | 1.6.4 Starter Kit                                             |    |  |  |  |

|   |         | 1.6.5 Demo Kit                                                | 6  |  |  |  |

|   | 1.7     | Software and Hardware Architecture                            | 7  |  |  |  |

| 2 | Detaile | ed Features                                                   | 8  |  |  |  |

|   | 2.1     | Communication Interfaces                                      | 8  |  |  |  |

|   | 2.2     | Security Mechanisms                                           | 8  |  |  |  |

| 3 | Produc  | ct Characteristics                                            | 10 |  |  |  |

|   | 3.1     | Command Timings (T=25°C)                                      | 10 |  |  |  |

|   | 3.2     | Maximum Ratings                                               | 12 |  |  |  |

|   | 3.3     | AC/DC Characteristics (1.62V - 5.5V range; T= -25°C to +85°C) | 12 |  |  |  |

|   | 3.4     | Timings                                                       | 14 |  |  |  |

|   |         | 3.4.1 I <sup>2</sup> C Timings                                | 14 |  |  |  |

|   |         | 3.4.2 SPI Timings                                             | 15 |  |  |  |

|   | 3.5     | Connexions for Typical Application                            | 16 |  |  |  |

|   | 3.6     | Pin & Package Configuration                                   | 17 |  |  |  |

|   |         | 3.6.1 Pin Configuration                                       | 17 |  |  |  |

|   |         | 3.6.2 Pinouts for packages QFN20 and SOIC8                    | 18 |  |  |  |

|   |         | 3.6.3 Packages characteristics                                | 20 |  |  |  |

|   |         |                                                               |    |  |  |  |

#### **Headquarters**

Atmel Corporation 2325 Orchard Parkway San Jose, CA 95131 USA Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

### International

Atmel Asia Unit 01-05 & 16, 19/F BEA Tower, Millennium City 5 418 Kwun Tong Road Kwun Tong, Kowloon Hong Kong Tel: (852) 2245-6100 Fax: (852) 2722-1369 Atmel Europe Le Krebs 8, Rue Jean-Pierre Timbaud BP 309 78054 Saint-Quentin-en-Yvelines Cedex France Tel: (33) 1-30-60-70-00 Fax: (33) 1-30-60-71-11

#### Atmel Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

#### **Product Contact**

Web Site www.atmel.com Technical Support at98sc@atmel.com Sales Contact www.atmel.com/contacts

Literature Requests www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Atmel's products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

© 2009 Atmel Corporation. All rights reserved. Atmel<sup>®</sup>, logo and combinations thereof, Everywhere You Are<sup>®</sup> and others, are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.