# **OKI** Semiconductor

# **MSM5839C**

#### **40-DOT SEGMENT DRIVER**

#### **GENERAL DESCRIPTION**

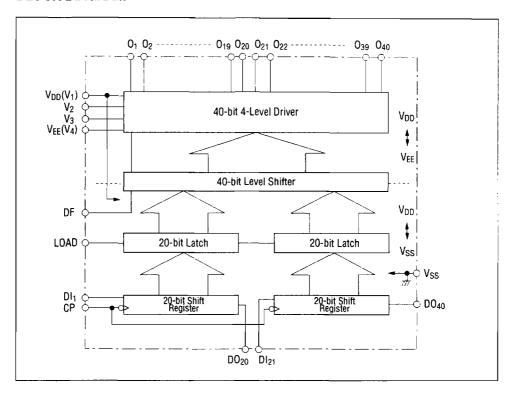

The MSM5839C is a dot matrix LCD segment driver LSI which is fabricated with low power CMOS metal gate technology. This LSI consists of 40-bit shift register (two 20-bit shift registers), 40-bit latch (two 20-bit latches), 40-bit level shifter and 40-bit 4-level driver.

It converts serial data, which is received from LCD controller LSI, into parallel data and outputs LCD driving waveform to the LCD panel.

This LSI can drive a variety of LCD panels because the bias voltage, which determines an LCD driving voltage, can be optionally supplied from the external source.

#### **FEATURES**

Supply voltage : 4.5 to 5.5V

LCD driving voltage : 4 to 11V

Applicable LCD duty : 1/3 to 1/64

Bias voltage can be supplied externally.

• Recommended controller LSI: MSM6262-xx

Package options

56-pin plastic QFP (QFP56-P-910-2K) (Product name: MSM5839CGS-2K)

56-pin plastic QFP (QFP56-P-910-K) (Product name: MSM5839CGS-K)

56-pin plastic QFP (QFP56-P-910-L2) (Product name: MSM5839CGS-L2)

239

## **BLOCK DIAGRAM**

## PIN CONFIGURATION (TOP VIEW)

NC: No-connection pin

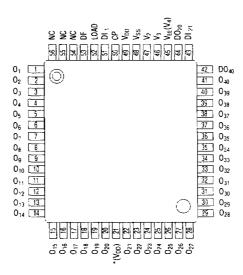

#### 56-Pin Plastic QFP

• This pin is internally connected with  $V_{DD}$ , so it must not be connected to other signals. It is also prohibited to use the 21 pin as a  $V_{DD}$  independently. This pin may be used as a line reinforcing  $V_{DD}$ .

## **ABSOLUTE MAXIMUM RATINGS**

| Parameter Symbol Supply Voltage (1) V <sub>DD</sub> |                                      | Condition             | Condition Rating             |    |  |

|-----------------------------------------------------|--------------------------------------|-----------------------|------------------------------|----|--|

|                                                     |                                      | T <sub>a</sub> = 25°C | -0.3 to +6                   | ٧  |  |

| Supply Voltage (2)                                  | V <sub>DD</sub> - V <sub>EE</sub> *1 | $T_a = 25$ °C         | 0 to 12                      | ٧  |  |

| Input Voltage                                       | V <sub>1</sub>                       | T <sub>a</sub> = 25°C | -0.3 to V <sub>DD</sub> +0.3 | ٧  |  |

| Storage Temperature                                 | T <sub>STG</sub>                     | _                     | -55 to +150                  | °C |  |

<sup>\*1:</sup>  $V_{DD} > V_2 > V_3 > V_{EE}$

#### RECOMMENDED OPERATING CONDITIONS

| Parameter             | Symbol                               | Condition | Range      | Unit |  |

|-----------------------|--------------------------------------|-----------|------------|------|--|

| Supply Voltage (1)    | V <sub>DD</sub>                      | -         | 4.5 to 5.5 | ٧    |  |

| Supply Voltage (2)    | V <sub>DD</sub> - V <sub>EE</sub> *1 | _         | 4 to 11    | ٧    |  |

| Operating Temperature | Top                                  | _         | -20 to +85 | °C   |  |

<sup>\*1:</sup>  $V_{DD} > V_2 > V_3 > V_{EE}$

## **ELECTRICAL CHARACTERISTICS DC** Characteristics

$(V_{DD} = 5V \pm 10\%, Ta = -20 \text{ to } +85^{\circ}\text{C})$

|                     |                    |                                                 |                       | (400 - 04 - | 1070, 14 - 20      | 10 +00 07 |

|---------------------|--------------------|-------------------------------------------------|-----------------------|-------------|--------------------|-----------|

| Parameter           | Symbol             | Condition                                       | Min.                  | Тур.        | Max.               | Unit      |

| "H" Input Voltage   | V <sub>IH</sub> *1 | -                                               | 0.8V <sub>DD</sub>    | -           | V <sub>DD</sub>    | ٧         |

| "L" Input Voltage   | V <sub>IL</sub> *1 | -                                               | V <sub>SS</sub>       | _           | 0.2V <sub>DD</sub> | ٧         |

| "H" Input Current   | I <sub>H</sub> *1  | $V_{iH} = V_{DD}$                               | -                     | _           | 1                  | μА        |

| "L" Input Current   | I <sub>IL</sub> *1 | V <sub>IL</sub> = 0V                            | _                     | -           | 1                  | μА        |

| "H" output Voltage  | V <sub>OH</sub> *2 | l <sub>0</sub> = -0.4 mA                        | V <sub>DD</sub> - 0.4 |             | _                  | ٧         |

| "L" output Voltage  | V <sub>OL</sub> *2 | I <sub>0</sub> = 0.4 mA                         | -                     | _           | 0.4                | ٧         |

| ON Resistance       | R <sub>ON</sub> *4 | $V_{DD} - V_{EE} = 8V$ $ V_N - V_0  = 0.25V$ *3 | -                     | 5           | 10                 | kΩ        |

| Current Consumption | I <sub>DD</sub>    | CP = DC<br>$V_{DD} - V_{EE} = 11V$ , No load    | _                     | -           | 100                | μА        |

<sup>\*1:</sup> Applicable to LOAD, CP, DI<sub>1</sub>, DI<sub>21</sub>, DF

<sup>\*2:</sup> Applicable to  $DO_{20}$ ,  $DO_{40}$ \*3:  $V_N = V_{DD} - V_{EE}$ ,  $V_2 = \frac{7}{9}$  ( $V_{DD} - V_{EE}$ ),  $V_3 = \frac{2}{9}$  ( $V_{DD} - V_{EE}$ ) \*4: Applicable to  $O_1 - O_{40}$

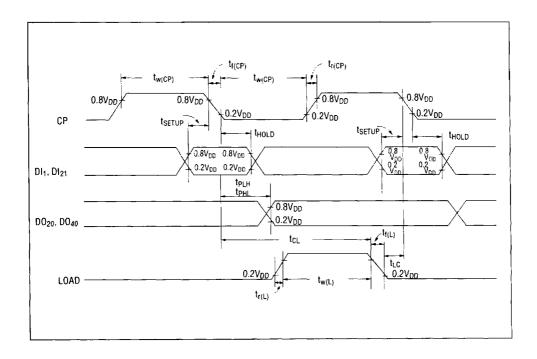

## **Switching Characteristics**

$(V_{DD} = 5V \pm 10\%, Ta = -20^{\circ} \text{ to } +85^{\circ}\text{C}, C_L = 15pF)$

| Parameter                       | Symbol Condition   |            | Min. Typ. |   | Max. | Unit |  |

|---------------------------------|--------------------|------------|-----------|---|------|------|--|

| "H", "L" Propagation Delay Time | tpLH               | _          |           |   | 250  | ns   |  |

|                                 | t <sub>PHL</sub>   | _          | -         |   |      |      |  |

| Clock Frequency                 | f <sub>CP</sub>    | DUTY = 50% | -         | _ | 2    | MHz  |  |

| Clock Pulse Width               | tw(CP)             | _          | 150       | _ | -    | ns   |  |

| LOAD Pulse Width                | t <sub>W(L)</sub>  | -          | 150       | _ | -    | ns   |  |

| Data Setup Time DI → CP         | tsetup             | _          | 100       | _ | _    | ns   |  |

| CP → LOAD Time                  | t <sub>CL</sub>    | _          | 250       |   | _    | ns   |  |

| LOAD → CP Time                  | t <sub>LC</sub>    | -          | 0         | _ | _    | ns   |  |

| DATA Hold Time DI → CP          | tHOLD              | _          | 50        | - | _    | ns   |  |

| CP Rise/Fall Time               | t <sub>r(CP)</sub> |            |           |   | 50   | ns   |  |

|                                 | t <sub>f(CP)</sub> | -          | _         | _ |      |      |  |

| LOAD Rise/Fall Time             | t <sub>r(L)</sub>  |            |           | _ | 1    | μ\$  |  |

|                                 | t <sub>f(L)</sub>  | -          | _         |   |      |      |  |

#### **FUNCTIONAL DESCRIPTION**

#### **Pin Functional Description**

#### DI<sub>1</sub>

The data input pin for the 20-bit shift register (from 1st to 20th bit).

#### • CP

Clock pulse input pin for the two 20-bit shift registers. The data is shifted in the two 20-bit shift registers at the falling edge of the clock pulse. Data setup time ( $t_{SETUP}$ ) and data hold time ( $t_{HOLD}$ ) are required each between DI<sub>1</sub>, DI<sub>21</sub> and CP.

## • DO<sub>20</sub>

The 20th bit output of the shift register.

The data which is input from  $DI_1$  is clocked out with the delay in the number of bits of the shift register (20). The 40-bit shift register is configured by connecting the output of this pin to  $DI_{21}$  pin.

#### • DI<sub>21</sub>

The data input pin for the 20-bit shift register (from 21st to 40th bit).

The connection of  $DO_{20}$  pin and this pin allows the device to be used as the 40-bit shift register.

#### • DO<sub>40</sub>

The 40th bit output of the shift register.

The data which is input from  $DI_1$  is clocked out with the delay in the number of the bits of the shift register.

When extending the number of characters, this pin is used to connect in cascade to the next MSM5839C.

#### • DF

Alternate signal input pin for LCD driving waveform.

#### V<sub>DD</sub>(V<sub>1</sub>), V<sub>SS</sub>

Supply voltage pins. V<sub>DD</sub> should be 4.5 to 5.5V.

$V_{SS}$  is a ground pin ( $V_{SS} = 0V$ ).

#### V<sub>2</sub>, V<sub>3</sub>, V<sub>EE</sub>(V<sub>4</sub>)

Bias supply voltage pins to drive the LCD. Bias voltage is usually used as supply voltage source.

#### • LOAD

The signal for latching the shift register contents is input from this pin.

When LOAD pin is set at "H", the shift register contents are transferred to 40-bit 4-level driver. When LOAD pin is set at "L", the last display output data  $(O_1$  to  $O_{40}$ ), which was transferred when LOAD pin was at "H", is held.

## • O<sub>1</sub> to O<sub>40</sub>

Display data output pins which correspond to each data bit in the latch. One of the  $V_{DD}$ ,  $V_2$ ,  $V_3$  or  $V_{EE}$  ( $V_4$ ) is selected as a display driving voltage source according to the combination of latched data level and DF signal. Refer to the truth table. These pins should be connected to the SEGMENT side of the LCD panel.

## **Truth Table**

| Latched data | DF | Display data output level |

|--------------|----|---------------------------|

| н            | Н  | V <sub>EE</sub> (V4)      |

|              | L  | V <sub>DD</sub>           |

|              | Н  | V <sub>3</sub>            |

| L            | L  | V <sub>2</sub>            |