## 512K (64K x 8) SYNCHRONOUS STATIC RAM PLASTIC SIP MODULE

**IDT 7MP6025**

## **FEATURES:**

- 64K x 8 fully synchronous memory

- High-speed 20MHz read cycle time

- · 16-bit synchronous address input

- · 8-bit synchronous data input

- · Synchronous chip select and write enable

- · Separate clock enable for each register

- Low standby power

- Onboard decoupling capacitors

- · Available in 43-pin SIP (single in-line package) configuration

- · 2 Ground and 2 Voc pins

### **DESCRIPTION:**

The IDT7MP6025 is a 64K x 8 synchronous RAM with edge triggered registers on the address lines, data-in bus, data-out bus, chip select and write enable. The edge triggered register of the 16 address lines features an independent clock enable that allows the address register to be selectively loaded. The address register will be loaded on the low-to-high transition of the clock when the clock enable line is low and will hold its current contents on the low-to-high transition of the clock when the clock enable is high. Similarly, the 8-bit data-in register will be loaded with new data on the low-to-high transition of the clock when the data-in clock enable is high. The data-out register will receive new data from the 64K x 8 RAM when the clock enable line is low and will hold its data when the clock enable line is low and will hold its data when the clock enable line is high at the low-to-high transition of the clock. All

clock enables, as well as address and data inputs, must meet the appropriate set-up and hold times with respect to the clock.

The eight data output bits are enabled when the output enable is low and are in the high-impedance state when the output enable is high. The chip select and write enable signals are also registered in D flip-flops. These two flip-flops are loaded with new data on each low-to-high transition of the clock. The chip select is passed directly from the Q output of the D-type flip-flop to the 64K x 8 RAM. The write enable signal is gated with the clock signal to generate a delayed write enable pulse. In essence, this gives the output of the address register time to settle and internally select the appropriate byte of RAM before the write enable goes low to write new data into the RAM. Thus, the low-to-high transition of the clock causes the chip select and write enable flip-flops to be loaded with new data and immediately deselects a previous write by means of the clock going high. The data lines to the RAM and the address lines to the RAM may indeed change to new values based on the low-to-high transition of the clock. When the clock goes from high-to-low, if the chip select is low and the write enable is low, a write cycle is begun and the data at the RAM data inputs will be written into the selected address. If the write enable is high or the chip enable is high, data will not be written into the memory.

One of the features of this configuration of memory that has registers on all of the address lines, data input lines and data output lines as well as the control lines, is to provide the highest possible clock rate in the system. All that is necessary is that the data, address, chip select, write enable and clock enables signals meet the required set-up and hold time with respect to the clock. In this manner, fully asynchronous operation is achieved. The IDT7MP6025 is offered as a compact, cost-effective 43-pin plastic SIP module.

## **FUNCTIONAL BLOCK DIAGRAM**

CEMOS is a trademark of Integrated Device Technology, Inc.

COMMERCIAL TEMPERATURE RANGE

JANUARY 1989

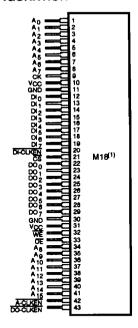

## PIN CONFIGURATION

SIP SIDE VIEW

## NOTE:

For module dimension, please refer to module drawing M18 in the packaging section.

## PIN NAMES

| I III IIAIIIEO    |                          |

|-------------------|--------------------------|

| A <sub>0-15</sub> | Addresses                |

| СК                | Clock                    |

| DI <sub>0-7</sub> | Data Input               |

| DO <sub>0-7</sub> | Data Output              |

| DI-CLKEN          | Data Input Clock Enable  |

| A-CLKEN           | Address Clock Enable     |

| DO-CLKEN          | Data Output Clock Enable |

| Vcc               | Power                    |

| GND               | Ground                   |

| CS                | Chip Select              |

| WE                | Write Enable             |

| OE                | Output Enable            |

|                   | ·                        |

## **ABSOLUTE MAXIMUM RATINGS**

| SYMBOL            | RATING                               | COMMERCIAL   | UNIT |

|-------------------|--------------------------------------|--------------|------|

| V <sub>TERM</sub> | Terminal Voltage with Respect to GND | -0.5 to +7.0 | ٧    |

| TA                | Operating Temperature                | 0 to +70     | °C   |

| TBIAS             | Temperature Under Bias               | -55 to + 125 | °C   |

| T <sub>STG</sub>  | Storage Temperature                  | -55 to + 125 | °C   |

| four              | DC Output Current                    | 50           | mA   |

### NOTE:

Stresses greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

## RECOMMENDED DC OPERATING CONDITIONS

| SYMBOL          | PARAMETER          | MIN.    | TYP. | MAX. | UNIT |

|-----------------|--------------------|---------|------|------|------|

| V <sub>cc</sub> | Supply Voltage     | 4.5     | 5.0  | 5.5  | ٧    |

| GND             | Supply Voltage     | 0       | 0    | 0    | V    |

| V <sub>IH</sub> | Input High Voltage | 2.2     | _    | 6.0  | V    |

| V <sub>IL</sub> | input Low Voltage  | -0.5(1) |      | 0.8  | ٧    |

## NOTE:

## RECOMMENDED OPERATING TEMPERATURE AND SUPPLY VOLTAGE

| GRADE      | GRADE AMBIENT TEMPERATURE |    | Vcc        |

|------------|---------------------------|----|------------|

| Commercial | 0°C to +70°C              | ov | 5.0V ± 10% |

## DC ELECTRICAL CHARACTERISTICS

$V_{CC} = 5V \pm 10\%$

| SYMBOL           | PARAMETER                         | TEST CONDITIONS                                                              | MIN. | MAX. | UNIT |

|------------------|-----------------------------------|------------------------------------------------------------------------------|------|------|------|

| liul             | Input Leakage (Address & Control) | V <sub>CC</sub> = Max., V <sub>IN</sub> = GND to V <sub>CC</sub>             | _    | 5    | μА   |

| اياا             | Input Leakage (Data)              | V <sub>CC</sub> = Max., V <sub>IN</sub> = GND to V <sub>CC</sub>             | -    | 5    | μΑ   |

| ll <sub>LO</sub> | Output Leakage                    | $V_{CC} = Max., \overline{CS} = V_{OUT},$ $V_{OUT} = GND \text{ to } V_{CC}$ | _    | 10   | μА   |

| V <sub>OL</sub>  | Output Low Voltage                | V <sub>CC</sub> = Min., I <sub>OL</sub> = 8mA                                | _    | 0.4  | V    |

| V <sub>OH</sub>  | Output High Voltage               | V <sub>CC</sub> = Min., I <sub>OH</sub> = -4mA                               | 2.4  |      | V    |

## DC ELECTRICAL CHARACTERISTICS

$V_{CC} = 5.0V \pm 10\%$

| $V_{CC} = 5.0V$  | ±10%                            |                                                                                             |      |      |

|------------------|---------------------------------|---------------------------------------------------------------------------------------------|------|------|

| SYMBOL           | PARAMETER                       | TEST<br>CONDITIONS                                                                          | MAX. | UNIT |

| l <sub>CC1</sub> | Operating Current               | f = 0, CS = V <sub>IL</sub><br>V <sub>CC</sub> = Max.;<br>Output Open                       | 725  | mA   |

| l <sub>CC2</sub> | Dynamic Operating<br>Current    | V <sub>CC</sub> = Max.;<br>CS = V <sub>IL.</sub> ; f<br>= f <sub>MAX</sub> ,<br>Output Open | 950  | mA   |

| ¹saı             | Standby Power<br>Supply Current | $\frac{\overline{CS}}{V_{IN}} > V_{CC} - 0.2V$<br>$V_{IN} > V_{CC} - 0.2V$<br>or < 0.2V     | 125  | mA   |

## CAPACITANCE (T<sub>A</sub> = +25°C, f = 1.0MHz)

| OAI AO | TIATION (A - 120   | O, 1 = 1.0M112)       |      |      |

|--------|--------------------|-----------------------|------|------|

| SYMBOL | PARAMETER(1)       | CONDITIONS            | TYP. | UNIT |

| CiN    | Input Capacitance  | V <sub>IN</sub> = 0V  | 20   | pF   |

| Соит   | Output Capacitance | V <sub>OUT</sub> = 0V | 22   | ρF   |

## NOTE:

1. This parameter is sampled and not 100% tested.

<sup>1.</sup>  $V_{\rm it}$  (min.) = ~3.0V for pulse width less than 20ns.

# AC ELECTRICAL CHARACTERISTICS $V_{CC} = 5V \pm 10\%$

|                      |                                    | 7MP60 | 25835 | 7MP6025S45 |      | 7MP6025S55 |      |      |

|----------------------|------------------------------------|-------|-------|------------|------|------------|------|------|

| SYMBOL               | PARAMETER                          | MIN.  | MAX.  | MIN.       | MAX. | MIN.       | MAX. | UNIT |

| READ C               | YCLE                               |       |       |            |      |            |      |      |

| t <sub>CP</sub>      | Read Cycle Time                    | 35    |       | 45         | _    | 55         | -    | ns   |

| t <sub>CH</sub>      | Clock High Time                    | 10    | _     | 10         | -    | 10         | -    | ns   |

| t <sub>CL</sub>      | Clock Low Time                     | 10    | _     | 10         |      | 10         |      | ns   |

| ts                   | Address, WE, CS, CE Set Up Time    | 4     |       | 5          | _    | 5          | -    | ns   |

| t <sub>H</sub>       | Address, WE, CS, CE Hold Time      | 4     | -     | 6          | -    | 6          | -    | ns   |

| t <sub>OLZ</sub> (1) | Output Low Z Time                  |       | 10    | _          | 15   | -          | 15   | ns   |

| t <sub>OHZ</sub> (1) | Output High Z Time                 | _     | 8     |            | 11   | -          | 11   | กร   |

| t <sub>PVD</sub>     | Prop Delay to Valid Data Out       | _     | 10    | _          | 15   | _          | 15   | ns   |

| WRITE                | CYCLE                              |       |       |            |      |            |      |      |

| t <sub>CP</sub>      | Write Cycle Time                   | 35    | _     | 45         | _    | 55         | ~    | ns   |

| t <sub>CH</sub>      | Clock High Time                    | 10    | _     | 10         | _    | 10         | ~    | ns   |

| t <sub>CL</sub>      | Clock Low Time                     | 23    | -     | 30         | -    | 37         | ~-   | ns   |

| ts                   | Data, Addr, WE, CS, CE Set Up Time | 4     | _     | 5          | _    | 5          | -    | ns   |

| t <sub>H</sub>       | Data, Addr, WE, CS, CE Hold Time   | 4     | _     | 6          | _    | 6          | ~    | ns   |

### NOTE:

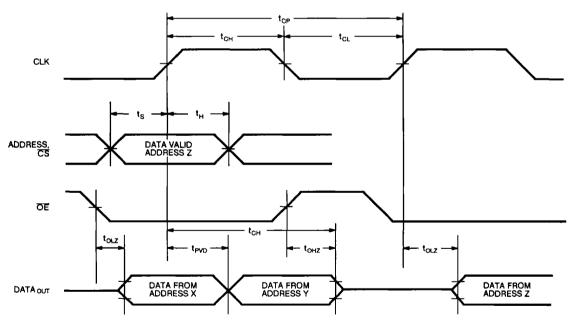

## TIMING WAVEFORM OF READ CYCLE (1)

## NOTE:

1. The device must be selected by a  $\overline{\text{CS}}$  level for the conditions above to take place.

<sup>1.</sup> This parameter is guaranteed but not tested.

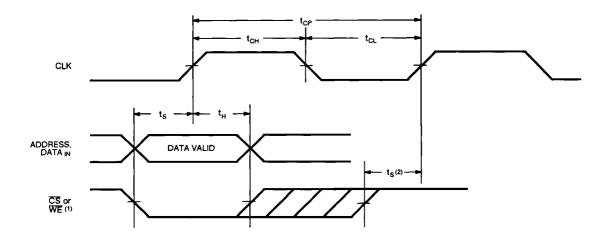

## TIMING WAVEFORM OF WRITE CYCLE

## NOTES:

- 1. Either  $\overline{\text{CS}}$  or  $\overline{\text{WE}}$  can be used to trigger a write cycle, provided that the other signal is low at the same time.

- 2. When a write is terminated, either CS or WE must become high at least one ts before the next rising edge of CLK.

## **TRUTH TABLE**

| MODE    | CS | ŌĒ | CK             | DO-CLKEN | DI-CLKEN | A-CLKEN | WE | OUTPUT | POWER   |

|---------|----|----|----------------|----------|----------|---------|----|--------|---------|

| Standby | Н  | н  | †              | н        | н        | н       | х  | High Z | Standby |

| Read    | L  | L  | 1              | L        | х        | L       | н  | Low Z  | Active  |

| Read    | L  | Н  | †              | L        | х        | L       | н  | High Z | Active  |

| Write   | L  | Н  | T <sub>t</sub> | Н        | L        |         |    | High Z | Active  |

## AC TEST CONDITIONS

| AO ILOI OONDIIIONO            |                     |

|-------------------------------|---------------------|

| Input Pulse Levels            | GND to 3.0V         |

| Input Rise/Fall Times         | 5ns                 |

| Input Timing Reference Levels | 1.5V                |

| Output Reference Levels       | 1.5V                |

| Output Load                   | See Figures 1 and 2 |

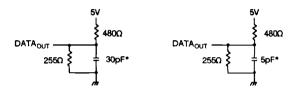

Figure 1. Output Load

Figure 2. Output Load (for t<sub>OLZ</sub>, t<sub>CHZ</sub>, t<sub>OHZ</sub>, t<sub>WHZ</sub> and t<sub>OW</sub>)

\* Including scope and jig.

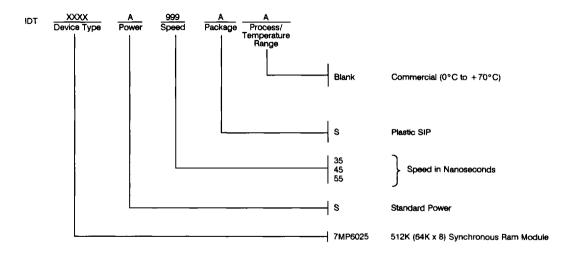

## ORDERING INFORMATION