### AN189

#### BALANCED MODULATOR/DEMODULATOR APPLICATIONS USING MC1496/MC1596

The MC1496 is a monolithic transistor array arranged as a balanced modulator-demodulator. The device takes advantage of the excellent matching qualities of monolithic devices to provide superior carrier and signal rejection. Carrier suppressions of 50dB at 10MHz are typical with no external balancing networks required.

Applications include AM and suppressed carrier modulators, AM and FM demodulators, and phase detectors.

#### THEORY OF OPERATION

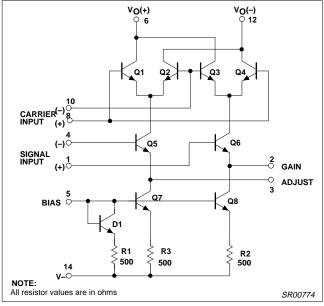

As Figure 1 suggests, the topography includes three differential amplifiers. Internal connections are made such that the output becomes a product of the two input signals  $V_c$  and  $V_s$ .

To accomplish this the differential pairs Q1-Q2 and Q3-Q4, with their cross-coupled collectors, are driven into saturation by the zero crossings of the carrier signal V<sub>C</sub>. With a low level signal, V<sub>S</sub> driving the third differential amplifier Q5-Q6, the output voltage will be full wave multiplication of V<sub>C</sub> and V<sub>S</sub>. Thus for sine wave signals, V<sub>OUT</sub> becomes:

$$V_{OUT} = E_{X}E_{Y} \left[ \cos(\omega x + \omega y)t + \cos(\omega x - \omega y)t \right]$$

(1)

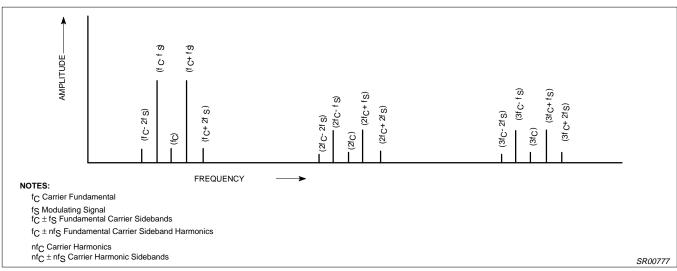

As seen by equation (1) the output voltage will contain the sum and difference frequencies of the two original signals. In addition, with the carrier input ports being driven into saturation, the output will contain the odd harmonics of the carrier signals. (See Figure 4.)

Figure 1. Balanced Modulator Schematic

Internally provided with the device are two current sources driven by a temperature-compensated bias network. Since the transistor geometries are the same and since  $V_{BE}$  matching in monolithic devices is excellent, the currents through  $Q_7$  and  $Q_8$  will be identical to the current set at Pin 5. Figures 2 and 3 illustrate typical biasing arrangements from split and single-ended supplies, respectively.

Of primary interest in beginning the bias circuitry design is relating available power supplies and desired output voltages to device requirements with a minimum of external components. The transistors are connected in a cascode fashion. Therefore, sufficient collector voltage must be supplied to avoid saturation if linear operation is to be achieved. Voltages greater than 2V are sufficient in most applications.

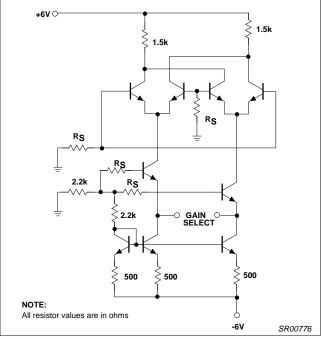

Biasing is achieved with simple resistor divider networks as shown in Figure 3. This configuration assumes the presence of symmetrical supplies. Explaining the DC biasing technique is probably best accomplished by an example. Thus, the initial assumptions and criteria are set forth:

- 1. Output swing greater than  $4V_{P-P}$ .

- 2. Positive and negative supplies of 6V are available.

- Collector current is 2mA. It should be noted here that the collector output current is equal to the current set in the current sources.

As a matter of convenience, the carrier signal ports are referenced to ground. If desired, the modulation signal ports could be ground referenced with slight changes in the bias arrangement. With the carrier inputs at DC ground, the quiescent operating point of the outputs should be at one-half the total positive voltage or 3V for this case. Thus, a collector load resistor is selected which drops 3V at 2mA or 1.5k $\Omega$ . A quick check at this point reveals that with these loads and current levels the peak-to-peak output swing will be greater than 4V. It remains to set the current source level and proper biasing of the signal ports.

The voltage at Pin 5 is expressed by

$$V_{BIAS} = V_{BE} = 500 \cdot I_{S}$$

where  $I_S$  is the current set in the current sources.

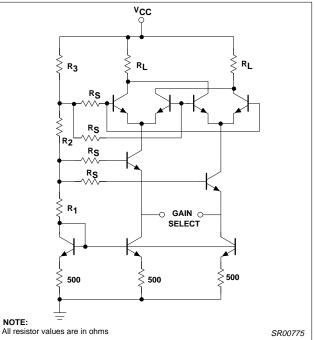

Figure 2. Single-Supply Biasing

#### BIASING

Since the MC1496 was intended for a multitude of different functions as well as a myriad of supply voltages, the biasing techniques are specified by the individual application. This allows the user complete

freedom to choose gain, current levels, and power supplies. The device can be operated with single-ended or dual supplies.

Figure 3. Dual Supply Biasing

$V_{BIAS} = V_{BE} = 500 \times I_S$

where I<sub>S</sub> is the current set in the current sources.

For the example V<sub>BE</sub> is 700mV at room temperature and the bias voltage at Pin 5 becomes 1.7V. Because of the cascode configuration, both the collectors of the current sources and the collectors of the signal transistors must have some voltage to operate properly. Hence, the remaining voltage of the negative supply (-6V+1.7V=-4.3V) is split between these transistors by biasing the signal transistor bases at -2.15V. Countless other bias arrangements can be used with other power supply voltages. The important thing to remember is that sufficient DC voltage is applied

to each bias point to avoid collector saturation over the expected signal wings.

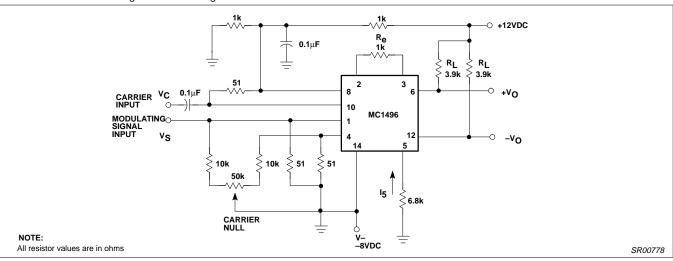

#### **BALANCED MODULATOR**

In the primary application of balanced modulation, generation of double sideband suppressed carrier modulation is accomplished. Due to the balance of both modulation and carrier inputs, the output, as mentioned, contains the sum and difference frequencies while attenuating the fundamentals. Upper and lower sideband signals are the strongest signals present with harmonic sidebands being of diminishing amplitudes as characterized by Figure 4.

Gain of the 1496 is set by including emitter degeneration resistance located as  $\mathsf{R}_\mathsf{E}$  in Figure 5. Degeneration also allows the maximum signal level of the modulation to be increased. In general, linear response defines the maximum input signal as

$$Vs \le 15 \bullet R_E$$

(Peak)

and the gain is given by

$$A_{VS} = \frac{R_L}{R_E + 2r_e}$$

(2)

This approximation is good for high levels of carrier signals. Table 1 summarizes the gain for different carrier signals.

As seen from Table 1, the output spectrum suffers an amplitude increase of undesired sideband signals when either the modulation or carrier signals are high. Indeed, the modulation level can be increased if  $R_E$  is increased without significant consequence. However, large carrier signals cause odd harmonic sidebands (Figure 4) to increase. At the same time, due to imperfections of the carrier waveforms and small imbalances of the device, the second harmonic rejection will be seriously degraded. Output filtering is often used with high carrier levels to remove all but the desired sideband. The filter removes unwanted signals while the high carrier level guards against amplitude variations and maximizes gain. Broadband modulators, without benefit of filters, are implemented using low carrier and modulation signals to maximize linearity and minimize spurious sidebands.

Figure 4. Modulator Frequency Spectrum

Application note

### AN189

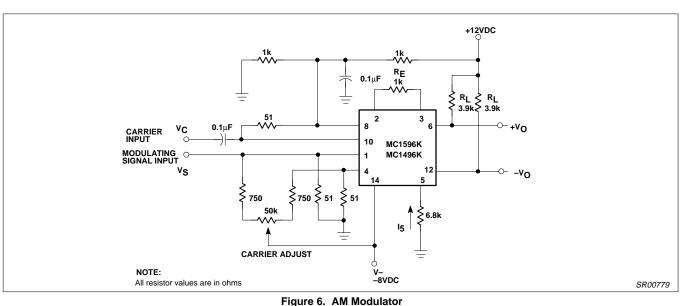

#### AM MODULATOR

The basic current of Figure 5 allows no carrier to be present in the output. By adding offset to the carrier differential pairs, controlled amounts of carrier appear at the output whose amplitude becomes a function of the modulation signal or AM modulation. As shown, the carrier null circuit is changed from Figure 5 to have a wider range so that wider control is achieved. All connections are shown in Figure 6.

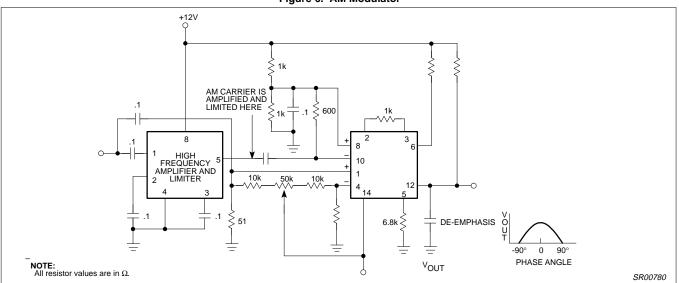

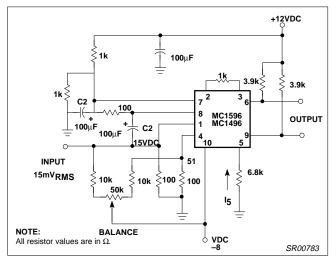

#### AM DEMODULATION

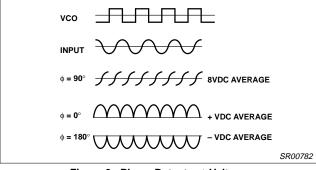

As pointed out in Equation 1, the output of the balanced mixer is a cosine function of the angle between signal and carrier inputs. Further, if the carrier input is driven hard enough to provide a switching action, the output becomes a function of the input amplitude. Thus the output amplitude is maximum when there is 0° phase difference as shown in Figure 7.

Amplifying and limiting of the AM carrier is accomplished by IF gain block providing 55dB of gain or higher with limiting of  $400\mu$ V. The limited carrier is then applied to the detector at the carrier ports to provide the desired switching function. The signal is then

demodulated by the synchronous AM demodulator (1496) where the carrier frequency is attenuated due to the balanced nature of the device. Care must be taken not to overdrive the signal input so that distortion does not appear in the recovered audio. Maximum conversion gain is reached when the carrier signals are in phase as indicated by the phase-gain relationship drawn in Figure 7.

Output filtering will also be necessary to remove high frequency sum components of the carrier from the audio signal.

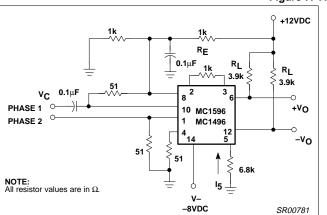

#### PHASE DETECTOR

The versatility of the balanced modulator or multiplier also allows the device to be used as a phase detector. As mentioned, the output of the detector contains a term related to the cosine of the phase angle. Two signals of equal frequency are applied to the inputs as per Figure 8. The frequencies are multiplied together producing the sum and difference frequencies. Equal frequencies cause the difference component to become DC while the undesired sum component is filtered out. The DC component is related to the phase angle by the graph of Figure 9.

Figure 5. Double Suppressed Carrier Modulator

| Table 1. | Voltage | Gain and | Output | vs Input | Signal |

|----------|---------|----------|--------|----------|--------|

|----------|---------|----------|--------|----------|--------|

| CARRIER INPUT SIGNAL (V <sub>C</sub> ) | APPROXIMATE VOLTAGE GAIN                                                     | OUTPUT SIGNAL FREQUENCY(S)                                                                                                                                                                         |  |

|----------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Low-level DC                           | $\frac{R_L V_C}{2(R_E + 2r_E) \frac{KT}{q}}$                                 | fM                                                                                                                                                                                                 |  |

| High-level DC                          | $\frac{R_{L}}{R + 2r_{e}}$                                                   | f <sub>M</sub>                                                                                                                                                                                     |  |

| Low-level AC                           | $\frac{R_{L} V_{C} (rms)}{2 \ \overline{2} \ \frac{KT}{q} (R_{E} + 2r_{e})}$ | f <sub>C</sub> + f <sub>M</sub>                                                                                                                                                                    |  |

| High-level AC                          | $\frac{0.637 R_L}{R_E + 2r_e}$                                               | $ \begin{aligned} \mathbf{f}_{\mathrm{C}} + \mathbf{f}_{\mathrm{M}}, & 3\mathbf{f}_{\mathrm{C}} + \mathbf{f}_{\mathrm{M}}. \\ & 5\mathbf{f}_{\mathrm{C}} + \mathbf{f}_{\mathrm{M}} \end{aligned} $ |  |

AN189

Figure 8. Phase Comparator

#### Figure 7. AM Demodulator

At  $90^{\circ}$  the cosine becomes zero, while being at maximum positive or maximum negative at  $0^{\circ}$  and  $180^{\circ}$ , respectively.

The advantage of using the balanced modulator over other types of phase comparators is the excellent linearity of conversion. This configuration also provides a conversion gain rather than a loss for greater resolution. Used in conjunction with a phase-locked loop, for instance, the balanced modulator provides a very low distortion FM demodulator.

#### FREQUENCY DOUBLER

Very similar to the phase detector of Figure 8, a frequency doubler schematic is shown in Figure 10. Departure from Figure 8 is primarily the removal of the low-pass filter. The output then contains the sum component which is twice the frequency of the input, since both input signals are the same frequency.

AN189

Figure 9. Phase Detector  $\pm$  Voltages

Figure 10. Low Frequency Doubler