# CMOS 8-BIT, 20 MHz FLASH A/D CONVERTER

### DESCRIPTION

The TS 8338 is a monolithic CMOS 8 bit parallel flash analog to digital converter designed for applications requiring low power consumption and high speed conversion.

The TS 8338 uses 256 parallel comparators to digitize fast moving analog input signals without the need for external sample and hold circuits or input buffers. An overflow bit can be used

With an encode rate of 15 MHz (A version) or 20 MHz (B version), the TS 8338 is specified to operate from commercial to military temperature range with analog input frequency of 3 MHz (A version) or 5 MHz (B version), making it useful for a variety of applications and environments.

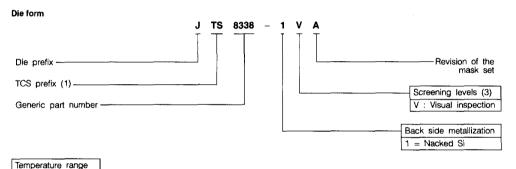

The TS 8338 is packaged in hermetic DIL ceramic 28 pin configuration or in LDCC but also available in die form.

# MAIN FEATURES

- 8 bits resolution.

- 20 MHz sampling rate.

- Low power CMOS: 330 mW @ 20 MHz.

- Single power supply: 5 V.

- -55°C/ + 125°C specified.

- Guaranteed monotonicity.

- High input impedance.

- Command input / tristate output :

- CMOS / TTL compatible.

- Overflow bit.

- No sample & hold required.

- Pin to Pin compatible with MP 7684.

# APPLICATIONS

- Military systems.

- Radar pulse analysis.

- Video digitizing.

- Image processing.

- Medical imaging.

- High energy physics.

- X-Ray and ultrasound imaging.

## **ABSOLUTE MAXIMUM RATINGS (Note 1)**

| Parameter                                  | Symbol                               | Value                 | Unit |

|--------------------------------------------|--------------------------------------|-----------------------|------|

| Supply voltages (Note 2)                   | AV <sub>DD</sub> , DV <sub>DD</sub>  | 4 to +7               | ٧    |

| Maximum difference between supply voltages | AV <sub>DD</sub> to DV <sub>DD</sub> | ±0.4                  | ٧    |

| Upper reference voltage                    | + VREF                               | 0 to AVDD             | V    |

| Lower reference voltage                    | - VREF                               | 0 to AV <sub>DD</sub> | V    |

| Mid point reference current                | 1/2 IVREF                            | 2                     | mA   |

| First quarter reference current            | 1/4 IVREF                            | 2                     | mA   |

| Third quarter reference current            | 3/4 IVREF                            | 2                     | mA   |

| Analog input voltage (Note 2)              | VIN                                  | 0 to AV <sub>DD</sub> | V    |

| Digital input voltage (Note 2)             | CLK                                  | 0 to DV <sub>DD</sub> | V    |

| Tristate command                           | ČĒ1, CE2                             | 0 to DV <sub>DD</sub> | V    |

| Digital output currents                    | 1 <sub>D</sub>                       | 40                    | mA   |

| Junction temperature                       | Τį                                   | + 150                 | °C   |

| Storage temperature                        | T <sub>stg</sub>                     | - 65 to + 150         | °C   |

| Operating temperature range                | T <sub>case</sub>                    | - 55 to + 125         | °C   |

| Lead temperature (soldering 10 S)          | Tleads                               | + 260                 | °C   |

Note 1: Absolute maximum ratings are limiting applied individually while other parameters are within specified operating conditions. Long exposure to maximum rating may affect device reliability.

Note 2: With respect to AVSS = DVSS.

## **USER WARNING**

The power supplies must be applied before all the other signals to prevent damage from occuring on the device.

To prevent reliability problem and dynamic performance damage, high speed transition on power supply must be avoided.

## **SPECIFICATIONS**

## **Electrical operating characteristics**

$AV_{DD} = DV_{DD} = +5 \text{ V}$ ;  $T_{C} = 25^{\circ}\text{C}$  (unless otherwise specified)

|                                                                                                              |                   |                    |                | TS 8338 B  |                                    |                | TS 8338 A  |                                    |                      |

|--------------------------------------------------------------------------------------------------------------|-------------------|--------------------|----------------|------------|------------------------------------|----------------|------------|------------------------------------|----------------------|

| Parameter                                                                                                    | T <sub>case</sub> | Test<br>level      | Min.           | Тур.       | Max.                               | Min.           | Тур.       | Max.                               | Unit                 |

| RESOLUTION                                                                                                   |                   |                    | 8              |            |                                    | 8              |            |                                    | Bits                 |

| DIGITAL INPUTS AND OUTPUTS Logic compatibility (Note 1)                                                      |                   |                    | С              | MOS and 1  | ΠL                                 | (              | MOS and    | TTL                                |                      |

| Clock input : CMOS level  Logic «0» voltage  Logic «1» voltage                                               | full<br>full      | IV                 | 0<br>3.5       |            | 1.5<br>5                           | 0<br>3.5       |            | 1.5<br>5                           | v<br>v               |

| Tristate command : CMOS level  • Logic «0» voltage  • Logic «1» voltage                                      |                   | 111                | 0<br>3.5       |            | 1.5<br>5                           | 0<br>3.5       |            | 1.5<br>5                           | V<br>V               |

| Output data  • Logic «0» voltage (Note 2)  • Logic «1» voltage (Note 3)  • Tristate  • Output delay (Note 4) | full<br>full      | II, D<br>III<br>IV | 2.4            | 0.1<br>25  | 0.5<br>10<br>40                    | 2.4            | 0.1<br>25  | 0.5<br>10<br>40                    | V<br>V<br>μA<br>ns   |

| MAXIMUM SAMPLING FREQUENCY                                                                                   |                   | 1                  | 20             |            |                                    | 15             |            |                                    | MHz                  |

| ANALOG INPUT Voltage range Input capacitance Input resistance Analog bandwidth (Note 5)                      |                   | V<br>IV<br>I, D    | 10             | VREF       | 50                                 | 10             | VREF       | 50                                 | V<br>pF<br>MΩ<br>MHz |

| REFERENCE INPUT Lower reference voltage Upper reference voltage                                              |                   | V<br>I, D          | 1              | 0<br>2.5   | AV <sub>DD</sub> 1.5               | 1              | 0<br>2.5   | AVDD - 1.5                         | V<br>V               |

| Differential reference voltage Reference ladder resistance                                                   | full              | I, D<br>I, D       | 1<br>100<br>50 | 2.5<br>150 | AV <sub>DD</sub> 1.5<br>200<br>250 | 1<br>100<br>50 | 2.5<br>150 | AV <sub>DD</sub> 1.5<br>200<br>250 | V<br>Ω<br>Ω          |

| POWER REQUIREMENTS Power supply                                                                              |                   | I, D               | 4.5            | 5          | 5.5                                | 4.5            | 5          | 5.5                                | ٧                    |

| Power dissipation (Note 6)  • Analog supply  • Digital supply                                                |                   | I, D<br>I, D       |                | 260<br>70  | 360<br>150                         |                | 230<br>55  | 330<br>120                         | mW<br>mW             |

| THERMAL RESISTANCE (Note 7) Junction-to-ambient (still air) θ JA Junction-to-case θ JC                       |                   | V                  |                | 50<br>20   |                                    |                | 50<br>20   |                                    | °C/W                 |

Note 1 : CMOS : clock input, CE1, CE2 TTL : data output.

Note 2: With  $l_{out} = -4 \text{ mA}$ .

Note 3: With  $l_{out} = +0.4 \text{ mA}$ .

Note 4: See timing diagram. Note 5: Specified frequencies are maximum with no missing codes.

Note 6: Clock frequency: 20 MHz for TS 8338 B, 15 MHz for TS 8338 A.

Note 7: For DIL ceramic package.

# System performance characteristics

$AV_{DD} = DV_{DD} = +5 V$ ;  $T_C = 25^{\circ}C$  (unless otherwise specified)

|                                                                                                                                                                                                                                                                                       |       |                    |               | TS 8338 B       |                |               | TS 8338 A       |                |                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------|---------------|-----------------|----------------|---------------|-----------------|----------------|----------------------|

| Parameter                                                                                                                                                                                                                                                                             | Tcase | Test<br>level      | Min.          | Тур.            | Max.           | Min.          | Тур.            | Max.           | Unit                 |

| ACCURACY (Note 1)                                                                                                                                                                                                                                                                     |       |                    |               |                 |                |               |                 |                |                      |

| Offset error                                                                                                                                                                                                                                                                          | full  | I, D<br>II         |               | ±5              | ± 10<br>± 15   |               | ±5              | ± 10<br>± 15   | LSB<br>LSB           |

| Gain error                                                                                                                                                                                                                                                                            | full  | l, D<br>II         |               | ±5              | ± 10<br>± 15   | ,             | ±5              | ± 10<br>± 15   | LSB<br>LSB           |

| Integral nonlinearity                                                                                                                                                                                                                                                                 | full  | 1, D<br>11         |               | ±0.6            | ± 1.2<br>± 2   |               | ± 0.6           | ±1.2<br>±2     | LSB<br>LSB           |

| Differential nonlinearity                                                                                                                                                                                                                                                             | full  | I, D<br>II         |               | ± 0.4           | ± 0.8<br>± 0.9 |               | ±0.4            | ± 0.8<br>± 0.9 | LSB<br>LSB           |

| Monotonicity and no missing codes                                                                                                                                                                                                                                                     | full  | IV                 | Guaranteed in | specified tem   | erature range  | Guaranteed in | specified temp  | perature range |                      |

| DYNAMIC CHARACTERISTICS (Note 2)                                                                                                                                                                                                                                                      |       |                    |               |                 |                |               |                 |                | 1                    |

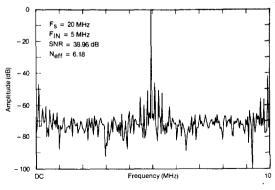

| $\begin{split} & \text{Signal-to-noise ratio} \\ & & F_S = 10 \text{ MHz}  F_{\text{in}} = 0.1 \text{ MHz} \\ & F_S = 15 \text{ MHz}  F_{\text{in}} = 3  \text{MHz} \\ & F_S = 20 \text{ MHz}  F_{\text{in}} = 5  \text{MHz} \end{split}$                                             |       | 1, D<br>1          | 44<br>32      | 45<br><br>36    |                | 44<br>32      | 45<br>36<br>—   |                | dB<br>dB<br>dB       |

| $\begin{split} & \text{Total harmonic distorsion} \\ & \text{F}_S = 10  \text{MHz}  \text{F}_{\text{in}} = 0.1  \text{MHz} \\ & \text{F}_S = 15  \text{MHz}  \text{F}_{\text{in}} = 3  \text{MHz} \\ & \text{F}_S = 20  \text{MHz}  \text{F}_{\text{in}} = 5  \text{MHz} \end{split}$ |       | 1, D<br> <br> <br> | 44            | 49<br>—<br>37   |                | 44<br>32      | 49<br>37<br>-   |                | dB<br>dB<br>dB       |

| Number of effective bits $F_S = 10 \text{ MHz} \qquad F_{in} = 0.1 \text{ MHz}$ $F_S = 15 \text{ MHz} \qquad F_{in} = 3  \text{MHz}$ $F_S = 20 \text{ MHz} \qquad F_{in} = 5  \text{MHz}$                                                                                             |       | I, D<br>I          | 7             | 7.3<br>—<br>5.6 |                | 7<br>5        | 7.3<br>5.6<br>— |                | Bits<br>Bits<br>Bits |

| Aperture uncertainty                                                                                                                                                                                                                                                                  |       | ν                  | <u></u>       | 100             |                |               | 100             |                | pS                   |

Note 1: Histogram based on sampling of 100 kHz sinusoïdal analog signal with an encode rate of 10 MHz. Note 2 : Dynamic measurements are performed with a  $V_{p\cdot p}$  sine wave input équal to 90 % of  $V_{REF}$ .

|            | EXPLANATION OF TEST LEVELS                                                   |

|------------|------------------------------------------------------------------------------|

| Test level |                                                                              |

| l          | 100 % production tested.                                                     |

| 11         | 100 % production tested at +25°C, and sample tested at specified temperature |

| 188        | Sampled test only.                                                           |

| IV         | Parameter is guaranteed by design and characterization testing.              |

| v          | Parameter is a typical value only.                                           |

| D          | 100 % probe tested on wafer at Tamb = +25°C.                                 |

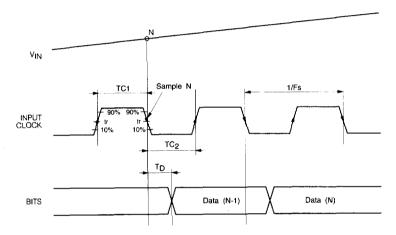

# **SWITCHING PERFORMANCES**

| Symbol           | Definition of terms                           | Min. | Тур. | Max. | Unit |

|------------------|-----------------------------------------------|------|------|------|------|

| 1/F <sub>S</sub> | Period of clock signal                        | 50   |      |      | ns   |

| TC1              | High level clock pulse width (auto zero time) | 15   |      |      | ns   |

| TC2              | Low level clock pulse width                   | 25   |      |      | ns   |

| TD               | Delay time between input and output           |      | 20   |      | ns   |

| tr/tf            | Clock rise and fall time                      |      | 5    |      | ns   |

# **TIMING DIAGRAM**

Figure 1

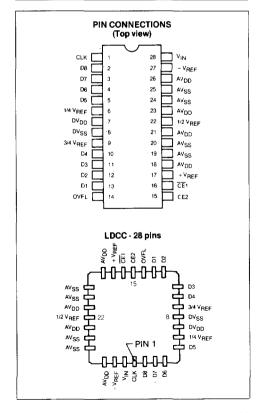

# PIN DESCRIPTION

| PIN Symbol     |                   | Function                 | Description                                                                                                                     |  |  |

|----------------|-------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|

| DIL            | Symbol            | Function                 | Description                                                                                                                     |  |  |

| 13             | D1                | LSB output               |                                                                                                                                 |  |  |

| 12             | D2                | D2 output                |                                                                                                                                 |  |  |

| 11             | D3                | D3 output                |                                                                                                                                 |  |  |

| 10             | D4                | D4 output                | Tristate buffer outputs                                                                                                         |  |  |

| 5              | D5                | D5 output                | mstate burier outputs                                                                                                           |  |  |

| 4              | D6                | D6 output                |                                                                                                                                 |  |  |

| 3              | D7                | D7 output                |                                                                                                                                 |  |  |

| 2              | D8                | D8 output                |                                                                                                                                 |  |  |

| 14             | OVFL.             | Overflow<br>status line  | This line is set to logical «1» when the input signal is higher than the + VREF voltage. All data (1 to 8) are set logical «1». |  |  |

| 6              | 1/4 VREF          | 1st quarter<br>reference | Access to the first quarter reference voltage.                                                                                  |  |  |

| 8              | DVss              | Digital ground           |                                                                                                                                 |  |  |

| 7              | DVDD              | Digital<br>supply        |                                                                                                                                 |  |  |

| 15             | CE2               | Tristate command         | CE2 = «0»: Tristate for both overflow status and data lines.                                                                    |  |  |

| 16             | CE1<br>(see Note) | Tristate command         | CE2 = $\alpha$ 1»: Overflow valid out data lines valid only if $\overline{CE1}$ = $\alpha$ 0».                                  |  |  |

| 27             | -VREF             | Lower ref.               | Access to the lower reference voltage. A voltage source must be applied (or ground).                                            |  |  |

| 19 24<br>20 25 | AVSS              | Analog ground            |                                                                                                                                 |  |  |

| 1              | CLK               | Clock input              | CMOS levels.                                                                                                                    |  |  |

| 22             | 1/2 VREF          | Half ref.                | Access to the half reference voltage.                                                                                           |  |  |

| 28             | VIN               | Analog input             |                                                                                                                                 |  |  |

| 17             | + VREF            | Upper ref.               | Access to the upper reference voltage. A voltage source must be applied.                                                        |  |  |

| 9              | 3/4 VREF          | Third quarter reference  | Access to the Third quarter reference voltage.                                                                                  |  |  |

| 18 23<br>21 26 | AVDD              | Analog supply            |                                                                                                                                 |  |  |

| Note : See     | e Figure 2.       |                          |                                                                                                                                 |  |  |

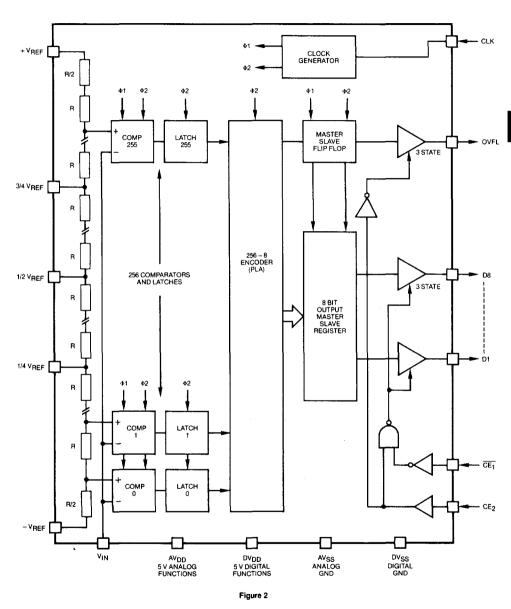

## **FUNCTIONAL BLOCK DIAGRAM**

#### **FUNCTIONAL DESCRIPTION**

TS 8338 series include:

- a sequencer generating internal clock,

- a core ensuring conversion,

- an output circuit delivering digital data,

- the sequencer generates 3 internal clocks from pin CLK and their complements.

| nternal phases | Circuits concerned                | Function                |  |  |

|----------------|-----------------------------------|-------------------------|--|--|

| Ф1             | Comparators                       | Autozero                |  |  |

| Φ1             | Comparators                       | Sampling and comparison |  |  |

| Ф2             | Latches                           | Storage                 |  |  |

| Φ2             | Encoder                           | Transmission            |  |  |

| Ф3             | Output master / slave flip - flop | Sampling                |  |  |

| Ф3             | Output master / slave flip - flop | Storage                 |  |  |

## · The core includes :

- A resistor linear network delivering 256 reference voltages distributed linearly between external reference voltages + VREF and - VREF. Access to quarter 1/4 VREF half 1/2 VREF and three quarter 3/4 VREF bridges enables following.

- either improve linearity by externally forcing reference voltages,

- filter disturbances going through the bridge by means of external capacitors,

- or delinearize the bridge by means of external resistors (law of linear compression by blocks).

- A set of 256 voltage comparators parallel connected across the 256 taps of the reference bridge and the input analog signal which defines the 256 (2<sup>8</sup>) quantization levels.

- In first phase Φ1, these comparators store their threshold then, in phase Φ, they compare the thresholds with the input The comparators with an input signal voltage lower than the reference voltage present a given state at the output, the

- others present the complementary state. The 256 comparators outputs are stored in 256 latches at the end of phase  $\Phi$ 2.

- A 256 to 8 decoder detecting the transition between the comparators in a given state and the ones in the complementary state.

- The line enabled corresponds to the last comparator which has trigged, i.e. the comparator with the reference voltage nearest by default to the input signal.

- A PLA following the decoder and coding over 8 bits the detected comparison chain in binary. If the input signal is lower than the lowest reference voltage (1st comparator), code 0 is written at the output. If the input signal is higher than the upper most reference voltage (256 th comparator), code 255 is written at the output and overflow bit is set to logic «1».

- The output stage consists of 9 identical parts (8 bits and overflow) each formed of a D flip-flop connected to the PLA output with an output buffer. This buffer includes a selective high impedance command.

Inputs CE1 and CE2 switch the output bits to this 3rd state (with overflow bit if required) in order to facilitate:

- Parallel connection of the 2 converters thus providing a double sampling frequency while maintaining an 8 bit resolution.

- Series connection of the 2 converters providing a 9 bit resolution while maintaining a 5 to 10 MHz sampling frequency.

| CE1 | CE2 | D1 D8 in 3rd state | OVFL in 3rd state |

|-----|-----|--------------------|-------------------|

| 0   | 0   | Yes                | Yes               |

| 0   | 1   | No                 | No                |

| 1   | 0   | Yes                | Yes               |

| 1   | 1   | Yes                | No                |

# User warning

The power supplies must be applied before all the other signals to prevent damages from occuring on the device.

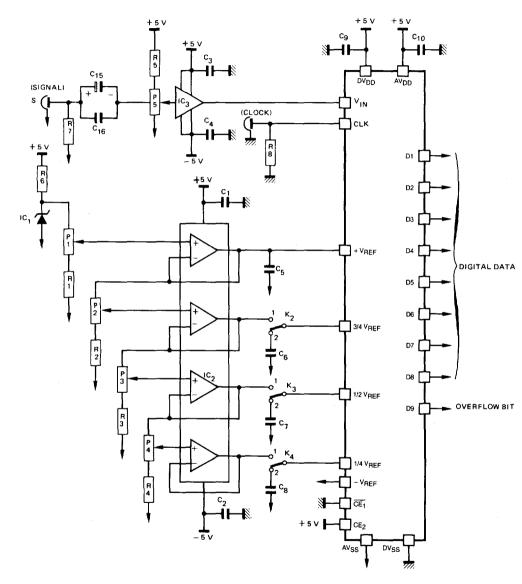

#### TYPICAL EVALUATION CIRCUIT

The general circuit used for the flash converter in typical conditions is represented on Figure 3.

#### Voltage reference

Flash converter requiring a positive reference voltage (+ VREF) ranging from 2 V to 3 V, the circuit generates a reference voltage of 2.5 V from the power supply voltage (+ 5 V) and a precision regulation diode (IC<sub>1</sub>).

#### Resistor bridge reference voltages

The circuit allows to access some particular points on the resistor bridge. These points correspond to 3/4, 1/2 and 1/4 of the bridge total resistance. This feature enables use of the flash converter in two ways:

- In linear operation with these 3 points grounded by decoupling capacitors in order to filter disturbances along the bridge (K2, K3 and K4 in position 2).

- In non-linear operation with the following 2 functions.

- Improvement in flash converter integral linearity by forcing the 3 points to their corresponding voltages (K<sub>2</sub>, K<sub>3</sub> and K<sub>4</sub> on position 1).

- Implementation of a non-linear conversion law (compression law for instance) in order to better observe the results of the conversion on one part only of the transfer curve (K<sub>2</sub>, K<sub>3</sub>, K<sub>4</sub> on position 1).

#### Analog signal

The input analog signal must be driven by a wide band buffer amplifier (IC3) with a very low output impedance.

In order to eliminate the almost uncontrollable off-sets introduced by the source generator or buffer amplifier proper, two capacitors parallel mounted (C₁₅ and C₁₆) are added in series after the amplifier. For low frequencies (≤ 1 MHz) tantalum capacitor (C₁₆) is used as a short-circuit; for higher frequencies (> 1 MHz) the ceramic capacitor (C₁₆) is used as a short-circuit.

After the capacitors, a potentiometer (P5) with the middle point connected to the buffer amplifier input adds a DC component to the input signal. The signal thus obtained has an average value different from zero, lying between —VREF and + VREF and which can be converted by the flash converter.

#### Clock signal

Clock signals are CMOS compatible.

## · Power dissipation

At very low frequency, (less than 1 MHz), all power dissipation is done by auto zero time (high level clock). If clock is clamped at high level, power dissipation is 600 mW. To reduce power dissipation it's necessary to increase low level clock.

#### · Considerations on electrical layout

A certain number of elementary precautions should be taken in the electrical layout when using high frequencies.

The main ones are as follows:

- a ground plane for the components,

- the ground tracks corresponding to the various signals (clock, input signal, references) are separated and connected together to a single point,

- a star distributed power supplies (idem for ground) to avoid any possible loop.

- a maximum capacitive uncoupling as close as possible to each circuit.

Notes: Use of chip capacitors increase decoupling quality.

For typical application circuit, the same surroundings can be used.

# TYPICAL EVALUATION CIRCUIT (SCHEMATIC)

Figure 3

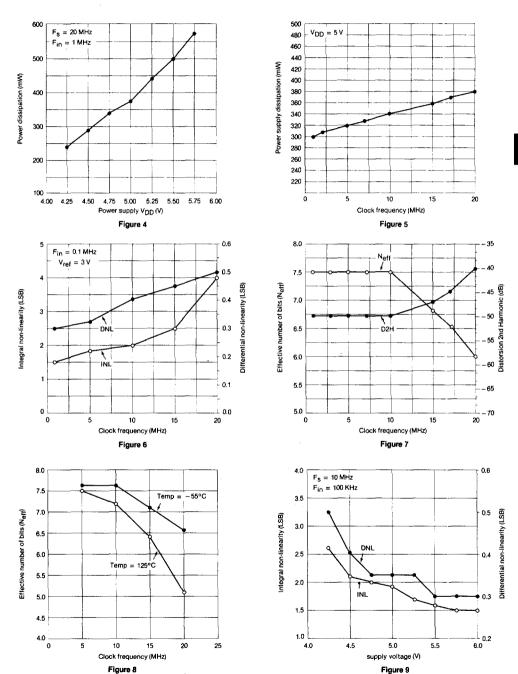

#### TYPICAL PERFORMANCE CURVES

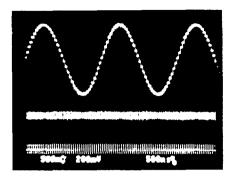

Figure 10 : Reconstructed waveform, 20 MHz sampling rate, 500 kHz input frequency.

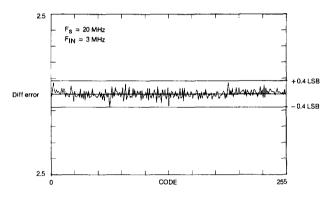

Figure 11: Differential linearity.

Figure 12: Spectrum analysis.

### **DEFINITION OF TERMS**

### Signal-to-noise ratio (SNR):

Determined by FFT analysis,

$$\text{SNR} = 10 \cdot \text{log} \quad \left[ \frac{P\left(F_{1N}\right)}{P_{n}} \right] = 10 \cdot \text{log} \quad \left[ \frac{A^{2}\left(F_{1N}\right)}{\Sigma \, A^{2}\left(j\right)} \right] \, j = F_{1n}$$

#### With:

- P (FIN) spectral power of the input frequency FIN.

- Pn noise power, which is defined as the sum of the powers of all spectral components, except FIN.

- A (i) amplitude of the spectral component of frequency i.

# Total harmonic distorsion (THD) :

Determined by FFT analysis.

$$THD = 10 . log \quad \left[ \frac{P\left(F_{\left|N\right\rangle}\right)}{P_{hm}} \right] = 10 . log \quad \left[ \frac{A^{2}\left(F_{\left|N\right\rangle}\right)}{\Sigma A^{2}\left(k,F_{\left|N\right\rangle}\right)} \right] \quad with \ k \geqslant 2$$

With: Phm harmonic noise power, which is defined as the sum of the powers of au harmonics of FIN.

## Number of effective bits (Neff):

Determined by FFT analysis.

$$N_{eff} = \frac{SNR - 1.76}{6.02}$$

# Gain error (Ge):

$$G_e = \frac{G - G_e}{G_o}$$

#### With:

- Go slope of theoretical straight line of the ADC transfer function.

- G slope of the real best-fit straight line.

# Integral nonlinearity (INL):

Measured after trimming the offset and gain errors to zero.

The integral nonlinearity for an output code i, INL(i), is the difference between the measured input voltage at which the transition occurs and the ideal value of this transition.

The ADC integral nonlinearity INL is the maximum value of all |INL(i)|.

# Differential nonlinearity (DNL):

Measured after trimming the offset and gain errors to zero.

The differential nonlinearity for an output code i, DNL(i), is the difference between the measured step size of code i and the ideal ISB step size.

The ADC differential nonlinearity DNL is the maximum value of all .DNL(i)|.

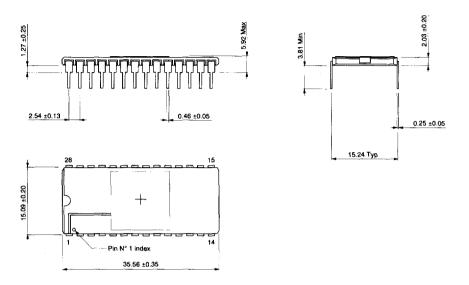

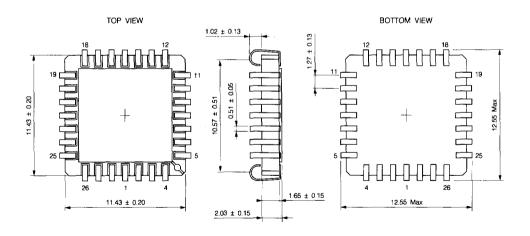

## MECHANICAL PACKAGE DATA

DIL 28 - CERAMIC SIDE BRAZED PACKAGE

Dimensions in mm

LDCC 28 - LEADED CERAMIC CHIP CARRIER PACKAGE Dimensions in mm

# **DIE MECHANICAL INFORMATION: JTS 8338**

Pad layout: V402

Pad size :  $0.120 \times 0.120$  mm Die size :  $3.660 \times 4.220$  mm Die thickness :  $380~\mu m$

Metallization : Si (Back side)

Al-Si-Ti (Front side)

Passivation : Nitride

Revision: A

Qualification lot package : DIL 28 Back side potential : AVSS

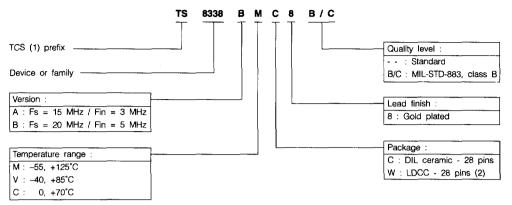

# ORDERING INFORMATION

# Packaged device

-: Tamb = 25°C

Note 1: THOMSON-CSF SEMICONDUCTEURS SPECIFIQUES.

Note 2: Available only in standard quality level (no BIC).

Note 3: For availability of the different available versions contact your TCS sales office.