# BIPOLAR HIGH-SPEED 8-BIT FLASH A/D CONVERTER

### DESCRIPTION

Designed to be user-friendly, the TS 83068 is a complete monolithic flash analog-to-digital converter that combines all circuitry required to convertor high-speed analog signals into 8-bit digital data at rates of up to 35 MHz. Based on the TS 83048 monolithic flash analog-to-digital converter, the TS 83068 contains a wideband analog input amplifier, precision voltage reference and three-state outputs as well as zero-scale and full-scale flags.

The TS 83068 offers significant advantages in space efficiency and ease of use. Combining all analog front-end circuitry with the A/D converter in an easy to use package results in savings of board space, component and assembly cost. Furthermore, labor intensive circuit adjustments are eliminated.

The TS 83068 is a monolithic alternate source to the THC 1068, but offers enhancements over it predecessors.

The TS 83068 is designed to meet the demanding requirements of military applications. It is available in a 24-pin hermetic package and operates with guaranteed performance over the full -55°C to +125°C case operating temperature range. Available also in die form.

# MAIN FEATURES

- 8-bit resolution.

- 35 MHz sampling rate.

- Excellent SNR.

- Low power: 0.8 W.

- Dual power supply: 5 V and 5.2 V.

- -55°C/ + 125°C specified.

- Guaranteed monotonicity.

- High slew rate of input stages.

- Compatible with THC 1068.

- No sample & hold required.

- Evaluation board : TSEV 83068.

- TTL compatible input and output.

- Tre companiole input and output.

- Three state outputs.

- Very low input capacitance.

- 45 MHz full power analog input bandwidth.

### **APPLICATIONS**

- Military systems.

- Radar pulse analysis.

- Video digitizing.

- Image processing.

- Medical imaging.

- High-energy physics.

- X-Ray and ultrasound imaging.

- Communication/signal intelligence.

# **ABSOLUTE MAXIMUM RATINGS (Note 1)**

| Parameter                         | Symbol                     | Value       | Unit |

|-----------------------------------|----------------------------|-------------|------|

| Positive supply voltages (Note 2) | Vcc                        | +4 to +6    | V    |

| Negative supply voltages (Note 2) | VEE                        | -6.2 to -4  | V    |

| Maximum current                   | Ref                        | ±5          | mA   |

| Analog control pins               | Range, Offset,<br>RB, AOUT | VEE to VCC  | V    |

| Analog input (Note 2)             | AIN                        | VEE to VCC  | V    |

| Digital input voltage (Note 2)    | CONV, OE,<br>NMINV, NLINV  | GND to VCC  | V    |

| Digital output currents           | D1 → D8, FS<br>ZS          | 30          | mA   |

| Junction temperature              | Τį                         | 175         | °C   |

| Storage temperature               | T <sub>stg</sub>           | -65 to +150 | °C   |

| Operating temperature range       | T <sub>case</sub>          | -55 to +125 | °C   |

| Lead temperature (soldering 10 s) | Tleads                     | + 260       | °C   |

Note 1: Absolute maximum ratings are limiting values applied individually while other parameters are within specified operating conditions. Long exposure to maximum rating may affect device reliability.

Note 2: With respect to AGND = DGND.

### **USER WARNING**

The power supplies must be applied before all the other signals to prevent damage from occuring on the device.

To prevent reliability problem and dynamic performance damage, high speed transition on power supply must be avoided.

# **SPECIFICATIONS**

# Electrical operating characteristics

$V_{CC} = 5 \, V$  ;  $V_{EE} = -5.2 \, V$  ;  $T_{C} = 25 \, ^{\circ} C$  (unless otherwise specified)

| Parameter                                                                               | Tcase        | Test<br>level            | Min.                         | Тур.                                  | Max.                         | Unit                 |

|-----------------------------------------------------------------------------------------|--------------|--------------------------|------------------------------|---------------------------------------|------------------------------|----------------------|

| RESOLUTION                                                                              |              |                          |                              | 8                                     |                              |                      |

| DIGITAL INPUTS AND OUTPUTS Logic compatibility                                          |              |                          |                              | ΠL                                    |                              |                      |

| Digital inputs  Logic «0» voltage  Logic «1» voltage                                    | full<br>full | IV<br>IV                 | 0<br>2                       |                                       | 0.8<br>5                     | v<br>v               |

| Output data  • Logic «0» voltage (Note 1)  • Logic «1» voltage  • Output delay (Note 2) | full<br>full | II, D<br>II, D<br>IV     | 0<br>2.4                     |                                       | 0.4<br>5                     | V<br>V<br>ns         |

| MAXIMUM CLOCK FREQUENCY                                                                 |              | 1                        | 30                           | 35                                    |                              | MHz                  |

| ANALOG INPUT Voltage range (Note 3)                                                     |              | ><br>><br>>              |                              | -0.5;0.5<br>-1;0<br>0;+1              |                              | V<br>V<br>V<br>pF    |

| Input capacitance Input resistance                                                      |              | v                        |                              | 1                                     |                              | kΩ                   |

| Analog bandwidth (Note 4)                                                               |              | v                        |                              | 45                                    |                              | MHz                  |

| ANALOG CONTROL Ref Range (Note 5) Offset RB                                             |              | V<br>V<br>V              |                              | 1.2<br>1<br>0 → 1.2<br>-2             |                              | v<br>v<br>v          |

| POWER REQUIREMENTS                                                                      | 1            |                          | <u></u>                      |                                       |                              |                      |

| Power supply  Positive supply  Negative supply                                          | full<br>full | I, D<br>II<br>I, D<br>II | 4.5<br>4.5<br>- 5.7<br>- 5.7 | 5<br>5<br>- 5.2<br>- 5.2              | 5.5<br>5.5<br>- 4.7<br>- 4.7 | V<br>V<br>V          |

| Power dissipation Positive supply Negative supply                                       | full<br>full | I, D<br>II<br>I, D<br>II |                              | 200<br>600                            | 350<br>400<br>700<br>750     | mW<br>mW<br>mW<br>mW |

| THERMAL RESISTANCE Junction-to-ambient (still air) Junction-to-case                     |              | ٧                        |                              | 45<br>5                               |                              | °CW                  |

| ACCURACY (Note 6) Differential nonlinearity                                             | full         | I, D<br>II<br>I, D       |                              | ± 0.5<br>± 0.6<br>± 0.5               | ± 0.8<br>± 0.9<br>± 0.8      | LSB<br>LSB<br>LSB    |

| Integral nonlinearity  Monotonicity and no missing codes                                | full<br>full | II<br>IV                 | Guaranteed                   | ± 0.5<br>± 0.6<br>over specified temp | ± 0.9                        | LSB                  |

### SPECIFICATIONS (Continued)

# Electrical operating characteristics

$V_{CC} = 5 \text{ V}$ ;  $V_{EE} = -5.2 \text{ V}$ ;  $T_{C} = 25 ^{\circ}\text{C}$  (unless otherwise specified)

| Parameter                                              |      | est<br>vel | Min. | Тур. | Max. | Unit   |

|--------------------------------------------------------|------|------------|------|------|------|--------|

| DYNAMIC CHARACTERISTICS (Note 7)                       |      |            |      |      |      | 1      |

| Signal to noise ratio                                  |      |            |      |      |      |        |

| $F_S = 30  \text{MHz}  F_{in} = 1  \text{MHz}$         | ١ ،  | v          |      | 43.9 |      | ₫B     |

| $F_S = 1 MHz$ $F_{in} = 0.1 MHz$                       | . l, | D          | 43.9 | 45.7 |      | ₫₿     |

| $F_S = 20 \text{MHz}$ $F_{in} = 1 \text{MHz}$          |      | 1          | 39.7 | 45.1 |      | dΒ     |

| $F_S = 20 \text{MHz}$ $F_{\text{in}} = 2.5 \text{MHz}$ |      | 1          | 37.9 | 41.5 | İ    | dB     |

| Total harmonic distorsion                              |      |            |      |      |      |        |

| $F_S = 30 \text{MHz}$ $F_{\text{in}} = 1 \text{MHz}$   | ,    | v          |      | 52   |      | dB     |

| $F_S = 1 MHz$ $F_{in} = 0.1 MHz$                       | l,   | D          | 48   | 55   |      | dB     |

| $F_S = 20  \text{MHz}  F_{in} = 1  \text{MHz}$         |      | 1          | 45   | 52   |      | dB     |

| $F_S = 20 \text{MHz}$ $F_{\text{in}} = 2.5 \text{MHz}$ | !    | 1          | 40   | 44   |      | dB     |

| Number of effective bits                               |      |            |      |      |      |        |

| $F_S = 30  \text{MHz}  F_{\text{in}} = 1  \text{MHz}$  | ١    | v          |      | 7.0  | ļ    | Bits   |

| $F_S = 1 MHz$ $F_{in} = 0.1 MHz$                       | l,   | D          | 7.0  | 7.3  |      | Bits   |

| $F_S = 20 \text{MHz}$ $F_{in} = 1 \text{MHz}$          | į    | 1          | 6.3  | 7.2  |      | Bits   |

| $F_S = 20 \text{MHz}  F_{in} = 2.5 \text{MHz}$         | İ    | i          | 6.0  | 6.6  |      | Bits   |

| Aperture uncertainty                                   | ,    | v          |      | 20   | 1    | ps     |

| Differential phase                                     | ١,   | v          |      | 1    | -    | degree |

| Differential gain                                      | ,    | v          |      | 2    |      | %      |

Note 1 : With  $I_{OUT} = 4 \text{ mA}$ .

Note 2: See timing diagram.

Note 3: Depending upon offset pin connection.

Note 4: The analog input frequency at which the spectral power of the fundamental frequency (as determined by FFT analysis) is reduced by 3 dB.

Note 5: The reference gain control voltage can be adjusted between 0.5 V and 1.2 V (see Figure 3).

Note 6: Histogram based on sampling of 100 kHz sinusoïdal analog signal with and encoding rate of 1 MHz.

Note 7: Dynamic measurements are performed with an analog input signal 1 dB below full scale.

|            | EXPLANATION OF TEST LEVELS                                                   |

|------------|------------------------------------------------------------------------------|

| Test level |                                                                              |

| 1          | 100 % production tested.                                                     |

| 11         | 100 % production tested at +25°C, and sample tested at specified temperature |

| IfI        | Sample tested only.                                                          |

| IV         | Parameter is guaranteed by design and characterization testing.              |

| V          | Parameter is a typical value only.                                           |

| D          | 100 % probe tested on wafer at Tamb = +25°C.                                 |

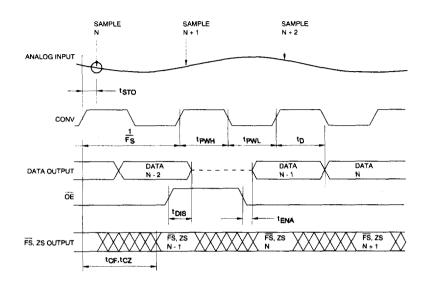

# **TIMING DIAGRAM**

Figure 1

# **SWITCHING PERFORMANCES**

| Parameter               | Symbol         | Test conditions | Тур. | Unit<br>MHz |  |

|-------------------------|----------------|-----------------|------|-------------|--|

| Maximum conversion rate | FS             | VCC, VEE = Min  | 35   |             |  |

| Sampling time offset    | tsто           |                 | -8   | ns          |  |

| Digital output delay    | t <sub>D</sub> |                 | 10   | ns          |  |

| HIGH impedance enable   | †ENA           |                 | 12   | ns          |  |

| HIGH impedance disable  | tDIS           |                 | 12   | ns          |  |

| Full-scale flag delay   | tor            |                 | 20   | ns          |  |

| Zero-scale flag delay   | tcz            |                 | 20   | ns          |  |

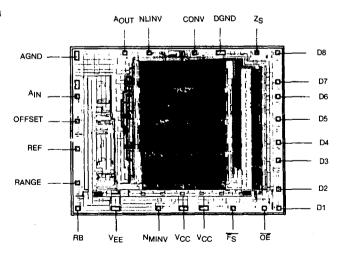

# **FUNCTIONAL BLOCK DIAGRAM**

Figure 2

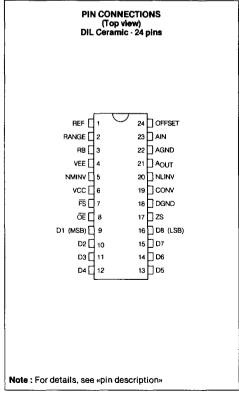

# PIN DESCRIPTION

| Pin | Symbol Function       |                                  | Description                               |  |  |  |  |  |

|-----|-----------------------|----------------------------------|-------------------------------------------|--|--|--|--|--|

| DIL | Зупівої               | Function                         | Description                               |  |  |  |  |  |

| 1   | REF                   | Reference voltage output         | +1.2 V                                    |  |  |  |  |  |

| 2   | RANGE                 | Reference gain control           | +1V                                       |  |  |  |  |  |

| 3   | l RB                  | Reference voltage monitor point  | -2V                                       |  |  |  |  |  |

| 4   | VEE                   | Negative power supply            | -5.2 V                                    |  |  |  |  |  |

| 5   | NMINV                 | Not most significant bit invert  | TTL compatible active low                 |  |  |  |  |  |

| 6   | Vcc                   | Positive power supply            | +5V                                       |  |  |  |  |  |

| 7   | V <sub>CC</sub><br>FS | Full scale flag                  | TTL compatible                            |  |  |  |  |  |

| 8   | ŌĒ                    | Output enable                    | TTL compatible active low                 |  |  |  |  |  |

| 9   | D1                    | Digital output (MSB)             |                                           |  |  |  |  |  |

| 10  | D2                    | Digital output                   |                                           |  |  |  |  |  |

| 11  | D3                    | Digital output                   |                                           |  |  |  |  |  |

| 12  | D4                    | Digital output                   | TTI Adi atata anno atible                 |  |  |  |  |  |

| 13  | D5                    | Digital output                   | > TTL tri state compatible                |  |  |  |  |  |

| 14  | D6                    | Digital output                   |                                           |  |  |  |  |  |

| 15  | D7                    | Digital output                   |                                           |  |  |  |  |  |

| 16  | D8                    | Digital output (LSB)             |                                           |  |  |  |  |  |

| 17  | ZS                    | Zero scale flag                  | TTL compatible                            |  |  |  |  |  |

| 18  | DGND                  | Digital ground                   |                                           |  |  |  |  |  |

| 19  | CONV                  | Convert                          | TTL compatible                            |  |  |  |  |  |

| 20  | NLINV                 | Not least significant bit invert | TTL compatible active low                 |  |  |  |  |  |

| 21  | AOUT                  | Amplifier output monitor point   | 0 to -2 V                                 |  |  |  |  |  |

| 22  | AGND                  | Analog ground                    |                                           |  |  |  |  |  |

| 23  | AIN                   | Analog input                     | -1 to +1 V depending of offset connection |  |  |  |  |  |

| 24  | OFFSET                | Input range offset control       | 0 to +1.2 V                               |  |  |  |  |  |

# **OUTPUT CODING**

|      |                 |                               | Binary           |    |                               |      |                        |                               | Offset two's complement             |                        |                               |     |    |  |

|------|-----------------|-------------------------------|------------------|----|-------------------------------|------|------------------------|-------------------------------|-------------------------------------|------------------------|-------------------------------|-----|----|--|

|      | Midpoints       | True . Inverted               |                  |    |                               | True |                        |                               | Inverted                            |                        |                               |     |    |  |

| Step | 1 LSB = 3.92 mV |                               | NV = 1<br>NV = 1 |    | NMINV = 0<br>NLINV = 0        |      | NMINV = 0<br>NLINV = 1 |                               |                                     | NMINV = 1<br>NLINV = 0 |                               |     |    |  |

|      |                 | D <sub>1</sub> D <sub>8</sub> | FS               | zs | D <sub>1</sub> D <sub>8</sub> | FS   | zs                     | D <sub>1</sub> D <sub>8</sub> | D <sub>1</sub> D <sub>8</sub> FS ZS |                        | D <sub>1</sub> D <sub>8</sub> | FS  | ZS |  |

| 000  | - 0.5000 V      | 00000000                      | 1                | 1  | 11111111                      | 0    | 0                      | 10000000                      | 1                                   | 0                      | 01111111                      | 1   | 0  |  |

| 001  | 0.4961 V        | 00000001                      | 1                | 0  | 11111110                      | 1    | 0                      | 10000001                      | 1                                   | 0                      | 01111110                      | 1   | 0  |  |

| •    | •               | •                             |                  |    | •                             |      |                        | •                             |                                     | •                      |                               |     |    |  |

|      |                 |                               |                  |    |                               |      |                        |                               |                                     |                        | :                             |     |    |  |

| 126  | 0.0059 V        | 01111110                      | 1                | 0  | 10000001                      | 1    | 0                      | 11111110                      | 1                                   | 0                      | 00000001                      | 1   | 0  |  |

| 127  | - 0.0020 V      | 01111111                      | 1                | 0  | 10000000                      | 1    | 0                      | 111111111                     | 0                                   | 0                      | 00000000                      | 1   | 1  |  |

| 128  | + 0.0020 V      | 10000000                      | 1                | О  | 01111111                      | 1    | 0                      | 00000000                      | 1                                   | 1                      | 11111111                      | 0   | 0  |  |

| 129  | - 0.0059 V      | 10000001                      | 1                | 0  | 01111110                      | 1    | 0                      | 00000001                      | 1                                   | 0                      | 11111110                      | 1   | 0  |  |

| •    | •               | •                             |                  |    | •                             |      |                        | •                             | •                                   |                        | •                             |     |    |  |

| :    | •               | •                             |                  |    |                               |      |                        |                               |                                     |                        |                               |     |    |  |

| 254  | +0.4961 V       | 11111110                      | 1                | 0  | 00000001                      | 1    | 0                      | 01111110                      | 1                                   | 0                      | 10000001                      | 1   | 0  |  |

| 1    | ,               |                               |                  |    | 1 1                           |      |                        |                               |                                     | 1.                     |                               | ١ . |    |  |

| 255  | + 0.5000 V      | 11111111                      | 0                | 0  | 00000000                      | 1    | 1                      | 01111111                      | 1                                   | 0                      | 10000000                      | 1   | 0  |  |

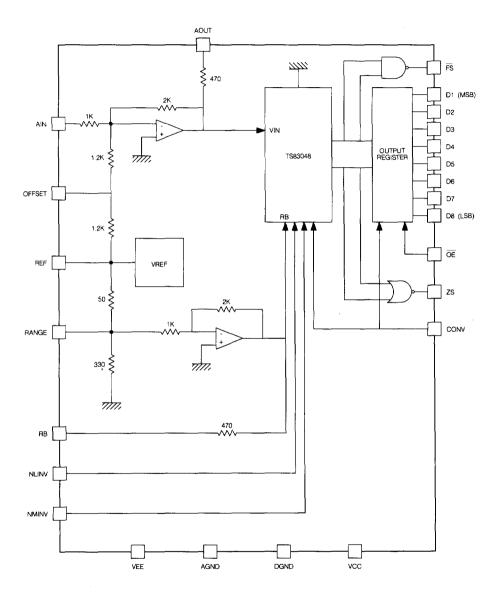

### THEORY OF OPERATION

The TS 83068 is a complete 8 bit A/D monolithic converter. The TS 83068 has four fonctional sections: a wideband input amplifier, a reference generation circuit, an 8 bit flash A/D converter, and an 8 bit three state output register.

The wideband amplifier provides the current necessary to drive the input capacitance of the flash converter while translating the bipolar input to the unipolar range of the flash converter. The input amplifier has a gain of -2 and the stable reference needs no adjustment. The analog input voltage range is -0.5 to 0.5 V but can be configured for a 0 to +1.0 V range by shorting OFFSET to AGND. Likewise, the input can be configured for a 0 to -1.0 V range by connecting the OFFSET pin to the REF pin.

The converter stage is derived from the TS 83048 8 bit A/D converter. The TS 83048 is a flash converter: it compares the signal in an array of 255 comparators referenced by 256 resistors. An encoding stage converts the thermometer code to the 8-bit binary output code. Details of the TS 83048 operation are reported in its data sheet.

The three-state output register holds the output data between convert cycles and can be set into the high-impedance state with the  $\overline{OE}$  control pin.

### **APPLICATIONS**

#### User warning

The power supplies must be applied before all the other signals to prevent damage from occuring on the device.

### **Functional description**

The TS 83068 operates with analog input signals of 1 V amplitude. It is designed for bipolar ( $\pm 0.5$  V) or unipolar positive (0;  $\pm 1$  V) or negative ( $\pm 1$  V; 0 V) input voltage.

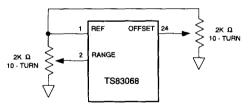

For bipolar input, the offset pin is not connected. For unipolar positive, the offset pin is connected to A<sub>GND</sub>. For unipolar negative the offset pin is connected to the REF pin. A 2 k0 potentiometer can be connected between A<sub>GND</sub>, OFFSET and REF to vary the DC offset of the input amplifier as shown in Figure 3.

The A<sub>OUT</sub> pin allows monitoring the analog signal at the input to the flash converter and is normally left unconnected. It has a nominal series resistance of  $470 \,\Omega$ .

A precision voltage reference is used for the flash converter reference as well as for DC level shifting. The REF pin can sink or source up to 2 mA but is normally left unconnected.

The range pin allows optional adjustment of the negative reference voltage (thus the gain) of the flash converter and is normally left unconnected. For gain adjustment a 2 kΩ potentiometer can be connected between REF, RANGE and AGND as shown in Figure 3. The nominal input resistance is 300  $\Omega$ . The Rg pin allows monitoring of the full scale reference voltage to the flash converter through a 470  $\Omega$  series resistor.

The wideband input amplifier of the TS 83068 provides the current necessary to drive the input capacitance of the flash converter. The amplifier provides a gain -2 and has a nominal input impedance of  $1\,000\,\Omega$ . For lower impedances, a termination resistor should be added as close to the  $A_{IN}$  pin as possible. The TS 83068 is capable of digitizing sinusoidal signals up to 25 MHz. The input amplifier has pulse response as shown in the Typical Performance Curves, with a full-power bandwidth in excess of 40 MHz.

Figure 3: Connection of RANGE, REF and OFFSET.

The digital output of the TS 83068 can be formatted with the NMINV and NLINV control pins. These pins are for D.C. (steady state) use and allow either straight binary or offset two's complement, in either thue or inverted sense. The Output Coding Table shows the output formats possible with these pins. Note that in offset two's complement format, FS and ZS indicate midscale codes rather than full and zero scale codes, as shown in the Output Coding Table. When left unconnected, internal pull-up resistors keep the outputs in true straight binary format.

The data outputs of the TS 83068 can be set into the high-impedance state with the  $\overline{\text{OE}}$  control pin. The outputs become high-impedance points withing tDIS after the  $\overline{\text{OE}}$  is switched HIGH and likewise become valid within tENA after switching  $\overline{\text{OE}}$  LOW.

The output data are three state TTL compatible.

The output flags of the TS 83068 are not latched: they are active even when the data outputs are in the high-impedance state. The FS (active LOW) flag indicates that the output bits of the flash converter are all HIGH. Likewise, the ZS (active HIGH) flag indicates that the output bits of the flash converter are all LOW. ZS and FS represent zero-scale and full-scale analog inputs only when the output code is in the straight binary format. The Output Coding Table shows the status of the output flags for various input voltages and output code formats. Note that the flags indicate the status of the flash converter output one clock cycle before it appears at the output pins of the TS 83068.

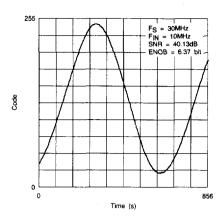

### Packaging

The TS 83068 is mounted in ceramic 24-pin DIL package.

Sockets may be used for prototype evaluation, but should be avoided afterwards, because it leads to limitations of TS 83068 dynamic performance, and increased decoupling difficulties.

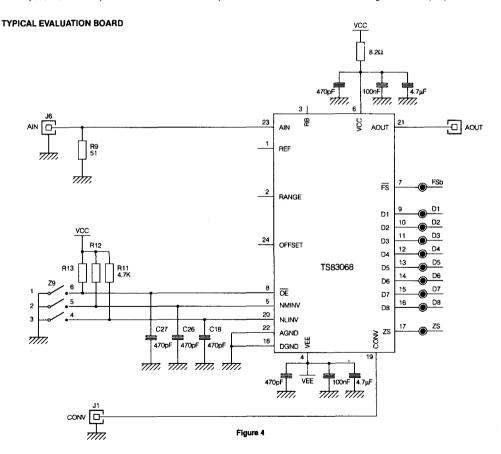

# LAYOUT AND POWER SUPPLY

The TS 83068 is a monolithic converter. Integration of internal (on chip) decoupling capacitors like those used in hybrid circuits is not possible.

So, proper layout of evaluation on board, always critical, is particularly important.

To insure optimum performance, a very quiet  $V_{CC}$  supply is recommended. A  $8.2\,\Omega$  serial resistance between external  $V_{CC}$  and the converter is necessary. Power supplies ( $V_{CC}$  and  $V_{EC}$ ) should be capacitively coupled to ground with three high quality capacitors ( $4.7\,\mu\text{F}$ , 100 nF and 470 pF) to reduce noise in the circuit. These capacitors should be kept as close as possible to circuit package. All ground pins should be connected to ground plane.

Digital switching noise may also have an impact on SNR. This noise can be minimized with 33  $\Omega$  serial resistances on the digital outputs. The commutation peak current will be limited.

The use of a socket with parasitic inductances may limit dynamic performances (noise floor increases), and is not recommended except for prototype or evaluation purposes.

The length of digital input/output signal paths should be matched and kept short, to avoid propagation delay mismatches, increased output bits time skew, and over or undershoot caused by reflections.

So long as propagation delay along the line is shorter than digital signal rise or fall time, the reflection has little effect on the waveform.

50  $\Omega$  impedance microstrip line with 50  $\Omega$  termination chip resistors should be used to drive analog and clock input pins.

### **DEFINITION OF TERMS**

# Signal-to-noise ratio (SNR)

determined by FFT analysis,

SNR =

$$10.\log \left[ \frac{P(F|N)}{P_n} \right] = 10.\log \left[ \frac{A^2(F|N)}{\sum A^2(j)} \right]_{j \neq F|n}$$

#### with:

- P(FIN) spectral power of the input frequency FIN,

- Pn noise power, which is defined as the sum of the powers of all spectral components, except F<sub>IN</sub>.

- A(j) amplitude of the spectral component of frequency j.

### Total harmonic distorsion (THD)

determined by FFT analysis,

$$THD = 10.log \left[ \frac{P\left(F_{1N}\right)}{P_{hn}} \right] = 10.log \left[ \frac{A^{2}\left(F_{1N}\right)}{\sum A^{2}\left(k,F_{1N}\right)} \right] \quad k \geqslant 2$$

with: Phn harmonic noise power, which is defined as the sum of the powers of all harmonics of FIN.

# Number of effective bits (Neff)

determined by FFT analysis,

$$N_{eff} = \frac{SNR - 1.76}{6.02}$$

### Gain error (G<sub>e</sub>)

$$G_e = \frac{G - G_0}{G_0}$$

#### with:

- Go slope of theoretical straight line of the ADC transfer function.

- G slope of the real best-fit straight line.

### Integral nonlinearity (INL)

Measured after trimming the offset and gain errors to zero.

The integral nonlinearity for an output code i, INL (i), is the difference between the measured input voltage at which the transition occurs and the ideal value of this transition.

The ADC integral nonlinearity INL is the maximum value of all [INL(i)].

# Differential nonlinearity (DNL)

Measured after trimming the offset and gain errors to zero.

The differential nonlinearity for an output code i, DNL(i), is the difference between the measured step size of code i and the ideal LSB step size.

The ADC differential nonlinearity DNL is the maximum value of all |DNL(i)|.

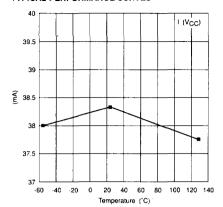

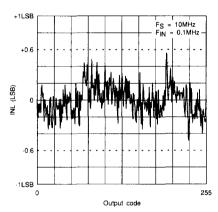

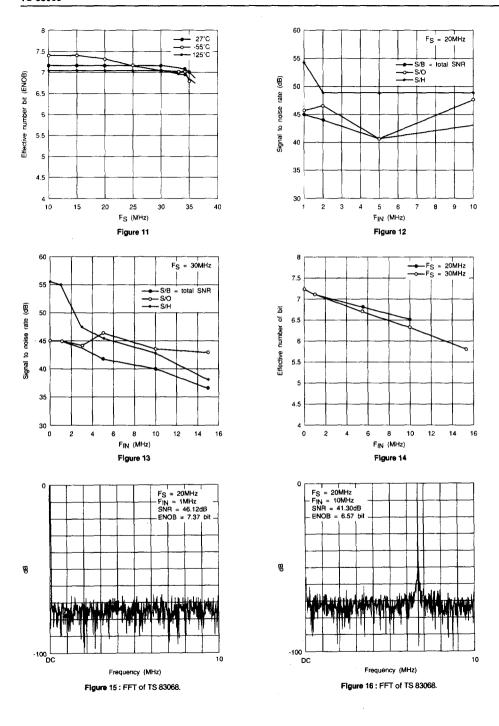

### TYPICAL PERFORMANCE CURVES

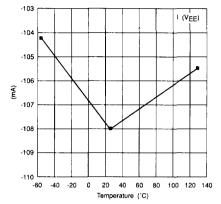

Figure 5 : Supply currents.

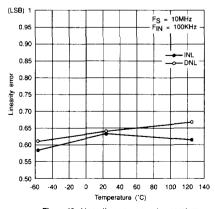

Figure 7: Integral non linearity.

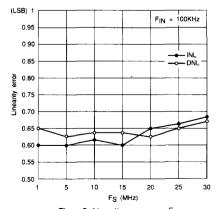

Figure 9: Linearity error versus Fg.

Figure 6: Supply currents.

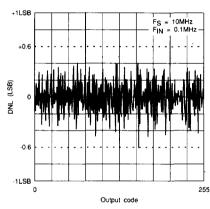

Figure 8: Differential non linearity.

Figure 10: Linearity error versus temperature.

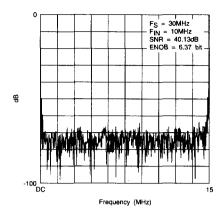

Figure 17: FFT of TS 83068.

Figure 18: Reconstructed waveform 30 MHz sampling rate, 15 MHz input frequency.

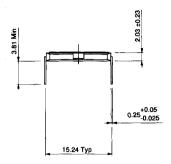

# MECHANICAL PACKAGE DATA

# DIL 24 - Ceramic package (Dimensions in mm)

30.48 ±0.30

# **DIE MECHANICAL INFORMATION: JTS 83068**

Pad layout: V676

Pad size: 0.120 x 0.120 mm Die size: 5.470 x 4.250 mm Die thickness : 380 μm

Metallization : Al-Ni-Au (Back side) Al-Si-Ti (Front side)

Passivation: Nitride

Revision: A

Qualification lot package: DIL 24

Back side potential: VEE

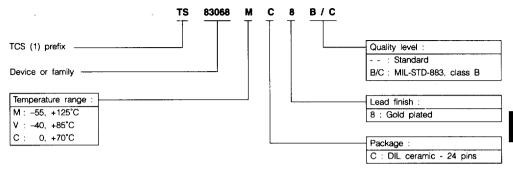

### ORDERING INFORMATION

# Packaged device

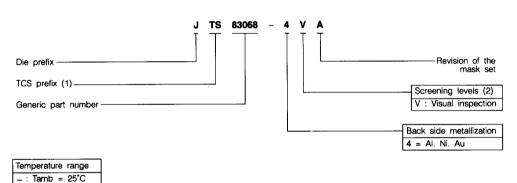

### Die form

Note 1: THOMSON-CSF SEMICONDUCTEURS SPECIFIQUES.

Note 2: For availability of the different available versions contact your TCS sales office.