# F1600 65,536 x 1-Bit Static RAM

Memory and High Speed Logic.

### Description

The F1600 is a 65,536-bit fully static asynchronous random access memory, organized as 65,536 words by 1-bit, using high-performance CMOS technology. The F1600 is based on an advanced isoplanar oxide isolation process: fully-implanted CMOS technology with sub-2 micron design rules and high-performance tantalum silicide gate electrodes. The high-density NMOS memory array and the CMOS peripheral circuits provide fast access time plus low active and standby power.

- Single +5V Operation (±10%)

- . Fully Static: No Clock or Timing Strobe Required

- Fast Access Time: 45 ns/55 ns/70 ns (Maximum)

- Low Power Dissipation:

- 70 mA Maximum (Active)

- 20 mA Maximum (Standby TTL Input Levels)

- 5 mA Maximum (Standby CMOS Input Levels)

- Directly TTL Compatible All Inputs and Outputs

- Separate Data Input and Three-State Output

- Available in a 22-Pin DIP or LCC

- Polyimide Die Coat for Alpha Immunity

### Pin Names

| A <sub>0</sub> -A <sub>15</sub> | Address Inputs |

|---------------------------------|----------------|

| Ē                               | Chip Enable    |

| W                               | Write Enable   |

| D                               | Data Input     |

| Q                               | Data Output    |

| Vcc                             | Power (5.0 V)  |

| GND                             | Ground (0 V)   |

### **Logic Symbol**

# Connection Diagrams 22-Pin DIP (Top View)

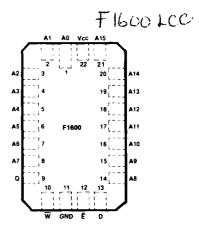

### 22-Pin LCC (Top View)

### **Absolute Maximum Ratings**

Voltage on Any Input or Output Pin With Respect to GND Storage Temperature Operating Temperature Power Dissipation

- 2.0 V to 7.0 V -55° C to +150° C 0° C to +70° C 1.0 W

Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### Recommended Operating Conditions: $T_C = 0^{\circ} C$ to $+70^{\circ} C$

| Symbol          | Characteristic     | Min.  | Тур. | Max. | Unit |

|-----------------|--------------------|-------|------|------|------|

| V <sub>CC</sub> | Supply Voltage     | 4.5   | 5.0  | 5.5  | >    |

| VIH             | Input HIGH Voltage | 2.2   |      | 6.0  | ٧    |

| $V_{IL}$        | Input LOW Voltage  | -0.5* |      | 0.8  | ٧    |

All voltages are referenced to GND pin = 0 V.

\*The device will withstand undershoots to -3.0 V of 20 ns duration. This is guaranteed by bench simulation in a DC mode, not 100% tested.

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high-impedance circuit.

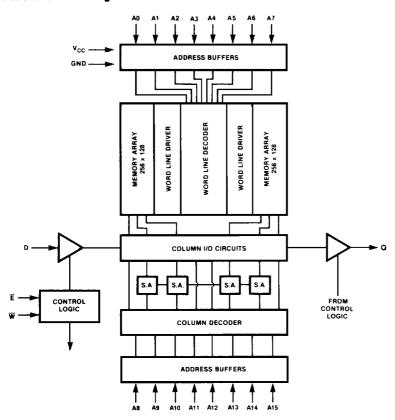

### **Functional Block Diagram**

DC Operating Characteristics:  $T_{\mbox{\scriptsize C}}=0^{\circ}\,\mbox{\scriptsize C}$  to  $+70^{\circ}\,\mbox{\scriptsize C},\,\mbox{\scriptsize V}_{\mbox{\scriptsize CC}}=5.0\mbox{\scriptsize V}\pm10\%$

|                  |                                              | _   | F1600-4 | 5    |     | F1600-5 | 5    | 1   | F1600-7 | 0    |      |                                                                      |

|------------------|----------------------------------------------|-----|---------|------|-----|---------|------|-----|---------|------|------|----------------------------------------------------------------------|

| Symbol           | Characteristic                               | Min | Typ.    | Max  | Min | Тур.    | Max  | Min | Тур.    | Max  | Unit | Condition                                                            |

| I <sub>IN</sub>  | Input Leakage<br>Current (All inputs)        | ·   |         | ±2   |     |         | ±2   |     |         | ±2   | μА   | V <sub>CC</sub> = 5.5 V,<br>V <sub>IN</sub> = 0 V to V <sub>CC</sub> |

| lout             | Output Leakage<br>Current (on Q)             | ·   |         | ±2   |     |         | ±2   |     |         | ±2   | μΑ   | E = V <sub>IH</sub><br>V <sub>OUT</sub> = 0 V to V <sub>CC</sub>     |

| loc <sub>1</sub> | Operating Power<br>Supply Current            | 1   | 40      | 70   |     | 40      | 70   |     | 40      | 70   | mA   | E = V <sub>IL</sub> ,<br>Output Open                                 |

| ICC2             | Dynamic Operating<br>Supply Current          |     | 40      | 70   |     | 40      | 70   |     | 40      | 70   | mA   | Min. Read Cycle Time<br>Duty Cycle = 100%<br>Output Open             |

| I <sub>SB1</sub> | Standby Supply<br>Current                    | -   | 5       | 20   |     | 5       | 20   |     | 5       | 20   | mA   | E ≥ V <sub>IH</sub> ,<br>see note 1                                  |

| I <sub>SB2</sub> | Full Standby<br>Supply Current               |     | 0.02    | 5.0  |     | 0.02    | 5.0  |     | 0.02    | 5.0  | mA   | see note 2                                                           |

| los              | Output Current<br>Short Circuit<br>to Ground |     |         | -125 |     |         | -125 |     |         | -125 | mA   | V <sub>CC</sub> = 5.5 V<br>Duration not to<br>Exceed 1 Second        |

| VoL              | Output LOW Voltage                           |     |         | 0.4  |     |         | 0.4  |     |         | 0.4  | ٧    | loL = 8.0 mA                                                         |

| VoH              | Output HIGH Voltage                          | 2.4 |         |      | 2.4 |         | Ī    | 2.4 |         |      | V    | loн = -4.0 mA                                                        |

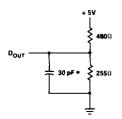

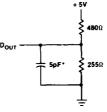

### AC Test Conditions<sup>3</sup>

| Input Pulse Levels                             |

|------------------------------------------------|

| Input Rise and Fall Times 5 ns                 |

| Input and Output Timing Reference Levels 1.5 V |

| Output Load See Figures 1 and 2                |

## $\textbf{Capacitance}^{4}\, T_{\mbox{\scriptsize C}} = +25^{o}\, \mbox{\scriptsize C}, \, f = 1.0 \; \mbox{\scriptsize MHz}$

| Symbol           | Parameter          | Max. | Units | Conditions            |

|------------------|--------------------|------|-------|-----------------------|

| CiN              | Input Capacitance  | 5    | pF    | V <sub>IN</sub> = 0 V |

| C <sub>OUT</sub> | Output Capacitance | 6    | рF    | $V_{OUT} = 0 V$       |

Effective capacitance calculated from the equation

$C = \frac{\triangle Q}{\triangle V}$  where  $\triangle V = 3 V$ .

### Figure 1 Output Load

Notes on page 5-9

### **Truth Table**

| Mode    | Ē | W D Q |   | Power Level |         |

|---------|---|-------|---|-------------|---------|

| Standby | Н | Х     | Х | HIGH Z      | Standby |

| Read    | L | Н     | х | О           | Active  |

| Write   | L | L     | D | HIGH Z      | Active  |

HIGH Z = High impedance

D = Valid data bit

X = Don't care

Figure 2 Output Load (for tenaz, telax, twlaz, twhax)

\*Including scope and jig.

AC Operating Conditions and Characteristics: Read Cycle  $T_C = 0^{\circ}$  C to  $+70^{\circ}$  C,  $V_{CC} = 5.0$ V  $\pm 10\%$

|     | Symbol             |                 |                                                                    | F160 | 0-45 | F160 | 0-55 | F160 | 0-70 |      |       |

|-----|--------------------|-----------------|--------------------------------------------------------------------|------|------|------|------|------|------|------|-------|

| No. | Standard           | Alternate       | Parameter                                                          |      | Max  | Min  | Max  | Min  | Max  | Unit | Notes |

| 1   | tavav              | t <sub>RC</sub> | Address Valid to Address Valid (Read Cycle Time)                   | 45   |      | 55   |      | 70   |      | ns   | 5,6,9 |

| 2   | tavov              | taa             | Address Valid to Output Valid (Address Access Time)                |      | 45   |      | 55   |      | 70   | ns   | 5     |

| 3   | taxox              | tон             | Address Invalid to Output Invalid (Output Hold Time)               | 5    |      | 5    |      | 5    |      | ns   |       |

| 4   | teleh              | tRC             | Chip Enable LOW to Chip Enable<br>HIGH (Read Cycle Time)           | 45   |      | 55   |      | 70   |      | ns   | 6,9   |

| 5   | tELQV              | tacs            | Chip Enable LOW to Output Valid (Chip Enable Access Time)          |      | 45   |      | 55   |      | 70   | ns   | 6     |

| 6   | tELQX              | tız             | Chip Enable LOW to Output Invaild (Chip Enable to Output Active)   | 0    |      | 0    |      | 0    |      | ns   | 4     |

| 7   | t <sub>EHQ</sub> z | tHZ             | Chip Enable HIGH to Output High Z (Chip Disable to Output Disable) | 0    | 20   | 0    | 25   | 0    | 30   | ns   | 4, 10 |

| 8   | telicch.           | tpu             | Chip Enable LOW to Power Up                                        | 0    |      | 0    |      | 0    |      | ns   | 4     |

| 9   | <b>t</b> EHICCL    | tpD             | Chip Enable HIGH to Power Down                                     |      | 40   |      | 40   |      | 40   | ns   | 4     |

Notes on page 5-9

### **Timing Waveforms**

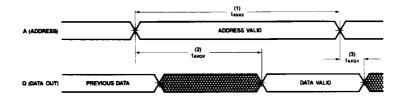

Read Cycle 1 (Where  $\overline{E}$  is active prior to address change.  $\overline{W} = HIGH$ )

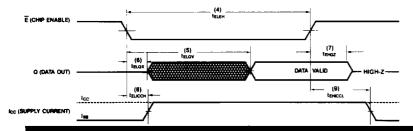

Read Cycle 2 (Where address is valid prior to  $\overline{E}$  becoming active.  $\overline{W} = HIGH$ )

### F1600

AC Operating Conditions and Characteristics: Write Cycle 1 T  $_{C}$  = 0° C to +70° C, V  $_{CC}$  = 5.0V  $\pm 10\%$

|     | Syn      | nbol            |                                                                       | F160 | 00-45 | F160 | 0-55 | F16 | 00-70 |      |       |

|-----|----------|-----------------|-----------------------------------------------------------------------|------|-------|------|------|-----|-------|------|-------|

| No. | Standard | Alternate       | Parameter                                                             | Min  | Max   | Min  | Max  | Min | Max   | Unit | Notes |

| 10  | tavav    | twc             | Address Valid to Address Valid (Write Cycle Time)                     | 45   |       | 55   |      | 70  |       | ns   | 7,8,9 |

| 11  | telWH    | t <sub>CW</sub> | Chip Enable to Write HIGH<br>(Chip Enable to End of Write)            | 40   |       | 45   |      | 55  |       | ns   | 11    |

| 12  | tavwh    | taw             | Address Valid to Write HIGH<br>(Address Setup to End of Write)        | 40   |       | 45   |      | 55  |       | ns   | 11    |

| 13  | twhax    | twn             | Write HIGH to Address Don't Care<br>(Address Hold After End of Write) | 0    |       | 0    |      | 0   |       | ns   | 11    |

| 14  | tww      | twp             | Write LOW to Write HIGH<br>(Write Pulse Width)                        | 20   |       | 25   |      | 40  |       | ns   | 11    |

| 15  | tavwl    | tas             | Address Valid to Write LOW (Address Setup to Beginning of Write)      | 5    | 0     | 5    |      | 5   |       | ns   | 11    |

| 16  | tоvwн    | tow             | Data Valid to Write HIGH<br>(Data Setup to End of Write)              | 15   | •••   | 20   |      | 30  |       | ns   | 11    |

| 17  | twnox    | tрн             | Write HIGH to Data Don't Care<br>(Data Hold After End of Write)       | 0    |       | 0    |      | 0   |       | ns   | 11    |

| 18  | twLqz    | twz             | Write LOW to Output High Z<br>(Write Enable to Output Disable)        | 0    | 20    | 0    | 25   | 0   | 30    | ns   | 4, 10 |

| 19  | twnax    | tow             | Write HIGH to Output Don't Care<br>(Output Active After End of Write) | 0    |       | 0    |      | 0   |       | ns   | 4     |

Notes on page 5-9

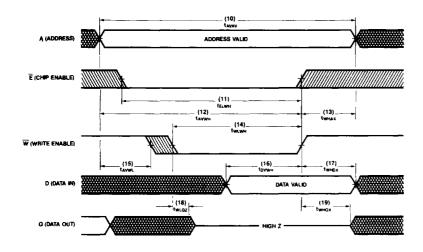

Write Cycle 1 ( $\overline{W}$  controlled, where  $\tilde{E}$  is active prior to  $\overline{W}$  becoming active.)

### F1600

AC Operating Conditions and Characteristics: Write Cycle 2 T  $_{C}$  = 0  $^{\circ}$  C to +70  $^{\circ}$  C, V  $_{CC}$  = 5.0V  $\pm 10\%$

|     | Syn                                  | Symbol                                                      |                                                                          | F1600-45 |         | F1600-55 |         | F1600-70 |     |      |       |

|-----|--------------------------------------|-------------------------------------------------------------|--------------------------------------------------------------------------|----------|---------|----------|---------|----------|-----|------|-------|

| No. | Standard Alternate                   |                                                             | Parameter                                                                |          | Min Max |          | Min Max |          | Max | Unit | Notes |

| 20  | tavel                                | tas                                                         | Address Valid to Chip Enable LOW (Address Set Up)                        |          |         | 0        |         | 0        |     | ns   |       |

| 21  | telen .                              | t <sub>cw</sub>                                             | Chip Enable LOW to Chip Enable<br>HIGH (Write Cycle Time)                | 45       |         | 55       |         | 70       |     | ns   | 11    |

| 22  | tehax                                | twn                                                         | Chip Enable HIGH to Address Don't Care (Address Hold After End of Write) |          |         | 0        |         | 0        |     | ns   |       |

| 23  | taveh                                | taw                                                         | Address Valid to Chip Enable HIGH (Address Setup to End of Write)        | 40       |         | 45       |         | 55       |     | ns   |       |

| 24  | terwh                                | telwh twp Chip Enable LOW to Write HIGH (Write Pulse Width) |                                                                          | 30       |         | 35       |         | 40       |     | ns   | 11    |

| 25  | toveh                                | tow                                                         | Data Valid to Chip Enable HIGH (Data Setup to End of Write)              |          |         | 20       |         | 30       |     | ns   |       |

| 26  | tehdx to Data Don't Care (Data Hold) |                                                             | 0                                                                        |          | 0       |          | 0       |          | ns  | i    |       |

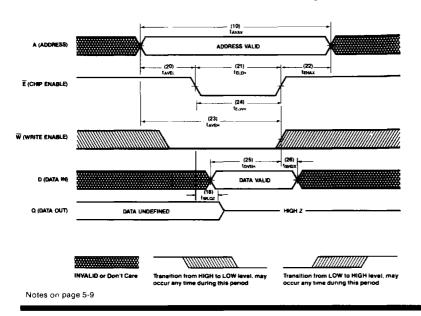

Write Cycle 2 ( $\overline{E}$  controlled, where  $\overline{W}$  is active prior to  $\overline{E}$  becoming active. See Note 9.)

5-8

### F1600

#### Notes

- This parameter is measured with E HIGH (chip deselected) and inputs at valid TTL levels.

- This parameter is measured with input levels either ≥ V<sub>CC</sub> = 0.2 V or ≤ 0.2 V, including E which must be ≥ V<sub>CC</sub> = 0.2 V. This condition results in significant reduction in current in the input buffer circuitry and consequently a lower overall current level.

- Operation to specifications guaranteed 2.0 ms after VCC applied.

- 4. This parameter is sampled and not 100% tested.

- 5. Read Cycle 1 assumes that Chip Enable (E) occurs before the addresses are valid. Timing considerations are referenced to the edges of Address Valid.

- 6. Read Cycle 2 assumes that Address Valid occurs prior to Chip Enable (E). Timing considerations are referenced to the edges of Chip Enable.

- 7. Since a write cycle can only occur during intervals where both E and W are LOW, Write Cycle 1 assumes that W is the latter of the two signals to go LOW (active) and is also the first of the two signals to go HIGH (inactive). Consequently, timing considerations are referenced to the edges of W rather than E.

- Write Cycle 2 assumes that, of the two control signals, E and W. E is the latter of the two to go LOW (active) and is also the first of the two to go HIGH (inactive).

Consequently, timing considerations are referenced to the edges of E rather than W.

- 9. All READ and WRITE cycle timings are referenced from the last bit to become valid address to the first transitioning address.

- Transition to high impedance state is measured ±500 mV from steady state voltage with specified loading in Figure 2. This parameter is sampled not 100% tested.

- 11. Since Write Enable (W) is gated internally with Chip Enable (E), the value of W during periods where E is HIGH is irrelevant (i.e., don't care). Thus, whenever W transitions to the LOW state prior to E, all timing references will be to the falling edge of E rather than W. Similarly, whenever E transitions to the HIGH state prior to W, all timing references will be to the rising edge of E rather than W.

- 2. Input pulse levels 0 to 3.0 Volts.

- 13. Input rise and fall times are assumed to be 5 ns. Timing measurement reference levels are 1.5 Volts.

- 4 Rise and fall times should not exceed 45 ns.

### **Ordering Information**

| Part Number | Access Time | Temperature Range | Package               | Order Code |

|-------------|-------------|-------------------|-----------------------|------------|

| F1600-45    | 45 ns       | 0°C to + 70°C     | Side-brazed           | 1600DC45   |

| F1600-45    | 45 ns       | 0°C to + 70°C     | Leadless Chip Carrier | 1600LC45   |

| F1600-45    | 45 ns       | 0°C to + 70°C     | Plastic DIP           | 1600PC45   |

| F1600-55    | 55 ns       | 0°C to + 70°C     | Side-brazed           | 1600DC55   |

| F1600-55    | 55 ns       | 0°C to + 70°C     | Leadless Chip Carrier | 1600LC55   |

| F1600-55    | 55 ns       | 0°C to + 70°C     | Plastic DIP           | 1600PC55   |

| F1600-70    | 70 ns       | 0°C to + 70°C     | Side-brazed           | 1600DC70   |

| F1600-70    | 70 ns       | 0°C to + 70°C     | Leadless Chip Carrier | 1600LC70   |

| F1600-70    | 70 ns       | 0°C to + 70°C     | Plastic DIP           | 1600PC70   |