# 3.3V LVDS 1:4 Clock Fanout Buffer AK8181G

### Features

- Four differential 3.3V LVDS outputs

- Selectable two LVCMOS/LVTTL clock inputs

**Preliminary**

- Clock output frequency up to 650MHz

- Translates LVCMOS/LVTTL input signals to LVDS levels

- Output skew : 30ps (maximum)

- Part-to-part skew : 500ps (maximum)

- Propagation delay : 2.2ns (maximum)

- Additive phase jitter(RMS): 0.1ps (typical)

- Operating Temperature Range: -40 to +85°C

- Package: 20-pin TSSOP (Pb free)

- Pin compatible with ICS8545I

### Description

The AK8181G is a member of AKM's LVDS clock fanout buffer family designed for telecom, networking and computer applications, requiring a range of clocks with high performance and low skew. The AK8181G distributes 4 buffered clocks.

AK8181G are derived from AKM's long-termexperienced clock device technology, and enable clock output to perform low skew. The AK8181G is available in a 20-pin TSSOP package.

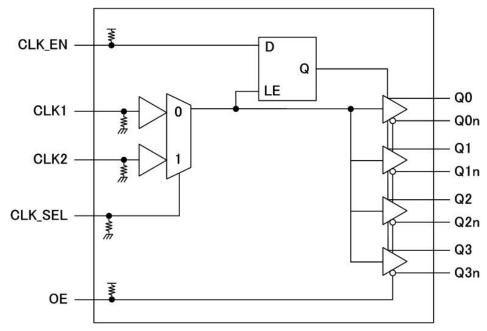

### **Block Diagram**

### **Pin Descriptions**

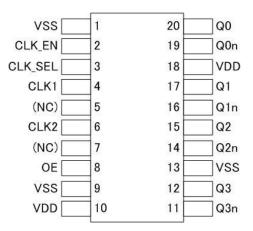

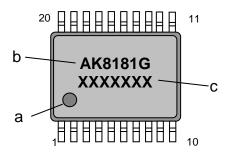

Package: 20-Pin TSSOP(Top View)

| Pin No. | Pin Name | Pin<br>Type | Pullup<br>down | Description                                                                                                                                                                                                                           |

|---------|----------|-------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | VSS      | PWR         |                | Negative power supply                                                                                                                                                                                                                 |

| 2       | CLK_EN   | IN          | Pull up        | Synchronizing clock output enable (LVCMOS/LVTTL)<br>Pin is connected to VDD by internal resistor. (typ. $51k\Omega$ )<br>High (Open): clock outputs follow clock input.<br>Low: Q outputs are forced low, Qn outputs are forced high. |

| 3       | CLK_SEL  | IN          | Pull down      | CLK Select Input (LVCMOS/LVTTL)<br>Pin is connected to VSS by internal resistor. (typ. $51k\Omega$ )<br>High: selects CLK2 input<br>Low (Open): selects CLK1 input                                                                    |

| 4       | CLK1     | IN          | Pull down      | Single-ended clock input Pin is connected to VSS by internal resistor. (typ. $51k\Omega$ )                                                                                                                                            |

| 5       | NC       |             |                | No connect                                                                                                                                                                                                                            |

| 6       | CLK2     | IN          | Pull down      | Single-ended clock input<br>Pin is connected to VSS by internal resistor. (typ. $51k\Omega$ )                                                                                                                                         |

| 7       | NC       |             |                | No connect                                                                                                                                                                                                                            |

| 8       | OE       | IN          | Pull up        | Output enable. Controls enabling and disabling of outputs Q0, Q0n through Q3, Q3n.<br>Pin is connected to VDD by internal resistor. (typ. $51k\Omega$ )                                                                               |

| 9       | VSS      | PWR         |                | Negative power supply                                                                                                                                                                                                                 |

| 10      | VDD      | PWR         |                | Positive power supply                                                                                                                                                                                                                 |

| 11, 12  | Q3n, Q3  | OUT         |                | Differential clock output (LVDS)                                                                                                                                                                                                      |

| 13      | VSS      | PWR         |                | Negative power supply                                                                                                                                                                                                                 |

| 14, 15  | Q2n, Q2  | OUT         |                | Differential clock output (LVDS)                                                                                                                                                                                                      |

| 16, 17  | Q1n, Q1  | OUT         |                | Differential clock output (LVDS)                                                                                                                                                                                                      |

| 18      | VDD      | PWR         |                | Positive power supply                                                                                                                                                                                                                 |

| 19, 20  | Q0n, Q0  | OUT         |                | Differential clock output (LVDS)                                                                                                                                                                                                      |

### **Ordering Information**

| Part Number | Marking | Shipping<br>Packaging | Package      | Temperature<br>Range |

|-------------|---------|-----------------------|--------------|----------------------|

| AK8181G     | AK8181G | Tape and Reel         | 20-pin TSSOP | -40 to 85 °C         |

### **Absolute Maximum Rating**

| Over operating free-air temperature | range unless | otherwise noted <sup>(1)</sup> |

|-------------------------------------|--------------|--------------------------------|

|                                     | range unless |                                |

| Items                                    | Symbol          | Ratings            | Unit |

|------------------------------------------|-----------------|--------------------|------|

| Supply voltage                           | VDD             | -0.3 to 4.6        | V    |

| Input voltage                            | Vin             | VSS-0.5 to VDD+0.5 | V    |

| Input current (any pins except supplies) | I <sub>IN</sub> | ±10                | mA   |

| Storage temperature                      | Tstg            | -55 to 150         | °C   |

Note

(1) Stress beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated under "Recommended Operating Conditions" is not implied. Exposure to absolute-maximum-rating conditions for extended periods may affect device reliability. Electrical parameters are guaranteed only over the recommended operating temperature range.

(2) VSS=0V

### **ESD Sensitive Device**

This device is manufactured on a CMOS process, therefore, generically susceptible to damage by excessive static voltage. Failure to observe proper handling and installation procedures can cause damage. AKM recommends that this device is handled with appropriate precautions.

#### **Recommended Operation Conditions**

| Parameter                     | Symbol | Conditions | Min   | Тур | Max   | Unit |

|-------------------------------|--------|------------|-------|-----|-------|------|

| Operating temperature         | Та     |            | -40   |     | 85    | °C   |

| Supply voltage <sup>(1)</sup> | VDD    | VDD±5%     | 3.135 | 3.3 | 3.465 | V    |

(1) Power of 3.3V requires to be supplied from a single source. A decoupling capacitor of  $0.1 \mu F$  for power supply line should be located close to each VDD pin.

### **Pin Characteristics**

| Parameter               | Symbol          | Conditions | Min | Тур | Max | Unit |

|-------------------------|-----------------|------------|-----|-----|-----|------|

| Input Capacitance       | CIN             |            |     | 4   |     | pF   |

| Input Pullup Resistor   | R <sub>PU</sub> |            |     | 51  |     | kΩ   |

| Input Pulldown Resistor | R <sub>PD</sub> |            |     | 51  |     | kΩ   |

### **Power Supply Characteristics**

| Parameter            | Symbol          | Conditions          | Min | Тур | Max | Unit |

|----------------------|-----------------|---------------------|-----|-----|-----|------|

|                      |                 | CLK1 = input 650MHz |     |     | 47  | mA   |

|                      | I <sub>DD</sub> | CLK2 = open         |     |     | 47  | ША   |

| Power Supply Current |                 | CLK1 = open         |     |     | 47  |      |

|                      |                 | CLK2 = input 650MHz |     |     | 47  | mA   |

## DC Characteristics (LVCMOS/LVTTL)

All specifications at VDD=3.3V±5%, Ta: -40 to +85°C, unless otherwise noted

| Param                | eter                    | Symbol          | Conditions             | MIN  | ТҮР | МАХ     | Unit |

|----------------------|-------------------------|-----------------|------------------------|------|-----|---------|------|

| Input High Voltage   |                         | V <sub>IH</sub> |                        | 2.0  |     | VDD+0.3 | V    |

|                      | CLK1, CLK2              |                 |                        | -0.3 |     | 1.3     | V    |

| Input Low Voltage    | CLK_SEL, OE,<br>CLK_EN, | V <sub>IL</sub> |                        | -0.3 |     | 0.8     | V    |

| In put Lliph Current | CLK_SEL                 |                 | Vin=VDD=3.465V         |      |     | 150     | μA   |

| Input High Current   | CLK_EN, OE              | Ι <sub>Η</sub>  | Vin=VDD=3.465V         |      |     | 5       | μA   |

|                      | CLK_SEL                 |                 | Vin=VSS,<br>VDD=3.465V | -5   |     |         | μΑ   |

| Input Low Current    | CLK_EN, OE              | ΙL              | Vin=VSS,<br>VDD=3.465V | -150 |     |         | μA   |

### **DC** Characteristics (Differential)

All specifications at VDD=3.3V±5%, VSS=0V, Ta: -40 to +85°C, unless otherwise noted

| Parameter                                 | Symbol          | Conditions | MIN   | ТҮР  | MAX   | Unit |

|-------------------------------------------|-----------------|------------|-------|------|-------|------|

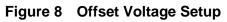

| Differential Output Voltage               | V <sub>OD</sub> |            | 200   | 280  | 360   | mV   |

| V <sub>OD</sub> Magnitude Change          | $\Delta V_{OD}$ |            |       |      | 40    | mV   |

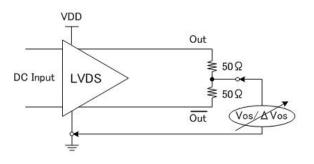

| Offset Voltage                            | Vos             |            | 1.125 | 1.25 | 1.375 | V    |

| Vos Magnitude Change                      | ΔVos            |            |       | 5    | 25    | mV   |

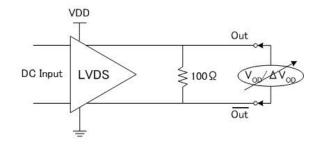

| High Impedance Leakage Current            | I <sub>OZ</sub> | OE = Low   | -10   |      | +10   | μA   |

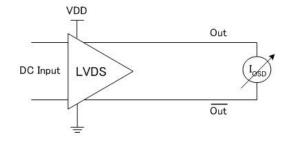

| Differential Output Short Circuit Current | IOSD            |            |       | -3.5 | -5    | mA   |

| Output Voltage High                       | V <sub>OH</sub> |            |       | 1.34 | 1.6   | V    |

| Output Voltage Low                        | V <sub>OL</sub> |            | 0.9   | 1.06 |       | V    |

### **AC Characteristics**

All specifications at VDD=3.3V±5%, VSS=0V, Ta: -40 to +85°C, unless otherwise noted

| Parameter                                  | Symbol                          | Conditions                | MIN | TYP | MAX | Unit |

|--------------------------------------------|---------------------------------|---------------------------|-----|-----|-----|------|

| Output Frequency                           | f <sub>OUT</sub>                |                           |     |     | 650 | MHz  |

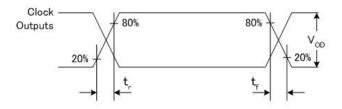

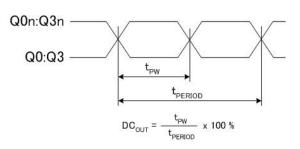

| Propagation Delay <sup>(1)</sup>           | t <sub>PD</sub>                 |                           | 0.7 |     | 2.2 | ns   |

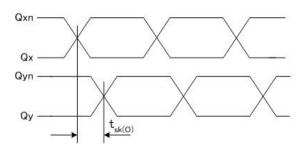

| Output Skew (2) (3)                        | t <sub>sk(O)</sub>              |                           |     |     | 30  | ps   |

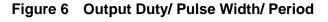

| Part-to-Part Skew (3) (4)                  | t <sub>skPP</sub>               |                           |     |     | 500 | ps   |

| Buffer Additive Jitter, RMS <sup>(5)</sup> | t <sub>jit</sub>                | 156.25MHz (12kHz – 20MHz) |     | 0.1 |     | ps   |

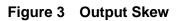

| Output Rise/Fall Time (5)                  | t <sub>r</sub> , t <sub>f</sub> | 20% to 80% @50MHz         | 100 |     | 500 | ps   |

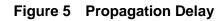

| Output Duty Cycle                          | DC <sub>OUT</sub>               |                           | 45  |     | 55  | %    |

All parameters measured at f  $\leq$  650MHz unless noted otherwise.

The cycle to cycle jitter on the input will equal the jitter on the output. The part does not add jitter.

(1) Measured from VDD/2 of the input to the differential output crossing point.

(2) Defined as skew between outputs at the same supply voltage and with equal load conditions.

(3) This parameter is defined in accordance with JEDEC Standard 65.

(4) Defined as skew between outputs on different devices operating at the same supply voltages and with equal load conditions. Using the same type of inputs on each device, the outputs are measured at the differential cross points.

(5) Design value.

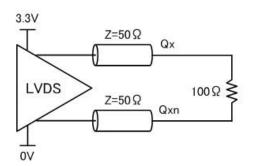

Figure 1 3.3V Output Load Test Circuit

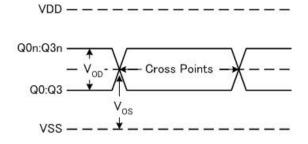

Figure 2 Differential Output Level

Figure 4 Output Rise/Fall Time

Figure 7 Part-to-Part Skew

Figure 9 Differential Output Voltage Setup

Figure 10 High Impedance Leakage Current Setup

### **Function Table**

The following table shows the inputs/outputs clock state configured through the control pins.

|    |            | Inputs     |                 | Outputs       |                |  |

|----|------------|------------|-----------------|---------------|----------------|--|

| OE | CLK_EN     | CLK_SEL    | Selected Source | Q0:Q3         | Q0n:Q3n        |  |

| 1  | 0          | 0 (Open)   | CLK1            | Disabled: Low | Disabled: High |  |

| 1  | 0          | 1          | CLK2            | Disabled: Low | Disabled: High |  |

| 1  | 1 (Open)   | 0 (Open)   | CLK1            | Enabled       | Enabled        |  |

| 1  | 1 (Open)   | 1          | CLK2            | Enabled       | Enabled        |  |

| 0  | Don't care | Don't care |                 | Hi-Z          | Hi-Z           |  |

#### **Table 1: Control Input Function Table**

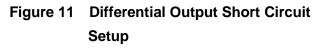

After CLK\_EN switches, the clock outputs are disabled or enabled following a rising and falling input clock edge as shown in Figure 12. In the active mode, the state of the outputs are a function of the CLK1 and CLK2 inputs as described in Table 2.

### Figure 12 CLK\_EN Timing Diagram

| Inputs | Outputs |           |  |  |

|--------|---------|-----------|--|--|

| CLK1/2 | Q0 : Q3 | Q0n : Q3n |  |  |

| 0      | Low     | High      |  |  |

| 1      | High    | Low       |  |  |

#### **Table 2: Clock Input Function Table**

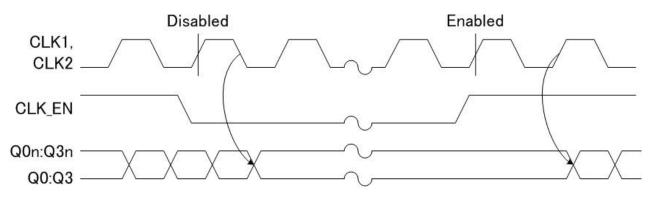

### **Package Information**

### • Mechanical data : 20pin TSSOP

• Marking

- a: #1 Pin Index

- b: Part number

- c: Date code (7 digits)

### • RoHS Compliance

All integrated circuits form Asahi Kasei Microdevices Corporation (AKM) assembled in "lead-free" packages\* are fully compliant with RoHS.

(\*) RoHS compliant products from AKM are identified with "Pb free" letter indication on product label posted on the anti-shield bag and boxes.

#### IMPORTANT NOTICE

- These products and their specifications are subject to change without notice. When you consider any use or application of these products, please make inquiries the sales office of Asahi Kasei Microdevices Corporation (AKM) or authorized distributors as to current status of the products.

- Descriptions of external circuits, application circuits, software and other related information contained in this document are provided only to illustrate the operation and application examples of the semiconductor products. You are fully responsible for the incorporation of these external circuits, application circuits, software and other related information in the design of your equipments. AKM assumes no responsibility for any losses incurred by you or third parties arising from the use of these information herein. AKM assumes no liability for infringement of any patent, intellectual property, or other rights in the application or use of such information contained herein.

- Any export of these products, or devices or systems containing them, may require an export license or other official

approval under the law and regulations of the country of export pertaining to customs and tariffs, currency exchange,

or strategic materials.

- AKM products are neither intended nor authorized for use as critical components<sub>Note1</sub> in any safety, life support, or other hazard related device or system<sub>Note2</sub>, and AKM assumes no responsibility for such use, except for the use approved with the express written consent by Representative Director of AKM. As used here:

- Note1) A critical component is one whose failure to function or perform may reasonably be expected to result, whether directly or indirectly, in the loss of the safety or effectiveness of the device or system containing it, and which must therefore meet very high standards of performance and reliability.

- Note2) A hazard related device or system is one designed or intended for life support or maintenance of safety or for applications in medicine, aerospace, nuclear energy, or other fields, in which its failure to function or perform may reasonably be expected to result in loss of life or in significant injury or damage to person or property.

- It is the responsibility of the buyer or distributor of AKM products, who distributes, disposes of, or otherwise places the product with a third party, to notify such third party in advance of the above content and conditions, and the buyer or distributor agrees to assume any and all responsibility and liability for and hold AKM harmless from any and all claims arising from the use of said product in the absence of such notification.