## SEMICONDUCTORS

SP8655 200MHz ÷ 32 SP8657 200MHz ÷ 20 SP8659 200MHz ÷ 16

The SP8655, 57 and 59 are low power emitter coupled logic counters with open collector outputs capable of driving TTL or CMOS. They are available in two temperature ranges: -  $55^{\circ}$ C to +125°C (A grade) and -30°C to +70°C (B grade). It has internally biased inputs.

## **FEATURES**

- AC Coupled Inputs

- Low Power Consumption

- Open Collector Output CMOS and TTL Compatible

### **QUICK REFERENCE DATA**

- Supply Voltage: 5.0V

- Power Consumption: 50mW

- Temperature Range:

-55°C to +125°C (A Grade)

-30°C to +70°C (B Grade)

## **ORDERING INFORMATION**

See page 3-120

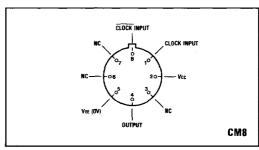

Fig.1 Pin connections - bottom view

### **ABSOLUTE MAXIMUM RATINGS**

Supply voltage 8V

Open collector output voltage 12V

Storage temperature range 4-55 °C to +150 °C

Max. junction temperature +175 °C

Max. clock I/P voltage 2.5V p-p

Output sink current 10mA

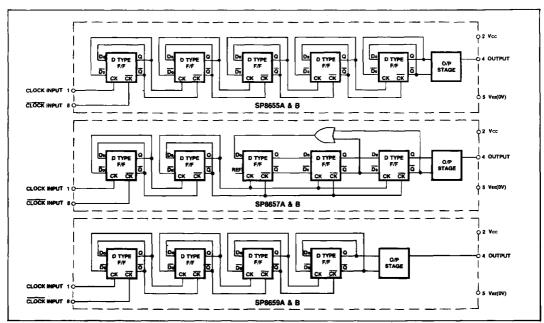

Fig.2 Functional diagram

## **ELECTRICAL CHARACTERISTICS**

Supply voltage: Vcc = 5.0V ± 0.25V VEE = 0V

Temperature: A grade T<sub>amb</sub> = -55°C to +125°C

B grade T<sub>amb</sub> = -30°C to +70°C

| Characteristic                     | Symbol      | Value |      | Units  | Conditions                    |

|------------------------------------|-------------|-------|------|--------|-------------------------------|

|                                    |             | Min.  | Max. | Office | 00/10/10/10                   |

| Maximum frequency (sinewave input) | fmax        | 200   |      | MHz    | Input =400 - 800mV            |

| Minimum frequency (sinewave input) | fmin        |       | 40   | MHz    | Input =400 - 800mV            |

| Power supply current               | IEE         | l     | 13   | mΑ     | Vcc = 5.25V                   |

| Output high voltage                | <b>V</b> oн | 7.5   |      | l v    | Vcc= 5V Note 4                |

| , , ,                              |             |       |      |        | Pin 4 = $1.5k\Omega$ to $10V$ |

| Output low voltage                 | Vol         |       | 400  | mV     | V∞ = 5V                       |

|                                    |             | l .   |      |        | Pin 4 = $1.5k\Omega$ to $10V$ |

#### NOTES

- 1. Unless otherwise stated the electrical characteristics are guaranteed over specified supply, frequency and temperature range.

- 2. The dynamic test circuit is shown in Fig.5.

- 3. Above characteristics are not tested at 25°C (tested at low and high temperature only).

- Open collector output not to be used above 15MHz. Cload ≤5pF.

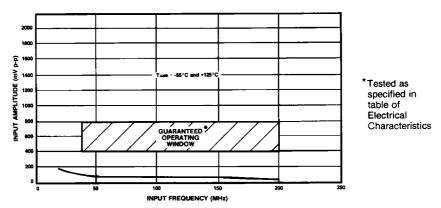

Fig.3 Typical input characteristics

#### **OPERATING NOTES**

- The clock inputs (pin 1 and 8) should be capacitively coupled to the signal source. When driven single-ended, the input signal path is completed by connecting a capacitor from the unused input to ground.

- 2. In the absence of a signal the devices will self-oscillate. This can be prevented by connecting a 39k resistor from either input to ground. If the device is driven single ended, it is recommended that the pulldown resistor be connected to the decoupled unused input. There will be a loss in sensitivity of approximately 200mV.

- 3. The device will operate down to DC but the input slew rate must be better than 100V/µs.

- 4. The open collector output will drive 3 TTL loads, and thus requires a suitable resistor to Vcc to maintain noise

- immunity. In order to ensure noise immunity on transitions, this resistor should not exceed 4.7k. For interfacing to CMOS, the open collector may be restored to a +10V line via a 3.3k resistor. The output sink current must not exceed 10mA, and the use of too low a value of resistor may lead to a loss of noise immunity, especially at low temperatures.

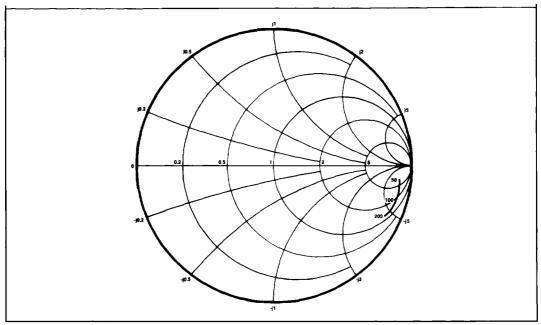

- 5. Input impedance is a function of frequency. See Fig. 4.

6. The rise time of the open collector output waveform is directly proportional to the load capacitance and load resistor value. Therefore the load capacitance should be minimised and the load resistor kept to a minimum compatible with system power requirements. In the test configuration of Fig. 5, the output rise time is approximately 20ns and fall time is typically 10ns.

Fig.4 Typical input impedance. Test conditions: supply voltage 5.0V, ambient temperature 25° C, frequencies in MHz, impedances normalised to 50 ohms.

Fig.5 Test circuit

Fig.6 Typical application showing interfacing

Fig.7 Interfacing to TTL. Load not to exceed 3 TTL unit loads.

# **ORDERING INFORMATION**

SP8655 A CM SP8655 B CM SP8655 AB CM SP8655 AC CM SP8655 AC SP8657 A CM SP8657 A CM SP8657 AB CM SP8657 AC CM SP8659 A CM SP8659 B CM SP8659 AB CM SP8659 AC CM SP8659 ABSS2 CM