# 8-bit Proprietary Microcontrollers

**CMOS**

# F<sup>2</sup>MC-8FX MB95110H Series

## MB95117H/F118HS/F118TS/F118HW/F118TW/ MB95FV100B-103

#### **■ DESCRIPTION**

The MB95110H series is general-purpose, single-chip microcontrollers. In addition to a compact instruction set, the microcontrollers contain a variety of peripheral functions.

Note: F2MC is the abbreviation of FUJITSU Flexible Microcontroller.

#### **■ FEATURES**

• F2MC-8FX CPU core

Instruction set optimized for controllers

- · Multiplication and division instructions

- 16-bit arithmetic operations

- · Bit test branch instruction

- Bit manipulation instructions etc.

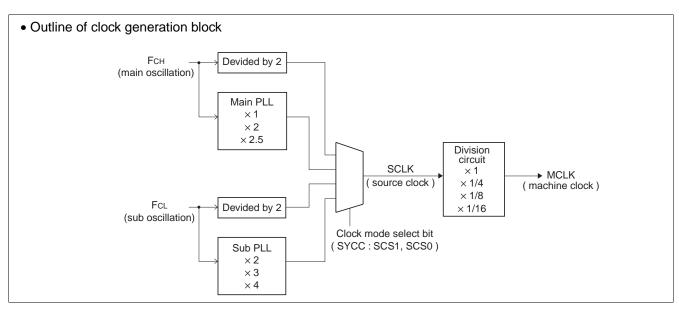

- Clock

- Main clock

- Main PLL clock

- Sub clock (for dual clock product)

- Sub PLL clock (for dual clock product)

- Timer

- 8/16-bit compound timer × 2 channels

- 8/16-bit PPG × 2 channels

- 16-bit PPG

- Timebase timer

- Watch prescaler (for dual clock product)

(Continued)

Be sure to refer to the "Check Sheet" for the latest cautions on development.

"Check Sheet" is seen at the following support page

URL: http://www.fujitsu.com/global/services/microelectronics/product/micom/support/index.html

"Check Sheet" lists the minimal requirement items to be checked to prevent problems beforehand in system development.

#### (Continued)

- LIN-UART

- Full duplex double buffer

- Clock asynchronous or clock synchronous serial data transfer capable

- UART/SIO

- Full duplex double buffer

- Clock asynchronous or clock synchronous serial data transfer capable

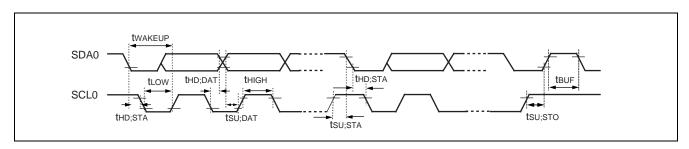

- I2C\*

Built-in wake-up function

- External interrupt

- Interrupt by edge detection (rising, falling, or both edges can be selected)

- Can be used to recover from low-power consumption (standby) modes.

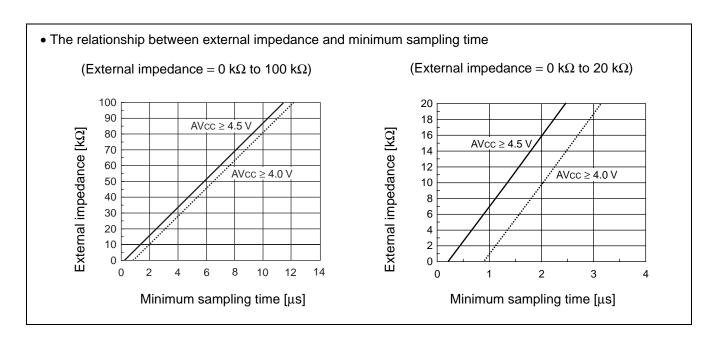

- 8/10-bit A/D converter

8-bit or 10-bit resolution can be selected

- Low-power consumption (standby) mode

- Stop mode

- Sleep mode

- Watch mode (for dual clock product)

- Timebase timer mode

- I/O port

- The number of maximum ports

- Single clock product : 39 ports

- Dual clock product : 37 ports

- Configuration

- General-purpose I/O ports (N-ch open drain) : 2 ports

- General-purpose I/O ports (CMOS) : Single clock product : 37 ports

Dual clock product : 35 ports

- \*: Purchase of Fujitsu I<sup>2</sup>C components conveys a license under the Philips I<sup>2</sup>C Patent Rights to use, these components in an I<sup>2</sup>C system provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

### **■ PRODUCT LINEUP**

|                      | Part number                 | MB95117H                                                                                                                                                                                                                                                                                                                                                                   | MB95F118HS                                                                                                                                                                           | MB95F118TS | MD05E449HW | MB95F118TW   |  |  |

|----------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------------|--------------|--|--|

| Par                  | rameter                     | WID95117H WID95F116H                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                      | MD93F11613 | MB95F118HW | MIDAZELIOLAA |  |  |

| Тур                  | pe                          | MASK ROM product                                                                                                                                                                                                                                                                                                                                                           | Flash memory product                                                                                                                                                                 |            |            |              |  |  |

| RO                   | M capacity                  | 48 Kbytes                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                      | 60 K       | bytes      |              |  |  |

| RAI                  | M capacity                  | 2 Kbytes                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                      | 2 Kb       | ytes       |              |  |  |

| Res                  | set output                  |                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                      | Yes        |            |              |  |  |

| Option*2             | Clock system                | Selectable<br>single/dual<br>clock*1                                                                                                                                                                                                                                                                                                                                       | Single                                                                                                                                                                               | clock      | Dual       | clock        |  |  |

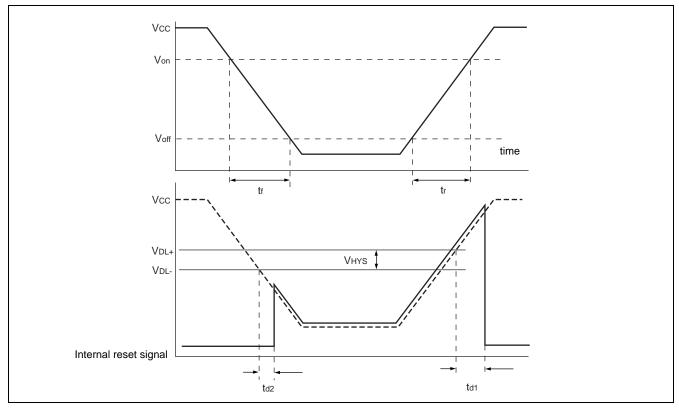

| ဝီ                   | Low voltage detection reset | Yes / No                                                                                                                                                                                                                                                                                                                                                                   | No                                                                                                                                                                                   | Yes        | No         | Yes          |  |  |

| CPU functions        |                             | Number of basic instructions: 136Instruction bit length: 8 bitsInstruction length: 1 to 3 bytesData bit length: 1, 8, and 16 bitsMinimum instruction execution time: 0.1 μs (at machine clock frequency 10 MHz)Interrupt processing time: 0.9 μs (at machine clock frequency 10 MHz)                                                                                       |                                                                                                                                                                                      |            |            |              |  |  |

|                      | General purpose I/O ports   |                                                                                                                                                                                                                                                                                                                                                                            | <ul> <li>Single clock product : 39 ports (N-ch open drain : 2 ports, CMOS : 37 ports)</li> <li>Dual clock product : 37 ports (N-ch open drain : 2 ports, CMOS : 35 ports)</li> </ul> |            |            |              |  |  |

|                      | Timebase timer              | Interrupt cycle: 0.5 ms, 2.1 ms, 8.2 ms, 32.8 ms (at main oscillation clock 4 MHz)                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                      |            |            |              |  |  |

|                      | Watchdog timer              | Reset generated cycle At main oscillation clock 10 MHz : Min 105 ms At sub oscillation clock 32.768 kHz (for dual clock product) : Min 250 ms                                                                                                                                                                                                                              |                                                                                                                                                                                      |            |            |              |  |  |

| ions                 | Wild register               | Capable of repla                                                                                                                                                                                                                                                                                                                                                           | cing 3 bytes of R                                                                                                                                                                    | OM data    |            |              |  |  |

| Peripheral functions | I <sup>2</sup> C            | Master/slave sending and receiving Bus error function and arbitration function Detecting transmitting direction function Start condition repeated generation and detection functions Built-in wake-up function                                                                                                                                                             |                                                                                                                                                                                      |            |            |              |  |  |

| Δ.                   | UART/SIO                    | Data transfer capable in UART/SIO Full duplex double buffer, variable data length (5/6/7/8-bit), built-in baud rate generator Transfer rate: 2400 bps to 1250000 bps (at machine clock 10 MHz) NRZ type transfer format, error detected function LSB-first or MSB-first can be selected. Clock synchronous (SIO) or clock asynchronous (UART) serial data transfer capable |                                                                                                                                                                                      |            |            |              |  |  |

#### (Continued)

|                                                                                                                                                                                                                                              | Part number                              | MB95117H                                                                                                                                              | MB95F118HS                                                                                                                                                                                                                                      | MB95F118TS        | MB95F118HW   | MB95F118TW                   |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------|------------------------------|--|--|--|

| Parameter                                                                                                                                                                                                                                    |                                          | MIDSSIILU                                                                                                                                             | MIDAOLIIOUO                                                                                                                                                                                                                                     | MIDARLIGIR        | MIDAOLIIOUAA | MIDAOLIIOIAA                 |  |  |  |

|                                                                                                                                                                                                                                              | LIN-UART                                 | Full duplex doub<br>Capable of seria                                                                                                                  | Dedicated reload timer allowing a wide range of communication speeds to be set. Full duplex double buffer. Capable of serial data transfer synchronous or asynchronous to clock signal. LIN functions available as the LIN master or LIN slave. |                   |              |                              |  |  |  |

|                                                                                                                                                                                                                                              | 8/10-bit A/D converter (8 channels)      | 8-bit or 10-bit re                                                                                                                                    | solution can be s                                                                                                                                                                                                                               | elected.          |              |                              |  |  |  |

| ctions                                                                                                                                                                                                                                       | 8/16-bit compound timer (2 channels)     | × 1 channel". Built-in timer fun waveform outpu                                                                                                       | Built-in timer function, PWC function, PWM function, capture function, and square                                                                                                                                                               |                   |              |                              |  |  |  |

| Peripheral functions                                                                                                                                                                                                                         | 16-bit PPG                               | PWM mode or one-shot mode can be selected. Counter operating clock : 8 selectable clock sources Support for external trigger start                    |                                                                                                                                                                                                                                                 |                   |              |                              |  |  |  |

| Peri                                                                                                                                                                                                                                         | 8/16-bit PPG<br>(2 channels)             | Each channel of the PPG can be used as "8-bit PPG × 2 channels" or "16-bit PPG × 1 channel".  Counter operating clock: Eight selectable clock sources |                                                                                                                                                                                                                                                 |                   |              |                              |  |  |  |

| Watch counter (for dual clock product)  Count clock: 4 selectable clock sources (125 ms, 250 m Counter value can be set from 0 to 63. (Capable of counter value can be set from 0 to 63. (Capable of counter value can be set from 0 to 63.) |                                          |                                                                                                                                                       |                                                                                                                                                                                                                                                 |                   |              | of counting for 1minute when |  |  |  |

|                                                                                                                                                                                                                                              | Watch prescaler (for dual clock product) | 4 selectable interval times (125 ms, 250 ms, 500 ms, or 1 s)                                                                                          |                                                                                                                                                                                                                                                 |                   |              |                              |  |  |  |

| External interrupt (12 channels) Interrupt by edge detection (rising, falling, or both edges can be selected (12 channels) Can be used to recover from standby modes.                                                                        |                                          |                                                                                                                                                       |                                                                                                                                                                                                                                                 |                   |              | lected.)                     |  |  |  |

| Sta                                                                                                                                                                                                                                          | ndby mode                                | Sleep, stop, wat                                                                                                                                      | ch (for dual clock                                                                                                                                                                                                                              | product), and til | mebase timer |                              |  |  |  |

The evaluation device of this product is MB95FV100B-103. MCU board is MB2146-303.

Note: Part number of the evaluation device in MB95110H series is MB95FV100B-103. When using it, the MCU board (MB2146-303) is required.

<sup>\*1 :</sup> Specify clock mode when ordering MASK ROM.

<sup>\*2 :</sup> For details of option, refer to "■ MASK OPTION".

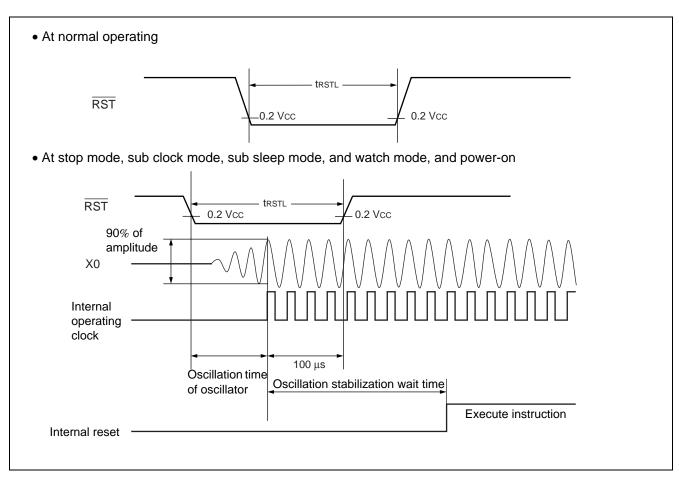

#### **■ OSCILLATION STABILIZATION WAIT TIME**

The initial value of the main clock oscillation stabilization wait time is fixed to the maximum value. The maximum value is shown as follows.

| Oscillation stabilization wait time | Remarks                                           |  |  |

|-------------------------------------|---------------------------------------------------|--|--|

| (2 <sup>14</sup> –2) /Fcн           | Approx. 4.10 ms (at main oscillation clock 4 MHz) |  |  |

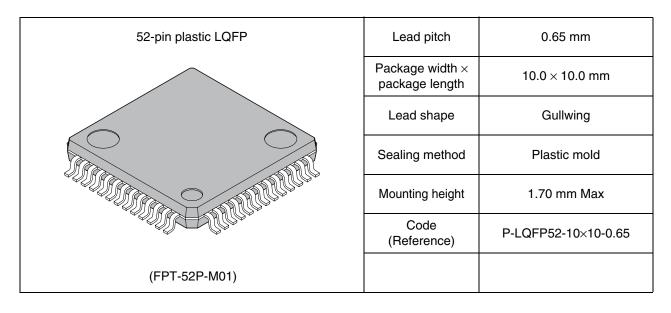

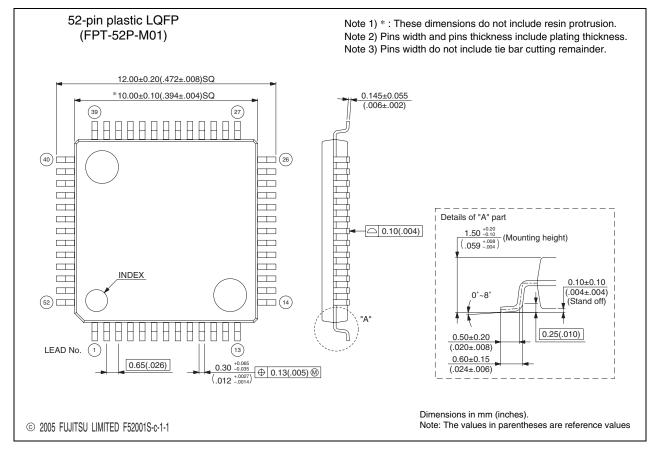

#### ■ PACKAGES AND CORRESPONDING PRODUCTS

| Part number Package | MB95117H | MB95F118HS<br>MB95F118TS | MB95F118HW<br>MB95F118TW | MB95FV100B-103 |

|---------------------|----------|--------------------------|--------------------------|----------------|

| FPT-52P-M01         | 0        | 0                        | 0                        | ×              |

| BGA-224P-M08        | ×        | ×                        | ×                        | 0              |

○ : Available× : Unavailable

#### ■ DIFFERENCES AMONG PRODUCTS AND NOTES ON SELECTING PRODUCTS

#### Notes on Using Evaluation Products

The Evaluation product has not only the functions of the MB95110H series but also those of other products to support software development for multiple series and models of the F²MC-8FX family. The I/O addresses for peripheral resources not used by the MB95110H series are therefore access-barred. Read/write access to these access-barred addresses may cause peripheral resources supposed to be unused to operate, resulting in unexpected malfunctions of hardware or software.

Particularly, do not use word access to odd numbered byte address in the prohibited areas (If these access are used, the address may be read or write unexpectedly).

Note that the values read from barred addresses are different between the Evaluation product and the Flash memory or MASK ROM product. Therefore, the data must not be used for software processing.

The Evaluation product do not support the functions of some bits in single-byte registers. Read/write access to these bits does not cause hardware malfunctions. Since the Evaluation, Flash memory, and MASK ROM products are designed to behave completely the same way in terms of hardware and software.

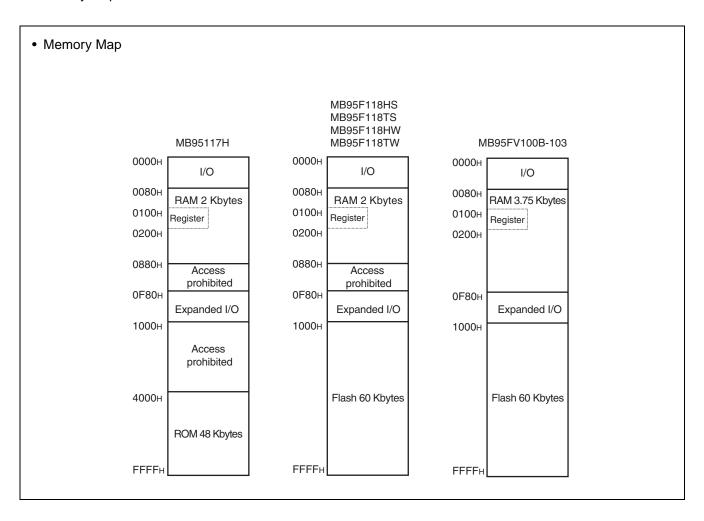

#### Difference of Memory Spaces

If the amount of memory on the Evaluation product is different from that of the Flash memory or MASK ROM product, carefully check the difference in the amount of memory from the model to be actually used when developing software.

For details of memory space, refer to "■ CPU CORE".

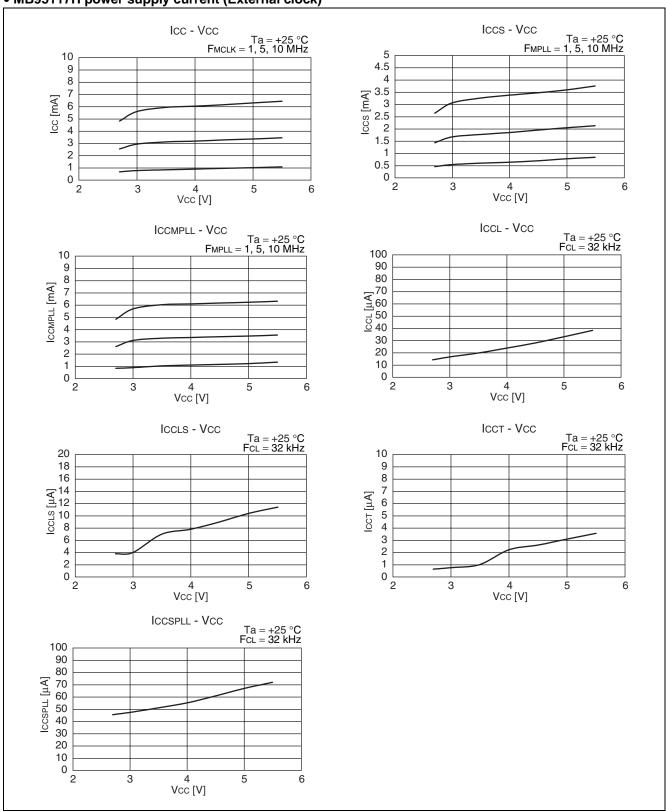

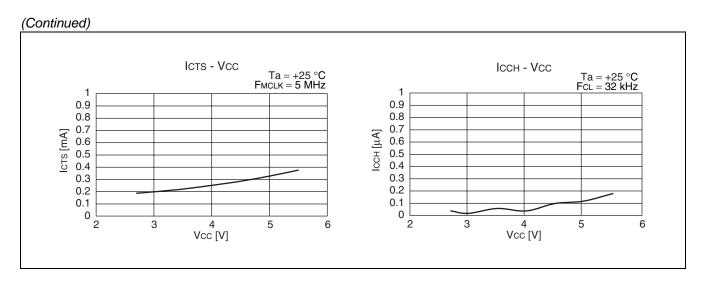

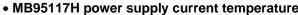

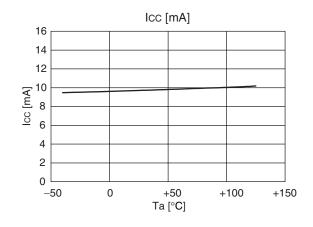

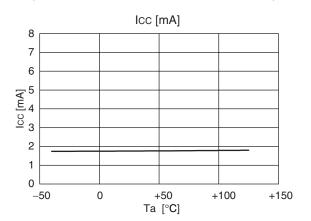

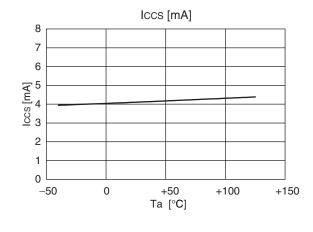

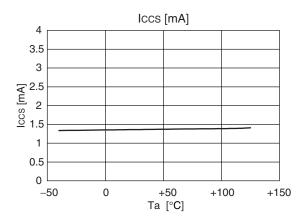

#### Current Consumption

- The current consumption of Flash memory product is typically greater than for MASK ROM product.

- For details of current consumption, refer to "■ ELECTRICAL CHARACTERISTICS".

#### Package

For details of information on each package, refer to "■ PACKAGE AND CORRESPONDING PRODUCTS" and "■ PACKAGE DIMENSIONS".

#### Operating Voltage

The operating voltage are different among the Evaluation, Flash memory, and MASK ROM products.

For details of operating voltage, refer to "■ ELECTRICAL CHARACTERISTICS"

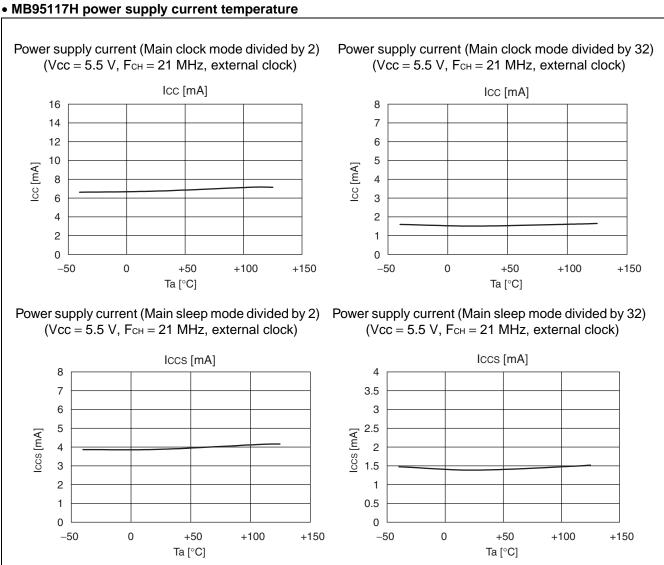

#### • Difference between RST and MOD Pins

The input type of RST and MOD pins is CMOS inputs on the Flash memory product.

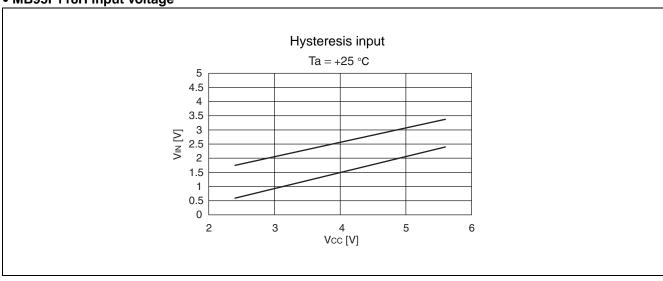

The  $\overline{RST}$  and MOD pins are hysteresis inputs on the MASK ROM product. A pull-down resistor is provided for the MOD pin of the MASK ROM product.

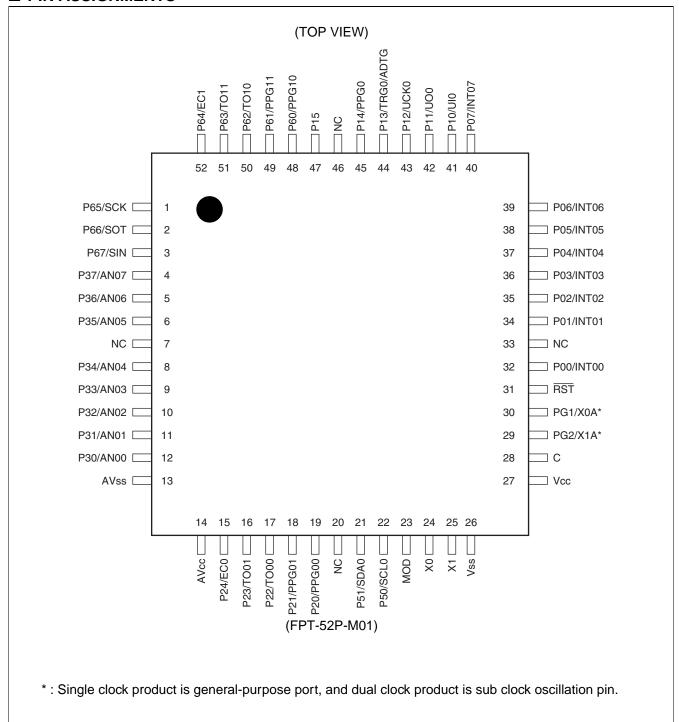

#### **■ PIN ASSIGNMENTS**

### **■ PIN DESCRIPTION**

| Pin no. | Pin name  | I/O<br>Circuit<br>type* | Function                                                                                                             |                           |

|---------|-----------|-------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------|

| 1       | P65/SCK   | К                       | General-purpose I/O port. The pin is shared with LIN-UART clock I/O.                                                 |                           |

| 2       | P66/SOT   |                         | General-purpose I/O port. The pin is shared with LIN-UART data output.                                               |                           |

| 3       | P67/SIN   | L                       | General-purpose I/O port. The pin is shared with LIN-UART data input.                                                |                           |

| 4       | P37/AN07  |                         |                                                                                                                      |                           |

| 5       | P36/AN06  |                         |                                                                                                                      |                           |

| 6       | P35/AN05  |                         |                                                                                                                      |                           |

| 8       | P34/AN04  | J                       | General-purpose I/O port.                                                                                            |                           |

| 9       | P33/AN03  |                         | The pins are shared with A/D converter analog input.                                                                 |                           |

| 10      | P32/AN02  |                         |                                                                                                                      |                           |

| 11      | P31/AN01  |                         |                                                                                                                      |                           |

| 12      | P30/AN00  |                         |                                                                                                                      |                           |

| 13      | AVss      | _                       | A/D converter power supply pin (GND)                                                                                 |                           |

| 14      | AVcc      | _                       | A/D converter power supply pin                                                                                       |                           |

| 15      | P24/EC0   |                         | General-purpose I/O port. The pin is shared with 8/16-bit compound timer ch.0 clock input.                           |                           |

| 16      | P23/TO01  | -<br>Н                  | Н                                                                                                                    | General-purpose I/O port. |

| 17      | P22/TO00  |                         |                                                                                                                      | 1 H                       |

| 18      | P21/PPG01 |                         | General-purpose I/O port.                                                                                            |                           |

| 19      | P20/PPG00 |                         | The pins are shared with 8/16-bit PPG ch.0 output.                                                                   |                           |

| 21      | P51/SDA0  | ı                       | General-purpose I/O port.<br>The pin is shared with I <sup>2</sup> C ch.0 data I/O.                                  |                           |

| 22      | P50/SCL0  | '                       | General-purpose I/O port. The pin is shared with I <sup>2</sup> C ch.0 clock I/O.                                    |                           |

| 23      | MOD       | В                       | Operating mode designation pin                                                                                       |                           |

| 24      | X0        | Α                       | Main clock oscillation input pin                                                                                     |                           |

| 25      | X1        | _ ^                     | Main clock oscillation I/O pin                                                                                       |                           |

| 26      | Vss       | _                       | Power supply pin (GND)                                                                                               |                           |

| 27      | Vcc       | _                       | Power supply pin                                                                                                     |                           |

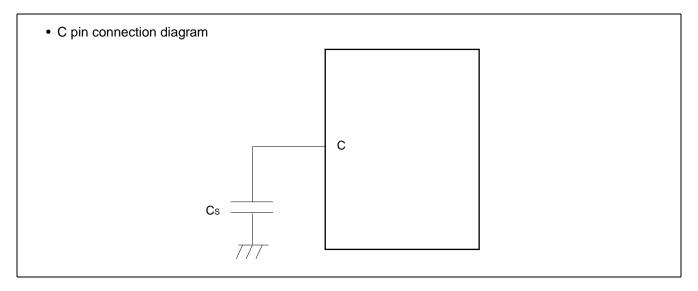

| 28      | С         | _                       | Capacitor connection pin                                                                                             |                           |

| 29      | PG2/X1A   | H/A                     | Single clock product is general-purpose port (PG2).  Dual clock product is sub clock I/O oscillation pin (32 kHz).   |                           |

| 30      | PG1/X0A   | 11/7                    | Single clock product is general-purpose port (PG1).  Dual clock product is sub clock input oscillation pin (32 kHz). |                           |

| 31      | RST       | B'                      | Reset pin                                                                                                            |                           |

| Pin no.       | Pin name          | I/O<br>Circuit<br>type* | Function                                                                                                            |  |

|---------------|-------------------|-------------------------|---------------------------------------------------------------------------------------------------------------------|--|

| 32            | P00/INT00         |                         |                                                                                                                     |  |

| 34            | P01/INT01         |                         |                                                                                                                     |  |

| 35            | P02/INT02         |                         |                                                                                                                     |  |

| 36            | P03/INT03         | С                       | General-purpose I/O port.                                                                                           |  |

| 37            | P04/INT04         |                         | The pins are shared with external interrupt input. Large current port.                                              |  |

| 38            | P05/INT05         |                         |                                                                                                                     |  |

| 39            | P06/INT06         |                         |                                                                                                                     |  |

| 40            | P07/INT07         |                         |                                                                                                                     |  |

| 41            | P10/UI0           | G                       | General-purpose I/O port. The pin is shared with UART/SIO ch.0 data input.                                          |  |

| 42            | P11/UO0           |                         | General-purpose I/O port. The pin is shared with UART/SIO ch.0 data output.                                         |  |

| 43            | P12/UCK0          |                         | General-purpose I/O port. The pin is shared with UART/SIO ch.0 clock I/O.                                           |  |

| 44            | P13/TRG0/<br>ADTG | н                       | General-purpose I/O port. The pin is shared with 16-bit PPG ch.0 trigger input (TRG0) and A/D trigger input (ADTG). |  |

| 45            | P14/PPG0          |                         | General-purpose I/O port. The pin is shared with 16-bit PPG ch.0 output.                                            |  |

| 47            | P15               |                         | General-purpose I/O port.                                                                                           |  |

| 48            | P60/PPG10         |                         | General-purpose I/O port.                                                                                           |  |

| 49            | P61/PPG11         |                         | The pins are shared with 8/16-bit PPG ch.1 output.                                                                  |  |

| 50            | P62/TO10          | K                       | General-purpose I/O port.                                                                                           |  |

| 51            | P63/TO11          | '`                      | The pins are shared with 8/16-bit compound timer ch.1 output.                                                       |  |

| 52            | P64/EC1           |                         | General-purpose I/O port. The pin is shared with 8/16-bit compound timer ch.1 clock input.                          |  |

| 7, 20, 33, 46 | NC                | _                       | Internal connect pin. Be sure this pin is left open.                                                                |  |

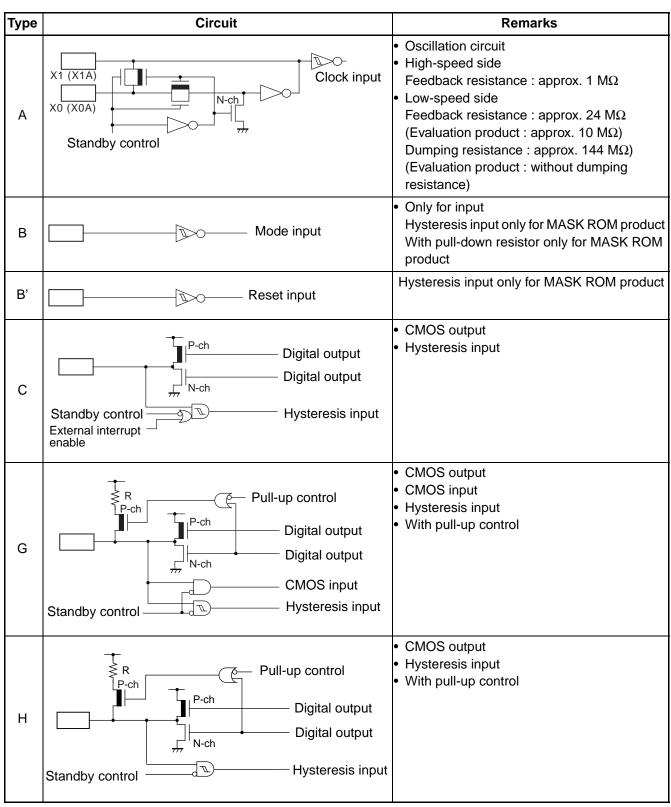

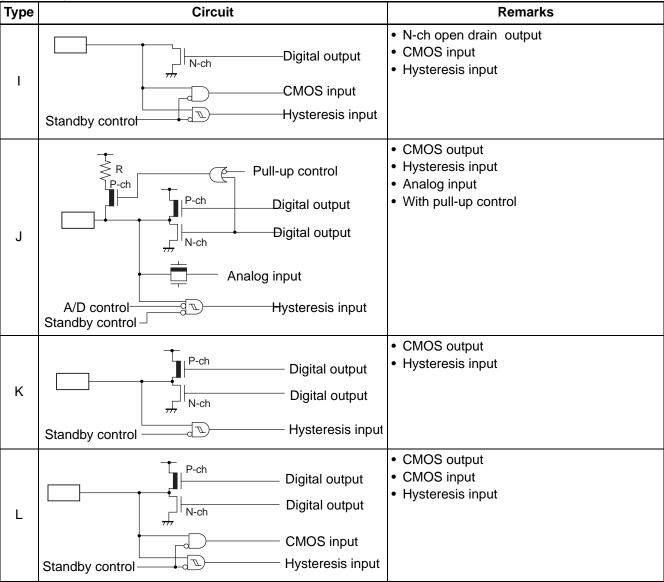

<sup>\*:</sup> For the I/O circuit type, refer to "■ I/O CIRCUIT TYPE"

#### **■ I/O CIRCUIT TYPE**

#### **■ HANDLING DEVICES**

#### • Preventing Latch-up

Care must be taken to ensure that maximum voltage ratings are not exceeded when they are used.

Latch-up may occur on CMOS ICs if voltage higher than  $V_{\text{CC}}$  or lower than  $V_{\text{SS}}$  is applied to input and output pins other than medium- and high-withstand voltage pins or if higher than the rating voltage is applied between  $V_{\text{CC}}$  pin and  $V_{\text{SS}}$  pin.

When latch-up occurs, power supply current increases rapidly and might thermally damage elements.

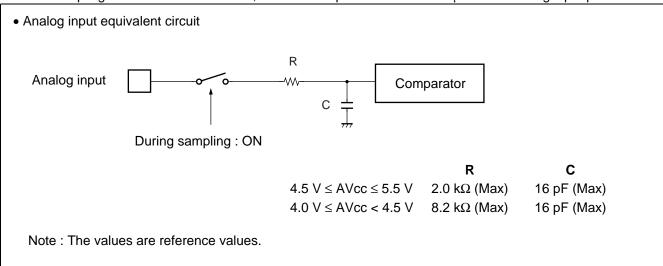

Also, take care to prevent the analog power supply voltage (AVcc) and analog input voltage from exceeding the digital power supply voltage (Vcc) when the analog system power supply is turned on or off.

#### Stable Supply Voltage

Supply voltage should be stabilized.

A sudden change in power-supply voltage may cause a malfunction even within the guaranteed operating range of the Vcc power-supply voltage.

For stabilization, in principle, keep the variation in Vcc ripple (p-p value) in a commercial frequency range (50/60 Hz) not to exceed 10% of the standard Vcc value and suppress the voltage variation so that the transient variation rate does not exceed 0.1 V/ms during a momentary change such as when the power supply is switched.

#### Precautions for Use of External Clock

Even when an external clock is used, oscillation stabilization wait time is required for power-on reset, wake-up from sub clock mode or stop mode.

#### ■ PIN CONNECTION

#### • Treatment of Unused Pin

Leaving unused input pins unconnected can cause abnormal operation or latch-up, leaving to permanent damage. Unused input pins should always be pulled up or down through resistance of at least 2  $k\Omega$ . Any unused input/output pins may be set to output mode and left open, or set to input mode and treated the same as unused input pins. If there is unused output pin, make it open.

#### • Treatment of Power Supply Pins on A/D Converter

Connect to be AVcc = Vcc and AVss = Vss even if the A/D converter is not in use.

Noise riding on the AV $_{\text{CC}}$  pin may cause accuracy degradation. So, connect approx. 0.1  $\mu$ F ceramic capacitor as a bypass capacitor between AV $_{\text{CC}}$  and AV $_{\text{SS}}$  pins in the vicinity of this device.

#### Power Supply Pins

In products with multiple  $V_{\text{CC}}$  or  $V_{\text{SS}}$  pins, the pins of the same potential are internally connected in the device to avoid abnormal operations including latch-up. However, you must connect the pins to external power supply and a ground line to lower the electro-magnetic emission level, to prevent abnormal operation of strobe signals caused by the rise in the ground level, and to conform to the total output current rating.

Moreover, connect the current supply source with the Vcc and Vss pins of this device at the low impedance.

It is also advisable to connect a ceramic bypass capacitor of approximately 0.1  $\mu$ F between Vcc and Vss pins near this device.

#### • Mode Pin (MOD)

Connect the mode pin directly to Vcc or Vss pins.

To prevent the device unintentionally entering test mode due to noise, lay out the printed circuit board so as to minimize the distance from the mode pins to Vcc or Vss pins and to provide a low-impedance connection.

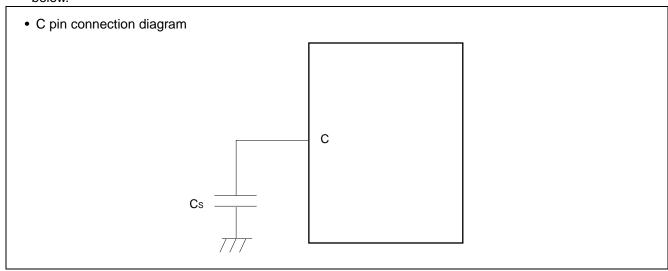

Use a ceramic capacitor or a capacitor with equivalent frequency characteristics. A bypass capacitor of Vcc pin must have a capacitance value higher than Cs. For connection of smoothing capacitor Cs, see the diagram below.

#### • NC Pins

Any pins marked "NC" (not connected) must be left open.

#### • Analog Power Supply

Always set the same potential to AVcc and Vcc. When Vcc > AVcc, the current may flow through the AN00 to AN07 pins.

# ■ PROGRAMMING FLASH MEMORY MICROCONTROLLERS USING PARALLEL PROGRAMMER

• Supported Parallel Programmers and Adapters

| Package     | Applicable adapter model | Parallel programmers                                                                               |

|-------------|--------------------------|----------------------------------------------------------------------------------------------------|

| FPT-52P-M01 | under development        | AF9708 (Ver 02.35G or more)<br>AF9709/B (Ver 02.35G or more)<br>AF9723+AF9834 (Ver 02.08E or more) |

Note: For information on applicable adapter models and parallel programmers, contact the following: Flash Support Group, Inc. TEL: +81-53-428-8380

#### • Sector Configuration

The individual sectors of Flash memory correspond to addresses used for CPU access and programming by the parallel programmer as follows:

| Flash memory       | CPU address          | Programmer address*     |            |

|--------------------|----------------------|-------------------------|------------|

| SA1 (4 Kbytes)     | 1000н                | 71000 <sub>H</sub>      |            |

| <i>5,</i> ( )      | 1FFF <sub>H</sub>    | 71FFF <sub>H</sub>      | \ <u>~</u> |

| SA2 (4Kbytes)      |                      | 72000 <sub>H</sub>      | Lower bank |

| - (                | 2FFF <sub>H</sub>    | 72FFFн                  | ) We       |

| SA3 (4 Kbytes)     | 3000н                | 73000н                  | 1          |

| OAS (4 Royles)     | 3FFF <sub>H</sub>    | 73FFFн                  |            |

| CAA (16 Khytos)    | 4000н                | 74000н                  |            |

| SA4 (16 Kbytes)    | 7FFF <sub>H</sub>    | 77FFFн                  |            |

| 0.45 (4.0 1/1 (+ ) | 8000 <sub>H</sub>    | 78000 <sub>H</sub>      |            |

| SA5 (16 Kbytes)    | BFFF <sub>H</sub>    | 7BFFFн                  |            |

| 0.40 (4.16) (5.5)  | С000н                | 7C000H                  |            |

| SA6 (4 Kbytes)     | CFFFH                | 7CFFFн                  | bank       |

| 0.07 (4.16)        | D000H                | 7D000H                  | Upper bank |

| SA7 (4 Kbytes)     | DFFFH                | 7DFFFн                  | 하          |

|                    |                      | 7E000H                  |            |

| SA8 (4 Kbytes)     | EFFFH                | 7000.                   |            |

|                    | <u>Еггн</u><br>F000н | <u>7ЕFF</u> н<br>7F000н |            |

| SA9 (4 Kbytes)     |                      |                         | 7 }        |

|                    | <u>FFFF</u> H        | <u>7FFFF</u>            |            |

<sup>\*:</sup> Programmer addresses are corresponding to CPU addresses, used when the parallel programmer programs data into Flash memory.

These programmer addresses are used for the parallel programmer to program or erase data in Flash memory.

#### • Programming Method

- 1) Set the type code of the parallel programmer to "17222".

- 2) Load program data to programmer addresses 71000H to 7FFFFH.

- 3) Programmed by parallel programmer

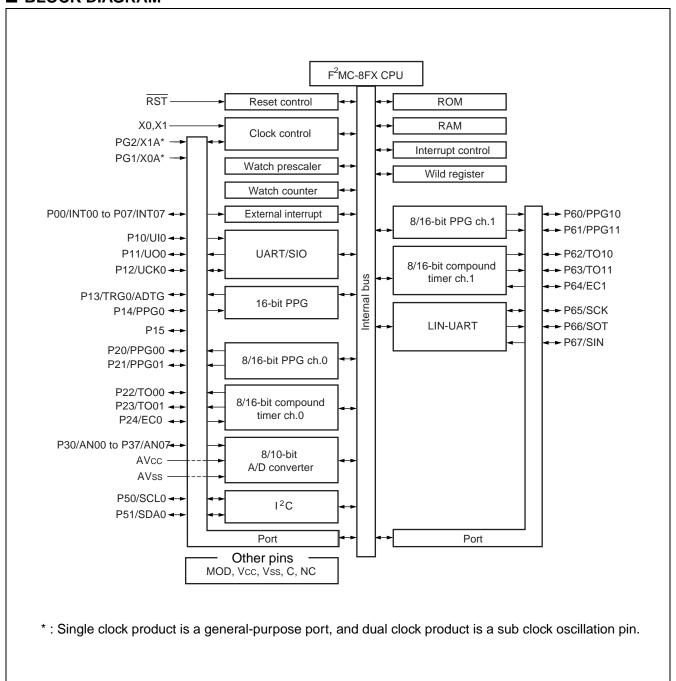

#### **■ BLOCK DIAGRAM**

#### **■ CPU CORE**

#### 1. Memory space

Memory space of the MB95110H series is 64 Kbytes and consists of I/O area, data area, and program area. The memory space includes special-purpose areas such as the general-purpose registers and vector table. Memory map of the MB95110H series is shown below.

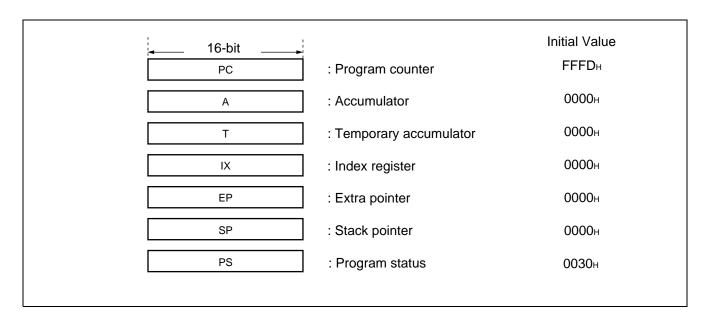

#### 2. Register

The MB95110H series has two types of registers; dedicated registers in the CPU and general-purpose registers in the memory. The dedicated registers are as follows:

Program counter (PC) : A 16-bit register to indicate locations where instructions are stored.

Accumulator (A) : A 16-bit register for temporary storage of arithmetic operations. In the case of

an 8-bit data processing instruction, the lower 1 byte is used.

Temporary accumulator (T) : A 16-bit register which performs arithmetic operations with the accumulator.

In the case of an 8-bit data processing instruction, the lower 1 byte is used.

Index register (IX) : A 16-bit register for index modification.

Extra pointer (EP) : A 16-bit pointer to point to a memory address.

Stack pointer (SP) : A 16-bit register to indicate a stack area.

Program status (PS) : A 16-bit register for storing a register bank pointer, a direct bank pointer, and

a condition code register.

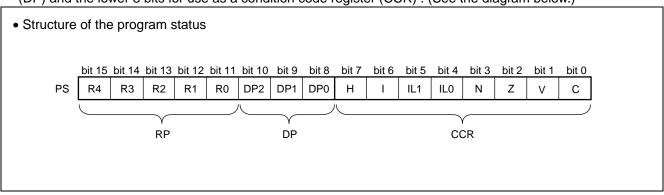

The PS can further be divided into higher 8 bits for use as a register bank pointer (RP) and a direct bank pointer (DP) and the lower 8 bits for use as a condition code register (CCR). (See the diagram below.)

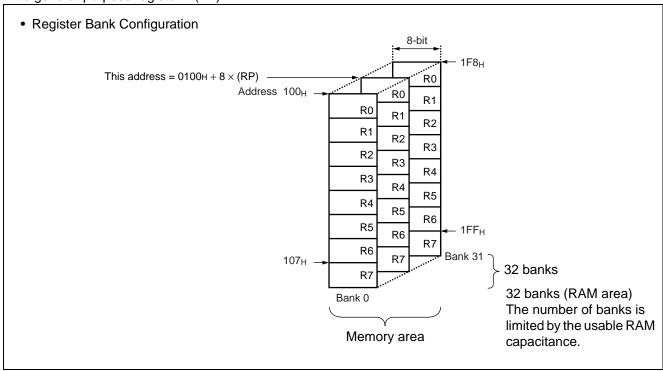

The RP indicates the address of the register bank currently being used. The relationship between the content of RP and the real address conforms to the conversion rule illustrated below:

Rule for Conversion of Actual Addresses in the General-purpose Register Area RP upper OP code lower "0" "1" R4 R3 R2 R1 R0 b2 b0 ¥ ¥ ¥ ¥ ¥ Generated address A<sub>15</sub> A14 A13 A12 A11 A10 Α9 **A8** Α7 A6 Α5 Α4 АЗ A2 Α1 A0

The DP specifies the area for mapping instructions (16 different instructions such as MOV A, dir) using direct addresses to 0080<sub>H</sub> to 00FF<sub>H</sub>.

| Direct bank pointer (DP2 to DP0)        | Specified address area | Mapping area                     |

|-----------------------------------------|------------------------|----------------------------------|

| XXX <sub>B</sub> (no effect to mapping) | 0000н to 007Fн         | 0000н to 007Fн (without mapping) |

| 000 <sub>B</sub> (initial value)        |                        | 0080н to 00FFн (without mapping) |

| 001в                                    |                        | 0100н to 017Fн                   |

| 010в                                    |                        | 0180н to 01FFн                   |

| 011в                                    | 0080н to 00FFн         | 0200н to 027Fн                   |

| 100в                                    | - 0000H 10 00FFH       | 0280н to 02FFн                   |

| 101в                                    |                        | 0300н to 037Fн                   |

| 110в                                    |                        | 0380н to 03FFн                   |

| 111в                                    |                        | 0400н to 047Fн                   |

The CCR consists of the bits indicating arithmetic operation results or transfer data contents and the bits that control CPU operations at interrupt.

H flag : Set to "1" when a carry or a borrow from bit 3 to bit 4 occurs as a result of an arithmetic operation.

Cleared to "0" otherwise. This flag is for decimal adjustment instructions.

I flag : Interrupt is enabled when this flag is set to "1". Interrupt is disabled when this flag is set to "0".

The flag is set to "0" when reset.

IL1, IL0 : Indicates the level of the interrupt currently enabled. Processes an interrupt only if its request level

is higher than the value indicated by these bits.

| IL1 | IL0 | Interrupt level | Priority              |

|-----|-----|-----------------|-----------------------|

| 0   | 0   | 0               | High                  |

| 0   | 1   | 1               | 1 ★                   |

| 1   | 0   | 2               |                       |

| 1   | 1   | 3               | Low = no interruption |

N flag : Set to "1" if the MSB is set to "1" as the result of an arithmetic operation. Cleared to "0" when the bit is set to "0".

Dit is set to 0

Z flag : Set to "1" when an arithmetic operation results in "0". Cleared to "0" otherwise.

V flag : Set to "1" if the complement on 2 overflows as a result of an arithmetic operation. Cleared to "0" otherwise.

C flag : Set to "1" when a carry or a borrow from bit 7 occurs as a result of an arithmetic operation. Cleared

to "0" otherwise. Set to the shift-out value in the case of a shift instruction.

The following general-purpose registers are provided:

General-purpose registers: 8-bit data storage registers

The general-purpose registers are 8 bits and located in the register banks on the memory. 1-bank contains 8-register. Up to a total of 32 banks can be used on the MB95110H series. The bank currently in use is specified by the register bank pointer (RP), and the lower 3 bits of OP code indicates the general-purpose register 0 (R0) to general-purpose register 7 (R7).

### ■ I/O MAP

| Address              | Register abbreviation | Register name                                        | R/W      | Initial value |

|----------------------|-----------------------|------------------------------------------------------|----------|---------------|

| 0000н                | PDR0                  | Port 0 data register                                 | R/W      | 00000000в     |

| 0001н                | DDR0                  | Port 0 direction register                            | R/W      | 00000000В     |

| 0002н                | PDR1                  | Port 1 data register                                 | R/W      | 00000000В     |

| 0003н                | DDR1                  | Port 1 direction register                            | R/W      | 0000000В      |

| 0004н                | _                     | (Disabled)                                           | _        |               |

| 0005н                | WATR                  | Oscillation stabilization wait time setting register | R/W      | 11111111В     |

| 0006н                | PLLC                  | PLL control register                                 | R/W      | 0000000В      |

| 0007н                | SYCC                  | System clock control register                        | R/W      | 1010Х011в     |

| 0008н                | STBC                  | Standby control register                             | R/W      | 00000000В     |

| 0009н                | RSRR                  | Reset source register                                | R        | XXXXXXXX      |

| 000Ан                | TBTC                  | Timebase timer control register                      | R/W      | 00000000В     |

| 000Вн                | WPCR                  | Watch prescaler control register                     | R/W      | 0000000В      |

| 000Сн                | WDTC                  | Watchdog timer control register                      | R/W      | 00000000В     |

| 000Дн                | _                     | (Disabled)                                           | _        |               |

| 000Ен                | PDR2                  | Port 2 data register                                 | R/W      | 0000000В      |

| 000Fн                | DDR2                  | Port 2 direction register                            | R/W      | 00000000В     |

| 0010н                | PDR3                  | Port 3 data register                                 | R/W      | 00000000В     |

| 0011н                | DDR3                  | Port 3 direction register                            | R/W      | 00000000В     |

| 0012н,<br>0013н      | _                     | (Disabled)                                           | _        | _             |

| 0014н                | PDR5                  | Port 5 data register                                 | R/W      | 00000000в     |

| 0015н                | DDR5                  | Port 5 direction register                            | R/W      | 00000000В     |

| 0016н                | PDR6                  | Port 6 data register                                 | R/W      | 00000000В     |

| 0017н                | DDR6                  | Port 6 direction register                            | R/W      | 00000000В     |

| 0018н<br>to<br>0029н | _                     | (Disabled)                                           | _        | _             |

| 002Ан                | PDRG                  | Port G data register                                 | R/W      | 0000000В      |

| 002Вн                | DDRG                  | Port G direction register                            | R/W      | 00000000в     |

| 002Сн                | _                     | (Disabled)                                           | <u> </u> | _             |

| 002Dн                | PUL1                  | Port 1 pull-up register                              | R/W      | 00000000в     |

| 002Ен                | PUL2                  | Port 2 pull-up register                              | R/W      | 00000000в     |

| 002Fн                | PUL3                  | Port 3 pull-up register                              | R/W      | 00000000В     |

| 0030н<br>to<br>0034н | _                     | (Disabled)                                           | _        | _             |

| Address              | Register abbreviation | Register name                                             |     | Initial value |

|----------------------|-----------------------|-----------------------------------------------------------|-----|---------------|

| 0035н                | PULG                  | Port G pull-up register                                   | R/W | 00000000В     |

| 0036н                | T01CR1                | 8/16-bit compound timer 01 control status register 1 ch.0 |     | 00000000В     |

| 0037н                | T00CR1                | 8/16-bit compound timer 00 control status register 1 ch.0 | R/W | 00000000В     |

| 0038н                | T11CR1                | 8/16-bit compound timer 11 control status register 1 ch.1 | R/W | 00000000В     |

| 0039н                | T10CR1                | 8/16-bit compound timer 10 control status register 1 ch.1 | R/W | 00000000в     |

| 003Ан                | PC01                  | 8/16-bit PPG1 control register ch.0                       | R/W | 00000000В     |

| 003Вн                | PC00                  | 8/16-bit PPG0 control register ch.0                       | R/W | 00000000В     |

| 003Сн                | PC11                  | 8/16-bit PPG1 control register ch.1                       | R/W | 00000000В     |

| 003Dн                | PC10                  | 8/16-bit PPG0 control register ch.1                       | R/W | 0000000В      |

| 003Ен<br>to<br>0041н | _                     | (Disabled)                                                | _   | _             |

| 0042н                | PCNTH0                | 16-bit PPG status control register (Upper byte) ch.0      | R/W | 0000000В      |

| 0043н                | PCNTL0                | 16-bit PPG status control register (Lower byte) ch.0      | R/W | 0000000В      |

| 0044н<br>to<br>0047н | _                     | (Disabled)                                                | _   | _             |

| 0048н                | EIC00                 | External interrupt circuit control register ch.0/1        | R/W | 0000000В      |

| 0049н                | EIC10                 | External interrupt circuit control register ch.2/3        | R/W | 0000000В      |

| 004Ан                | EIC20                 | External interrupt circuit control register ch.4/5        | R/W | 0000000В      |

| 004Вн                | EIC30                 | External interrupt circuit control register ch.6/7        | R/W | 0000000В      |

| 004Сн<br>to<br>004Fн | _                     | (Disabled)                                                | _   | _             |

| 0050н                | SCR                   | LIN-UART serial control register                          | R/W | 0000000В      |

| 0051н                | SMR                   | LIN-UART serial mode register                             | R/W | 0000000В      |

| 0052н                | SSR                   | LIN-UART serial status register                           | R/W | 00001000в     |

| 0053н                | RDR/TDR               | LIN-UART reception/transmission data register             | R/W | 00000000В     |

| 0054н                | ESCR                  | LIN-UART extended status control register                 | R/W | 00000100в     |

| 0055н                | ECCR                  | LIN-UART extended communication control register          | R/W | 000000XXB     |

| 0056н                | SMC10                 | UART/SIO serial mode control register 1 ch.0              | R/W | 0000000В      |

| 0057н                | SMC20                 | UART/SIO serial mode control register 2 ch.0              | R/W | 00100000в     |

| 0058н                | SSR0                  | UART/SIO serial status register ch.0                      | R/W | 0000001в      |

| 0059н                | TDR0                  | UART/SIO serial output data register ch.0                 | R/W | 00000000в     |

| 005Ан                | RDR0                  | UART/SIO serial input data register ch.0                  | R   | 00000000В     |

| 005Вн<br>to<br>005Fн | _                     | (Disabled)                                                | _   | _             |

| Address              | Register abbreviation | Register name                                                       | R/W | Initial value |

|----------------------|-----------------------|---------------------------------------------------------------------|-----|---------------|

| 0060н                | IBCR00                | I <sup>2</sup> C bus control register 0 ch.0                        | R/W | 00000000в     |

| 0061н                | IBCR10                | I <sup>2</sup> C bus control register 1 ch.0                        | R/W | 00000000в     |

| 0062н                | IBSR0                 | I <sup>2</sup> C bus status register ch.0                           | R   | 00000000в     |

| 0063н                | IDDR0                 | I <sup>2</sup> C data register ch.0                                 | R/W | 00000000в     |

| 0064н                | IAAR0                 | I <sup>2</sup> C address register ch.0                              | R/W | 00000000в     |

| 0065н                | ICCR0                 | I <sup>2</sup> C clock control register ch.0                        | R/W | 00000000в     |

| 0066н<br>to<br>006Вн | _                     | (Disabled)                                                          | _   | _             |

| 006Сн                | ADC1                  | 8/10-bit A/D converter control register 1                           | R/W | 00000000в     |

| 006Dн                | ADC2                  | 8/10-bit A/D converter control register 2                           | R/W | 00000000в     |

| 006Ен                | ADDH                  | 8/10-bit A/D converter data register (Upper byte)                   | R/W | 00000000в     |

| 006Fн                | ADDL                  | 8/10-bit A/D converter data register (Lower byte)                   | R/W | 00000000в     |

| 0070н                | WCSR                  | Watch counter status register                                       | R/W | 00000000В     |

| 0071н                | _                     | (Disabled)                                                          | _   | _             |

| 0072н                | FSR                   | Flash memory status register                                        | R/W | 000Х0000в     |

| 0073н                | SWRE0                 | Flash memory sector writing control register 0                      | R/W | 00000000в     |

| 0074н                | SWRE1                 | Flash memory sector writing control register 1                      | R/W | 00000000в     |

| 0075н                | _                     | (Disabled)                                                          | _   | _             |

| 0076н                | WREN                  | Wild register address compare enable register                       | R/W | 00000000В     |

| 0077н                | WROR                  | Wild register data test setting register                            | R/W | 0000000В      |

| 0078н                | _                     | (Mirror of register bank pointer (RP) and direct bank pointer (DP)) | _   | _             |

| 0079н                | ILR0                  | Interrupt level setting register 0                                  | R/W | 111111111     |

| 007Ан                | ILR1                  | Interrupt level setting register 1                                  | R/W | 111111111     |

| 007Вн                | ILR2                  | Interrupt level setting register 2                                  | R/W | 11111111В     |

| 007Сн                | ILR3                  | Interrupt level setting register 3                                  | R/W | 111111111     |

| 007Dн                | ILR4                  | Interrupt level setting register 4                                  | R/W | 111111111     |

| 007Ен                | ILR5                  | Interrupt level setting register 5                                  | R/W | 111111111     |

| 007Fн                | _                     | (Disabled)                                                          | _   | _             |

| 0F80н                | WRARH0                | Wild register address setting register (Upper byte) ch.0            | R/W | 0000000В      |

| 0F81н                | WRARL0                | Wild register address setting register (Lower byte) ch.0            | R/W | 00000000в     |

| 0F82н                | WRDR0                 | Wild register data setting register ch.0                            | R/W | 00000000в     |

| 0F83н                | WRARH1                | Wild register address setting register (Upper byte) ch.1            | R/W | 00000000в     |

| 0F84н                | WRARL1                | Wild register address setting register (Lower byte) ch.1            | R/W | 0000000В      |

| 0F85н                | WRDR1                 | Wild register data setting register ch.1                            | R/W | 00000000в     |

| Address              | Register abbreviation | Register name                                                  | R/W | Initial value |

|----------------------|-----------------------|----------------------------------------------------------------|-----|---------------|

| 0F86н                | WRARH2                | Wild register address setting register (Upper byte) ch.2       | R/W | 00000000В     |

| 0F87н                | WRARL2                | Wild register address setting register (Lower byte) ch.2       | R/W | 00000000В     |

| 0F88н                | WRDR2                 | Wild register data setting register ch.2                       | R/W | 00000000в     |

| 0F89н<br>to<br>0F91н | _                     | (Disabled)                                                     | _   | _             |

| 0F92н                | T01CR0                | 8/16-bit compound timer 01 control status register 0 ch.0      | R/W | 00000000в     |

| 0F93н                | T00CR0                | 8/16-bit compound timer 00 control status register 0 ch.0      | R/W | 00000000в     |

| 0F94н                | T01DR                 | 8/16-bit compound timer 01 data register ch.0                  | R/W | 00000000в     |

| 0F95н                | T00DR                 | 8/16-bit compound timer 00 data register ch.0                  | R/W | 00000000в     |

| 0F96н                | TMCR0                 | 8/16-bit compound timer 00/01 timer mode control register ch.0 | R/W | 00000000в     |

| 0F97н                | T11CR0                | 8/16-bit compound timer 11 control status register 0 ch.1      | R/W | 00000000в     |

| 0F98н                | T10CR0                | 8/16-bit compound timer 10 control status register 0 ch.1      | R/W | 0000000В      |

| 0F99н                | T11DR                 | 8/16-bit compound timer 11 data register ch.1                  | R/W | 00000000в     |

| 0F9Ан                | T10DR                 | 8/16-bit compound timer 10 data register ch.1                  | R/W | 00000000в     |

| 0F9Вн                | TMCR1                 | 8/16-bit compound timer 10/11 timer mode control register ch.1 | R/W | 00000000в     |

| <b>0</b> F9Сн        | PPS01                 | 8/16-bit PPG1 cycle setting buffer register ch.0               | R/W | 11111111в     |

| 0F9Dн                | PPS00                 | 8/16-bit PPG0 cycle setting buffer register ch.0               | R/W | 11111111в     |

| 0F9Eн                | PDS01                 | 8/16-bit PPG1 duty setting buffer register ch.0                | R/W | 11111111в     |

| 0F9Fн                | PDS00                 | 8/16-bit PPG0 duty setting buffer register ch.0                | R/W | 11111111в     |

| 0FА0н                | PPS11                 | 8/16-bit PPG1 cycle setting buffer register ch.1               | R/W | 11111111в     |

| 0FA1н                | PPS10                 | 8/16-bit PPG0 cycle setting buffer register ch.1               | R/W | 11111111в     |

| 0FA2н                | PDS11                 | 8/16-bit PPG1 duty setting buffer register ch.1                | R/W | 11111111в     |

| 0FА3н                | PDS10                 | 8/16-bit PPG0 duty setting buffer register ch.1                | R/W | 11111111в     |

| 0FА4н                | PPGS                  | 8/16-bit PPG starting register                                 | R/W | 00000000в     |

| 0FА5н                | REVC                  | 8/16-bit PPG output inversion register                         | R/W | 00000000в     |

| 0FA6н<br>to<br>0FA9н | _                     | (Disabled)                                                     | _   | _             |

| 0ГААн                | PDCRH0                | 16-bit PPG down counter register (Upper byte) ch.0             | R   | 0000000В      |

| 0FАВн                | PDCRL0                | 16-bit PPG down counter register (Lower byte) ch.0             | R   | 00000000в     |

| 0FAСн                | PCSRH0                | 16-bit PPG cycle setting buffer register (Upper byte) ch.0     | R/W | 11111111в     |

| 0FAD <sub>н</sub>    | PCSRL0                | 16-bit PPG cycle setting buffer register (Lower byte) ch.0     | R/W | 11111111в     |

| 0FAEн                | PDUTH0                | 16-bit PPG duty setting buffer register (Upper byte) ch.0      | R/W | 11111111в     |

| 0FAFн                | PDUTL0                | 16-bit PPG duty setting buffer register (Lower byte) ch.0      | R/W | 11111111в     |

#### (Continued)

| Address              | Register abbreviation | Register name                                                            | R/W | Initial value |

|----------------------|-----------------------|--------------------------------------------------------------------------|-----|---------------|

| 0FB0н<br>to<br>0FBBн | _                     | (Disabled)                                                               | _   | _             |

| 0FВСн                | BGR1                  | LIN-UART baud rate generator register 1                                  | R/W | 0000000в      |

| 0FBDн                | BGR0                  | LIN-UART baud rate generator register 0                                  | R/W | 0000000в      |

| 0FВЕн                | PSSR0                 | UART/SIO dedicated baud rate generator prescaler selection register ch.0 | R/W | 00000000в     |

| 0FBFн                | BRSR0                 | UART/SIO dedicated baud rate generator baud rate setting register ch.0   | R/W | 00000000в     |

| 0FC0н<br>to<br>0FC2н | _                     | (Disabled)                                                               | _   | _             |

| 0FС3н                | AIDRL                 | A/D input disable register (Lower byte)                                  | R/W | 0000000в      |

| 0FC4н<br>to<br>0FE2н | _                     | (Disabled)                                                               | _   | _             |

| 0FE3н                | WCDR                  | Watch counter data register                                              | R/W | 00111111в     |

| 0FE4н<br>to<br>0FEDн | _                     | (Disabled)                                                               | _   | _             |

| 0FEEн                | ILSR                  | Input level select register                                              | R/W | 0000000в      |

| 0FEFн                | WICR                  | Interrupt pin control register                                           | R/W | 01000000в     |

| 0FF0н<br>to<br>0FFFн | _                     | (Disabled)                                                               | _   | _             |

#### • R/W access symbols

R/W : Readable/Writable

R : Read only W : Write only

#### • Initial value symbols

0 : The initial value of this bit is "0".1 : The initial value of this bit is "1".

X : The initial value of this bit is undefined.

Note: Do not write to the "(Disabled)". Reading the "(Disabled)" returns an undefined value.

### **■ INTERRUPT SOURCE TABLE**

|                                      | Interrupt         | Vector tab        | le address        | Bit name of                      | Same level                                       |

|--------------------------------------|-------------------|-------------------|-------------------|----------------------------------|--------------------------------------------------|

| Interrupt source                     | request<br>number | Upper             | Lower             | interrupt level setting register | priority order<br>(atsimultaneous<br>occurrence) |

| External interrupt ch.0              | IRQ0              | FFFA <sub>H</sub> | FFFB⊦             | L00 [1 : 0]                      | High                                             |

| External interrupt ch.4              | INQU              | FFFAH             | ГГГОН             | L00 [1 . 0]                      | <b>A</b>                                         |

| External interrupt ch.1              | IRQ1              | FFF8 <sub>H</sub> | FFF9 <sub>H</sub> | L01 [1 : 0]                      |                                                  |

| External interrupt ch.5              | INQI              | ГГГОН             | ГГГЭН             | LOT [T.O]                        |                                                  |

| External interrupt ch.2              | IRQ2              | FFF6 <sub>H</sub> | FFF7 <sub>H</sub> | L02 [1 : 0]                      |                                                  |

| External interrupt ch.6              | IRQZ              | ГГГОН             | FFF/H             | L02 [1 . 0]                      |                                                  |

| External interrupt ch.3              | IRQ3              | FFF4 <sub>H</sub> | FFF5 <sub>H</sub> | 1.02 [4 - 0]                     |                                                  |

| External interrupt ch.7              | IRQS              |                   | ГГГЭН             | L03 [1 : 0]                      |                                                  |

| UART/SIO ch.0                        | IRQ4              | FFF2 <sub>H</sub> | FFF3 <sub>H</sub> | L04 [1 : 0]                      |                                                  |

| 8/16-bit compound timer ch.0 (Lower) | IRQ5              | FFF0 <sub>H</sub> | FFF1 <sub>H</sub> | L05 [1 : 0]                      |                                                  |

| 8/16-bit compound timer ch.0 (Upper) | IRQ6              | FFEEH             | FFEFH             | L06 [1 : 0]                      |                                                  |

| LIN-UART (reception)                 | IRQ7              | FFECH             | FFEDH             | L07 [1:0]                        |                                                  |

| LIN-UART (transmission)              | IRQ8              | FFEAH             | FFEBH             | L08 [1 : 0]                      |                                                  |

| 8/16-bit PPG ch.1 (Lower)            | IRQ9              | FFE8 <sub>H</sub> | FFE9 <sub>H</sub> | L09 [1 : 0]                      |                                                  |

| 8/16-bit PPG ch.1 (Upper)            | IRQ10             | FFE6 <sub>H</sub> | FFE7 <sub>H</sub> | L10 [1 : 0]                      |                                                  |

| (Unused)                             | IRQ11             | FFE4 <sub>H</sub> | FFE5 <sub>H</sub> | L11 [1 : 0]                      |                                                  |

| 8/16-bit PPG ch.0 (Upper)            | IRQ12             | FFE2 <sub>H</sub> | FFE3 <sub>H</sub> | L12 [1 : 0]                      |                                                  |

| 8/16-bit PPG ch.0 (Lower)            | IRQ13             | FFE0 <sub>H</sub> | FFE1 <sub>H</sub> | L13 [1 : 0]                      |                                                  |

| 8/16-bit compound timer ch.1 (Upper) | IRQ14             | FFDEH             | FFDF <sub>H</sub> | L14 [1 : 0]                      |                                                  |

| 16-bit PPG ch.0                      | IRQ15             | FFDCH             | FFDDH             | L15 [1 : 0]                      |                                                  |

| I <sup>2</sup> C ch.0                | IRQ16             | FFDA <sub>H</sub> | FFDB⊦             | L16 [1 : 0]                      |                                                  |

| (Unused)                             | IRQ17             | FFD8 <sub>H</sub> | FFD9⊦             | L17 [1:0]                        |                                                  |

| 8/10-bit A/D converter               | IRQ18             | FFD6 <sub>H</sub> | FFD7 <sub>H</sub> | L18 [1 : 0]                      |                                                  |

| Timebase timer                       | IRQ19             | FFD4 <sub>H</sub> | FFD5 <sub>H</sub> | L19 [1 : 0]                      |                                                  |

| Watch timer/counter                  | IRQ20             | FFD2 <sub>H</sub> | FFD3 <sub>H</sub> | L20 [1 : 0]                      |                                                  |

| (Unused)                             | IRQ21             | FFD0 <sub>H</sub> | FFD1 <sub>H</sub> | L21 [1 : 0]                      |                                                  |

| 8/16-bit compound timer ch.1 (Lower) | IRQ22             | FFCEH             | FFCFH             | L22 [1 : 0]                      | ▼                                                |

| Flash memory                         | IRQ23             | FFCCH             | FFCDH             | L23 [1 : 0]                      | Low                                              |

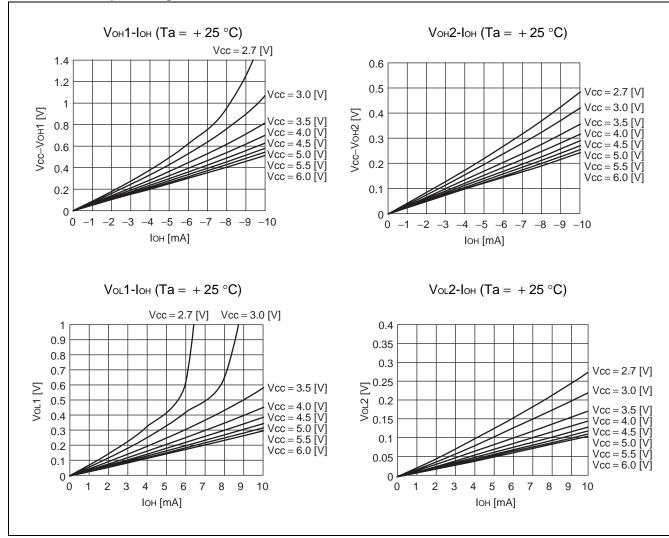

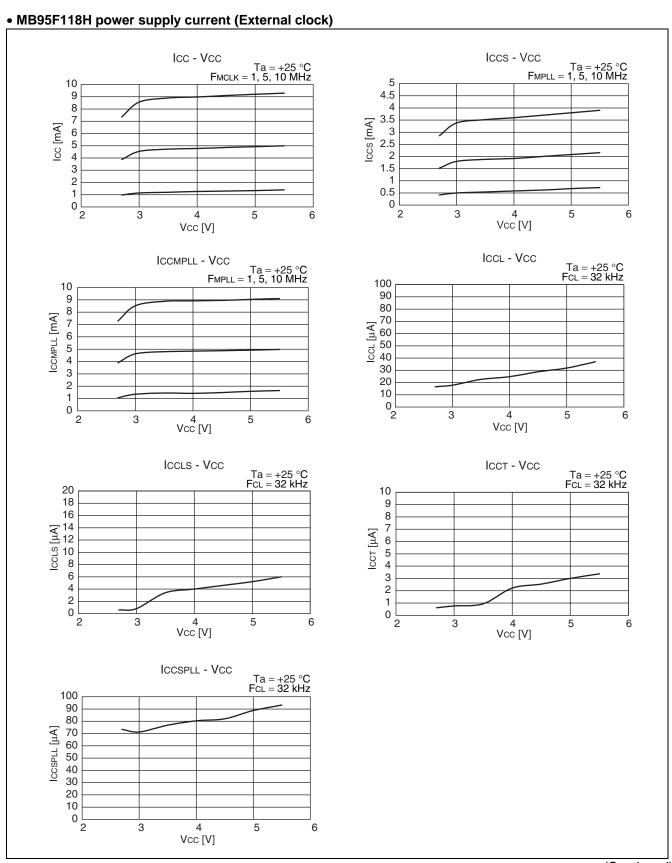

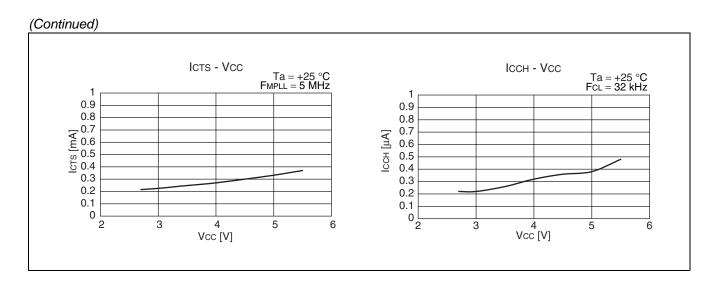

### **■ ELECTRICAL CHARACTERISTICS**

### 1. Absolute Maximum Ratings

| Parameter                              | Symbol             | Rat       | ting        | Unit | Remarks                                                                                    |

|----------------------------------------|--------------------|-----------|-------------|------|--------------------------------------------------------------------------------------------|

| Parameter                              | Symbol             | Min       | Max         | Unit | Remarks                                                                                    |

| Power supply voltage*1                 | Vcc<br>AVcc        | Vss - 0.3 | Vss + 6.0   | V    | *2                                                                                         |

| Input voltage*1                        | Vı                 | Vss - 0.3 | Vss + 6.0   | V    | *3                                                                                         |

| Output voltage*1                       | Vo                 | Vss - 0.3 | Vss + 6.0   | V    | *3                                                                                         |

| Maximum clamp current                  | CLAMP              | - 2.0     | + 2.0       | mA   | Applicable to pins*4                                                                       |

| Total maximum clamp current            | $\Sigma  I_CLAMP $ | _         | 20          | mA   | Applicable to pins*4                                                                       |

| "L" level maximum                      | lol1               |           | 15          | m /  | Other than P00 to P07                                                                      |

| output current                         | l <sub>OL2</sub>   | _         | 15          | mA   | P00 to P07                                                                                 |

| "L" level average                      | lolav1             |           | 4           | mA   | Other than P00 to P07 Average output current = operating current × operating ratio (1 pin) |

| current                                | lolav2             |           | 12          | TIIA | P00 to P07 Average output current = operating current × operating ratio (1 pin)            |

| "L" level total maximum output current | $\Sigma$ loL       | _         | 100         | mA   |                                                                                            |

| "L" level total average output current | $\Sigma$ lolav     | _         | 50          | mA   | Total average output current = operating current × operating ratio (Total of pins)         |